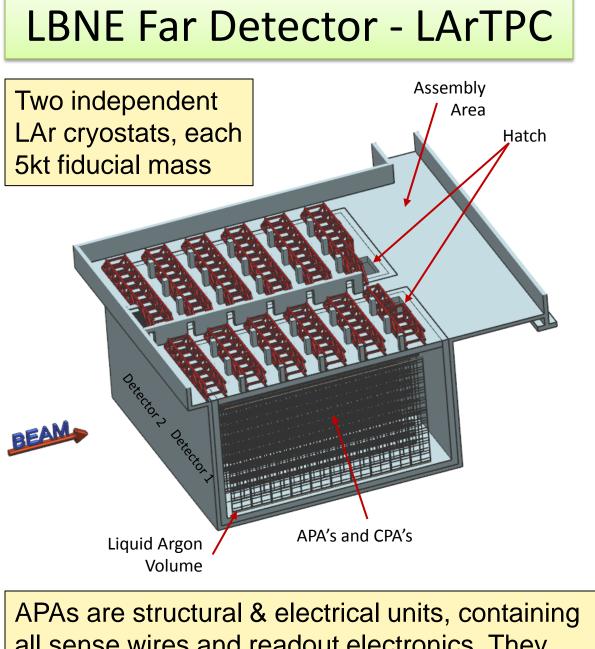

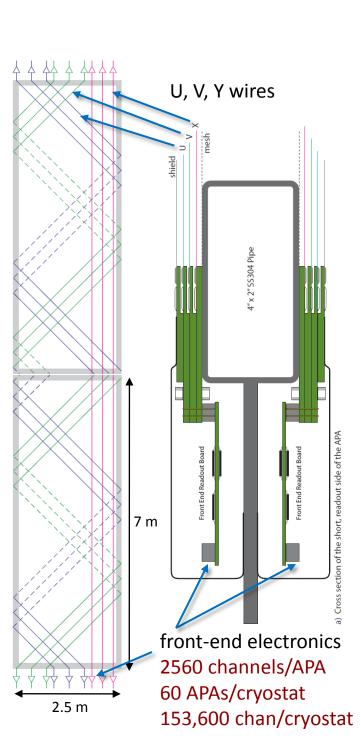

all sense wires and readout electronics. They are standardized manufactured assemblies, can be tested in LN2, stored and transported in shipping containers.

U side board SS Frame

On each APA:

560 X1 wires @ 4.5mm

560 X2 wires @ 4.5mm

720 U wires @ 4.9mm

720 V wires @ 5.0mm

1120 grid wires @ 4.5mm

20 front end mother boards (128ch)

mounted on one end of the frame.

V top board

X top boar

Mounting Plate The U and V sense wires wrap around the frame to read charge drifting from both sides. The X1 and X2 planes resolve the side of a hit. The U wires are at 45.7° and V wires are at 44.3° to the long axis to resolve ambiguities in hits on the two sides

U

G

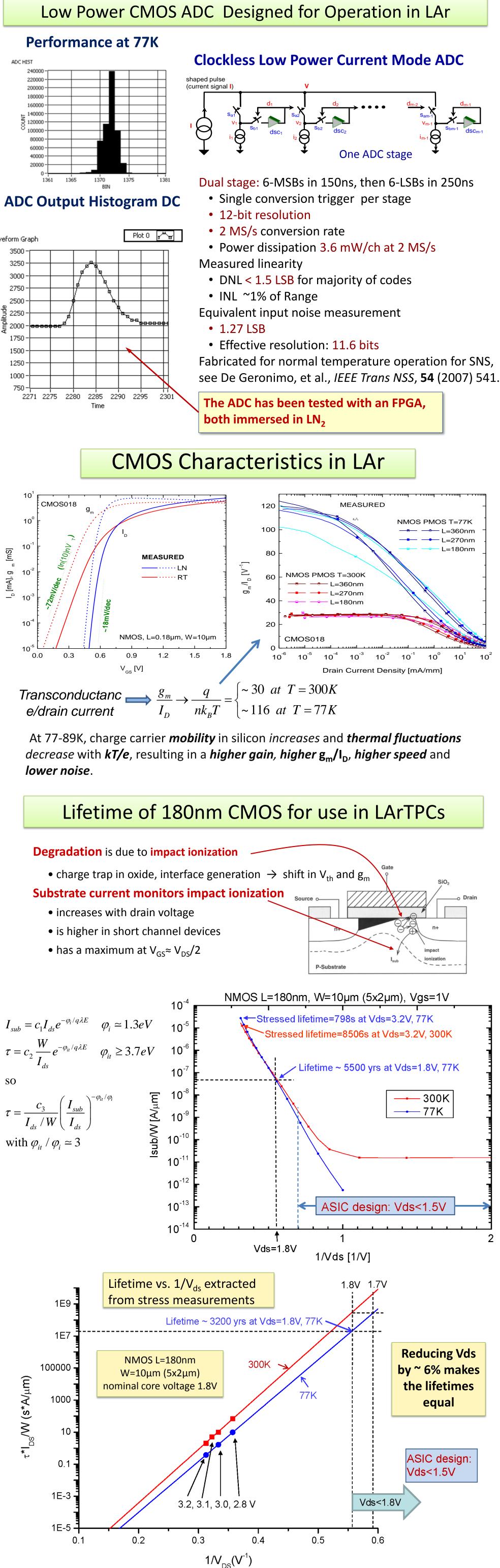

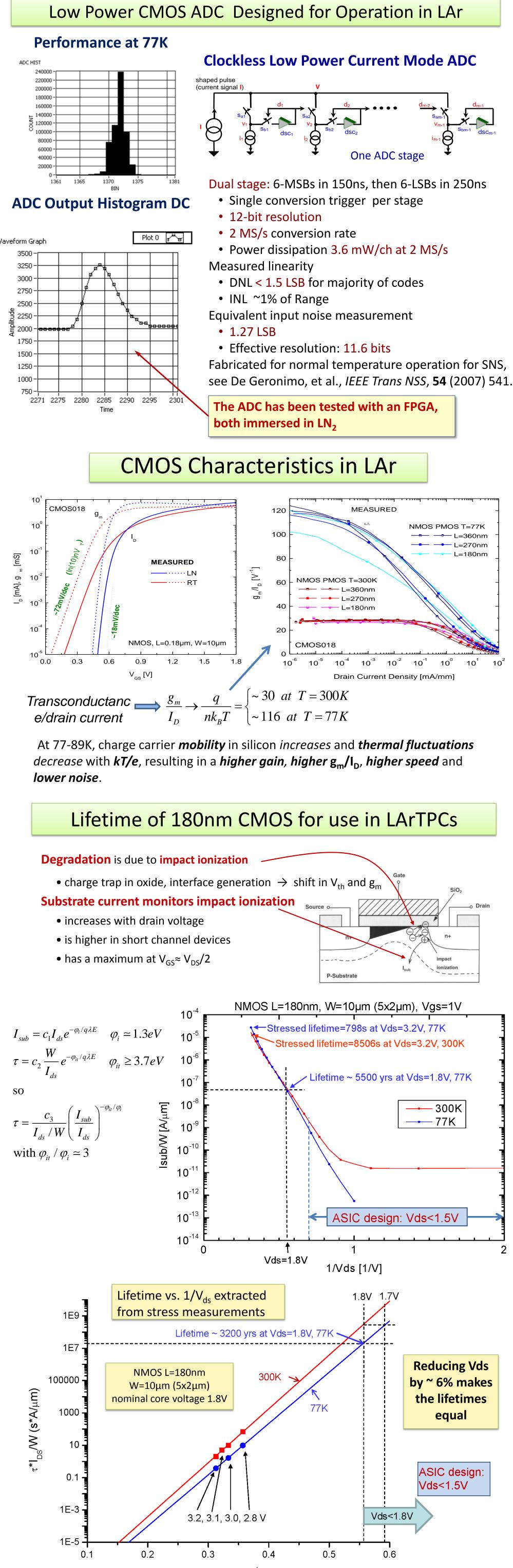

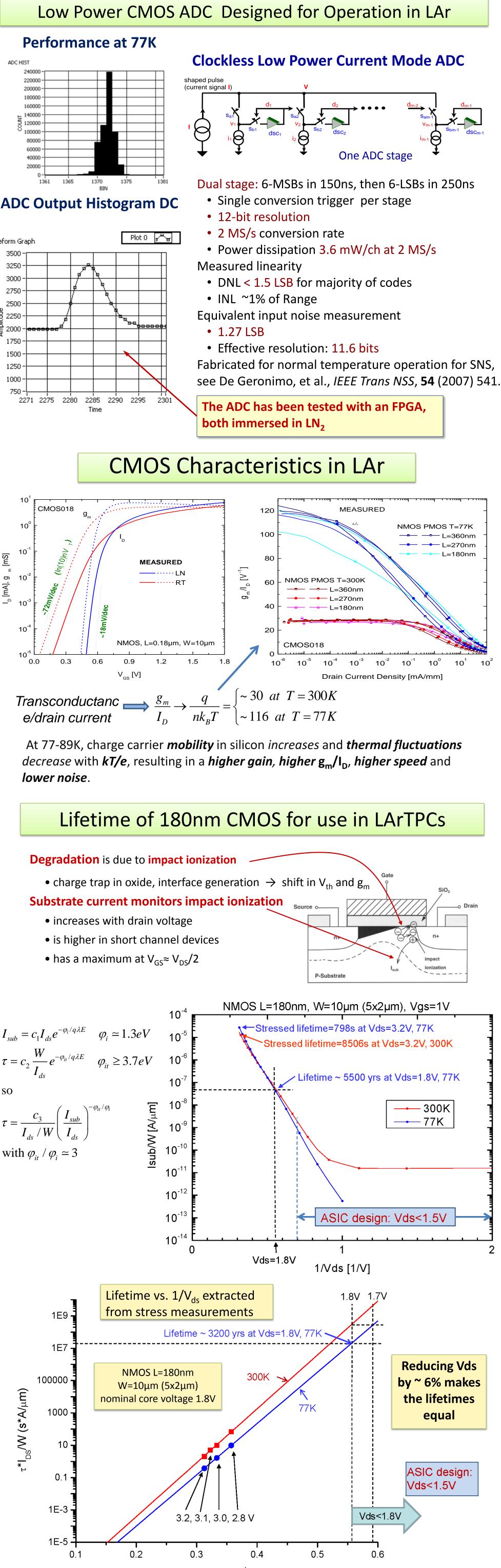

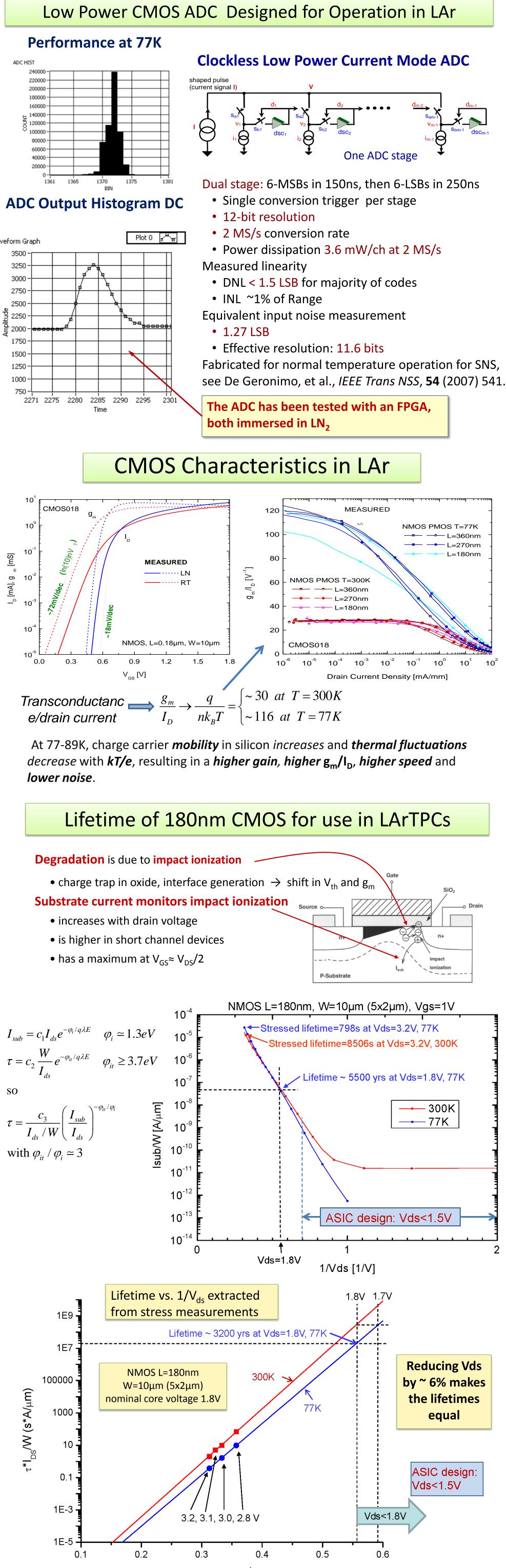

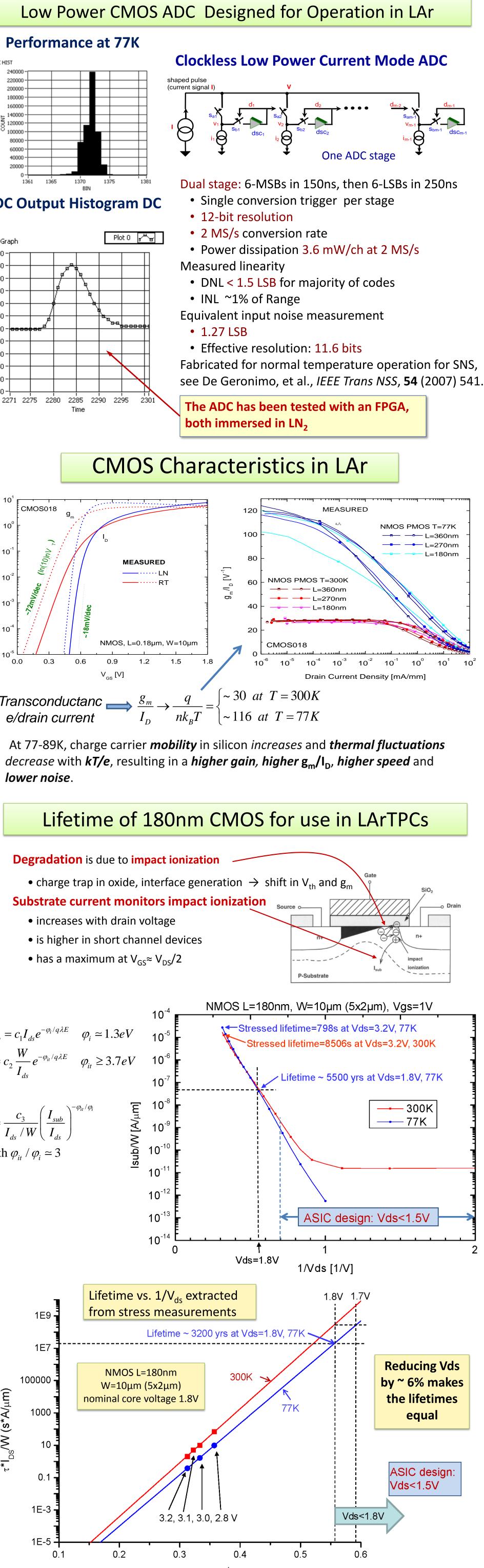

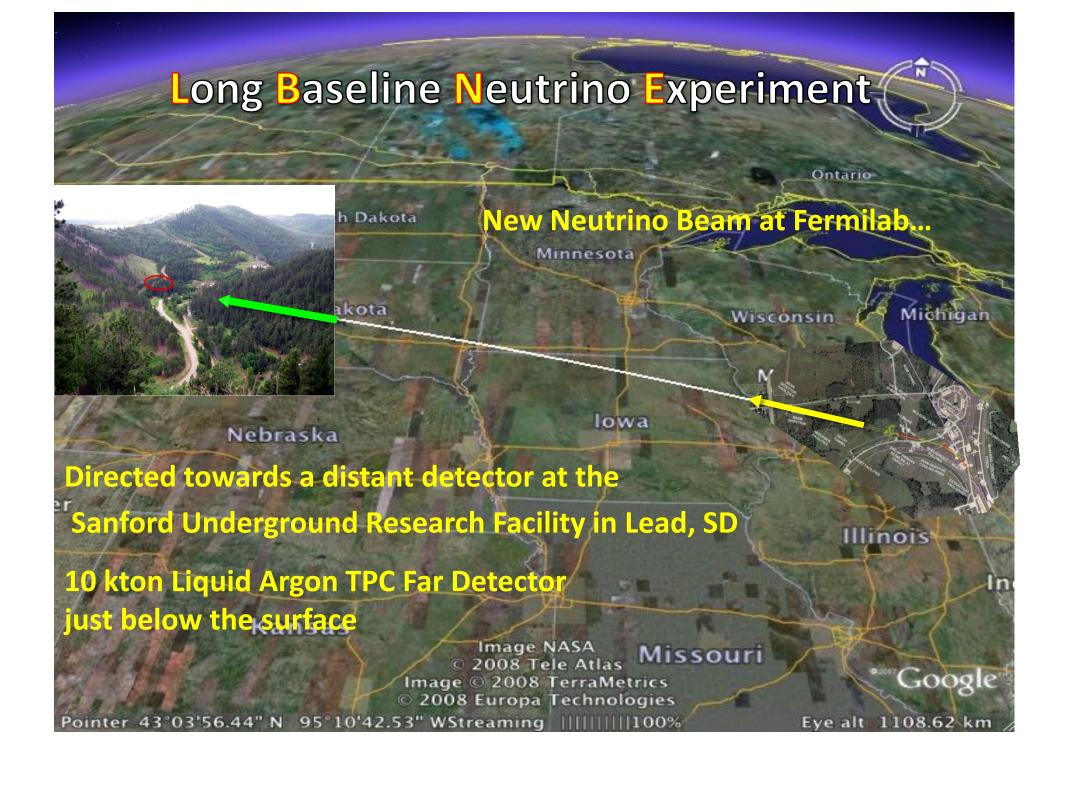

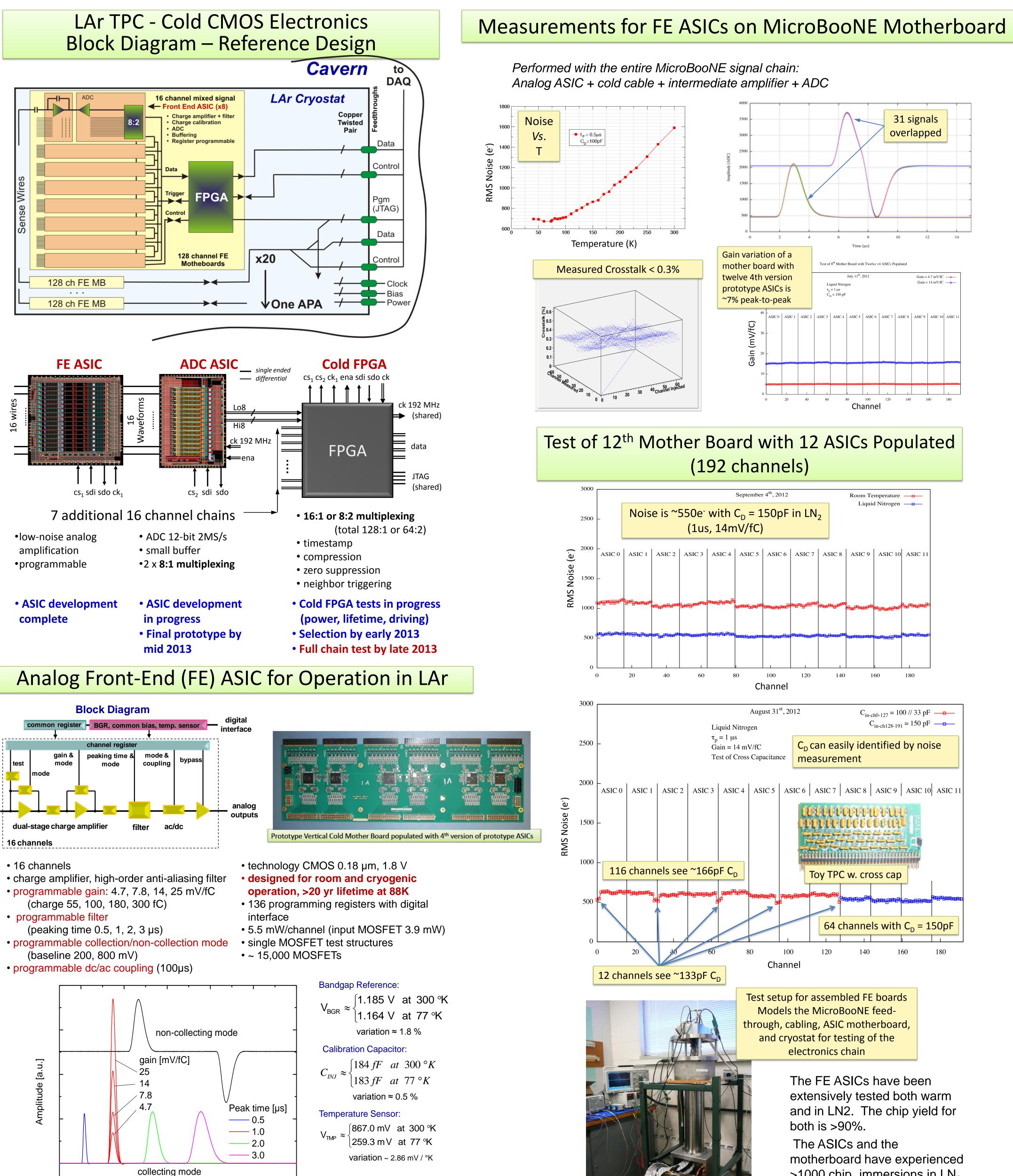

# Cold electronics for the LBNE LAr TPC

C. Thorn, Gianluigi De Geronimo, Alessio D'Andragora, Shaorui Li, Neena Nambiar, Sergio Rescia, Emerson Vernon, Hucheng Chen, Francesco Lanni, Don Makowiecki, Veljko Radeka, and Bo Yu Brookhaven National Laboratory, Upton, NY USA 11973-5000

## Why put the signal processing chain in LAr?

- 1. The proximity of the charge sensitive amplifier to the sense wires reduces cabling capacitance, and therefore noise.

- 2. Digitizing, zero-suppression, and multiplexing in LAr minimize the cable plant, decreasing contamination of LAr and decreasing dead volume

- Fewer feed-throughs are required in the cryostat decreasing contamination risk and increasing cryostat design flexibility

Maximum charge of 55, 100, 180, or 300 fC

40

20

Time [µs]

50

Electronics are incorporated into anode assemblies, manufactured, tested, and installed as a unit, with minimal cabling, increasing reliability

>1000 chip immersions in  $LN_2$ , without a single failure