LHCb Upgrade Mar 01, 2012 CERN

# Toward the readout board project

R. Le Gac CPPM, CNRS/IN2P3

## The Readout Board project

| WP | Work Package Title | Interested<br>Lead Participant |

|----|--------------------|--------------------------------|

| 0  | Coordination       | Marseille                      |

| 1  | Hardware           | Marseille                      |

| 2  | Firmwares          | Annecy                         |

| 3  | PVSS Supervision   |                                |

| 4  | Commissioning      |                                |

| 5  | Maintenance        |                                |

# WP 2: firmware developments

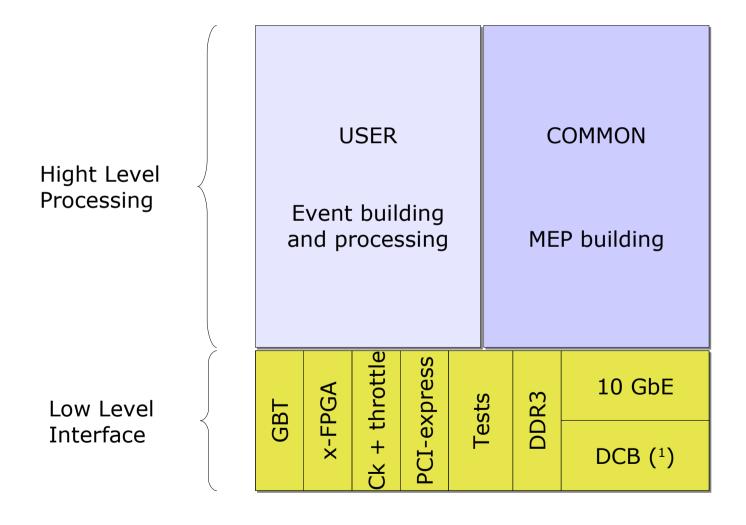

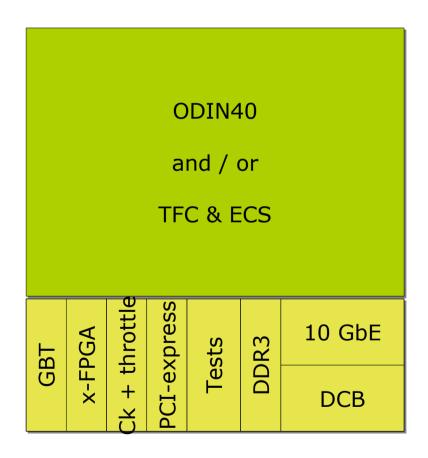

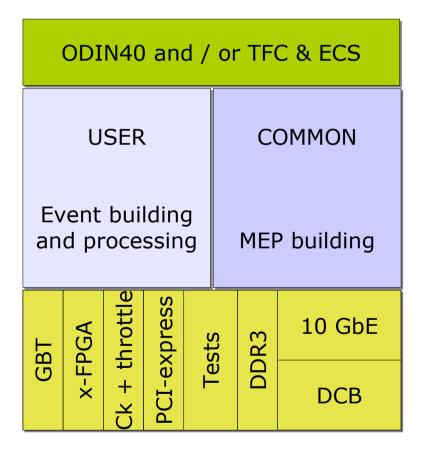

### Radiography of the TELL40 FPGA

<sup>(1)</sup> Data Center Bridging

#### **Variants**

## Firmware Development Work Packages

| WP | Title                                     | Participant(s)         | O(FTE) | Cost | Developpers                               |

|----|-------------------------------------------|------------------------|--------|------|-------------------------------------------|

| 0  | Coordination                              | Annecy                 |        | _    | Stéphane T'Jampens + Cyril Drancourt      |

| 1  | Specifications, documentation and reviews | Annecy                 |        | -    | Stéphane T'Jampens + Cyril Drancourt      |

| 2  | Low Level Interface                       | Marseille              | 6      | _    | Jean-Pierre Cachemiche et al.             |

| 3  | Data Centre Bridging                      | CERN                   |        | _    | Rainer Schwemmen                          |

| 4  | TELL40 MEPs building                      | Annecy (tbc)           | 4      | _    | Cyril Drancourt et al.                    |

| 5  | TELL40 generic user                       | Annecy (tbc)           | 2      | _    | Cyril Drancourt et al.                    |

| 6  | ODIN40, TFC&ECS                           | CERN                   |        | _    | Federico Alessio + Richard Jacobsson      |

| 7  | VELO pixel                                | Manchester, AGH-Krakow |        | _    | Chris Park et al. + Tomasz Szumlak et al. |

| 8  | VELO strip                                |                        |        | _    |                                           |

| 9  | Central Fiber Tracker                     |                        |        | _    |                                           |

| 10 | Scilicon Strip Tracker                    |                        |        | _    |                                           |

| 11 | ОТ                                        | Dormunt                |        | _    | Stefan Swientek et al.                    |

| 12 | RICH                                      | Cambridge              |        | _    | Stephen Wotton                            |

| 13 | TORCH                                     |                        |        | _    |                                           |

| 14 | CALO                                      |                        |        | _    |                                           |

| 15 | MUON                                      | Italie                 |        | _    |                                           |

| 16 | LLT CALO                                  | Annecy                 | 2.5    | _    | Cyril Drancourt et al.                    |

| 17 | LLT MUON                                  | Marseille              | 2      | -    | Jean-Pierre Cachemiche et al.             |

| 18 | LLT L0DU                                  | Clermont               |        | _    | Régis Lefèvre et al.                      |

| 19 | CCPC and test bench                       | Rio (CBPF)             |        |      | André Massaferri                          |

### Next steps

- Kick off meeting with interested developers: requirements, architecture of TELL40 FPGA, tools, ...

- ► May 2012:

- Addendum to the LoI ready:

cost, schedule, milestones, interested institutes / commitments

- End 2012 (R&D milestone)

- Validate that the selected Stratix V has enough resource to satisfy the requirements of the most demanding user (VELOPIX)

- ► Mid 2013:

- TDR ready

- ► End 2013:

- deploy a small fraction of the new readout