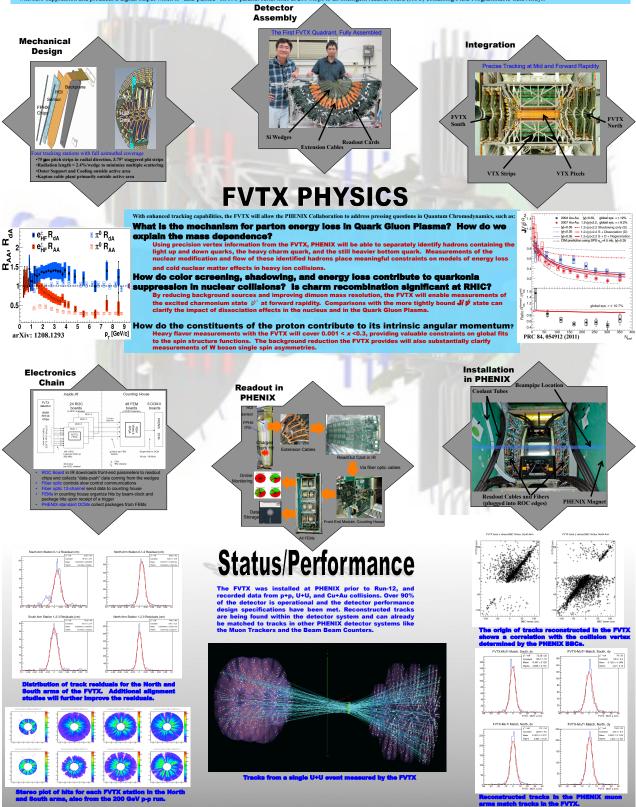

## **The Forward Silicon Vertex Detector**

J. Matthew Durham for the PHENIX FVTX Group (durham@anl.gov) Brookhaven National Laboratory, Charles University Prague, Columbia University, Fermilab, Institute of Physics Prague, Lawrence Berkeley Laboratory, Los Alamos National Laboratory, New Mexico State University, University of New Mexico, Saclay, University of Colorado

The two Forward Silicon Vertex Trackers (FVTX) for the Pioneering High Energy Nuclear Interaction eXperiment (PHENIX) at the Relativistic Heavy Ion Collider (RHIC) extend the precision vertex capability of the PHENIX Silicon Vertex Tracker (VTX) to forward and backward rapidities, covering the existing muon arms. The FVTX detector project was approved by the DOE Office of Science in March 2008, with first construction funds received in April 2008. Project completion was declared in December 2011 when the full FVTX detector was installed into PHENIX. The primary technical improvement provided by the FVTX is the identification of secondary vertices near the original event vertex. With an expected distance of closest approach (DCA) resolution of 200 µm or better at 5 GeV/c, we will see improvement in tracking from the original vertex and be able to identify secondary particles from in-flight decays.

The FVTX is composed of two endcaps, with four silicon mini-strip planes each, covering angles (~10 to 35 degrees) that match the two muon arms. Each silicon plane consists of 48 wedges of mini-strips with 75 µm pitch in the radial direction and lengths in the phi direction varying from 3.4 mm at the inner radius to 11.5 mm at the outer radius. The maximum occupancy reached in central Au-Au collisions is approximately 2.8%. The FVTX has about 0.54 mini-strips with 75 µm pitch in with PAL, which are wire bonded directly to the mini-strips. This chip provides analog and digital processing with zero-suppression and produces a digital output which is "data-pushed" on two parallel serial lines at 200 Mbps to an intelligent readout board (ROC) containing Field-Programmable Gate Arrays.