# Proposal of a sparsification circuit for mixed-mode MAPS detectors

Alessandro Gabrielli on behalf of the SLIM5 Collaboration

Physics Department of Bologna University & INFN Bologna, Viale Berti Pichat 6/2 40127 Bologna Italy Tel. +39-051-2095052 FAX +39-051-2095297 E-mail: alessandro.gabrielli@bo.infn.it

RD 2007: June 27th - 29th Florence IT Alessandro Gabrielli

#### SLIM5 project (INFN collaboration: BO, PI, PV, TO, TN, TS)

Aim

Improve the state-of-the-art of slim tracking system construction for high-energy physics applications

#### **Applications**

Low material budget silicon tracking systems (detector/ mechanics/cooling) relevant for the future experiments (SuperB, ILC) to reduce multiple scattering

MAPS (Monolithic Active Pixels Sensors)

- good candidate technology for the innermost layers of the vertex detectors,

- sensitive zone 10-20 µm thick with integrated front-end electronics,

- some latest papers and presentations:

- L. Ratti, et al., Nucl. Instr. and Meth. A-568 (2006) 159

- G. Rizzo et al., Nucl. Instrum. Methods, A-565 (2006), 195

- F. Forti et al., 2006 IEEE NSS, San Diego, Oct. 30-Nov. 2, IEEE 2006 N34-7

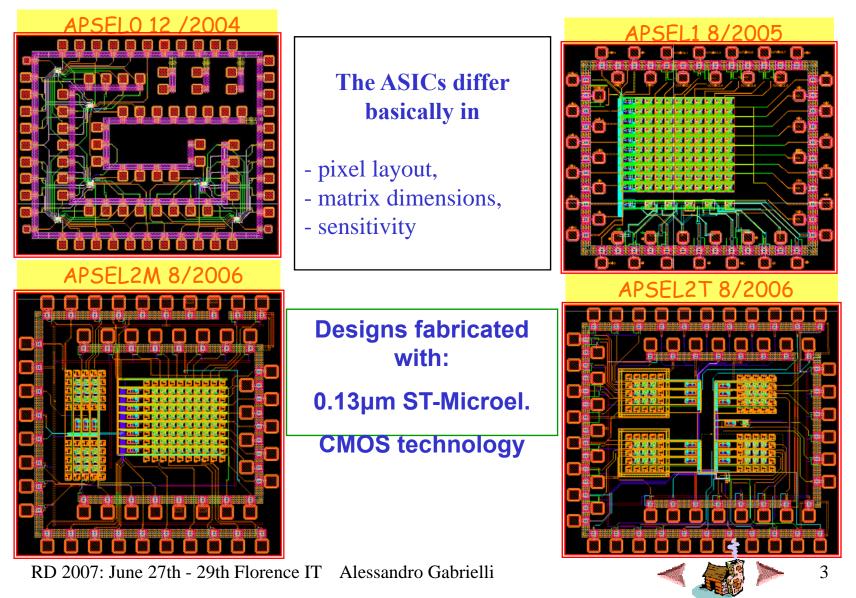

#### THE PAST: ASICs designed, fabricated and tested Full-Custom ASICs: APSEL0, APSEL1, APSEL2M/T

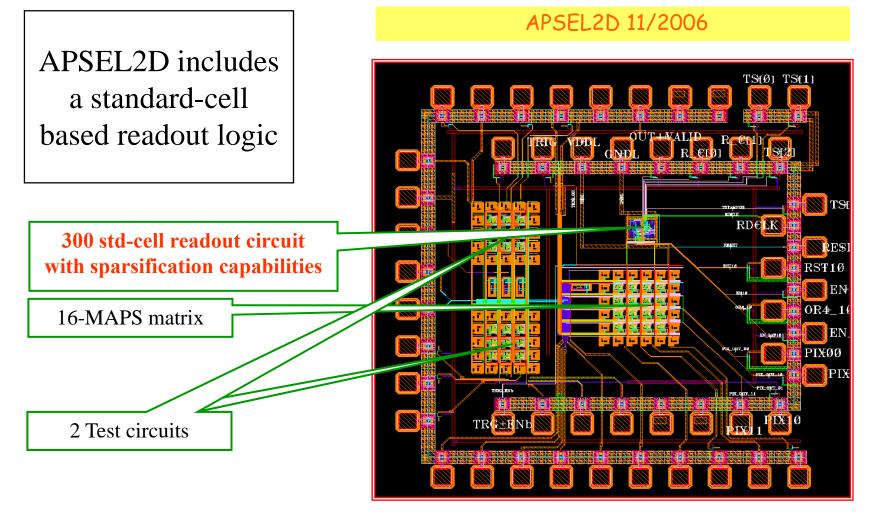

### THE PAST: ASICs designed and fabricated First mixed-mode ASIC: APSEL2D

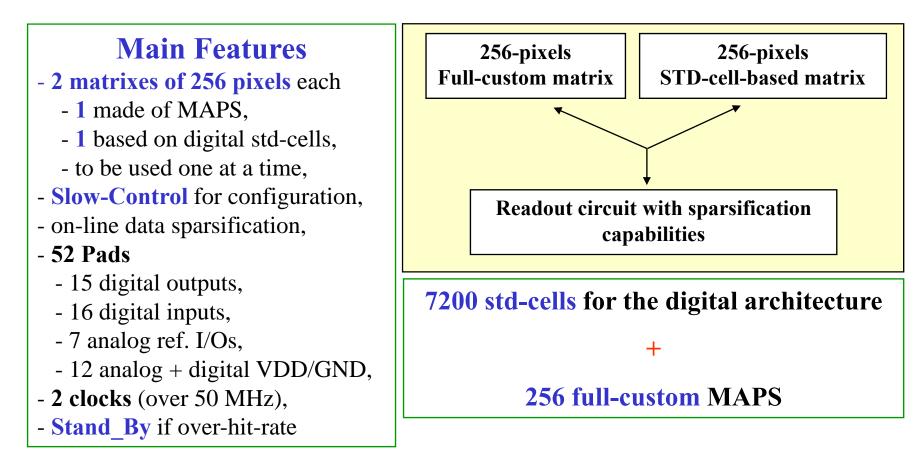

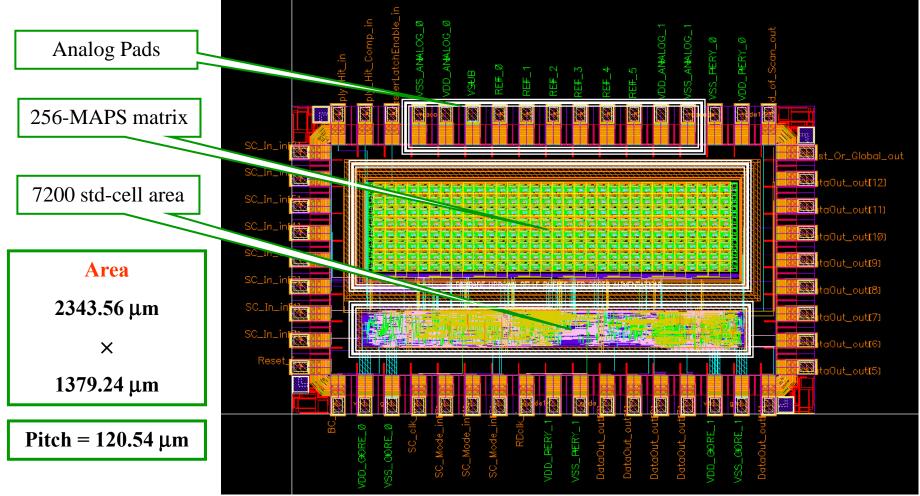

### **THE FUTURE: ASICs designed and under submission** First "large-matrix" mixed-mode ASIC: APSEL3D

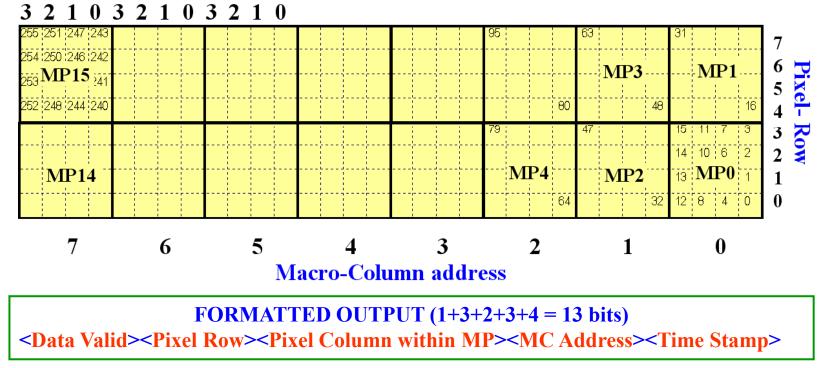

### **THE FUTURE: ASICs designed and under submission** The Matrix

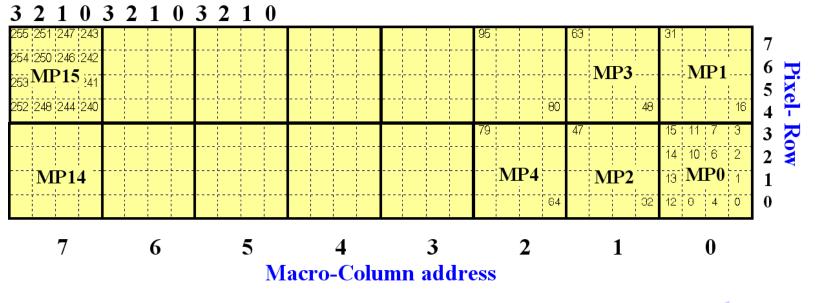

The 256-pixel matrix is arranged in:

- 32 columns  $\times$  8 rows,

- 8 MacroColumns (MC)  $\times$  2 MacroRows (MR),

- 16 MacroPixels composed of  $4 \times 4$  pixels

The pixels, the MCs, the MRs and the MPs are numbered to define the **13-bit** formatted output data

The hits are on-line associated with a **4-bit Time-Stamp**

#### Pixel-Column inside a MC/MP

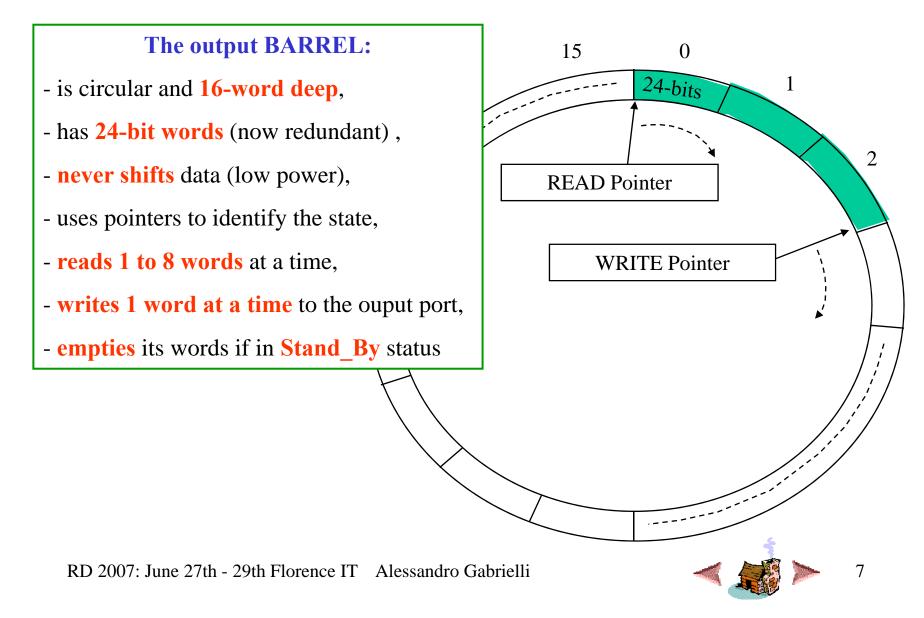

#### **THE FUTURE: ASICs designed and under submission** The queued output dataflow

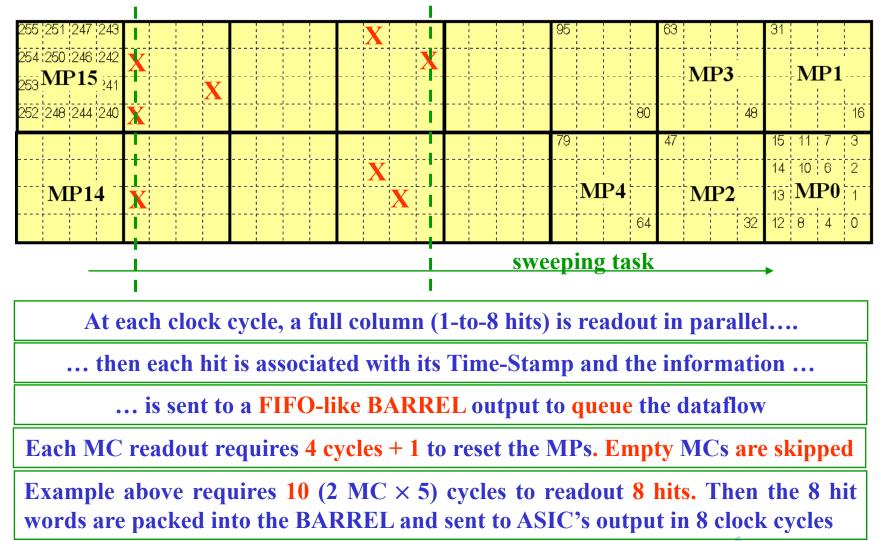

### **THE FUTURE: ASICs designed and under submission** The Matrix Readout

RD 2007: June 27th - 29th Florence IT Alessandro Gabrielli

### **THE FUTURE: ASICs designed and under submission** The Matrix Readout

#### Pixel-Column inside a MC/MP

### THE FUTURE: ASICs designed and under submission The APSEL3D ASIC

### **THE FUTURE: ASICs designed and under submission**

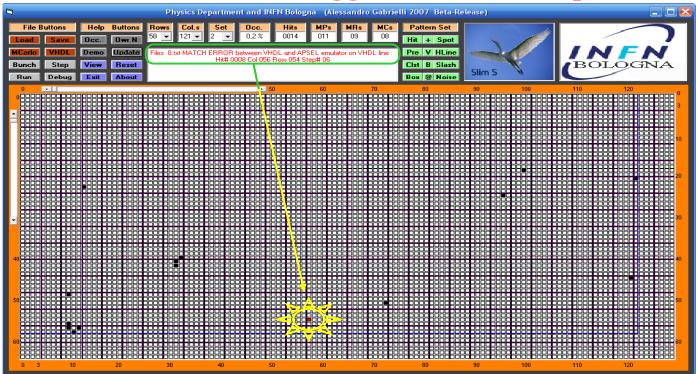

#### The simulator-debugger: under development

#### The simulator-debugger:

- interfaces with Monte Carlo input patterns,

- provides APSEL3D's formatted output data,

- copes with matrixes up to  $128 \times 64$  pixels

RD 2007: June 27th - 29th Florence IT Alessandro Gabrielli

## CONCLUSIONS

The work is aimed at

- fabricating a first "large-size" prototype,

- fabricating a high-density thin MAPS detector, new versions up to 10k MAPS,

- sparsifying on-line the hits,

- matching the requirements of future HEP experiments.

In particular, the readout architecture extends the flexibility of the MAPS devices to be also used in first level triggers on tracks in vertex of future detectors.

It is a novel ASIC with an integrated sparsification circuit on