# The EndoTOFPET-US front end & data acquisition system

Ricardo Bugalho Jornadas LIP, April 22<sup>nd</sup> 2012

#### What is EndoTOFPET-US?

Ultra-Sound transducer

PET head 0.8x0.8x10 mm<sup>3</sup> crystal filbers coupled to digital SiPMs

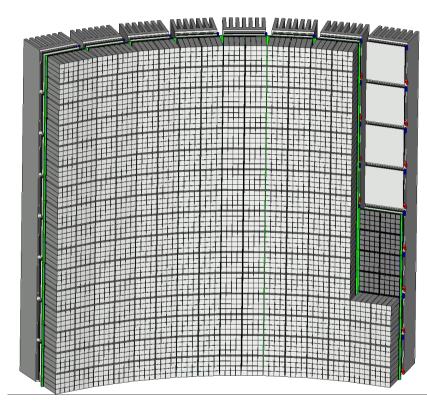

External 20.5x20.5 cm<sup>2</sup> PET plate 4096 3x3x15 mm<sup>3</sup> crystals coupled to SiPM

Very high background event rate (40 MHz)

200 ps time resolution required for background rejection

#### LIP's contribution

- External plate front end

- A suitable ASIC in collaboration with INFN

- Front End Boards

Data Acquisition System

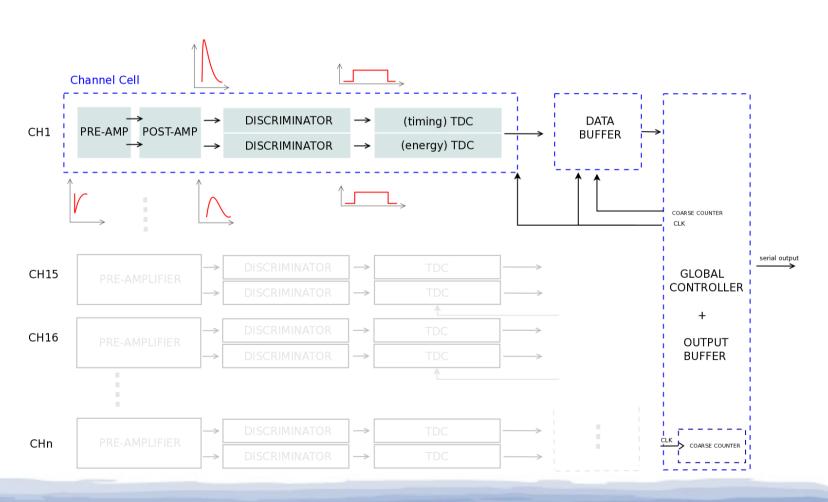

## **ASIC** requirements

- SiPM readout

- <200 ps time resolution</p>

- Suitable for dense systems (10 channels/cm²)

- Monolithic

- Fully digital Time & Energy readout

- < 10 mW/channel</li>

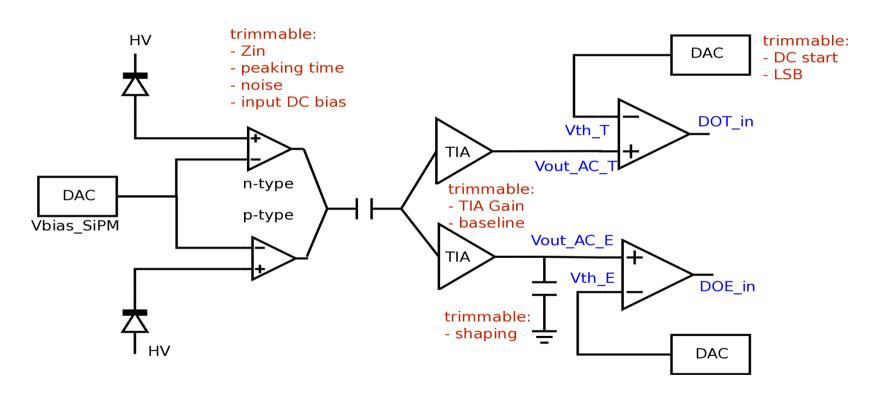

Two transimpedance stages generate two replicas for time and energy measurement; respectively, a fast trigger and a shaped signal.

The low noise front-end allows setting the threshold of the discriminator at 0.5 photoelectrons for the time stamp DOT\_in.

Energy is calculated after calibration of the time-over-threshold of DOE\_in. Both measures are based on a low-power analogue time-to-digital converter with 50ps time binning.

Expected power consumption per channel is 7mW.

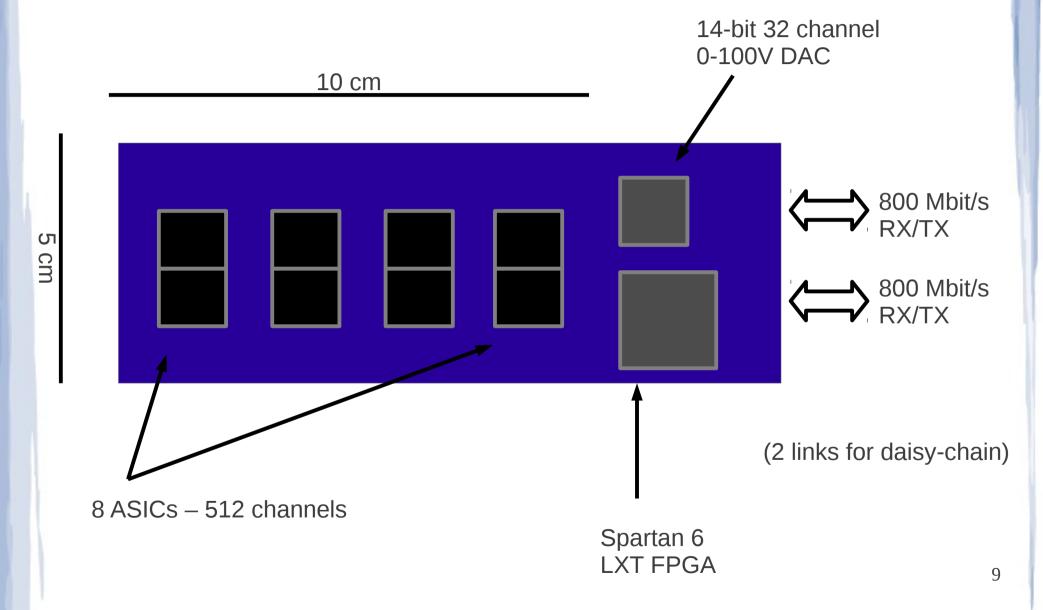

Low input impedance stage (Input resistance trimming to match line impedance) allows fine adjustment (6-bit over 500mV range) of the HV bias of the SiPM\*. Two independent input stages permit the use of devices with different polarities: h-collection (bottom left) or e-collection (top left).

\* Each 16 SiPM array has a common, but adjustable bias (14-bit over 0-100V).

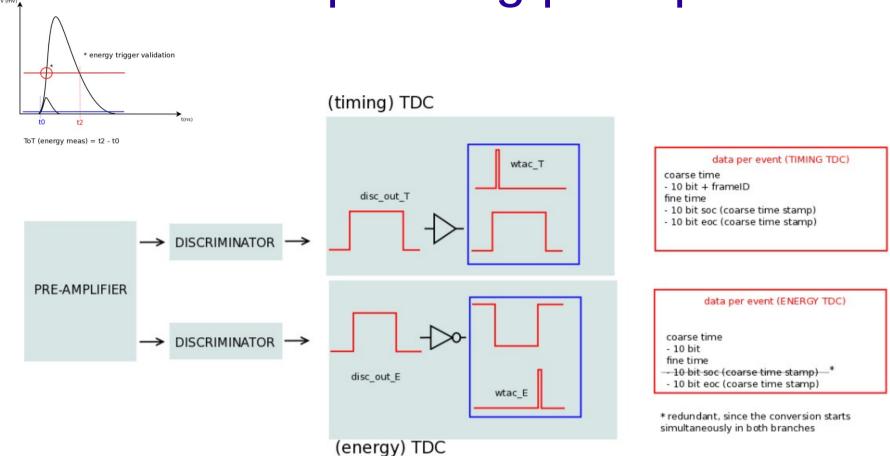

## TDC operating principle

wtac\_\* start at the edge of the discriminator edge but stop at a (known) clock edge wtac\_\* control the charging of a capacitor with a current source

⇒ voltage in the capacitor reflects phase between discriminator edge and clock edge

Afterwards, voltage in capacitor is discharged 128x more slowly

$\Rightarrow$  phase between event and clock is measured in 1/128<sup>th</sup> clock (48 ps for a 160 MHz clock)

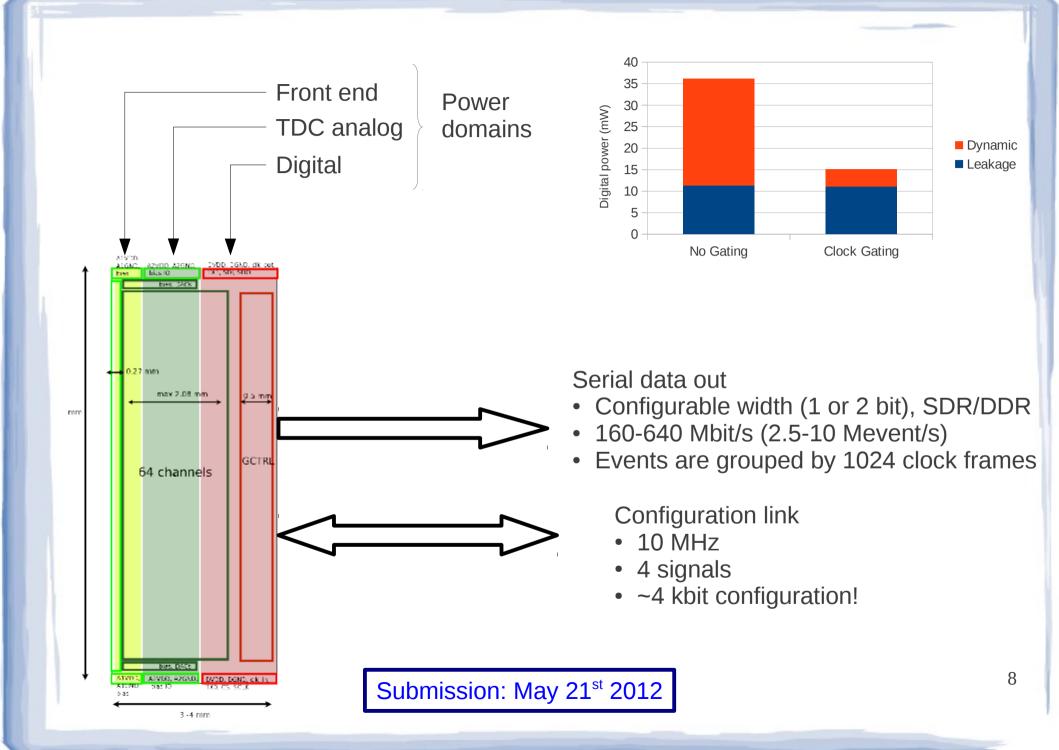

#### Front-end

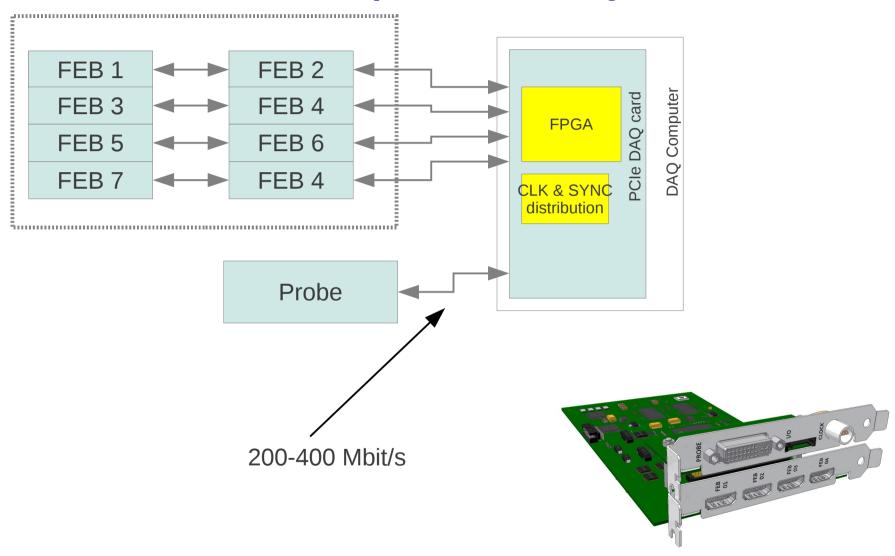

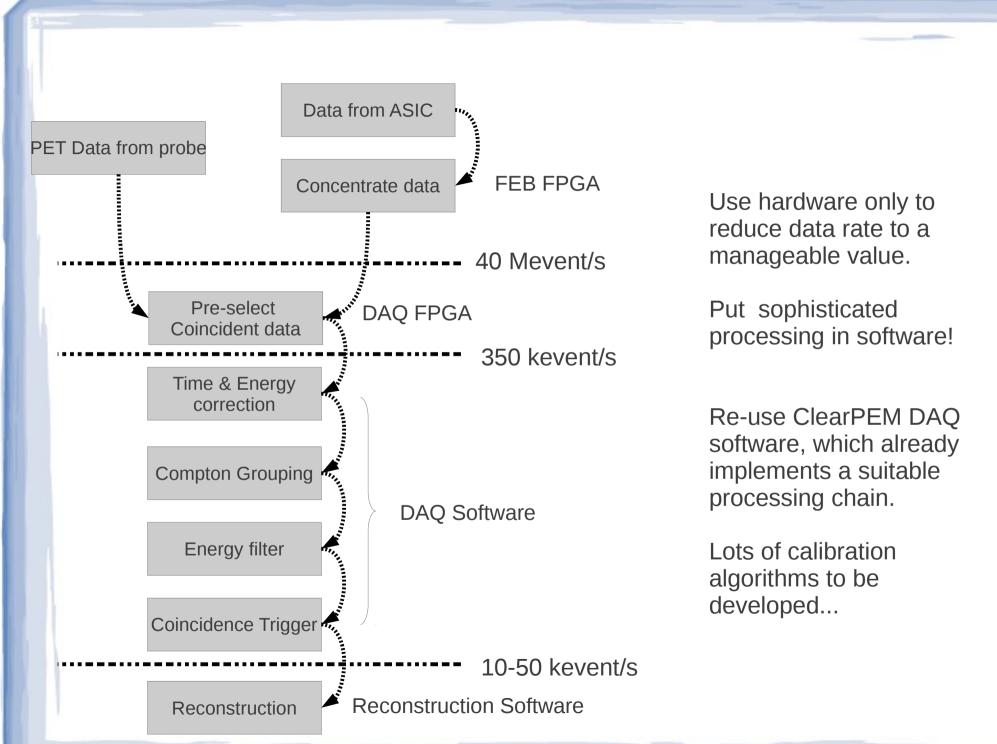

## **Data Acquisition System**

### Summary

- ASIC design is almost complete

- Submission May 21<sup>st</sup> 2012

- Validation in 3<sup>rd</sup> quarter 2012

- Front-end Board design pending

- ASIC pinout

- Plate geometry decisions

- DAQ card design is done

- Under assembly

- Firmware & Software will start in July

Thank you for your attention