## The TDCPix ASIC: Tracking for the NA62 GigaTracker

$\underline{\mathsf{M.\ Noy}^a}$  G. Aglieri Rinella $^a$  S. Bonacini $^a$  J. Kaplon $^a$  A. Kluge $^a$  M. Morel $^a$  L. Perktold $^a$  K. Poltorak $^a$

<sup>a</sup>CERN, CH-1211 Geneva 23, Switzerland

5<sup>th</sup> June 2014

5<sup>th</sup> June 2014

### Introduction to NA62 and the GigaTracker

#### The TDCPix Chip Architecture

#### Measured Performance

Pixel Jitter: Test Output

**TDC** Performance

Full Chain Performance

### Summary

#### Introduction to NA62 and the GigaTracker

The TDCPix Chip Architecture

#### Measured Performance

Pixel Jitter: Test Output

TDC Performance

Full Chain Performance

Summary

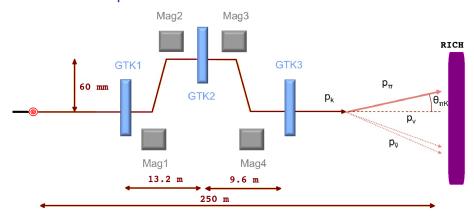

### The NA62 Experiment

- Trajectory

- momentum

- angle

- ► Time

- correlate hits with RICH

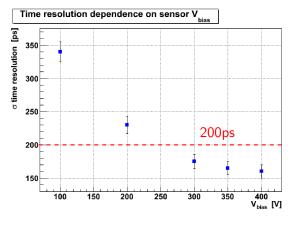

- $ightharpoonup \leq 200\, ps(RMS)$  per station

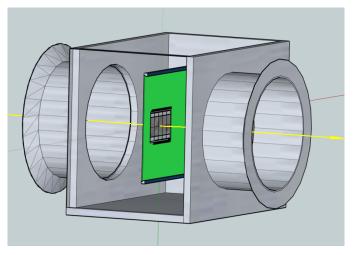

### GTK Station in the Beam Line

▶ in vacuum

- centred on the beam

- ▶  $0.8 \rightarrow 1 \text{ GHz beam rate}$

- 4 □ > 4 圖 > 4 圖 > 4 圖 ≥ 1 = り Q (?)

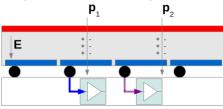

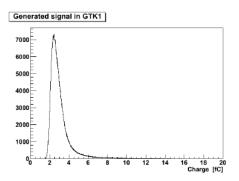

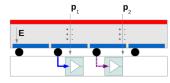

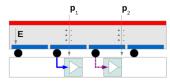

## Principle Of Sensor Operation

- $ightharpoonup V_{bias} \sim$  300-600V

- charge release mechanism is stochastic

- Landau distribution

$$Q_{MP} = 2.4 fC$$

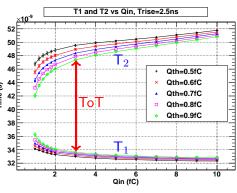

- ▶  $1 fC \le Q \le 10 fC$

- Segmented electrodes give spatial information

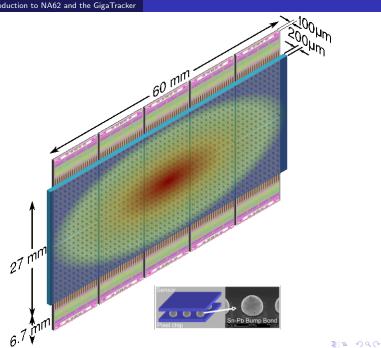

- ▶ Thickness:  $200\mu m$

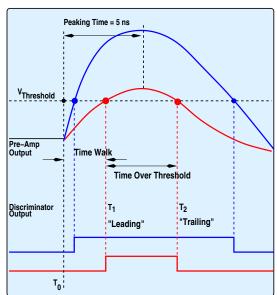

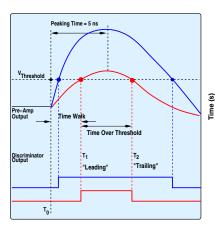

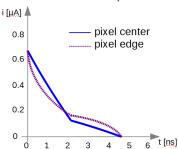

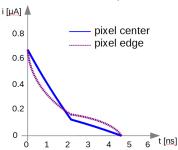

## Pre-Amplifier & Discriminator Signals

# Pre-Amplifier & Discriminator Signals

#### Introduction to NA62 and the GigaTracke

#### The TDCPix Chip Architecture

Measured Performance

Pixel Jitter: Test Output

TDC Performance

Full Chain Performance

### Summary

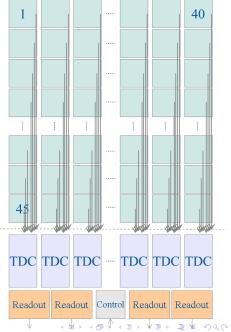

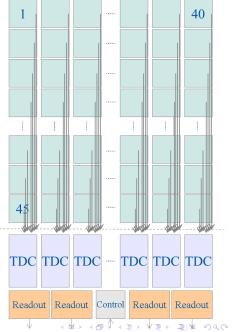

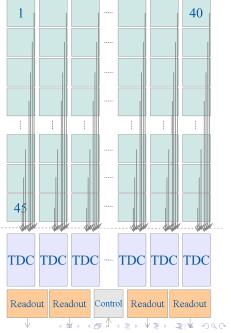

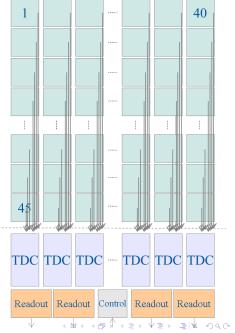

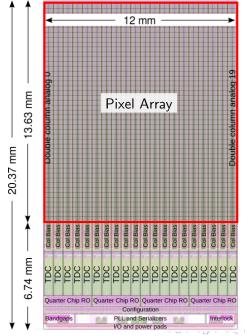

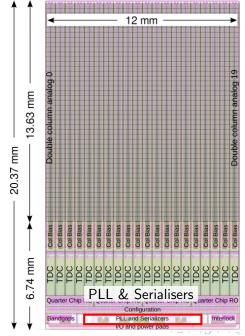

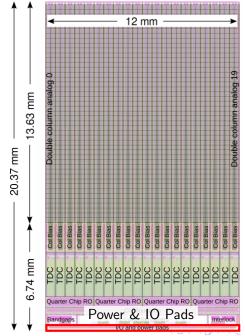

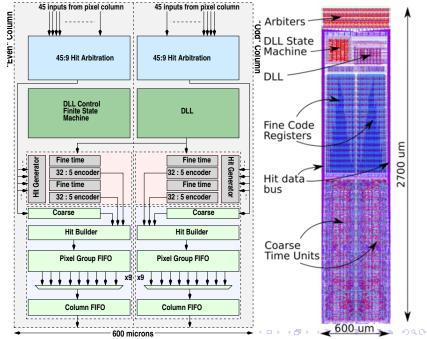

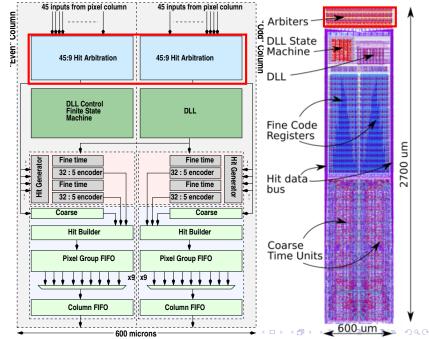

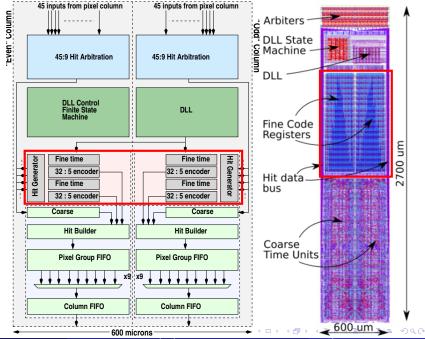

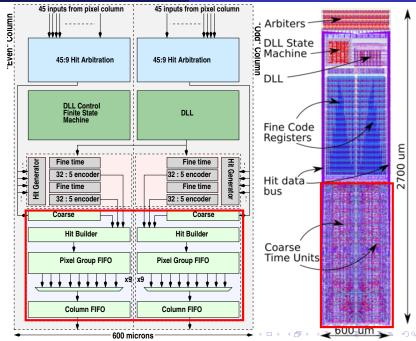

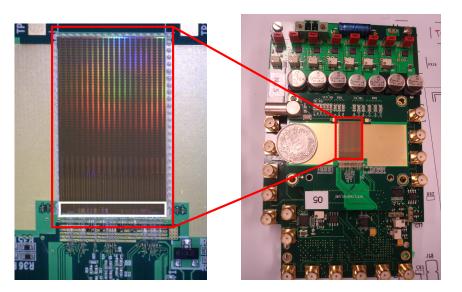

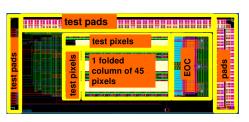

- ► 40 x 45 pixels

- ▶ 300x300  $\mu m^2$

- asynchronous

- ► 40 x 45 pixels

- ► 300×300  $\mu m^2$

- asynchronous

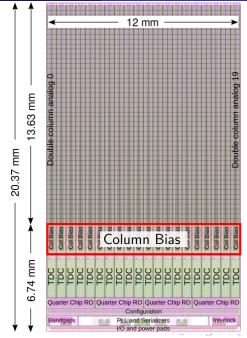

- ► End-Of-Column

- per-pixel hit signal to EOC

- ► 40 x 45 pixels

- ► 300×300 μm²

- asynchronous

- ► End-Of-Column

- per-pixel hit signal to EOC

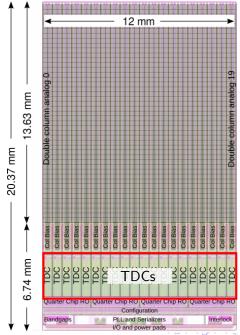

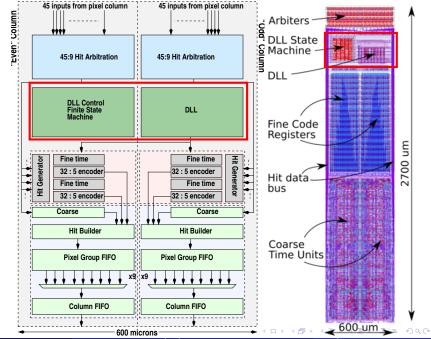

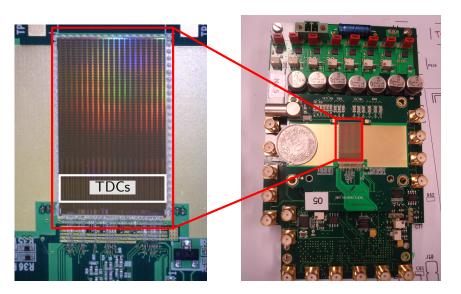

- ▶ 360 dual TDC channels

- ▶ TDC Bin size  $\sim 97\,ps$

- ► 40 x 45 pixels

- ▶  $300 \times 300 \, \mu m^2$

- asynchronous

- ► End-Of-Column

- per-pixel hit signal to EOC

- ▶ 360 dual TDC channels

- ▶ TDC Bin size  $\sim 97\,ps$

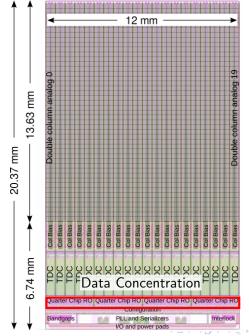

- self-triggered operation

- ► Rate:210MHits/s

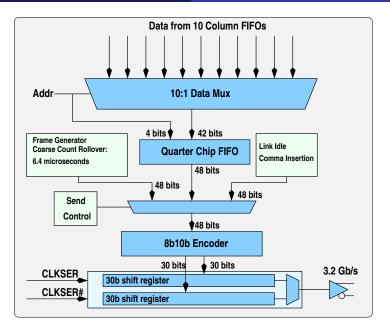

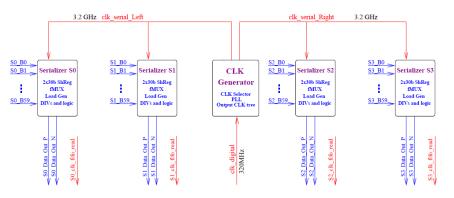

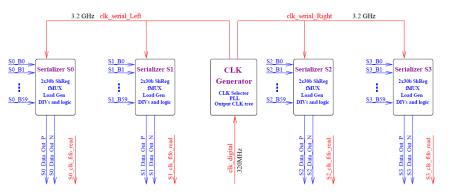

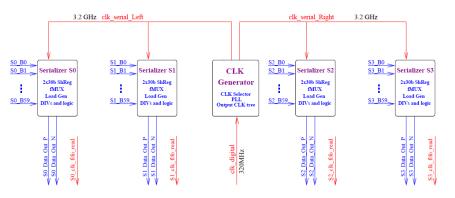

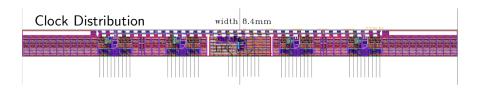

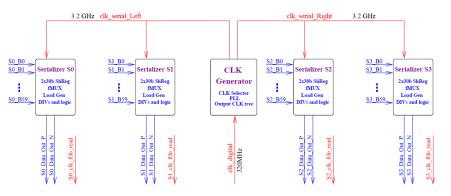

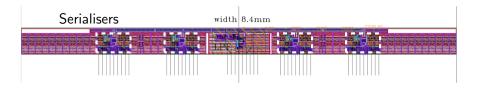

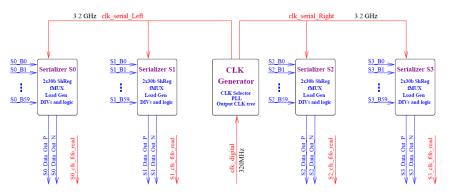

- $4 \times 3.2 \, Gb/s$  serialisers

- ► 40 x 45 pixels

- ► 300x300  $\mu m^2$

- asynchronous

- ► End-Of-Column

- per-pixel hit signal to EOC

- ▶ 360 dual TDC channels

- ▶ TDC Bin size  $\sim 97\,ps$

- self-triggered operation

- ► Rate:210MHits/s

- $4 \times 3.2 \, Gb/s$  serialisers

- ▶ SEE Tolerant

- ▶ state/config.

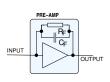

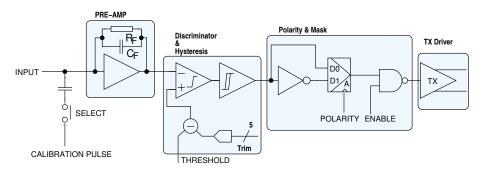

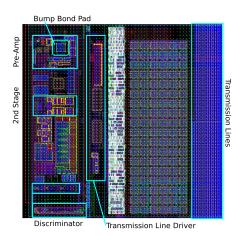

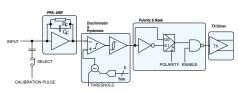

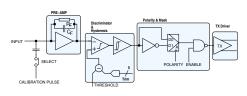

## Simplified Pixel Architecture

- Gain  $\sim 65 \, mV/fC$

- ightharpoonup peaking time  $\sim 5\,ns$

- ightharpoonup ENC  $<250\,e^-$

- Polarity control

- Pixel mask

- TX with pre-emphasis

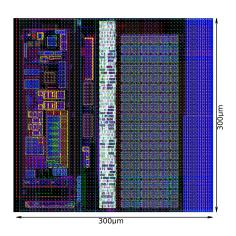

## Pixel Layout:

$300 \times 300 \mu m^2$  cell

# Pixel Layout: Signal Path

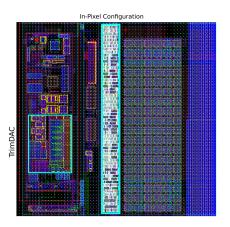

# Pixel Layout: Trimming & Configuration

June 2014

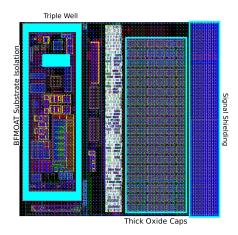

### Pixel Layout: Noise Mitigation

MQ 0.4um 0.4um 0.4um 0.4um 0.4um

- ► Triple well (input transistor)

- BFMOAT substrate isolation

- signal shielding

- Power supply decoupling

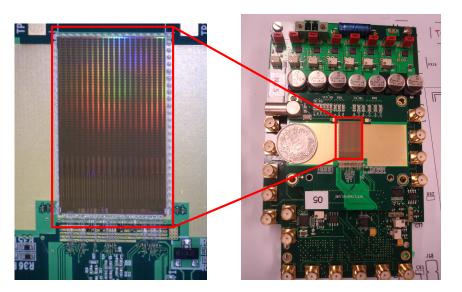

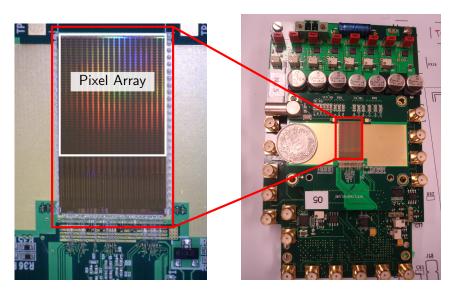

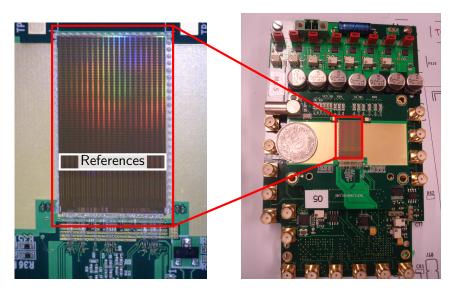

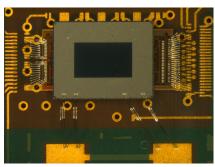

### TDCPix Wire Bonded to the Test Card

### TDCPix Wire Bonded to the Test Card

### TDCPix Wire Bonded to the Test Card

## TDCPix Wire Bonded to the Test Card

## TDCPix Wire Bonded to the Test Card

Introduction to NA62 and the GigaTracke

The TDCPix Chip Architecture

#### Measured Performance

Pixel Jitter: Test Output

**TDC** Performance

Full Chain Performance

# Functionality Tested

| Block                       | Status  | Remarks        |

|-----------------------------|---------|----------------|

| Configuration               | Working | 5 chips tested |

| PLL                         | Working | 3.2 GHz        |

| Serialisers                 | Working | 3.2 Gb/s       |

| Bandgaps                    | Working |                |

| Temperature Interlock       | Working |                |

| Column Biasing              | Working | 200 DACs       |

| In-Pixel Threshold Trimming | Working | 1800 DACs      |

| # of bugs detected          | 0       |                |

First Working Silicon

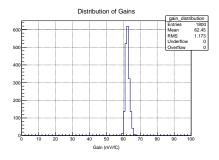

# Full Pixel Array Gain & ENC Distributions

$$<$$

Gain $> = 62 \,\mathrm{mV/fC}$

Spread =  $1.1 \,\mathrm{mV/fC}$

$$<$$

ENC $>=170e^{-}$

No sensor

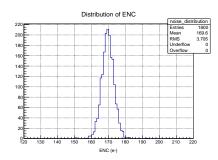

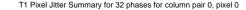

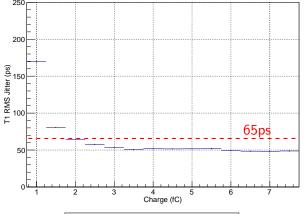

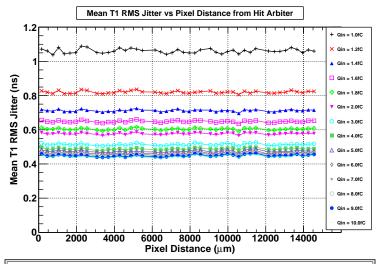

# Pixel Jitter: Test Output

#### nance Pixel Jitter:

# Pixel Jitter: Test Output

#### includes:

- Test pulse generation

- Test pulse distribution

- ► TX

- transmission line

- RX

- HitArbiter

- EoC Buffering

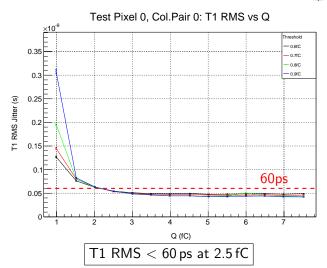

# **TDC** Performance

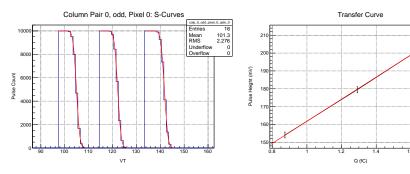

# TDC Test Input: Code Density Histograms

- ▶ 16 million random (unsynchronised) triggers

- bin content gives width estimate

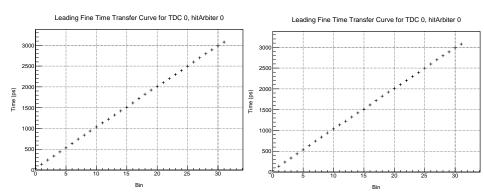

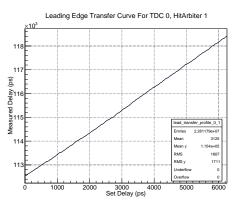

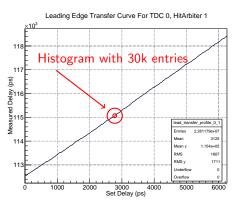

# TDC Test Input: Transfer Curves

▶ Bin widths give the transfer curve

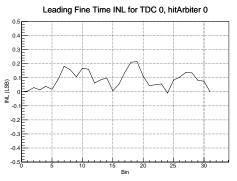

## TDC Test Input: INL

transfer curves give the INLs

matthew.noy@cern.ch

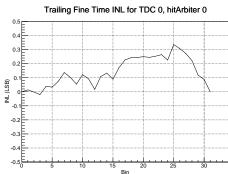

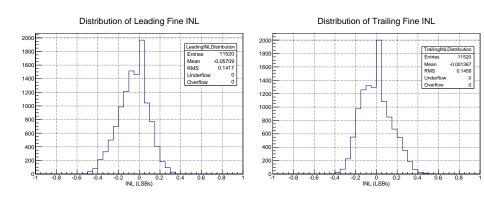

# Leading/Trailing INL: All TDC Channels

RMS INL  $\sim$  0.15 LSBs

## **TDC** Performance

TOT Transfer Curve For TDC 0, HitArbiter 1 14700 14650 14600 14450 3125 Mean y 1.455e+04 14400 RMS 14350 14300 1000 2000 3000 Set Delay (ps) 6000

- Pixel Matrix not involved in measurement

- ► Two clock periods (2\*3.125ns)

- ▶ Step: 10 ps

- ▶ 3.10<sup>4</sup> triggers/pt.

14700

## **TDC** Performance

14650

14600

14500

14500

14500

144500

144500

144500

144500

144500

144500

144500

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144600

144

TOT Transfer Curve For TDC 0, HitArbiter 1

- Pixel Matrix not involved in measurement

- ► Two clock periods (2\*3.125ns)

- ▶ Step: 10 ps

- $ightharpoonup 3.10^4$  triggers/pt.

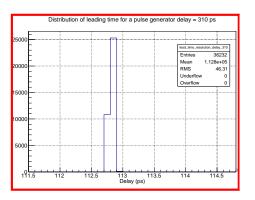

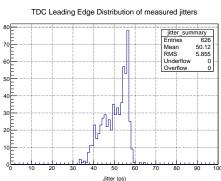

## **TDC** Resolution

- ▶ Resolution (Mode of the RMS dist.)  $\sim 58\,ps$

- ightharpoonup clock/pulse generator synchronisation contributes  $\sim 30\,ps$  RMS

- contribution from signal distribution in the chip unknown

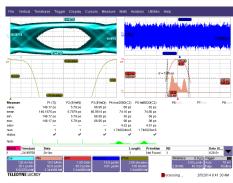

# Full Chain Performance

### Full Chain Behaviour

- trigger swept through full clk cycle

- ▶ 32 phases

- ► Step:100ps

- ▶ 10<sup>4</sup> triggers per phase

- No sensor present

$T_1(RMS) < 65 \, ps \, at \, 2.5 \, fC$

### Full Chain Behaviour

- trigger swept through full clk cycle

- ▶ 32 phases

- ► Step:100ps

- ▶ 10<sup>4</sup> triggers per phase

- No sensor present

$T_1(RMS) < 65 \, ps \, at \, 2.5 \, fC$

June 2014, Amsterdam

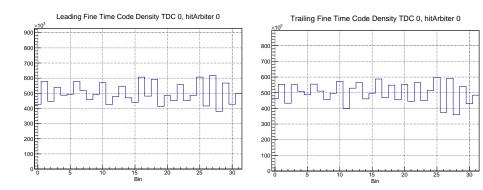

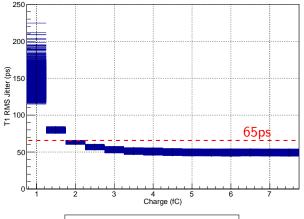

## TimeWalk-Corrected Time Resolution

- No sensor

- No sensor weighting

- Calibration done for every pixel

- $T_0 = T_1 K(Q) * [T_2 T_1]$

- ▶ Q = 1-7.5fC

"Whole Chip" Resolution  $\sim$  72 ps RMS

## Introduction to NA62 and the GigaTracke

## The TDCPix Chip Architecture

#### Measured Performance

Pixel Jitter: Test Output

TDC Performance

Full Chain Performance

- ▶ NA62: Ultra Rare Kaon decay measurement

- ightharpoonup huge beam rate ightharpoonup massive background reduction

- ► GTK Time Tagging <200ps per station

- ▶ NA62: Ultra Rare Kaon decay measurement

- lacktriangle huge beam rate ightarrow massive background reduction

- ► GTK Time Tagging <200ps per station

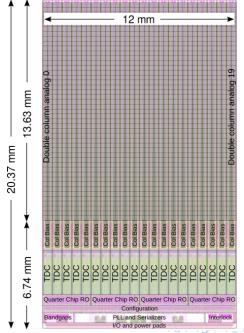

- TDCPix Architecture

- ▶ 1800 pixel End-of-Column chip

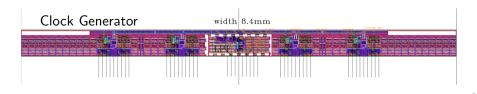

- ▶ 20mm x 12mm

- self-triggering architecture

- ▶ 4 x 3.2Gb/s on-chip serialisers

- ▶ NA62: Ultra Rare Kaon decay measurement

- lacktriangle huge beam rate ightarrow massive background reduction

- ► GTK Time Tagging <200ps per station

- ► TDCPix Architecture

- ▶ 1800 pixel End-of-Column chip

- ▶ 20mm x 12mm

- self-triggering architecture

- ► 4 x 3.2Gb/s on-chip serialisers

- ▶ TDCPix Performance is excellent

- First working silicon

- Pixel jitter < 60 ps RMS at 2.5fC</li>

- ► TDC gives <60 ps RMS time resolution

- ▶ Full chain works as expected < 65 ps RMS at 2.5fC

- Time Walk Correction Works as expected

- ▶ "Whole Chip" Resolution ~ 72 ps RMS

Thanks for your attention!!

# Backup Slides

# Demonstrator

## EoC Chip & Assembly

- ▶ What is the limit of the timing resolution attainable?

- Where does this limit come from?

# Summary of Results

# Transmission Line Uniformity $T_1$ RMS Jitter: ASIC

No systematic deterioration of signal quality with distance.

20

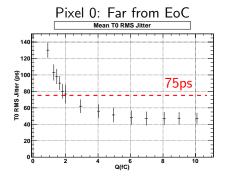

# RMS $T_0$ Jitter Vs Q: Assembly (@ 300V) + Laser

Pixel 44: Close to EoC

Mean TO RMS Jitter

140

120

75ps

75ps

- ► Full event time reconstruction done

- ► EoC activity doesn't feed through to the pixels

- detector bias = 300 V

- ightharpoonup average case  $\sim 75\,ps$  at  $2.4\,fC$

Q(fC)

## Beam Test: Time Resolution Vs Detector Bias

at  $300\,V$  average performance is  $175\,ps\,RMS$

M. Fiorini

## Time Resolution Limits

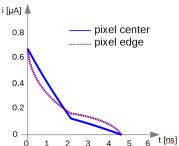

Sensor current pulses

- induced current pulse on electrode changes shape

- pre-amp output changes shape

- ► adds ~85ps

June 2014

## Time Resolution Limits

#### Sensor current pulses

- induced current pulse on electrode changes shape

- pre-amp output changes shape

- ► adds ~85ps

- Charge straggling also contributes

- inhomogeneities in charge deposition

- ▶ adds > 60ps

## Time Resolution Limits

#### Sensor current pulses

- induced current pulse on electrode changes shape

- pre-amp output changes shape

- ► adds ~85ps

- Charge straggling also contributes

- inhomogeneities in charge deposition

- ► adds > 60ps

- uncorrectable contributions for current sensor

### G. Aglieri Rinella

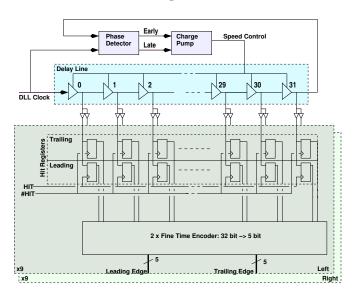

# Hit Arbiter

#### TDC: Hit Arbiter

- fully asynchronous

- timing information preserved

- ▶ 5 pixel + 1 test inputs

- ▶ hit signal

- ▶ 5 bit hit address + 5 bit pileup

- non-adjacent pixels connected to adjacent channels

# DLL & Hit Registers

## TDC: DLL & Fine Registers

## PLL & Serialisers

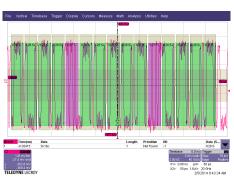

## Serial Outputs at 3.2Gb/s

- ► Idle words correct

- synchronisation works

- ► Total Jitter < 150 ps

- ► FPGA GTX recv. lock reliably

- ► DAQ works reliably

## Pixel Behaviour

## S-Curves $\rightarrow$ Pre-Amp Transfer Function

- Q<sub>injected</sub> adjusted for CAL DAC gain

- $\blacktriangleright$  Transfer fit  $\rightarrow$  discriminator offset and front end gain

- Polarity setup for a hole signal

- P-on-N sensor (baseline)

- "electron" polarity works too

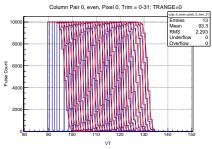

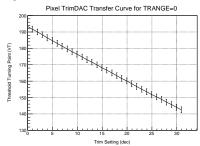

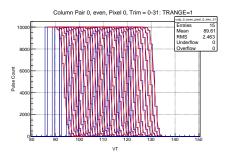

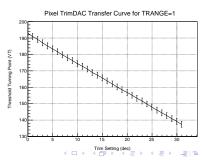

## Trim and TRANGE Functionality

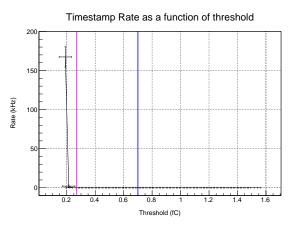

## How low will the threshold go?

- ► All pixels enabled (& trimmed)

- ▶ Pink: minimum threshold  $\sim 0.26 \, fC \, (1600 \mathrm{e^-})$

- ightharpoonup Blue: nomimal threshold 0.7 fC

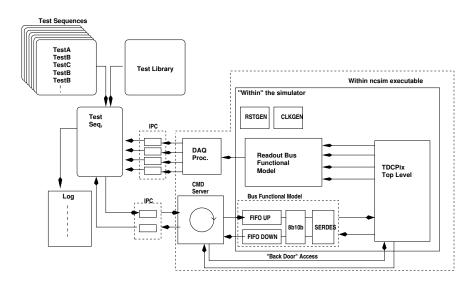

### Top Level Test Bench