### Upgrade of the LHCb VErtex LOcator

Kazu Akiba – Federal University of Rio de Janeiro On behalf of the VELO Upgrade Project

International Conference on Technology and Instrumentation in Particle Physics

2 – 6 June 2014 / Amsterdam, The Netherlands

"Instrumentation as enabler of Science"

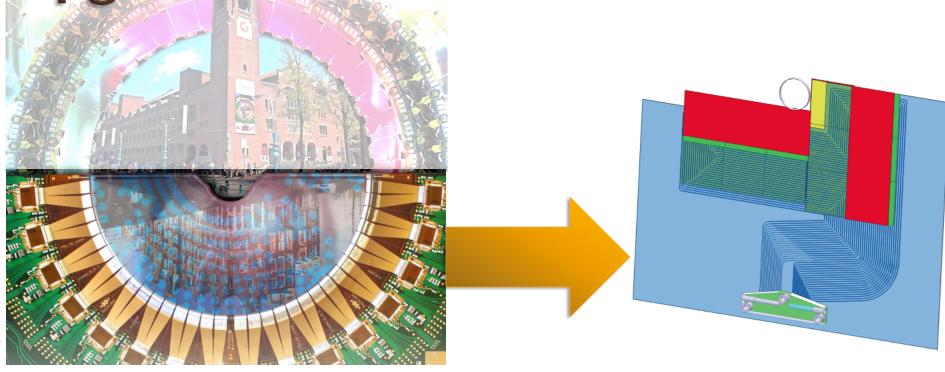

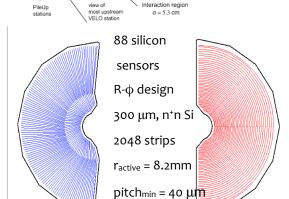

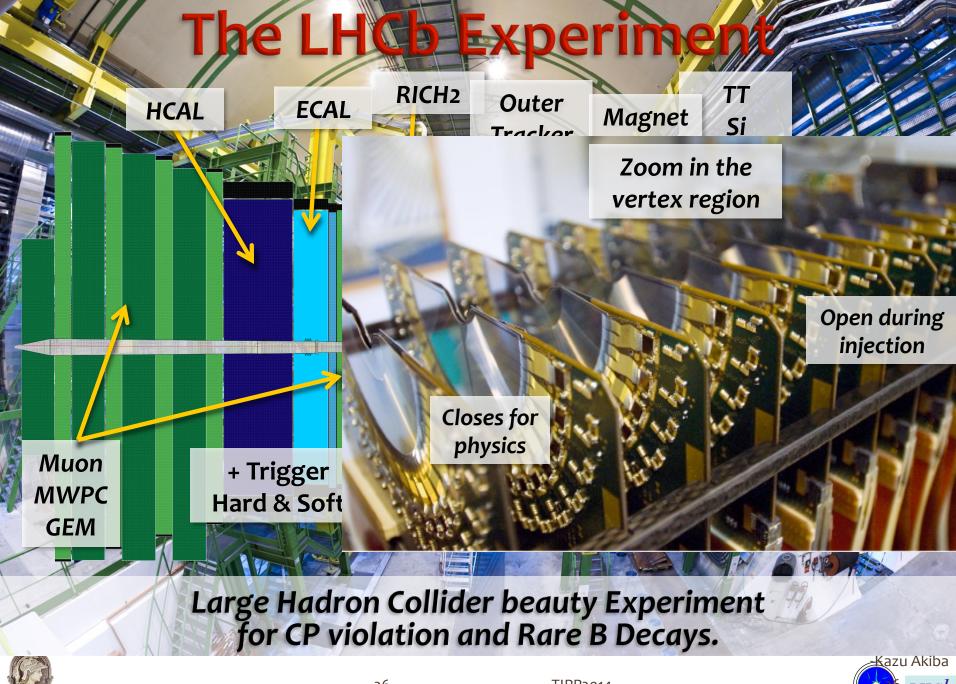

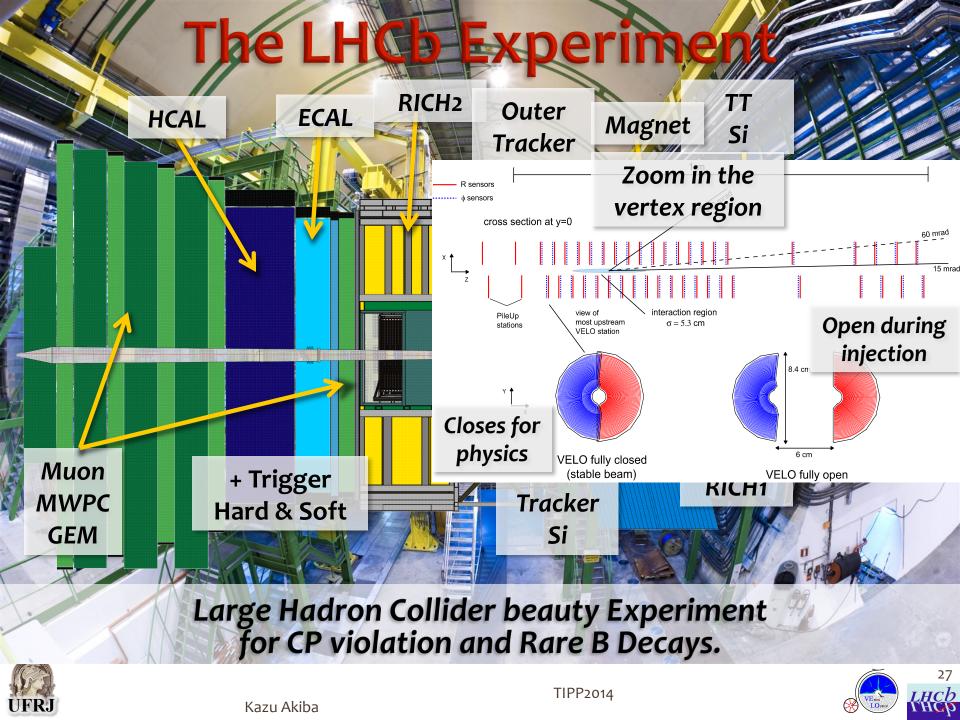

#### The current VELO

Moves away every fill and centers around the beam with self measured vertices

#### Poster:

The LHCb Vertex Locator - Performance and Radiation Damage https://indico.cern.ch/event/192695/ contribution/7

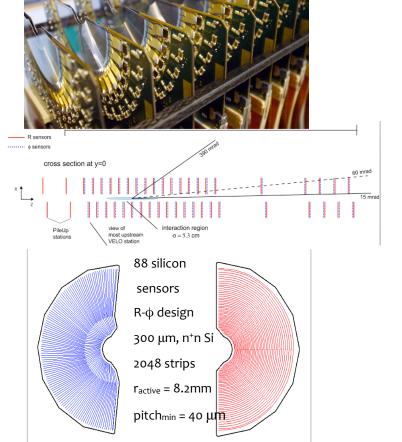

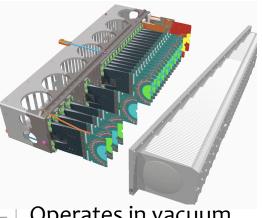

### The current VELO

Moves away every fill and centers around the beam with self measured vertices

Operates in vacuum

Separated from primary vacuum by thin RF foil with complex shape

-- Protection from beam pickup

#### Poster:

The LHCb Vertex Locator - Performance and Radiation Damage

https://indico.cern.ch/event/192695/

contribution/7

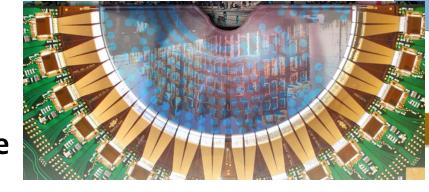

#### **The current VELO**

Moves away every fill and centers around the beam with self measured vertices

pitch<sub>min</sub> = 40 μm

Separated from primary vacuum by thin RF foil with complex shape

-- Protection from beam

Poster:

The LHCb Vertex Locator

- Performance and Radiation Damage https://indico.cern.ch/event/192695/ contribution/7

Kazu Akiba TIPP2014

pickup

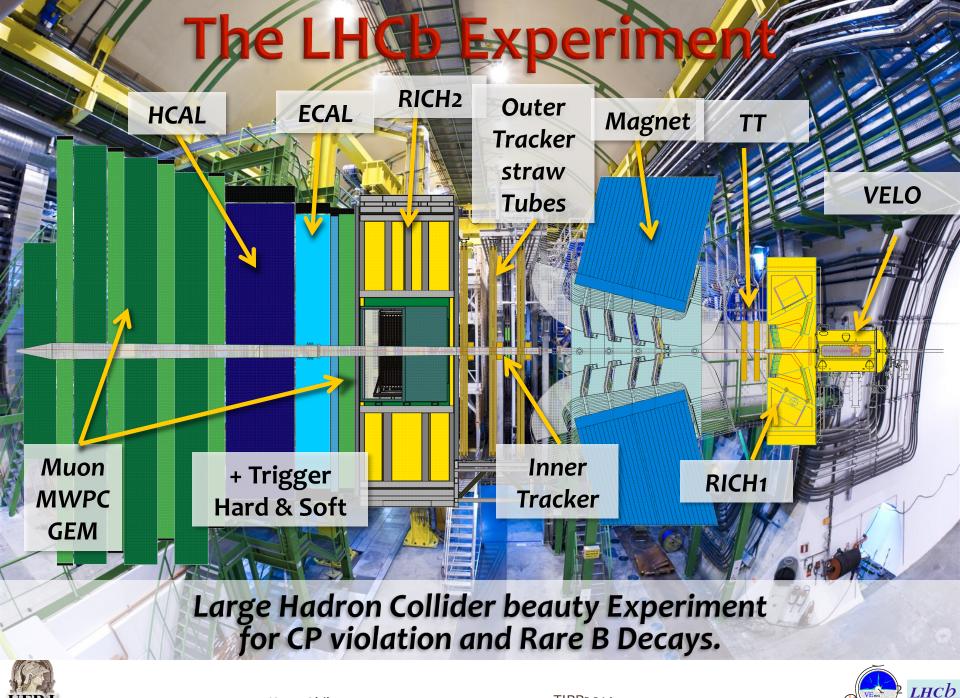

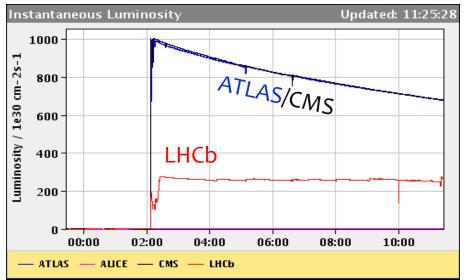

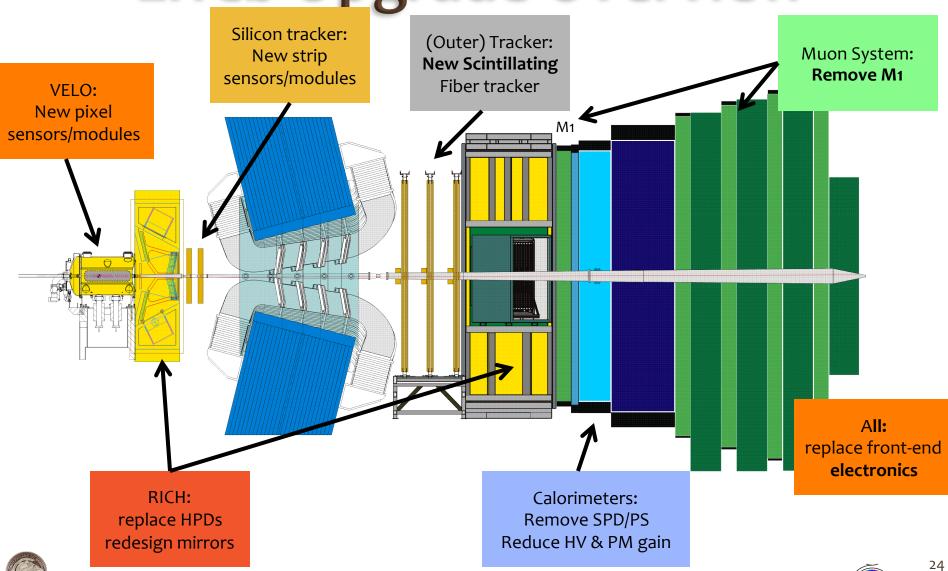

## Why upgrade LHCb

- Currently LHCb can cope with a inst. lumi. higher than design

- LHC still provides more than what we can handle:

- Current detector is limited due to 1 MHz readout.

- Higher Luminosities do not translate to higher physics: need smart Trigger.

- The upgrade is planned as a major Trigger/Readout upgrade:

- From 1 to 40 MHz full readout → Every collision read out to a computing farm

- Higher instantaneous Luminosity Higher occupancies/Faster Ageing

- Change all the front-end!

UFRJ

VEnn LHCK

### **Timeline**

Upgrade TDR module **UPGRADE HCb** production PGRADE Sensor Assembly production installation LS2 L\$1 25 ns 50 ns 25 ns Start-up 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 ... 20xx **LHCb** √s (TeV): 0.9 - 7 - 8 13 -14 **Upgrade**  $\mathcal{L}$  (cm<sup>-2</sup>s<sup>-1</sup>):  $10^{32}$  $3-4x10^{32}$  $4x10^{32}$  $20 - 30 \times 10^{32}$  $\int \mathcal{L}dt$  3 fb<sup>-1</sup> 8 fb<sup>-1</sup>  $> 50 \text{ fb}^{-1}$

Current upgrade plan still compatible with post LS3 ...

VEnes LHCL

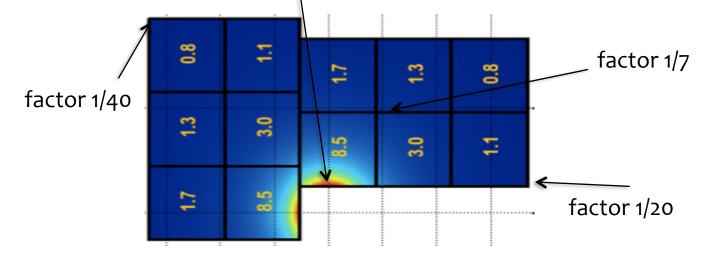

## Main challenges for the Velo Upgrade

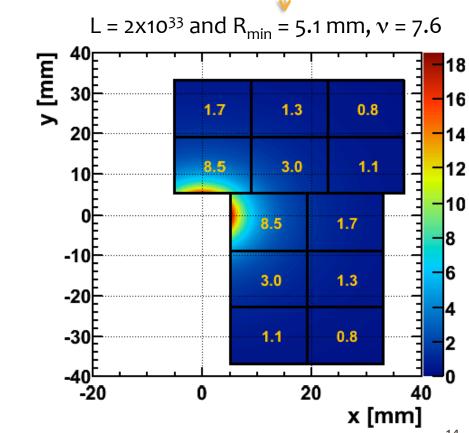

Non uniform Radiation exposure

8 x 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> @ tip, 0.2 x 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> @ outer edge

**HV** tolerance

1000V after 50 fb<sup>-1</sup>

Readout data rate

~33tracks/Event/module. (LHC: 40 MHz)

**Temperature operation**

-20 @ tip close to the beam

**ASIC** power consumption

3W/ASIC; up to 36 W/module;

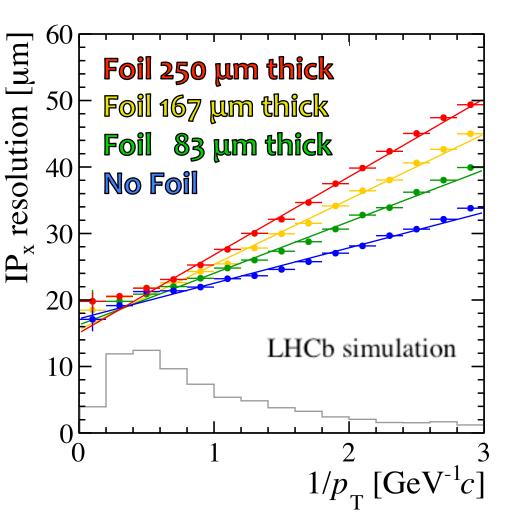

**Material budget**

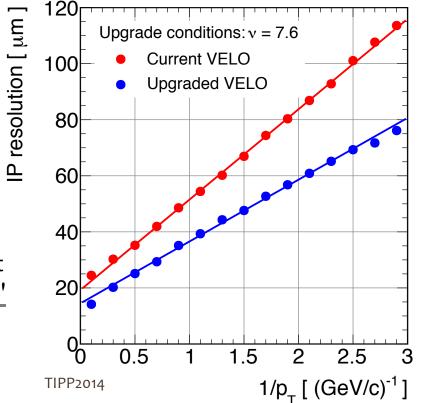

Good IP and tracking resolution currently:

- Proper time resolution ~ 50 fs

- IP resolution ~ 40 μm (p<sub>T</sub>=1GeV)

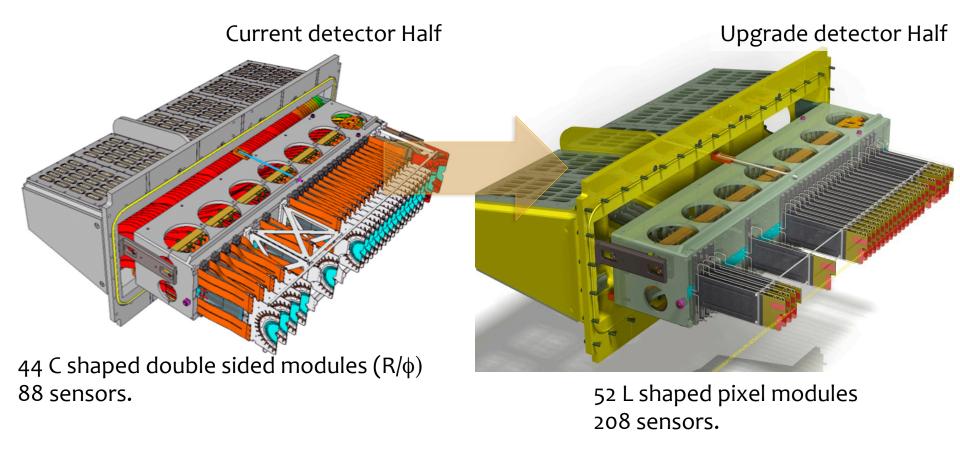

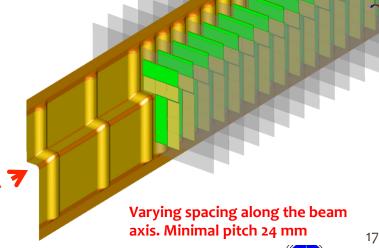

## **Upgrade Plan**

Keep vacuum and motion features.

## Changes to improve

- From strips to pixels: Planar Sensors 55x55 μm² pixel.

- Fast and robust pattern recognition.

- Cooling interface needs to come closer to the tip.

- Plan to use μ-channels etched in a silicon substrate. (see P. Rodriguez talk https://indico.cern.ch/event/192695/session/6/contribution/113)

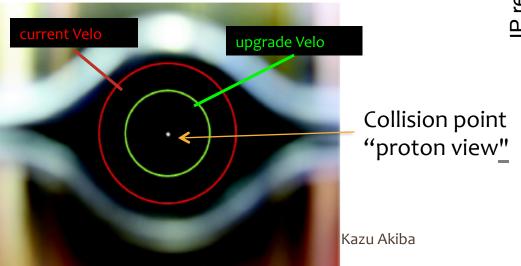

- First active element at 5.1 mm from beam (was 8.2 mm)

- New RF-box required.

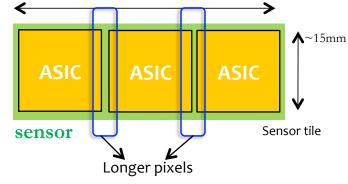

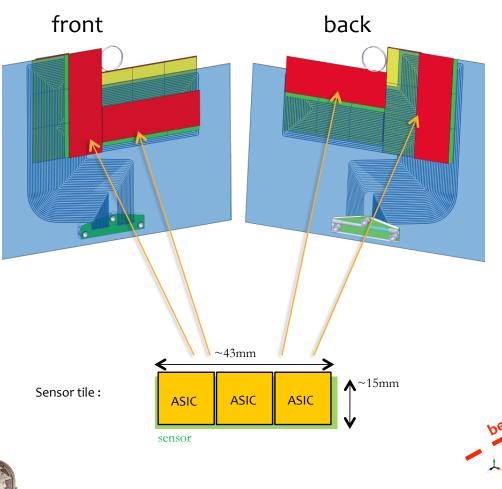

#### Silicon sensors

- Planar silicon, n-in-n or n-in-p under consideration

- Tile for 3 ASIC chips: ~ 43 x 14 mm, 200 μm thick

- 55x55 μm² pixels, elongated pixels at ASIC boundaries

- Non homogeneous irradiation sets constraints on guard ring design

- Tip close to beam:  $8 \times 10^{15} \, n_{eq}$ , far corner only at  $2 \times 10^{14} \, n_{eq}$

- guard ring width ~450 μm

- Bias of 1000V after 50 fb<sup>-1</sup>

~43mm

#### Silicon sensors

Focus on two vendors with proven track record in radiation hard and HV tolerant sensor designs:

VELO PIXEL Layout (Draft)

TS TS TS 3x1 PIXEL 3x1 PIXEL Single Single P(X 3x1 PIXEL 3×1 PIXEL Single PDX Single 3x1 PDEL 3x1 PIXEL Single 3x1 PIXEL 3x1 PDXEL Single PIX 3x1 PIXEL 3x1 PIXEL Single PIX 3x1 PIXEL 3x1 PDXEL 3x1 PDEL 3x1 PIXEL

n-in-p, 200 um thick

450 um guard ring

3x1 and single-ASIC sensors

Micron

**HPK**

n-in-n or n-in-p, 150/200 um

Baseline of 450 um guard ring

Possibility of reduced width guard rings (250um) and overlapping guard rings on backside in n-in-n case

> Irradiation and test beam program to validate Sensor and ASIC tech at high rates.

--- This year!

#### TimePix3 chips

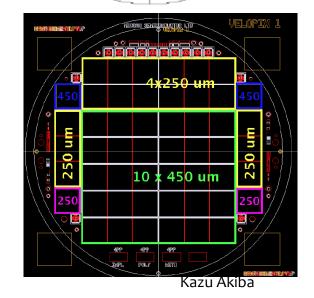

#### **VELOPIX ASIC**

Preamp Out

Clk (40MHz)

Disc Out

- MediPix → TimePix → Timepix3 → VELOPix

- VeloPix designed by CERN and Nikhef

- Square matrix of 256 x 256.

- Technology resistant to required ~400 MRad.

- Key features

- Data driven readout:

Each hit time-stamped,

sent off chip immediately

- Fast front-end: time walk < 25 ns</p>

- Bunch crossing time stamping9 bit

- SEU protection

- VeloPix output hit-rate = ~10 x TimePix3 rate

- Binary readout but optional ADC (slow) for calibration

- Chips will be thinned to 200 μm: minimize material

## VeloPix challenges

- Average # particles / chip / event

- average (peak) rate: multiply by 26.8 (40) MHz

- Hottest chip →230 (320) Mtracks/s ~ 600 (900) Mhits/s per chip

- grouping of pixel hits

2x4 super pixels → 30 % data reduction

- increase output bandwidth

- optimize buffering

- Output bandwidth of (hottest) VeloPix:

- Average: 13 Gbit/s; peak: 20 Gbit/s

- 4 links at ~ 5 Gbit/s

- for first submission summer 2014

- Production quantity chips end 2015

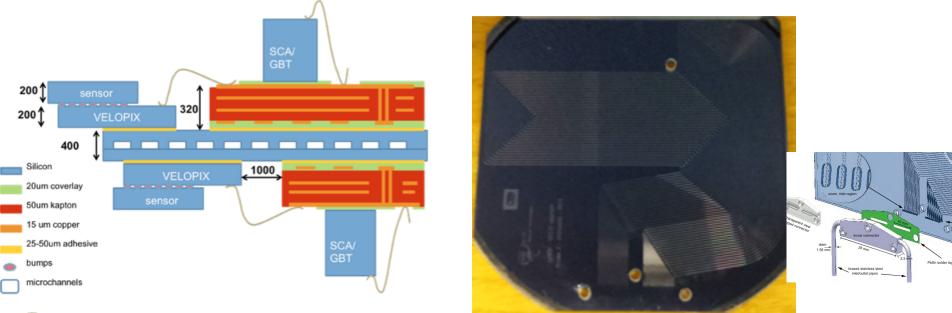

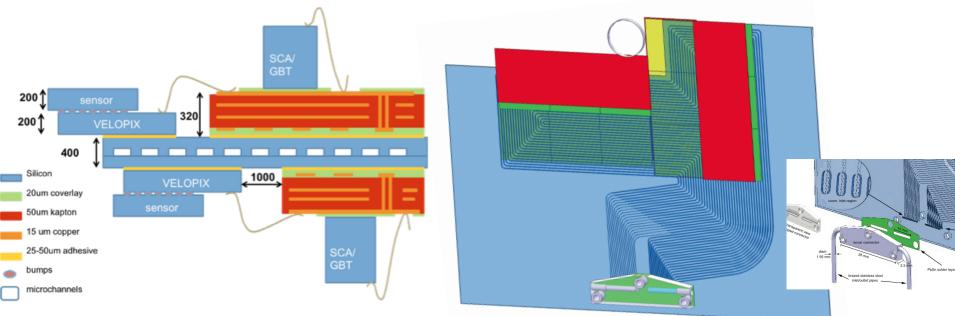

## Cooling: micro channel substrate

- Power consumption can go up to ~45 W/module.

- Keep the sensors at < -20 °C to minimize the effects of radiation damage, and to avoid thermal runaway

- Novel method: evaporate CO₂ via micro-channels etched in Si substrate

Same Thermal Expansion Coefficient (CTE)

VE<sub>ns</sub> LH

## Cooling: micro channel substrate

- Power consumption can go up to ~45 W/module.

- Keep the sensors at < -20 °C to minimize the effects of radiation damage, and to avoid thermal runaway

- Novel method: evaporate CO₂ via micro-channels etched in Si substrate

Same Thermal Expansion Coefficient (CTE)

## L-shape Pixel Modules

- A 'module' is made of 4 sensor tiles.

- active area ~100% (except small gaps)

- Closest pixel is at 5.1 mm from the beam center

Kazu Akiba

**TIPP2014**

LHCb

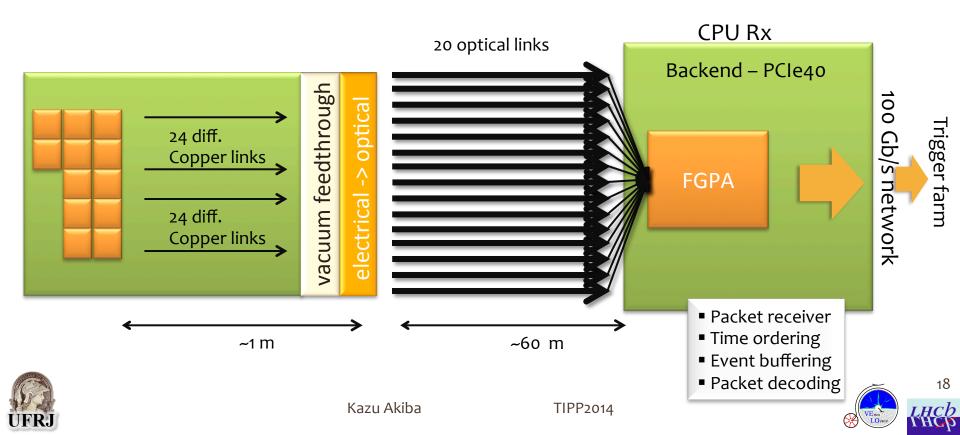

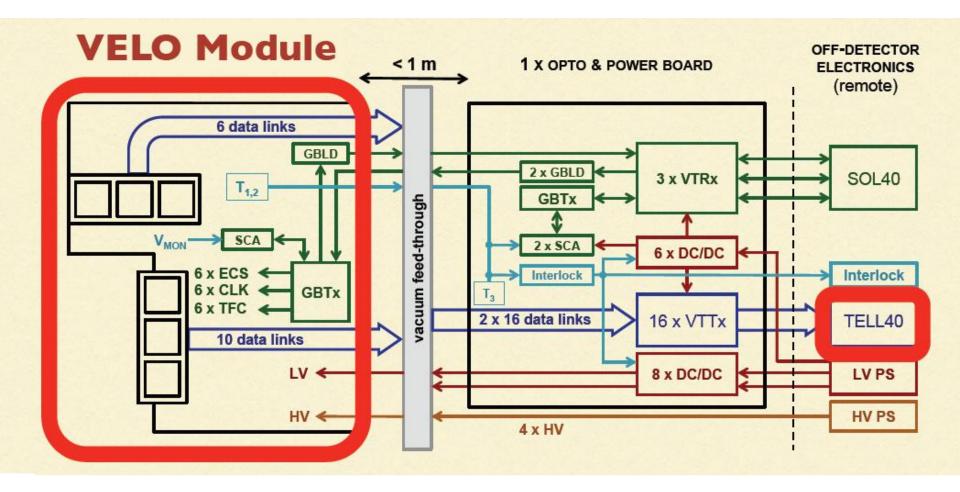

### Data acquisition overview

- LHCb common DAQ boards (PCIE40)

- 48 copper links from chips.

- Hotter chips demand higher speeds

- Electrical to optical conversion outside of vacuum tank

- 20 Optical links ~5 Gbit/s each

- 1 FPGA to time order events of 1 module

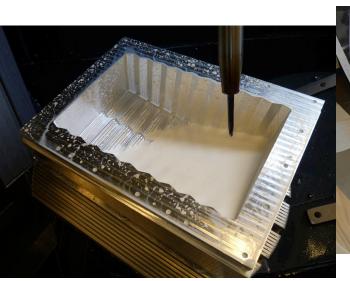

## **Upgrade RF Foil**

- Requirements

- Vacuum tight (< 10<sup>-9</sup> mbar l/s)

- Radiation hard

- Low Mass

- Good electrical conductivity

- Thermally stable and conductive

- Material and fabrication:

- •Aluminium (AlMgMn): 200-350 µm thickness:

- •By 5-axis milling of a single homogeneous block

- Chemical etching

**Upgrade RF Foil**

## Summary

- We plan to install a fully upgraded detector in the LS2/2018

- With a 40 MHz "triggerless" readout

- Run @ L =  $2 \times 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup> ( $5 \times 10^{33}$  cm<sup></sup>

- Velo subdetector will consist planar silicon pixel sensors with 55 x 55 μm² pitch

- Get closer to the collision point

- Minimize the material

- New ASIC VELOPix with 20 Gbit/s output bandwidth

- Evaporative CO<sub>2</sub> cooling in Silicon with a micro-channel substrate as interface

- 300 μm thick RF-box milled from solid block of Aluminum

- Developments for the upgrade going well and on schedule

The LHCb VELO upgrade is a very challenging project with many new techniques

VE res LHCb

# Back up

#### **Electronics overview**

LHCb Upgrade Overview

LHCb

### **VeloPix ASIC**

| Specification                | Timepix3                 | VeloPix           |

|------------------------------|--------------------------|-------------------|

| pixel dimension              | $55x55 \ \mu m^2$        | $55x55 \ \mu m^2$ |

| matrix size                  | 256x256                  | 256x256           |

| timewalk                     | < 25  ns                 | < 25  ns          |

| Time over Threshold range    | 10 bit                   | 4 bit             |

| leakage current compensation | > 20 nA                  | > 20 nA           |

| (per pixel)                  |                          |                   |

| Time stamp resolution        | 1.6 ns                   | 25 ns             |

| Time stamp range             | 18 bit                   | 12 bit            |

| sustainable hit rate         | 40 MHits/s               | > 600  MHits/s    |

| output bandwidth             | $2.5 \; \mathrm{Gbit/s}$ | > 13.6  Gbit/s    |

| power consumption per chip   | < 2 Watts                | < 3 Watts         |

| radiation hardness           | no spec.                 | > 400 MRad        |

| single event upset robust    | no                       | yes               |

## Main challenges for the Velo Upgrade

- Completely new front-end electronics and sensor

- Fast analogue pulse, Ultra fast read out readout every bunch crossing.

- High radiation hardness of ~ 400 MRad 8 x 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

- Very high data rate

- Major changes to front-end back-end electronics and data transport

- Improve the cooling performance

- Thermal Runaway risk at inner most region

- New cooling interface design.

- Improve the physics performance... currently:

- Proper time resolution ~ 50 fs

- IP resolution ~ 13 + 25/pT μm

VE<sub>us</sub> LHCb

Upgrade of the LHCb VErtex LOcator

**QUICK Current detector overview**

**Upgrade motivation**

**VELO Upgrade plan**

**Upgrade R&D**

Sensors

**ASIC**

Cooling

Infrastructure

**Summary**

International Conference on Technology and Instrumentation in Particle Physics

2 – 6 June 2014 / Amsterdam, The Netherlands

"Instrumentation as enabler of Science"