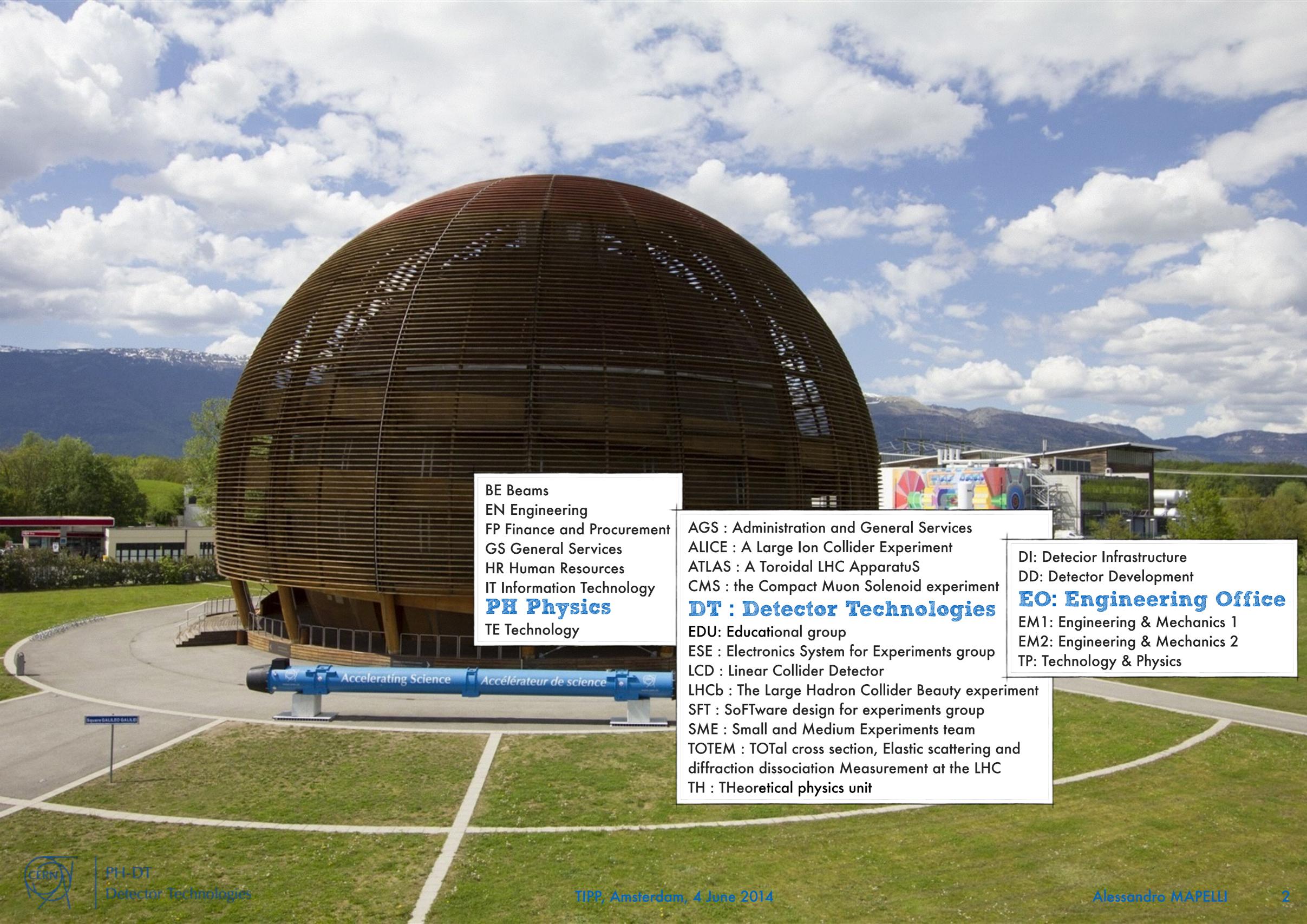

# Microfabrication Activities in the Engineering Office of the PH-DT Group at CERN

Alessandro MAPELLI

Diego ALVAREZ FEITO, Andrea CATINACCIO,

Jordan DEGRANGE, Cecilia ROSSI,

Giulia ROMAGNOLI, Pietro MAODDI

## microfinginecing

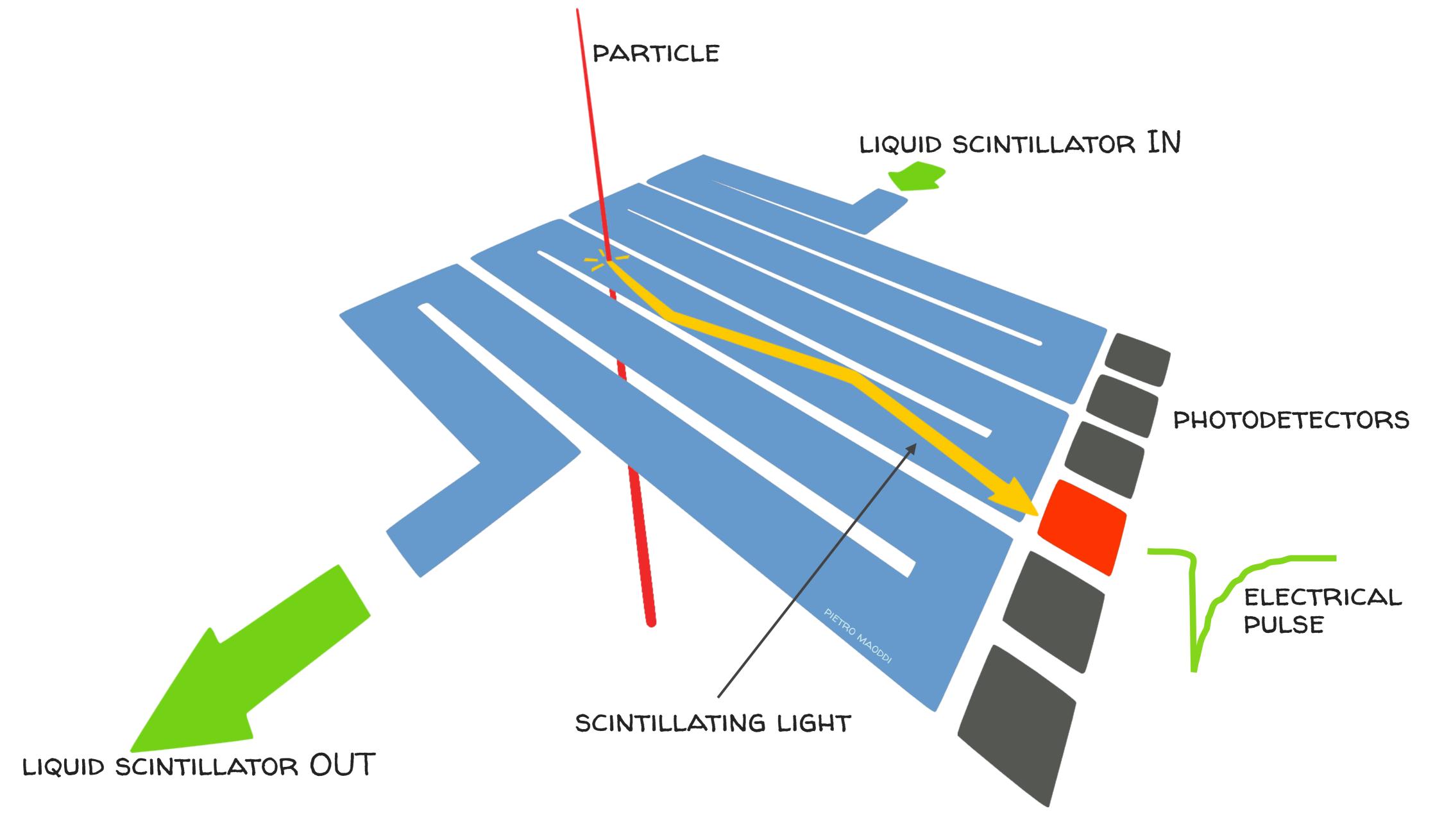

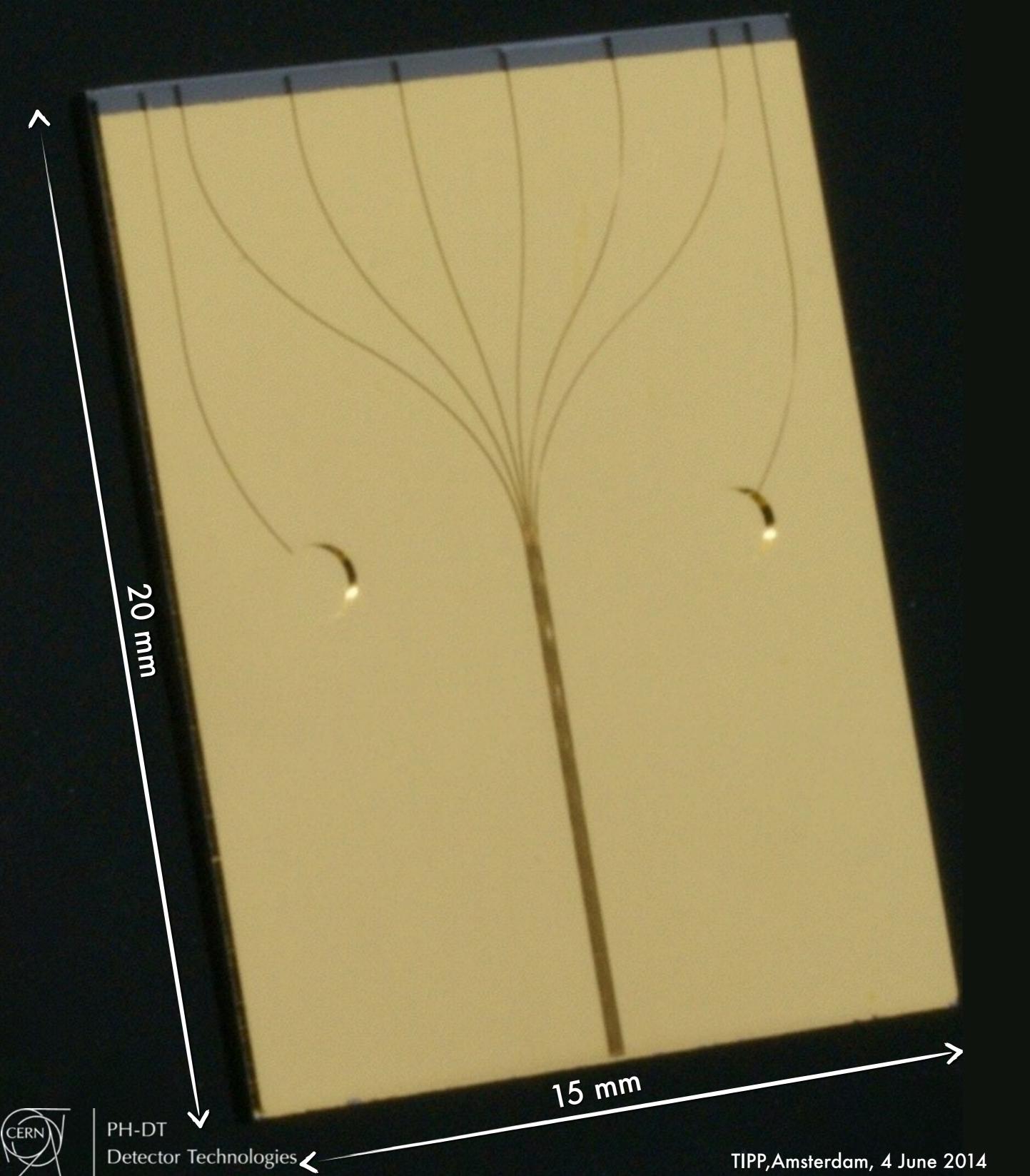

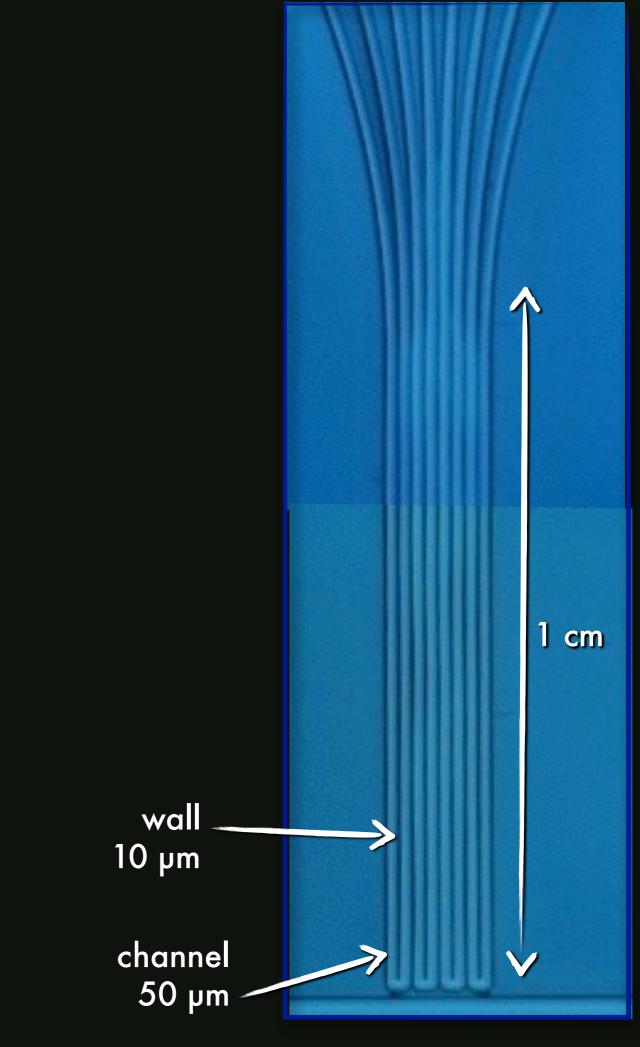

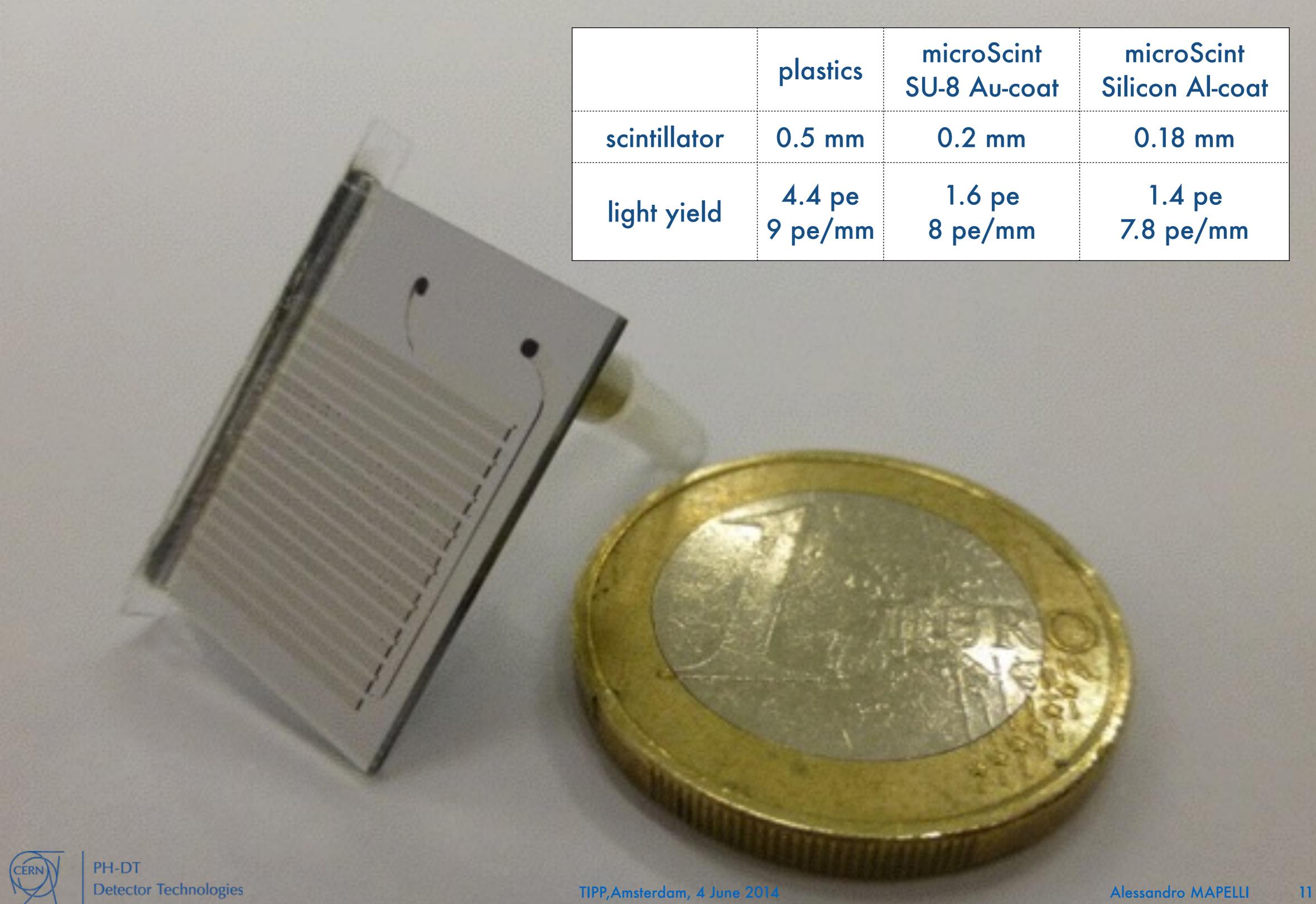

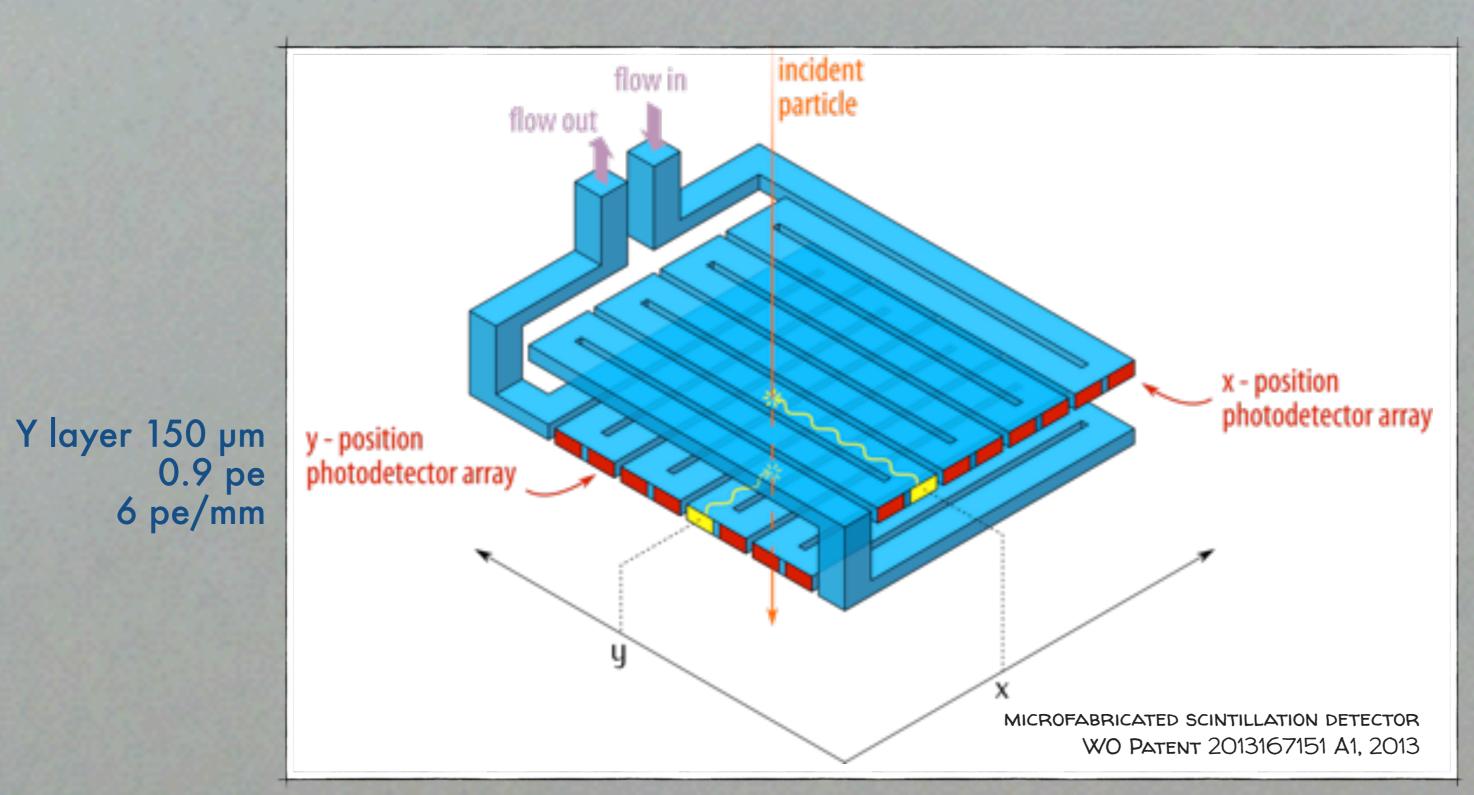

#### «microScint

development of a microfluidic scintillation detector

#### microCool

• implementation of microfabricated on-detector cooling systems

#### microHell

• study of heat transfer of superfluid Hell in microfluidic networks

### microSystems engineering

- microFabrication

- integration of microfabricated devices in detectors

- development of a methodology to estimate the mechanical performance of (silicon) µ-devices

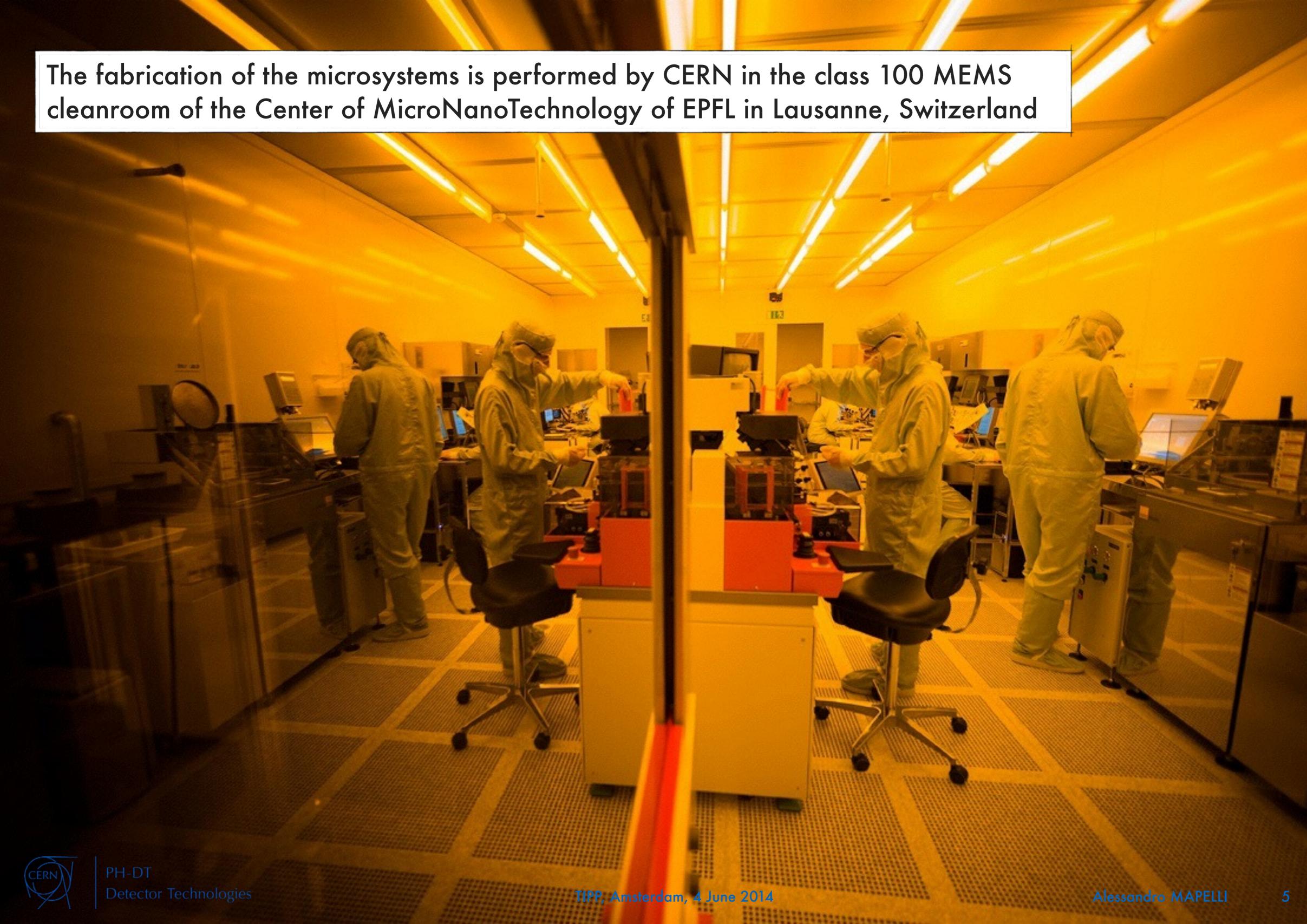

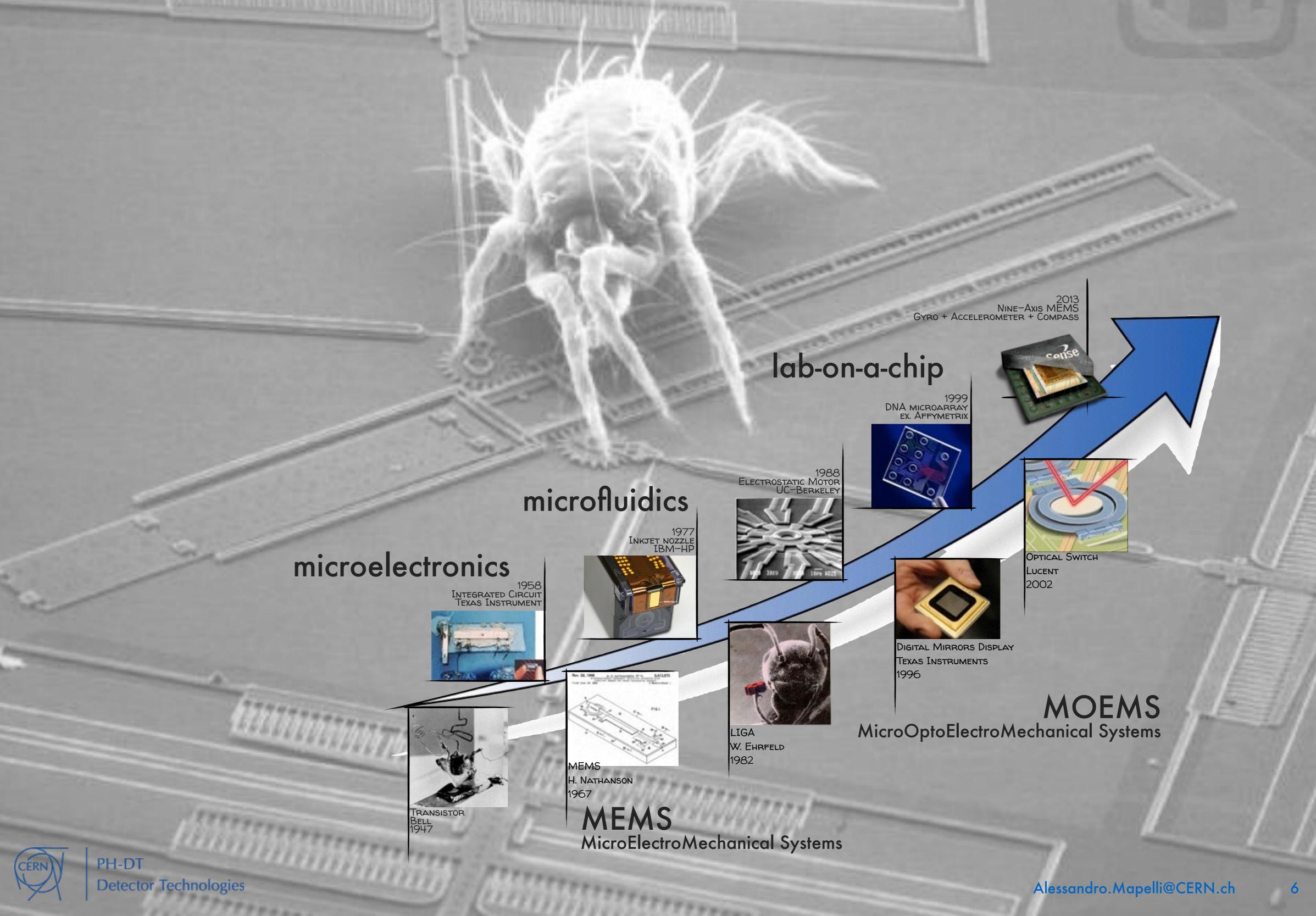

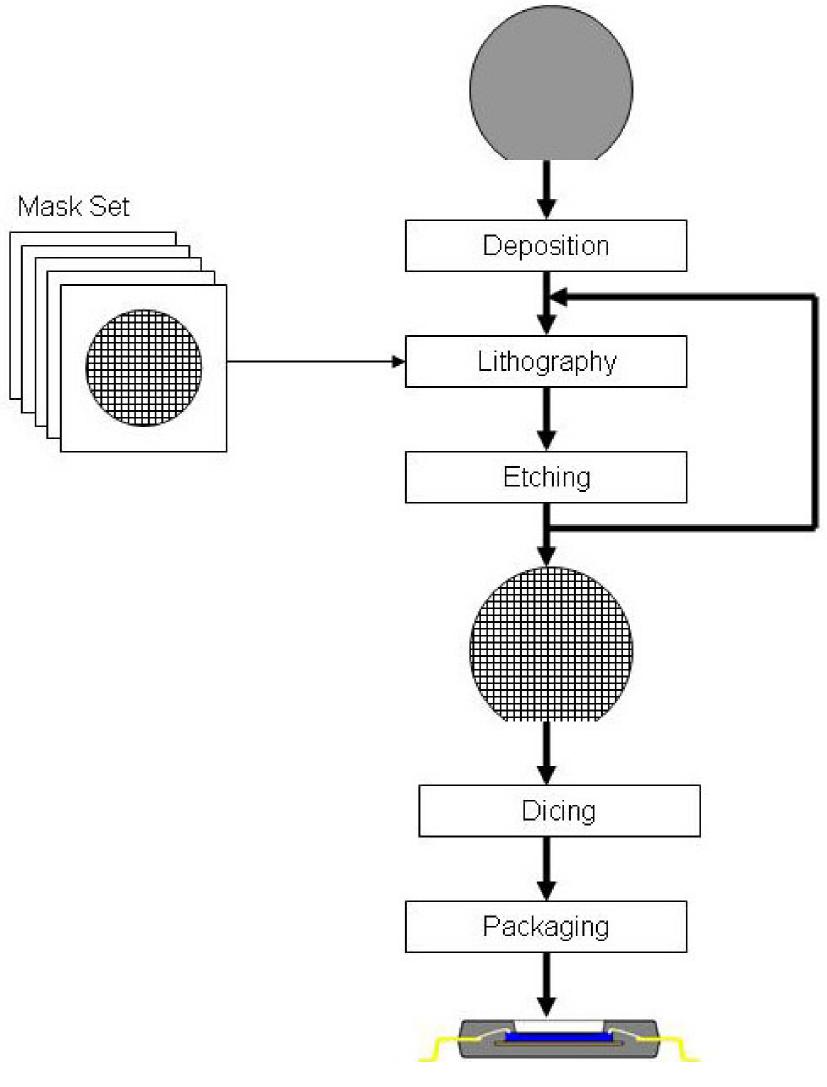

## microfabrication techniques

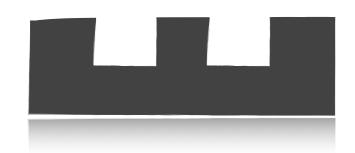

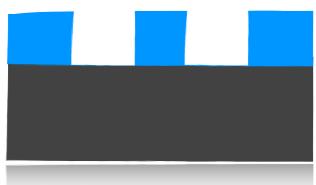

#### Bulk micromachining

mechanical structures are etched in the substrate

#### Surface micromachining

layers of material are deposited on the substrate, patterned and selectively removed

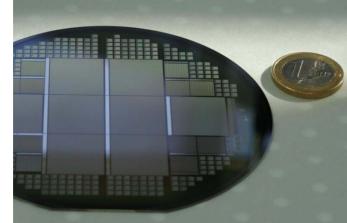

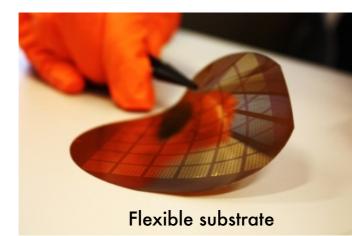

#### Substrates

round wafers 3", 4", 6", 8", 12"...

Silicon, SOI, glass, GaAs, SiC, Ge, polymers...

http://www.electronicproductsktn.org.uk, 2007

###

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

SILICON SUBSTRATE

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

PHOTORESIST SPIN COATING

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

MASK ALIGNMENT

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

UV EXPOSURE

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

UV EXPOSURE

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

DEVELOPMENT

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

METALLIZATION

SINGLE PHOTOLITHOGRAPHY STEP TO DEFINE THE CHANNELS (SURFACE MICROMACHINING)

DICING

X layer 150 µm 1.0 pe 6.7 pe/mm

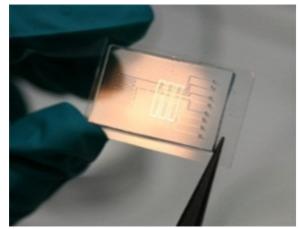

## coming up with microscint

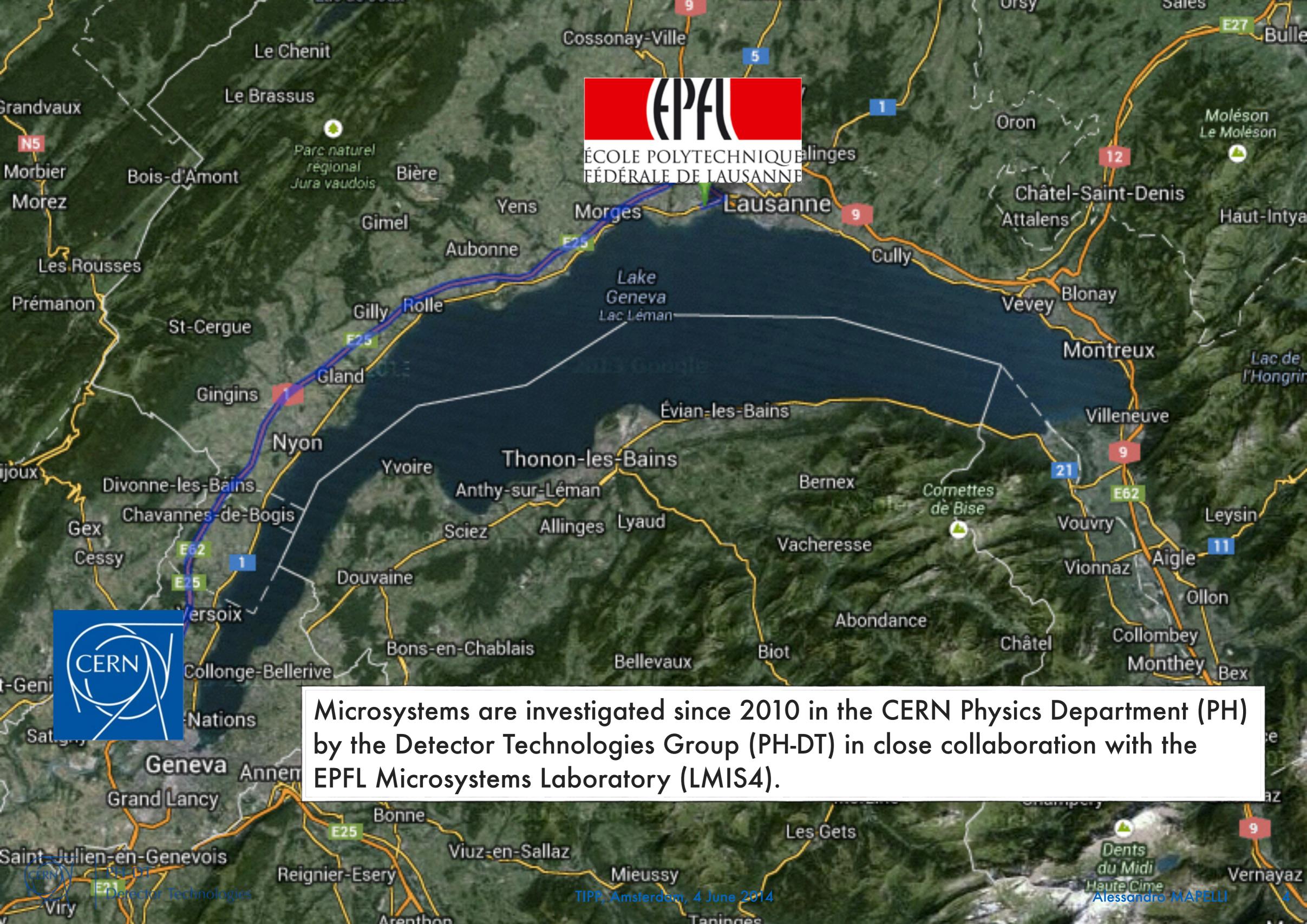

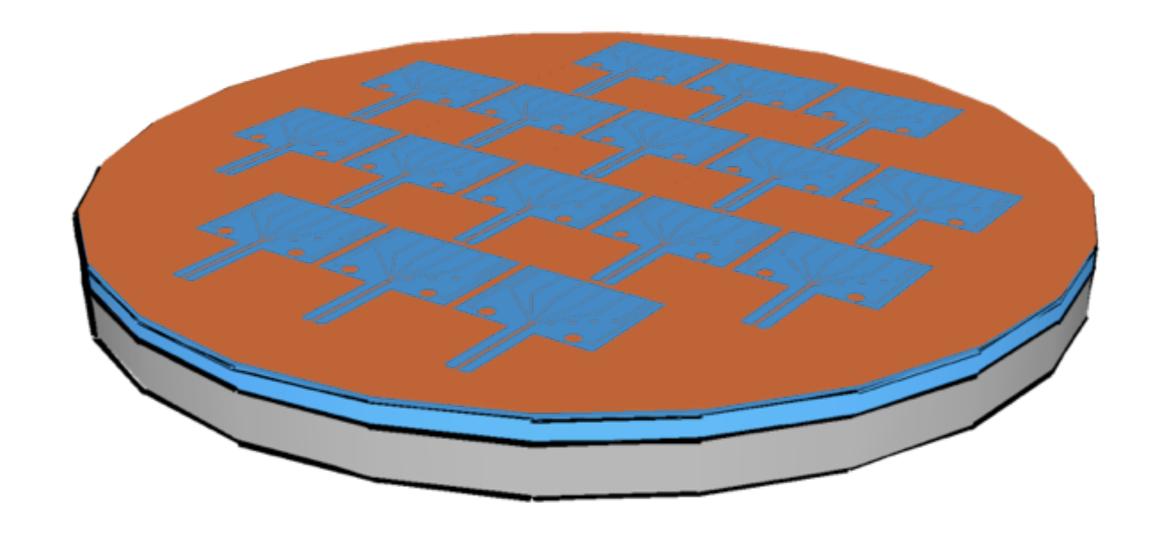

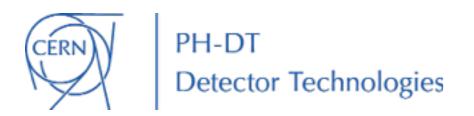

- Double layer (XY) microfluidic device

- EPFL Microsystems Laboratory (<a href="mailto:lmis4.epfl.ch">lmis4.epfl.ch</a>)

- SiPM readout

- INFN, Roma

- Integrating aSi:H photodiodes in the microfluidic channels

- EPFL PVLAB (pvlab.epfl.ch)

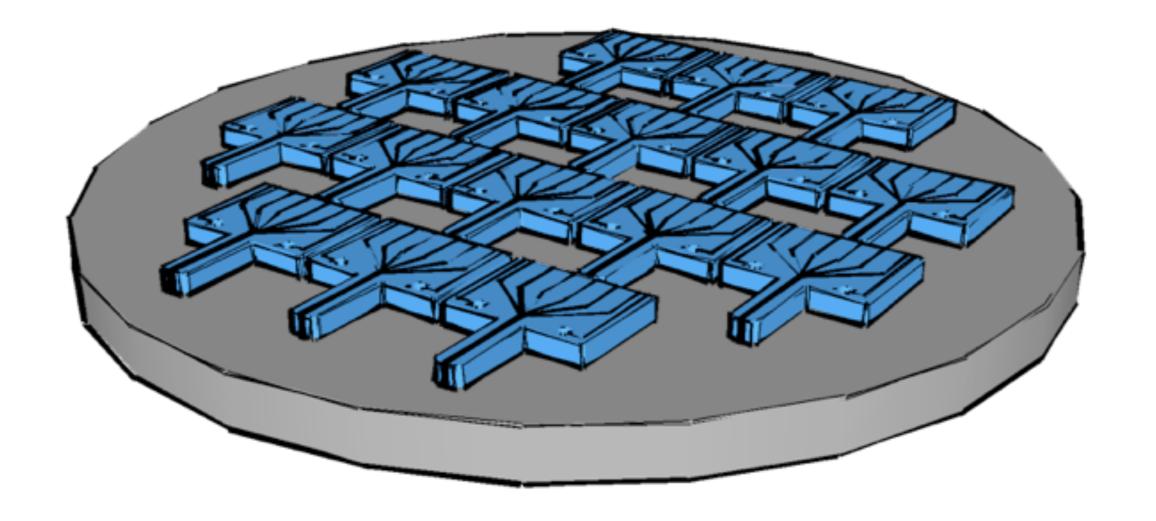

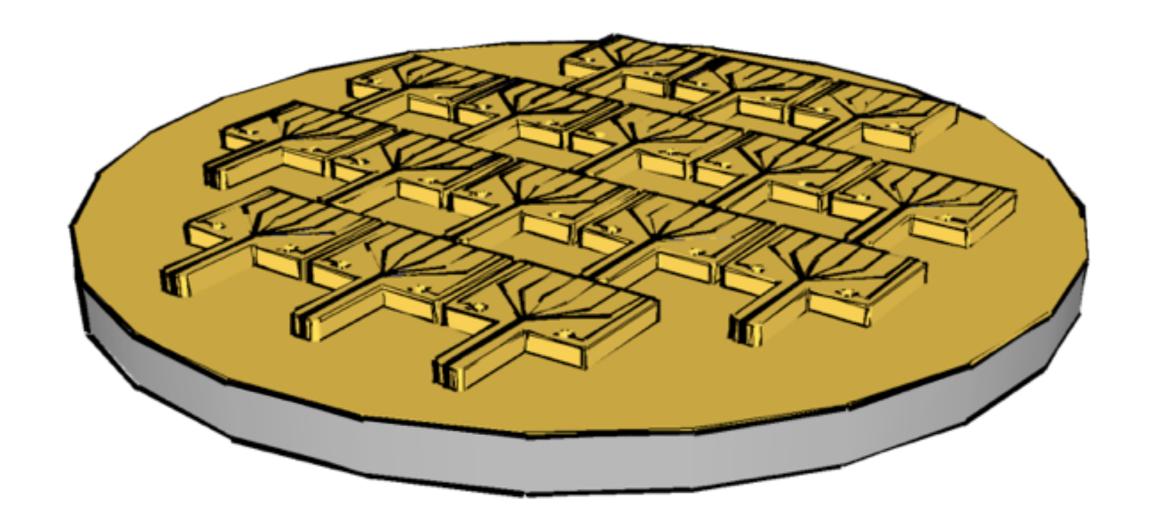

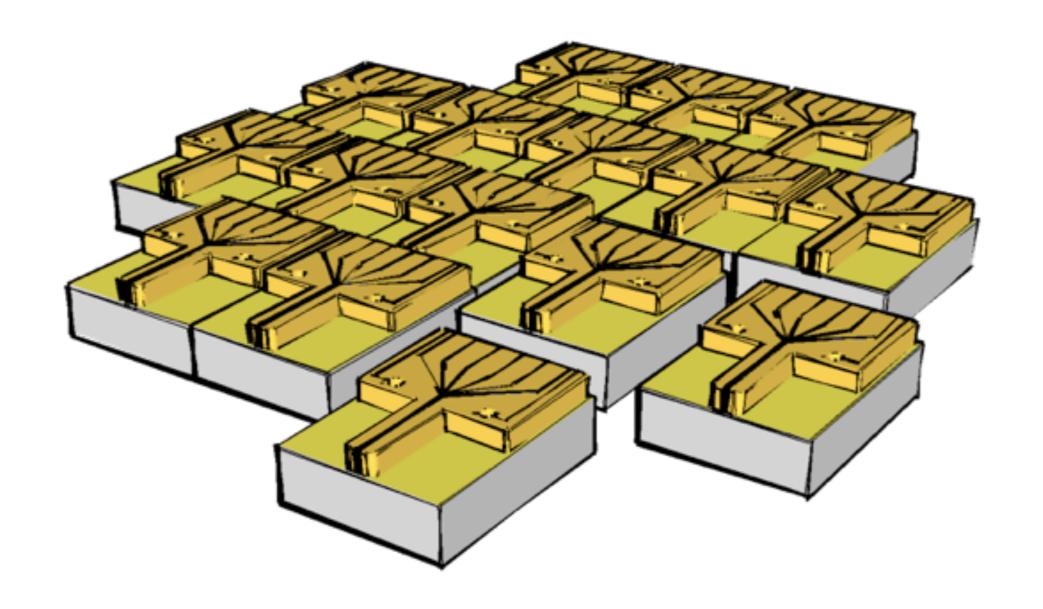

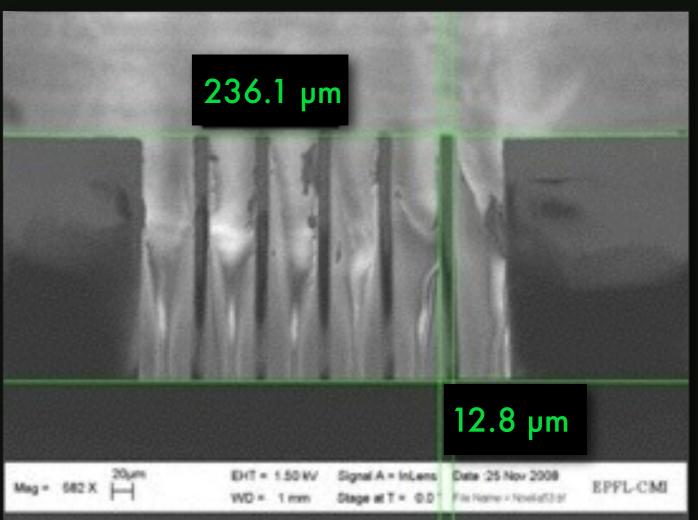

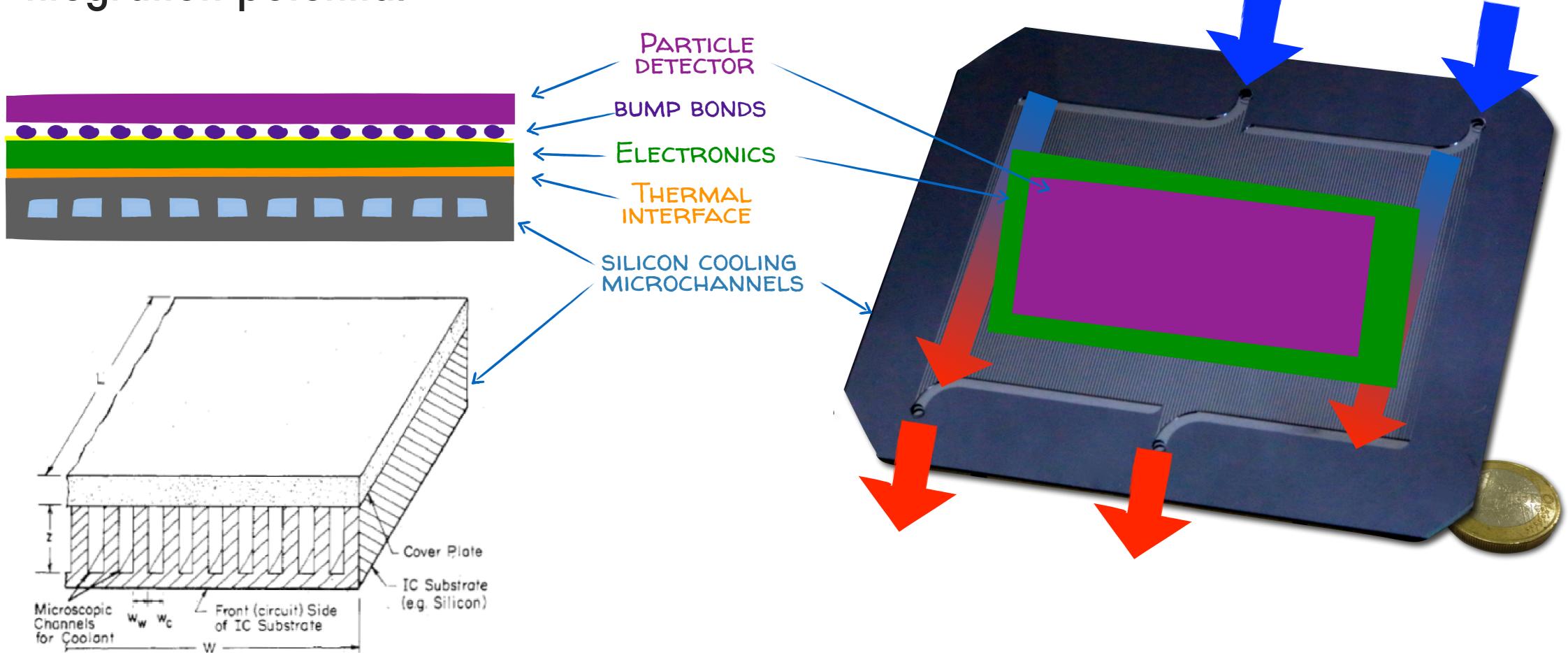

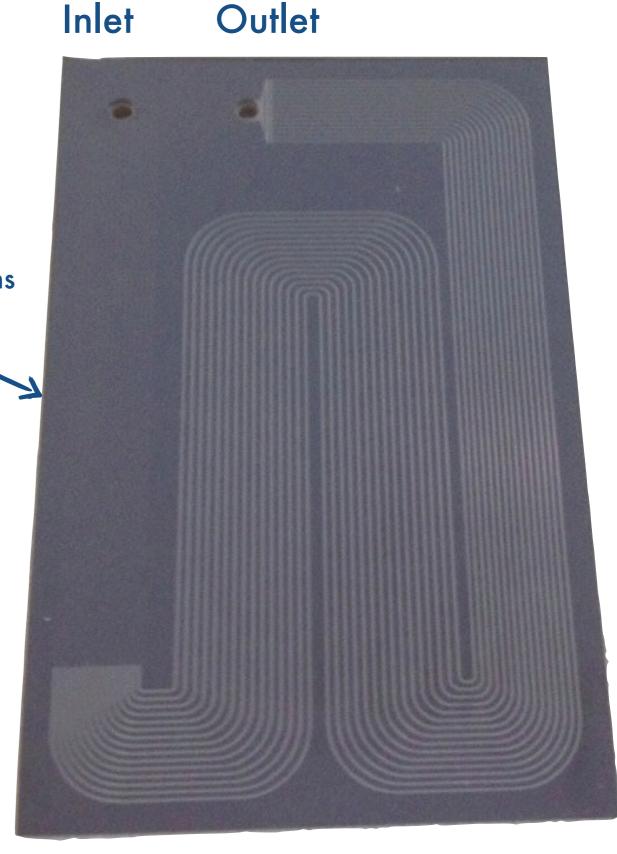

### silicon microchannel cooling

- No CTE mismatch

- Low material budget

- Active/distributed cooling

Integration potential

Great effort required for microfluidic connections in HEP!!

D.B. Tuckerman and R.F.W. Pease, IEEE Elec. Dev. Letters, Vol. 2, 5, 1981

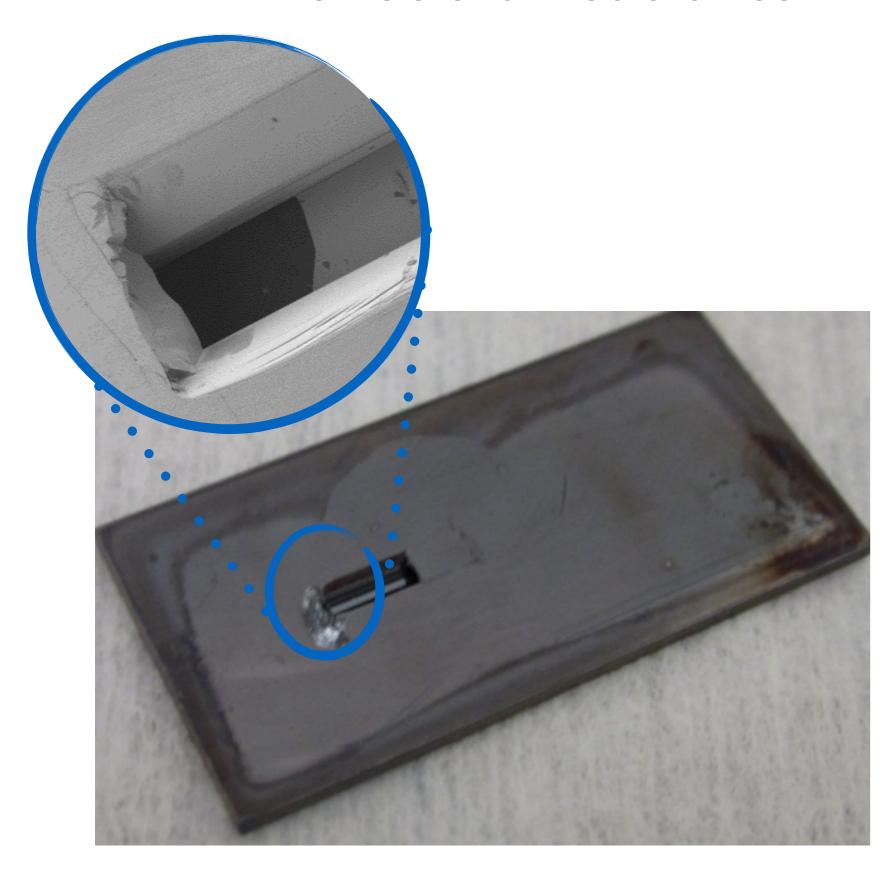

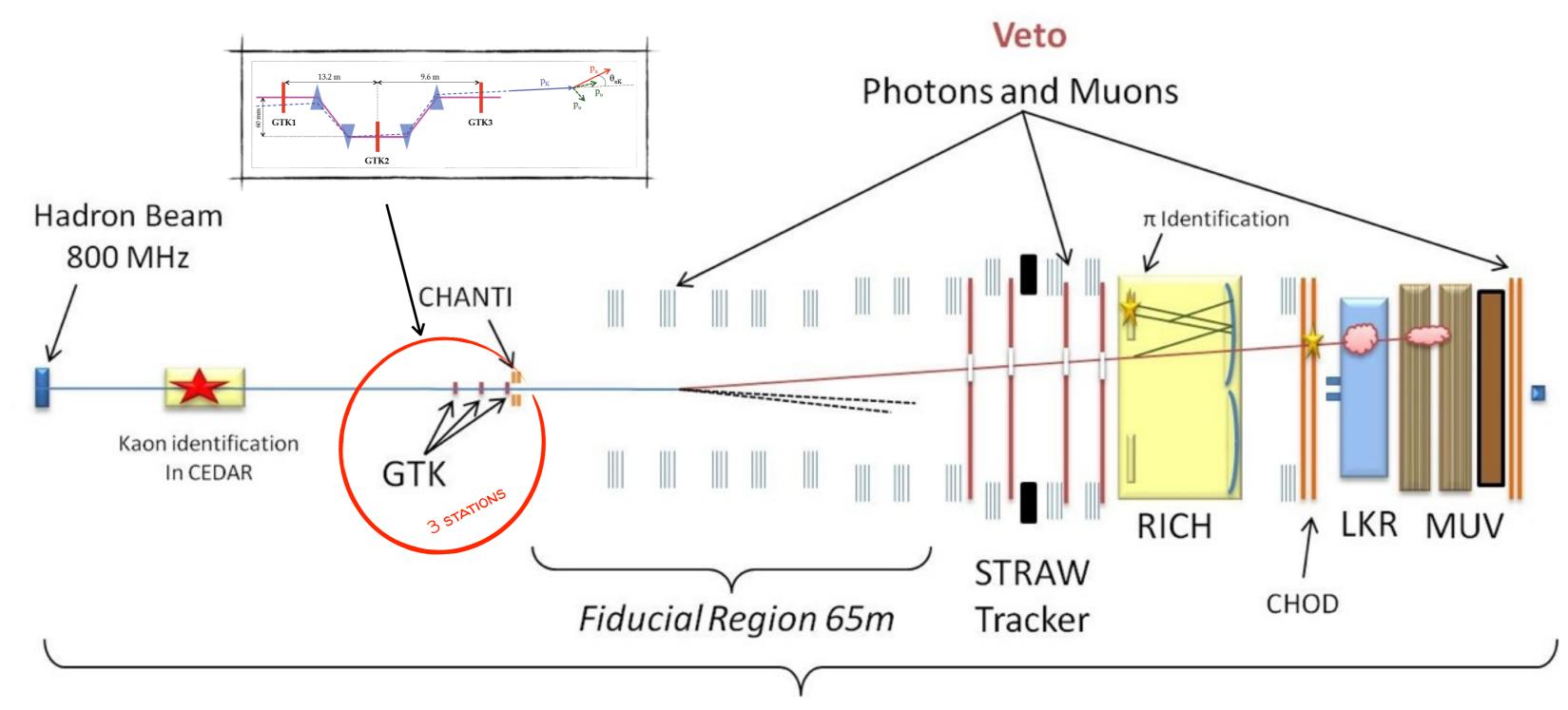

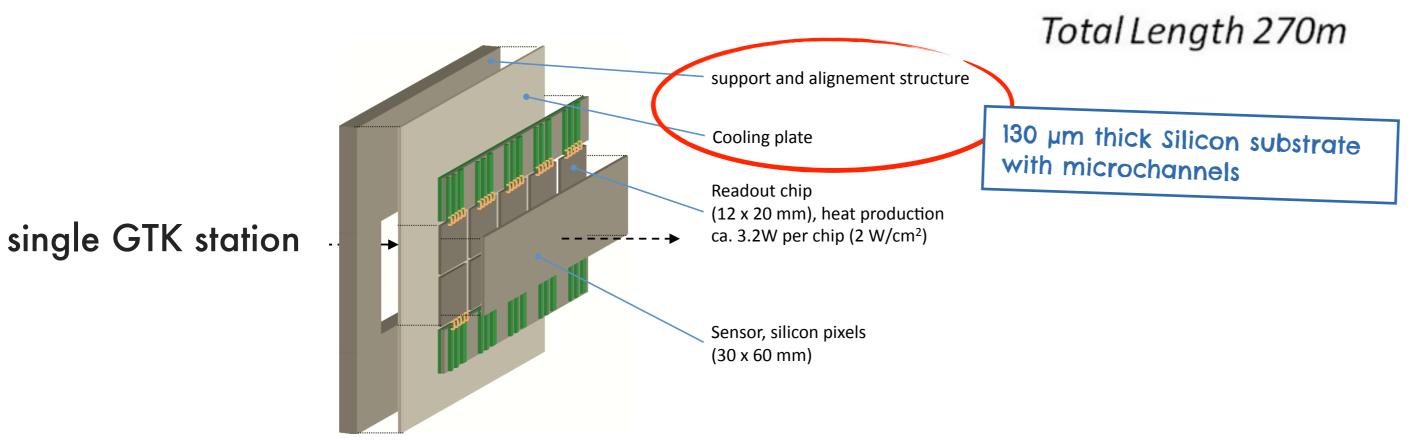

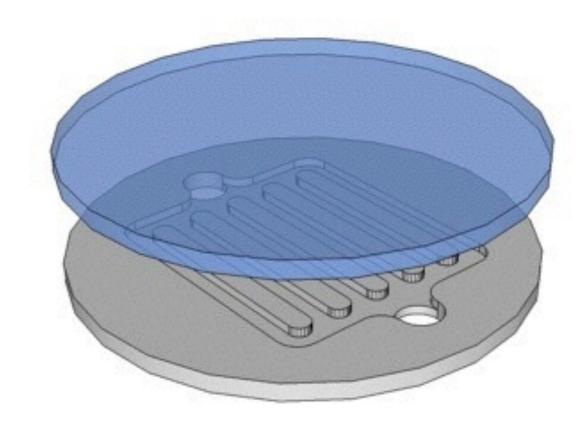

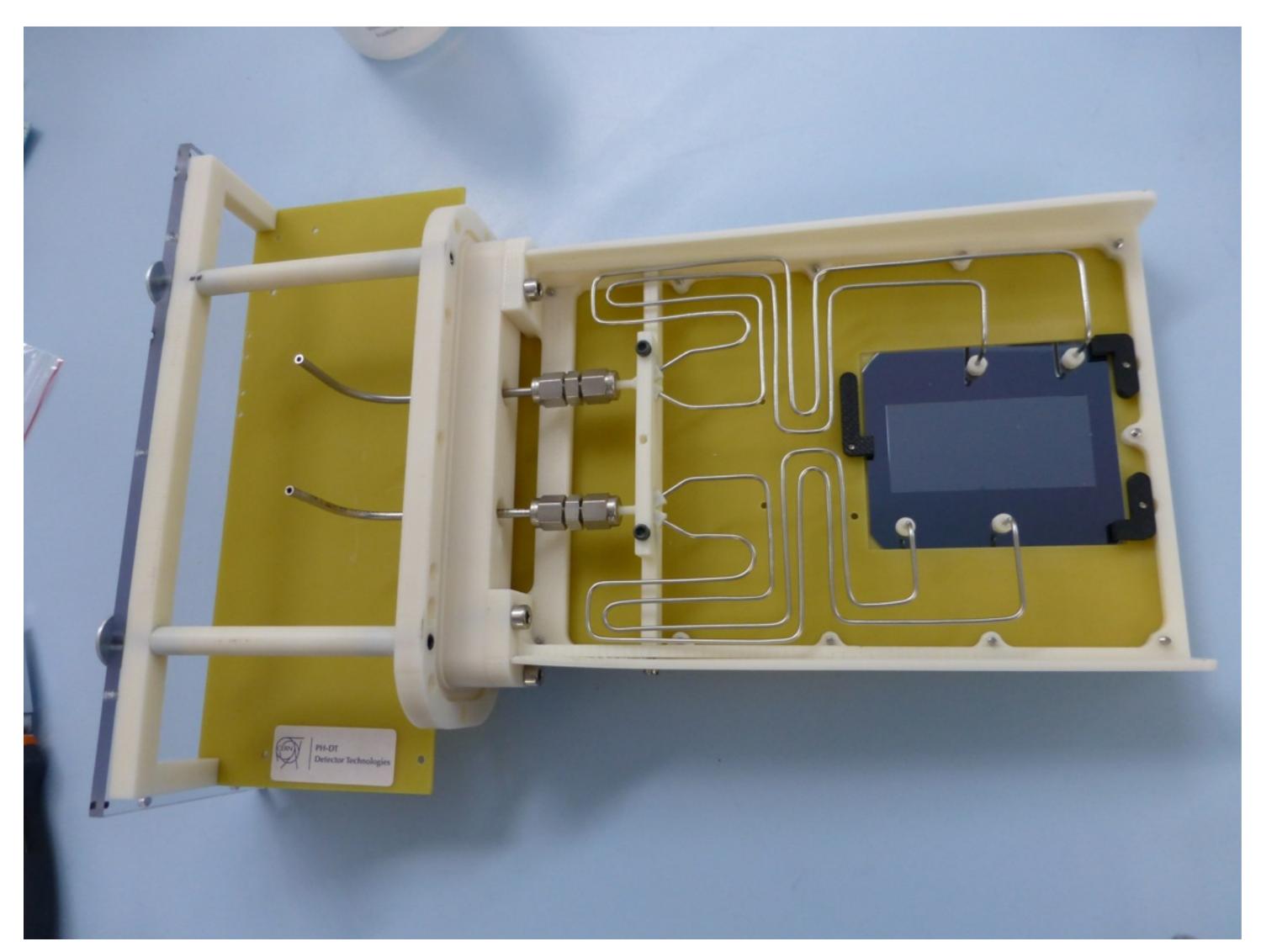

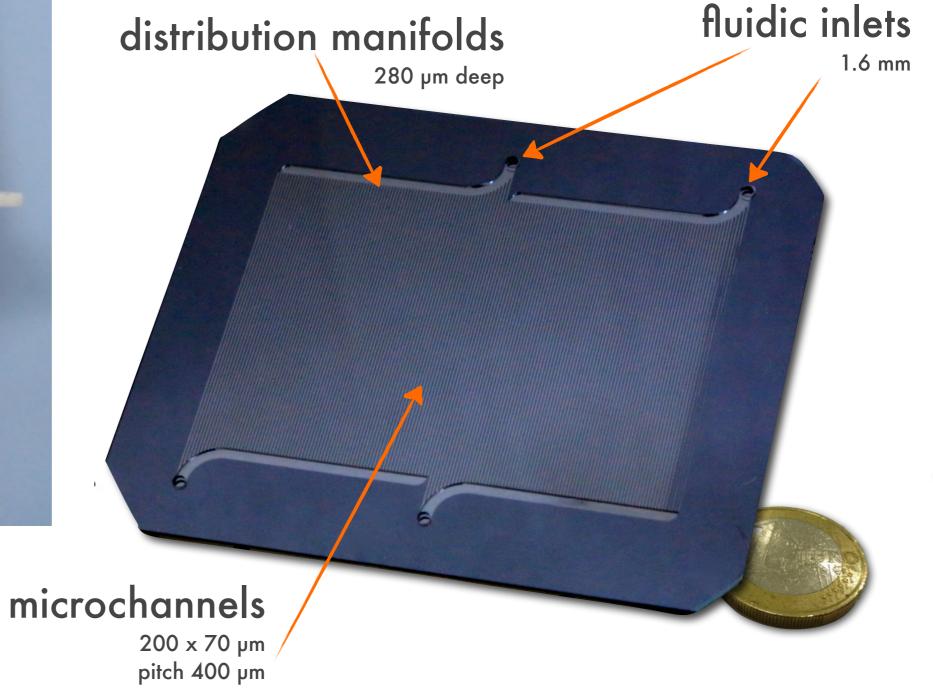

### 17A62-GTK. the 1st microCool

- In October 2014, the Gigatracker pixel detectors will be the first detectors to be cooled with silicon microchannels.

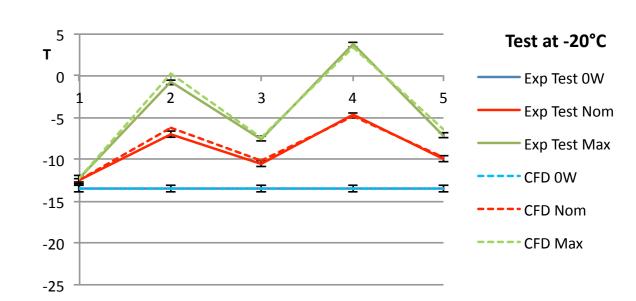

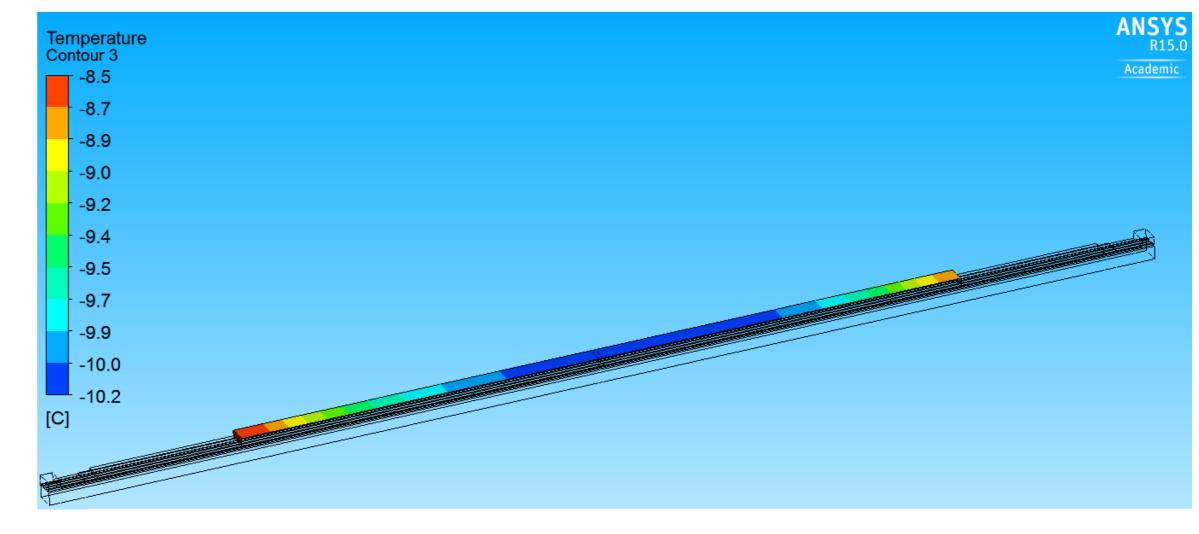

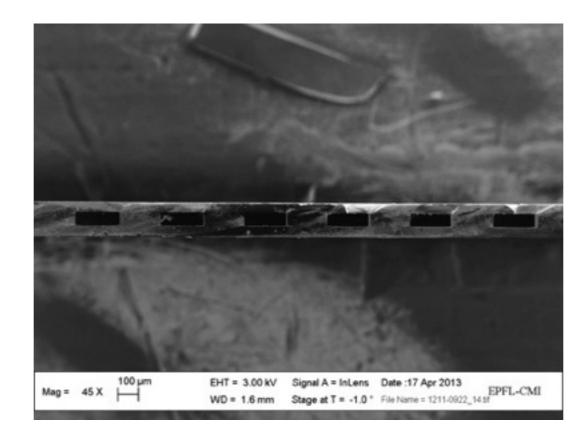

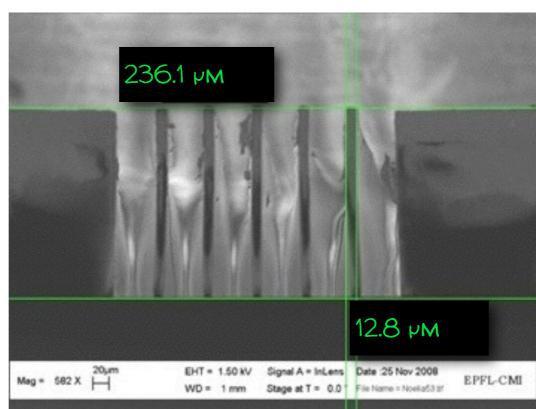

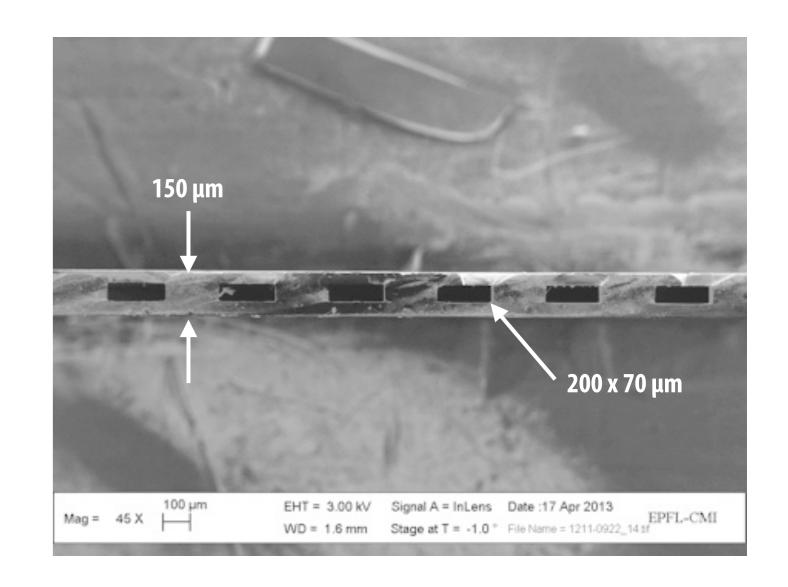

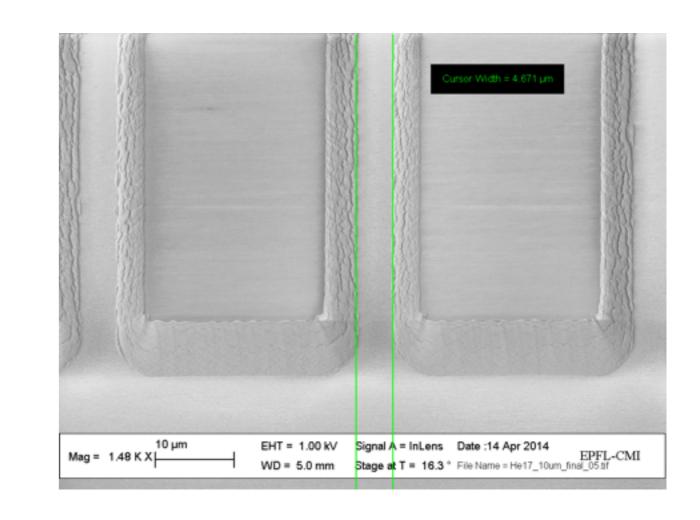

- Liquid C<sub>6</sub>F<sub>14</sub> will circulate at -20°C in a 130 μm thick silicon plate with microchannels (200 μm x 70 μm).

### NA62-GTK. the 1st microcool

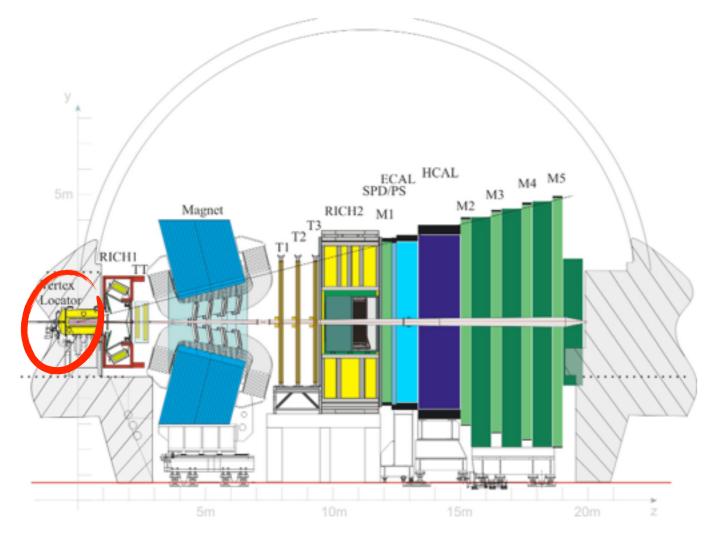

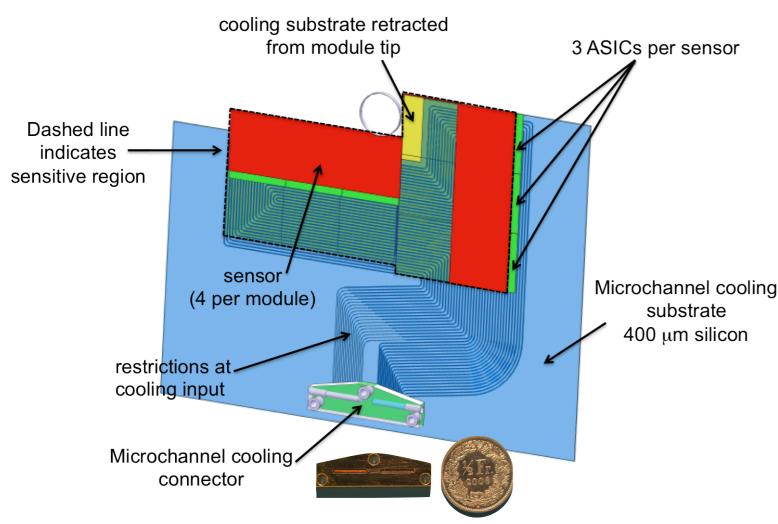

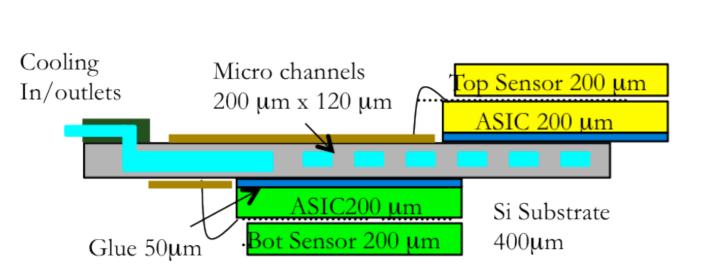

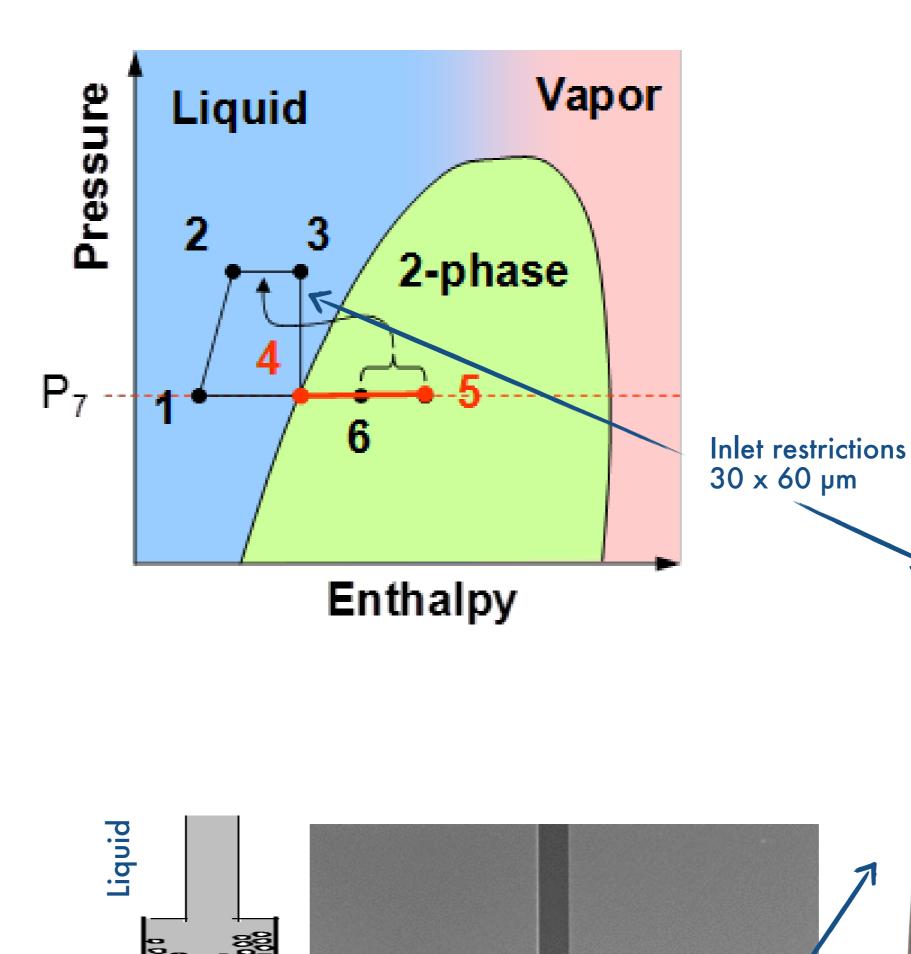

### LHCh Velo Upgrade. Co, in microchannels

Transition from inlet restrictions to evaporative microchannels

EHT = 3.00 kV Signal A = InLens Date :8 Jun 2012

WD = 4 mm Stage at T = 25.0 \* File Name = #3981\_LHCb-02338

Microchannels  $200 \times 60 \mu m$

2-phase

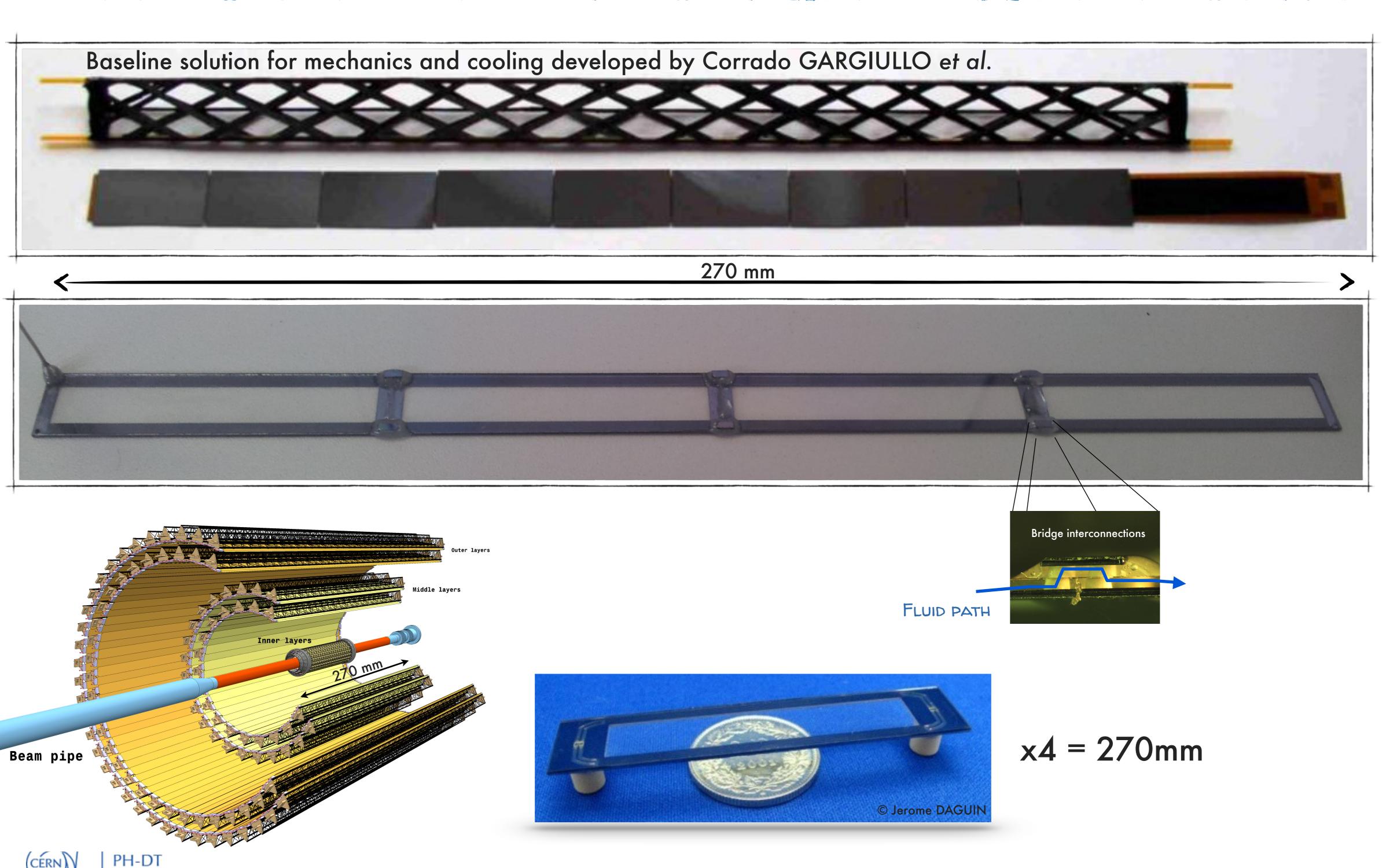

### ALICE ITS... towards a microfluidic stave

**Detector Technologies**

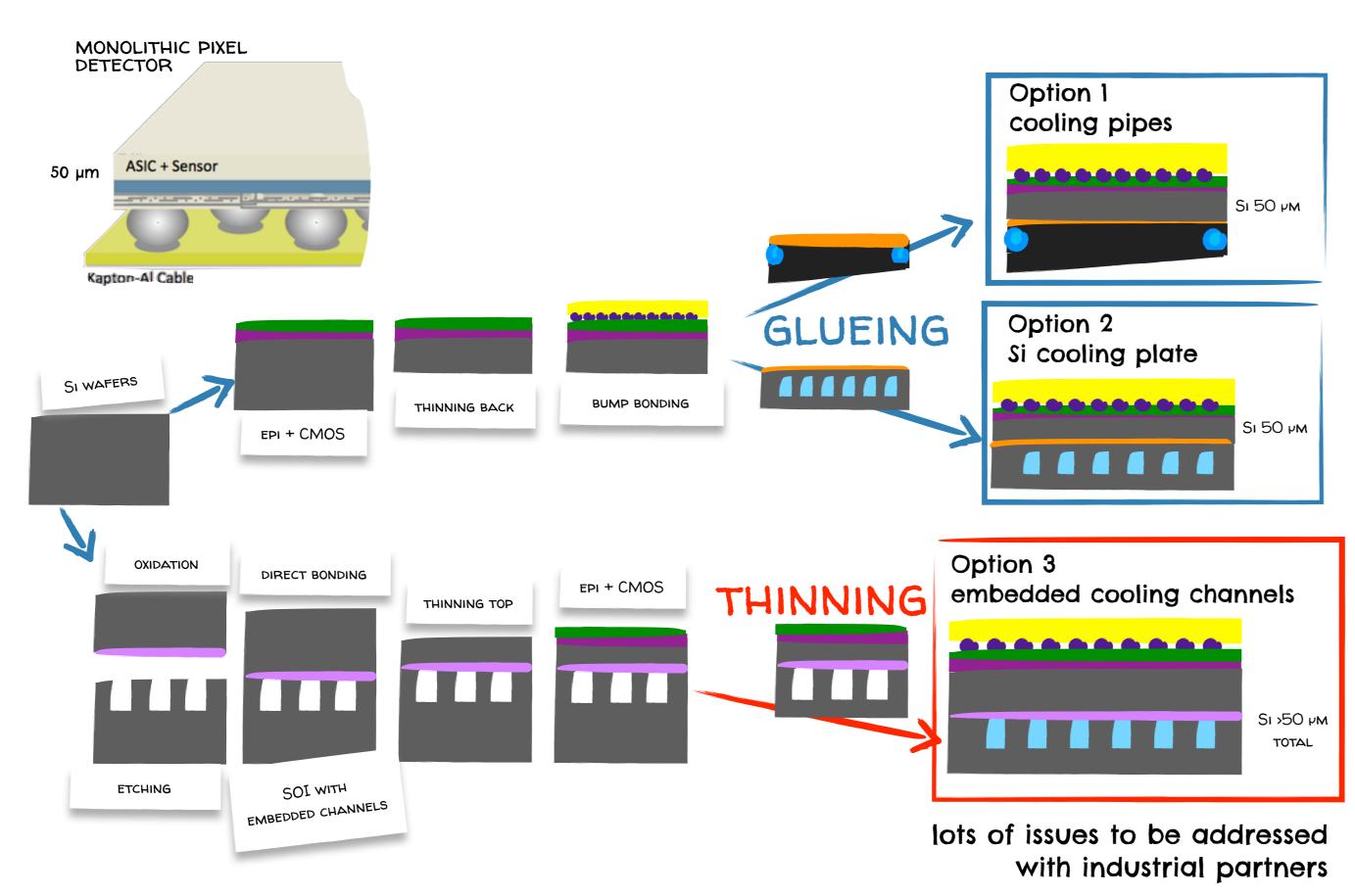

### towards integrated microcoling

A. Mapelli, L. Musa, P. Petagna, P. Riedler, 2011

#### How SOI wafers are made

[From P. N. Dunn, Solid State Technol., October, 32-35 (1993). Copyright 1993 PennWell Publishing Company, with permission.]

Many different silicon-on-insulator materials have been developed over the years, but two are currently being used for IC production: SIMOX (Separated by IMplanted OXygen) and bonded wafers.

In the SIMOX process, a standard silicon water is implanted with oxygen ions and then annealed at high temperatures; the oxygen and silicon combine to form a silicon oxide layer beneath the water surface. To minimize water damage, the oxygen is sometimes implanted

in two or more passes, each followed by an anneal. The oxide layer's thickness and depth are controlled by varying the energy and dose of the implant and the anneal temperature. In some cases, a CVD process is used to deposit additional silicon on the top layer.

The bonded water process starts with an oxide layer of the desired thickness (typically 0.25 to 2 microns) being grown on a standard silicon wafer. That wafer is then bonded at high temperatures to another wafer, with the oxide sand-

wiches between. One of the wafers is then ground to a thickness of a few microns using a mechanical tool.

Because advanced devices require an even thinner layer, more silicon must be removed. The wafer may be etched with a confined plasma, between 3 and 30 mm wide, which is stepped across the wafer surface. A film thickness map is made for each wafer and used to compute the dwell time for the plasma etcher at each

Sillicon

Sillic

stop. The process can be repeated for additional precision. Silicon thicknesses of a little as 1000 to 3000 Å, with total thickness variation of 200 Å have been achieved. IBM has also developed an etch-back process for bonded wafers.

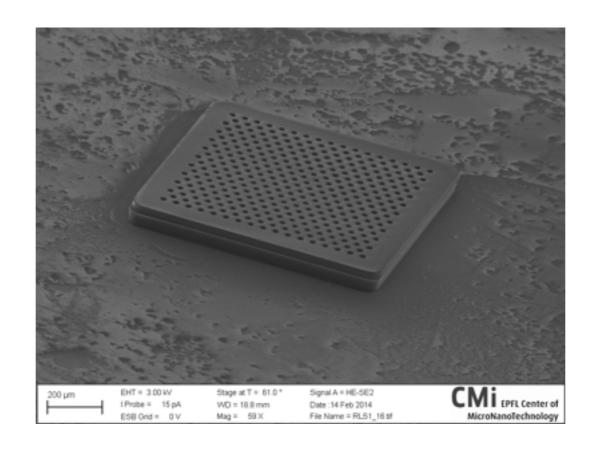

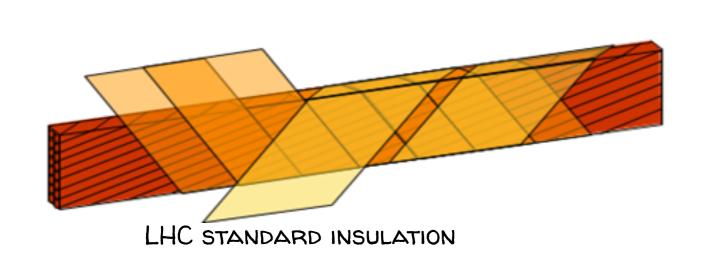

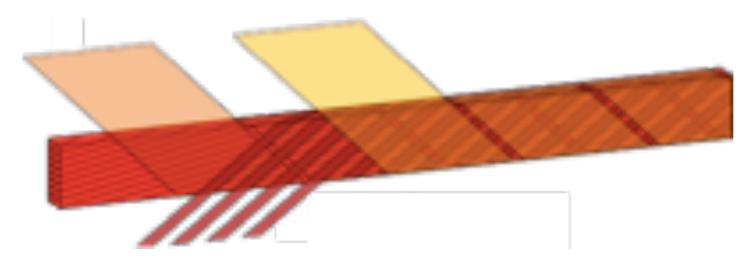

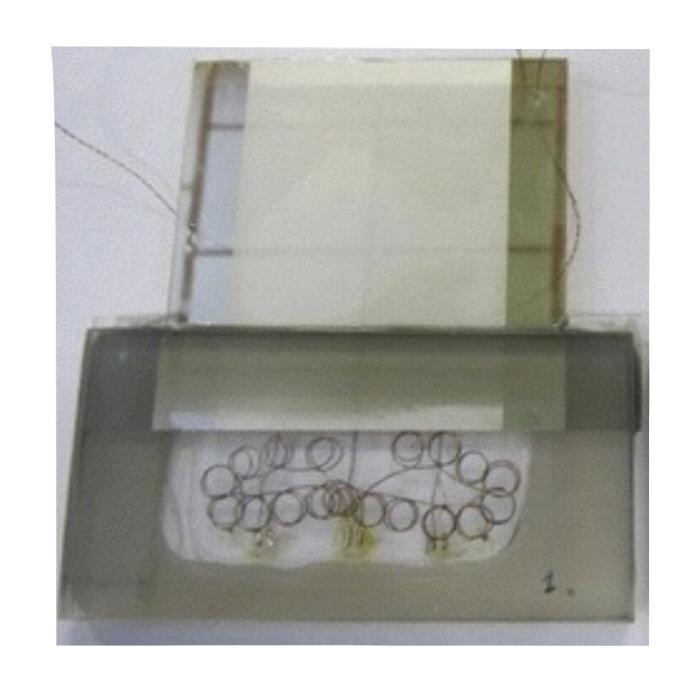

### microffell. superfluid helium

- \*study the heat transfer of superfluid Helium-II in glass microchannels

- thermally-enhanced insulation of LHC magnets for future upgrades

ENHANCED INSULATION FOR LHC UPGRADE

| Sample | MEMS<br>technique | Number of channels | Characteristic dimensions (µm)     | Total Channels<br>Area (mm <sup>2</sup> ) | Length (mm) |

|--------|-------------------|--------------------|------------------------------------|-------------------------------------------|-------------|

| 1      | Sandblasting      | 158                | $\Phi_{\text{equivalent}} = 100.4$ | 1.25                                      | 55          |

| 2      | HF etching        | 172                | 17.15 x 75.1                       | 0.22                                      | 55          |

| 3      | DRIE etching      | 1000               | ~15.8 x 24                         | 0.38                                      | 55          |

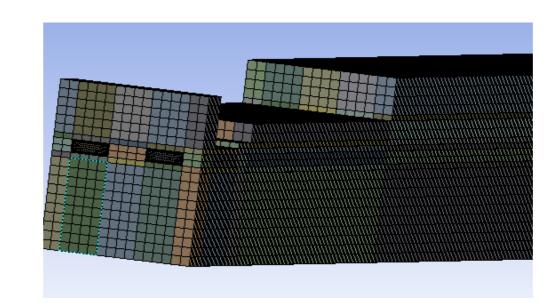

## simulations vs experiments

#### Structural resistance