# The Upgrade of the ALICE Inner Tracking System — Status of the R&D on Monolithic Silicon Pixel Sensors

Jacobus van Hoorne on behalf of the ALICE collaboration

CERN and TU Vienna

TIPP2014 , Amsterdam - 03.06.2014

## 1 A Large Ion Collider Experiment (ALICE)

## 2 ALICE Inner Tracking System (ITS) upgrade

#### **3** Status of R&D on monolithic silicon pixel sensors

2 / 20

## 1 A Large Ion Collider Experiment (ALICE)

#### 2 ALICE Inner Tracking System (ITS) upgrade

#### Status of R&D on monolithic silicon pixel sensors

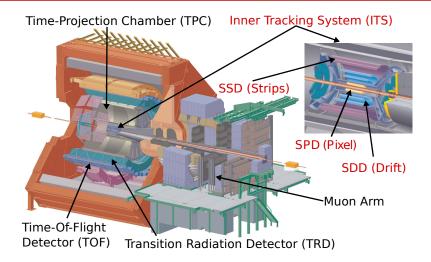

## ALICE with its present ITS

- ALICE is the experiment at the LHC optimized for A-A and p-A

- Its main goal is the study of the Quark-Gluon Plasma

Upgrade of the ALICE ITS

4 / 20

#### Motivation:

▶ High precision measurements of rare probes at low  $p_T$

#### $\textbf{Requirements} \Rightarrow \textbf{Targets:}$

- Large sample of events recorded on tape

- ▶ Pb-Pb recorded luminosity: 10 nb<sup>-1</sup> plus pp and p-A data → gain factor 100 in statistics for minimum bias trigger over current program

- Improved vertexing and tracking capabilities

#### Strategy:

- New silicon trackers:

- Inner Tracking System (ITS) covering mid-rapidity

- Muon Forward Tracker (MFT) covering forward rapidity

- Upgrades

- TPC

- Online systems

- Readout of several detectors

C. Lippmann, 2.a Experiments and Upgrades, Session 1: *Upgrade of the ALICE detector*

J. W. van Hoorne (CERN/TU Vienna)

Upgrade of the ALICE ITS

#### 1 A Large Ion Collider Experiment (ALICE)

## 2 ALICE Inner Tracking System (ITS) upgrade

#### Status of R&D on monolithic silicon pixel sensors

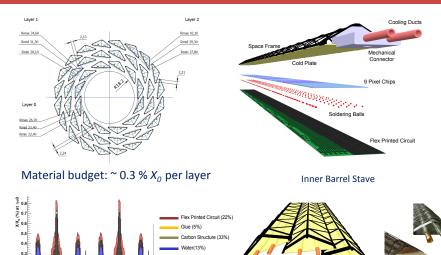

# ALICE ITS upgrade design objectives

- Improve impact parameter resolution by factor  $\approx 3(5)$  in r- $\phi(z)$  at  $p_T = 500 \text{ MeV/c}$

- move closer to IP (position of first layer):  $39 \text{ mm} \rightarrow 22 \text{ mm}$

- ▶ reduce material budget:  $X/X_0$ /layer:  $\sim 1.14\% \rightarrow 0.3\%$  (inner layers)

- reduce pixel size:  $50 \,\mu\text{m} \times 425 \,\mu\text{m} \rightarrow O(30 \,\mu\text{m} \times 30 \,\mu\text{m})$

**(2)** Improve tracking efficiency and  $p_T$  resolution at low  $p_T$

- increase granularity: 6 layers  $\rightarrow$  7 layers

- **Fast readout** (now limited at 1 kHz with full ITS):

- ▶ Pb-Pb: > 50 kHz

- pp: several 100 kHz

- Fast insertion/removal

- possibility to access for yearly maintenance

#### The new ALICE ITS will fully replace the present ITS

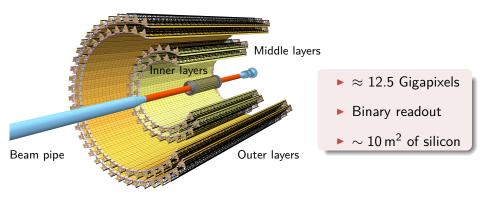

## Layout of upgraded ALICE ITS

Radiation level (innermost layer, including a safety factor 10):

- $\blacktriangleright~700\,krad$  (TID) and  $1\times10^{13}\,1\,MeV\,n_{eq}$  (NIEL)

- Radial coverage: 22 mm to 400 mm

- ▶  $\eta$  coverage:  $|\eta| \le 1.22$ , for tracks from 90 % most luminous region

## Technology choice and expected improvements

Very thin sensors Very high granularity Monolithic silicon pixel sensors Large area to cover Modest radiation levels ALICE. CERN-LHCC-2013-024 ALICE, CERN-LHCC-2013-024 (100 ق Efficiency (%) 8 001 ALICE Current ITS, Z (Pb-Pb data, 2011) Pointing resolution 200 120 120 Upgraded ITS, Z Current ITS, re (Pb-Pb data, 2011) Upgraded ITS, rg ALICE Current ITS Upgraded ITS 40 IB: X/X.= 0.3%: OB: X/X = 0.8% 100 20 50 0 10-1  $10^{-1}$ 10 10 p\_ (GeV/c) p\_ (GeV/c)

Exected improvement of pointing resolution (left) and tracking efficiency (right)

## A Large Ion Collider Experiment (ALICE)

#### 2 ALICE Inner Tracking System (ITS) upgrade

#### **3** Status of R&D on monolithic silicon pixel sensors

10 / 20

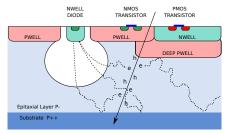

## Pixel chip technology and working principle

11 / 20

- Monolithic silicon pixel sensors using TowerJazz 0.18 µm CMOS Imaging Process

- High-resistivity epitaxial layer on p-type substrate

- Special deep p-well for full CMOS within the matrix (based on the experience of RAL)

- Working principle:

schematic cross section of pixel of monolithic silicon pixel sensor NWELL diode output signal:

$V \sim Q/C$

- Mitigate charge spread over different pixels

- Minimize capacitance:

- diode surface

- depletion volume

- ightarrow (reverse) biasing

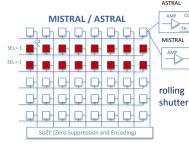

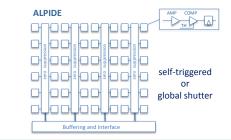

## Pixel chip architectures under development

COMP

Different architecture design streams:

#### — ASTRAL (MISTRAL):

based on the experience of the STAR PXL detector

#### **General requirements:**

- Chip size: 15 mm × 30 mm

- Sensor thickness: 50 μm

- ALPIDE:

A. Collu, poster 26, *An innovative Monolithic Active Pixel Sensor for the Upgrade of the ALICE ITS*

- Spatial resolution:  $\approx 5 \, \mu m$

- Integration time: < 30 µs</p>

- Power density: <100 mW/cm<sup>2</sup>

Upgrade of the ALICE ITS

## Pixel chip - R&D

- Dedicated R&D started in 2011 :

- Improve Signal/Noise Ratio (SNR):

- optimization of charge collection diode, apply reverse-bias voltage

- optimize thickness and resistivity of epitaxial layer

- Study different front-end and readout architectures

- reduce power consumption and integration/readout time

- Study radiation effects

- Several small and large scale prototypes, each focussing on particular aspect:

| Architecture     | Analogue                 | Digital                    |            |

|------------------|--------------------------|----------------------------|------------|

|                  |                          | small-scale                | full-scale |

| ASTRAL (MISTRAL) | MIMOSA-32-X<br>MIMOSA-34 | MIMOSA-22THR-X<br>AROM-0/1 | FSBB       |

| ALPIDE           | Explorer-0<br>Explorer-1 | pALPIDE                    | pALPIDEfs  |

J. W. van Hoorne (CERN/TU Vienna)

Upgrade of the ALICE ITS

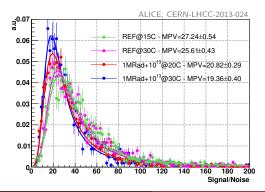

#### MIMOSA-32ter

ASTRAL (MISTRAL)

analogue prototype with in-pixel pre-amplification & average noise subtraction  $\rightarrow$  in-pixel circuitry optimisation, radiation hardness

▶ Seed pixel SNR before and after irradiation with 1 Mrad (TID) and  $1 \times 10^{13}$  1 MeV n<sub>eq</sub> (NIEL) at 20° and 30° C

Adequate radiation hardness

SNR measured for MIMOSA-32ter sensors (on an HR-18 wafer type) in the SPS with a 120 GeV/c pion beam

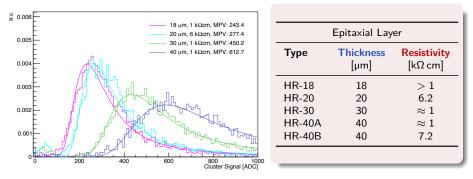

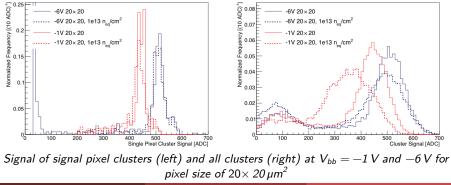

#### Explorer-1

analogue prototype with variable integration and readout time, 20 and 30  $\mu$ m pitch  $\rightarrow$  charge collection, reverse biasing, noise

Study of different starting wafers

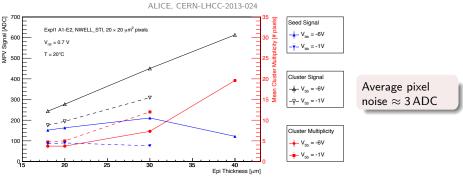

Cluster signal for different epi thicknesses at  $V_{bb} = -6 V$  measured at test beam at DESY with 3.2 GeV/c electron beam (pixel size  $20 \times 20 \,\mu m^2$ )

J. W. van Hoorne (CERN/TU Vienna)

Upgrade of the ALICE ITS

**ALPIDE**

#### Explorer-1

Seed signal, cluster signal and multiplicity vs. epi thickness for  $V_{bb} = -1 V$  and -6 V

- Reverse bias: significant increase of SNR

- Cluster charge increases linearly with the epi layer thickness

- Cluster size increases for thicker epi layer thicknesses

- ▶ Largest SNR (seed pixel): HR-30 for  $V_{bb} = -6$  V, HR-20 for  $V_{bb} = -1$  V

**ALPIDE**

#### Explorer-1

**ALPIDE**

#### TCAD simulations

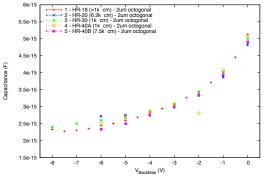

Pixel capacitance vs  $V_{bb}$  for different starting wafer types

- Pixel capacitance drops with increasing reverse bias, in agreement with simulated size of depletion region

- ► Effect similar for all starting materials → minor influence of epi resistivity for current pixel layouts

17 / 20

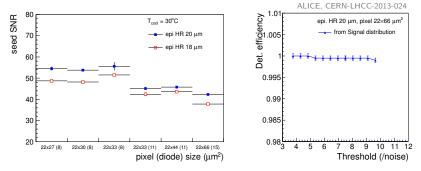

#### MIMOSA-34

analogue prototype with no in-pixel pre-amplification and CDS circuitry

$\rightarrow$  sensing node optimisation as function of pixel size and epitaxial layer characteristics

$\blacktriangleright$  SNR of seed pixel for pixels in the range  $22\times27\,\mu\text{m}^2$  to  $22\times66\,\mu\text{m}^2$

Measured at test beam at DESY with 4.4 GeV/c electron beam

High detection efficiency also for large pixels

**ASTRAL (MISTRAL)**

ALPIDE

#### ASTRAL (MISTRAL)

#### MIMOSA-22THR

in-pixel pre-amplification and CDS circuitry, parallel column readout and discriminators at end of column,  $22 \times 33 \,\mu m^2$  pixels  $\rightarrow$  used to validate upstream part of MISTRAL and most of ASTRAL readout

#### pALPIDE

*in-pixel front-end, binary readout, in-matrix sparsification, 22 μm pitch*

$\rightarrow$  used for optimization of in-pixel front-end with binary readout and priority encoder

• Measured at **test beam** at DESY with 3 to 6 GeV  $e^-$  and  $e^+$  beams:

- Detection efficiency: >99 %

- Fake hit rate:  $\approx 10^{-8}/(\text{event} \times \text{pixel})$

- Spatial resolution  $\approx$  5  $\mu$ m

Performance of small scale digital prototypes complies with requirements

Upgrade of the ALICE ITS

- New ALICE ITS with 7 layers of monolithic silicon pixel sensors will be installed during LS2 of the LHC in 2018/19

- Different architectures for the pixel chip have been explored

- Several small-scale prototype sensors have been characterized in test beam and laboratory

- adequate radiation hardness has been proven

- reverse biasing: significant increase of SNR

- effects of different epi layer thicknesses and resistivities:

- regions of parameter space could be excluded

approaching optimum

- epi resistivity has minor influence for current pixel layouts

- performance of small scale digital prototypes complies with requirements of pixel chip

- Full-scale prototypes are currently beeing characterized

on 12th March 2014

# Spare slides

| Parameter                          | Inner Barrel | Outer Barrel |

|------------------------------------|--------------|--------------|

| max. silicon thickness (µm)        | 50           |              |

| spatial resolution (µm)            | 5            | 30           |

| chip dimensions (mm <sup>2</sup> ) | 15 	imes 30  |              |

| max. power density (mW)            | 300          | 100          |

| max. integration time ( $\mu$ s)   | 30           |              |

#### Explorer-0

analogue prototype with variable integration and readout time, 20  $\mu m$  and 30  $\mu m$  pitch

ightarrow for pixel layout optimisation (charge collection, reverse biasing, noise)

Pixel response to X-rays from <sup>55</sup>Fe source before and after irradiation with 1 × 10<sup>13</sup> 1 MeV n<sub>eq</sub> (NIEL)

**ALPIDE**

#### Inner Barrel

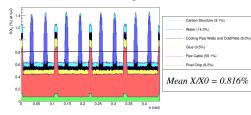

0.4 0.6 0.8 1 ¢ (rad)

0.2

0.1 0<sub>0</sub>

Upgrade of the ALICE ITS

Cooling pipes wall (2%)

Pixel Chip (26%)

Mean X/X0 = 0.282%

TIPP2014 - 03.06.2014 24 / 20

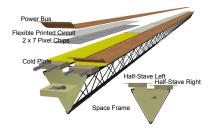

#### Outer Barrel

**Outer Barrel Stave**

#### Material budget: ~ 0.8 % $X_0$ per layer