# Recent Status of Front-end Electronics for DEPFET Pixel Detectors for Belle II

#### **Tetsuichi Kishishita**

T. Hemperek, H. Krüger, M. Lemarenko, F. Lütticke, L. Germic, C. Marinas, and N. Wermes

#### **Outline**

- -Concept of the Belle II Pixel Detector

- -Requirements to the Front-end Electronics

- -Hybrid Module

- -Test Results

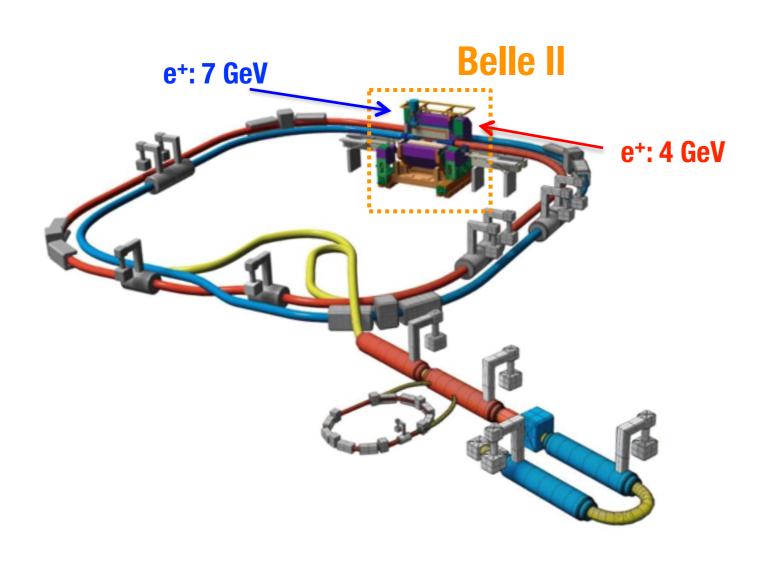

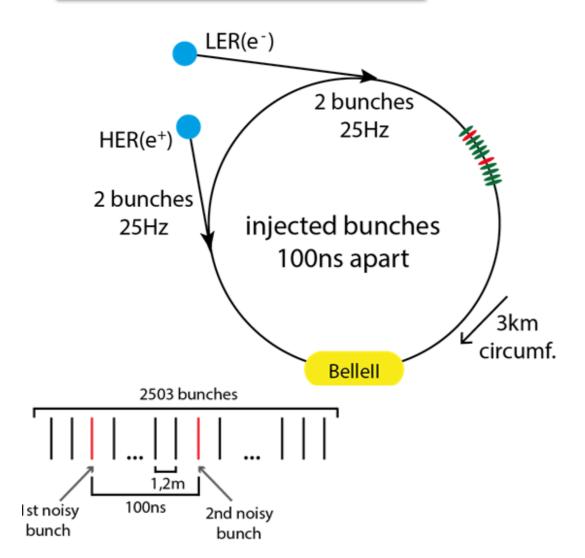

## Pixel Detector at Belle II Experiment

- e-/e+ collider for B<sup>0</sup>/B<sup>0</sup>-bar

- KEKB/Belle upgrade in Japan

- Super high-luminosity ~8×10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Refurbishment of accelerator & detector

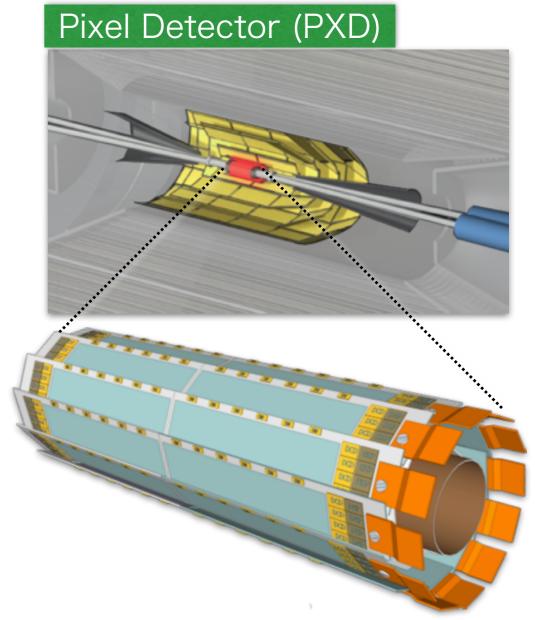

- Innermost vertex detector (PXD) at Φ=14 & 22 mm, total 40 modules

- DEPFET sensors technology

- Frame rate of 20 us

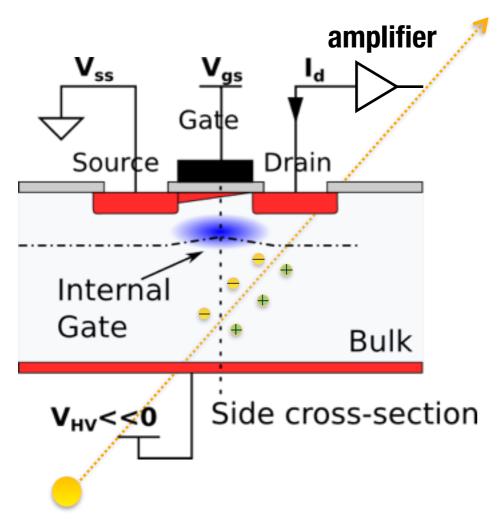

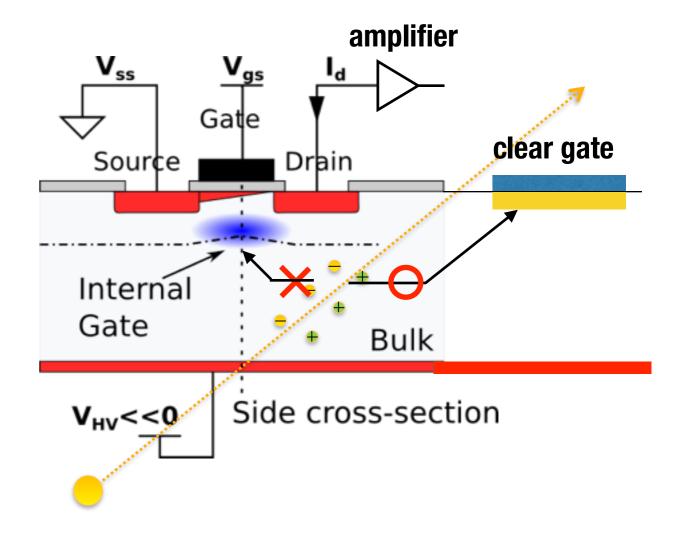

### **DEPFET Sensors**

- p-FET on fully depleted bulk

- Modulation of the FET current by accumulated electrons under the internal gate ( $g_q \sim 600 \text{ pA/e}^-$ )

- Clear signals via punch-through effect

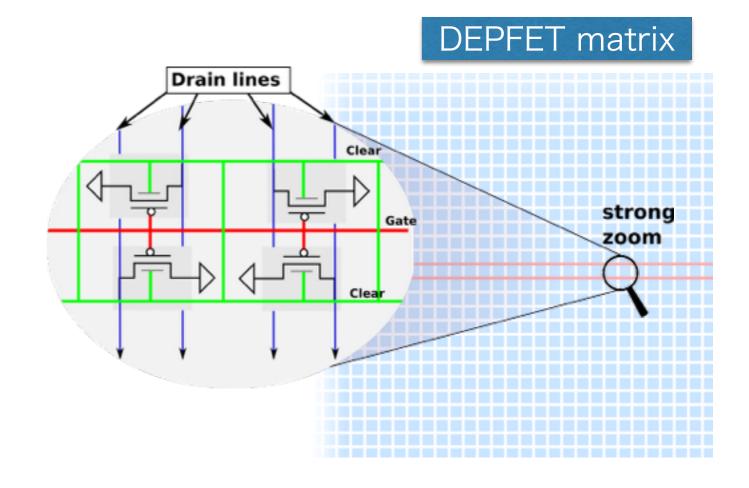

- Row-wise steering

- Column-wise connection of pixel drains

- Drain currents sampled by custom FE

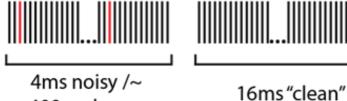

## **Operating Mode**

Normal, charge collection operation

#### Gated-Mode operation

Adjusting potential min. with gate and clear gates e- by noise bunch directly to clear gate

400packages

TIPP 2014, 2-6 June. Amsterdam

### **Front-end Electronics**

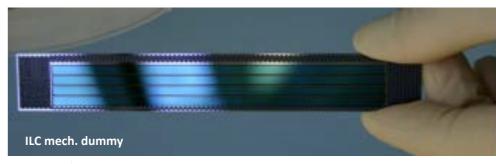

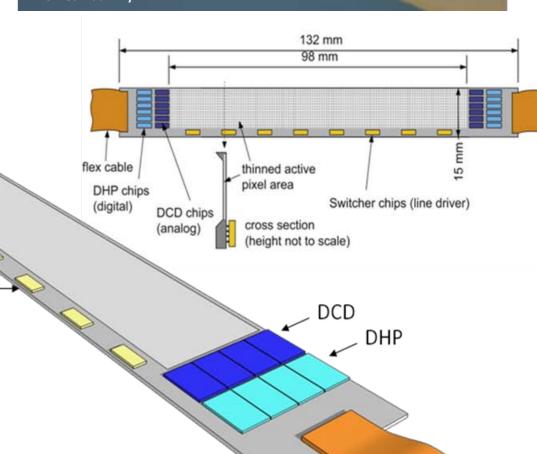

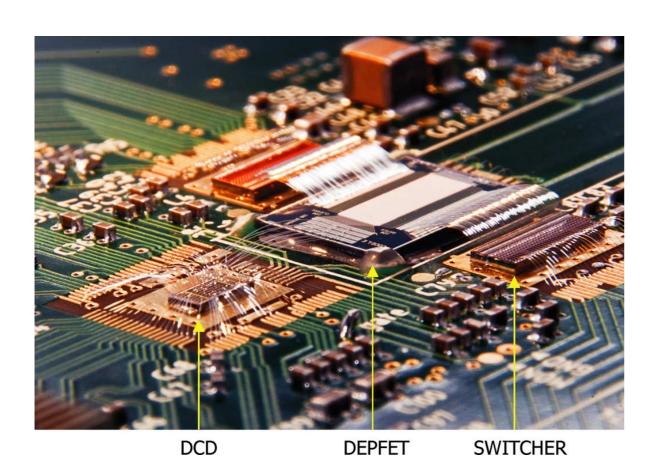

- Active pixel area thinned down to 75 um

- ASICs bump bonded on sensor substrate

**ASIC R&D more than 7 years**

#### SWITCHER

providing steering signals

#### DCD (Drain Current Digitizer)

digitize the drain current from matrix

#### DHP (Data Handling Processor)

- data reduction

- send data off the module to the backend elec.

#### "All-silicon" DEPFET module

Switcher

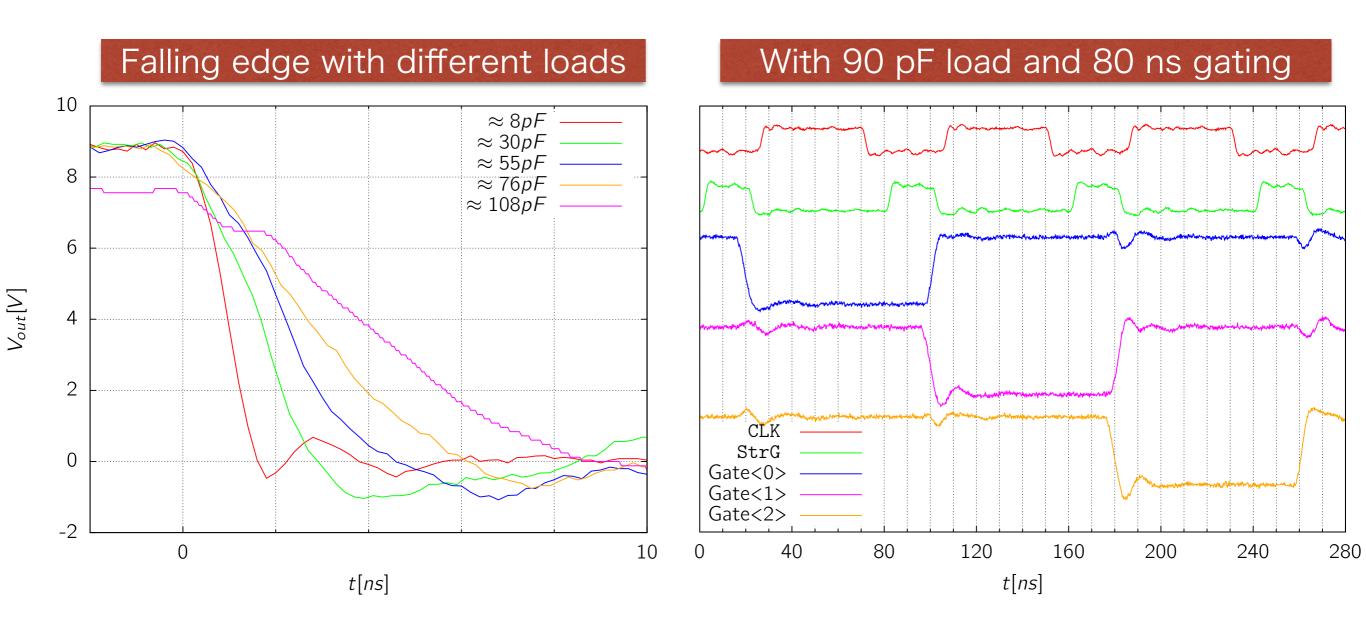

### Front-end ASIC #1: SWITCHER-B

- AMS high voltage 0.18 um CMOS

- Designed by Uni. Heidelberg

- Size: 3.6×1.5 mm<sup>2</sup>

- contains additional logic for gated-mode operation

#### Requirements to the ASIC

- Fast pulse to drive large line cap. (~50 pF)

- Fast HV up to 20 V for complete clear within ~20 ns

- stacked-transistor output stage

- thin gate oxide transistors for rad.-hard

### **Performance Verification**

- Flexible timing control with CLK and strobe signals

- Rad. Hard proven (up to 36 Mrad in previous design)

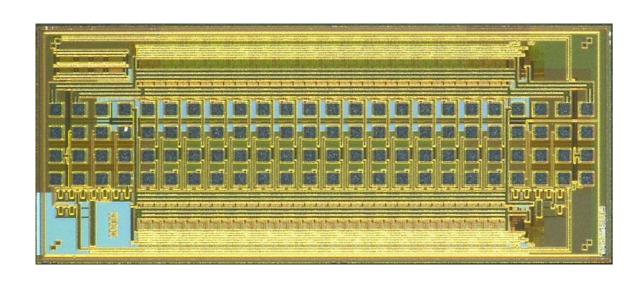

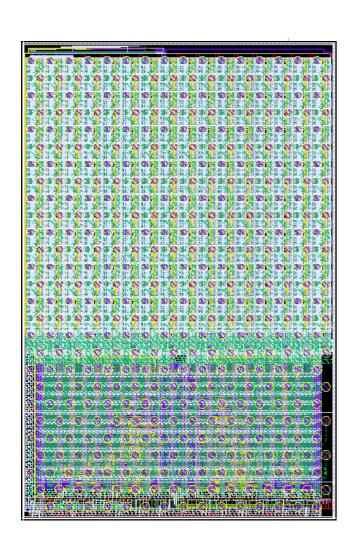

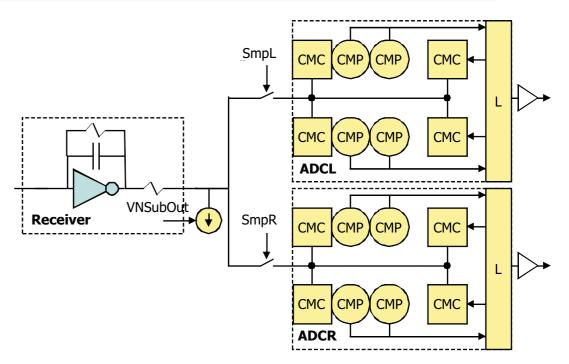

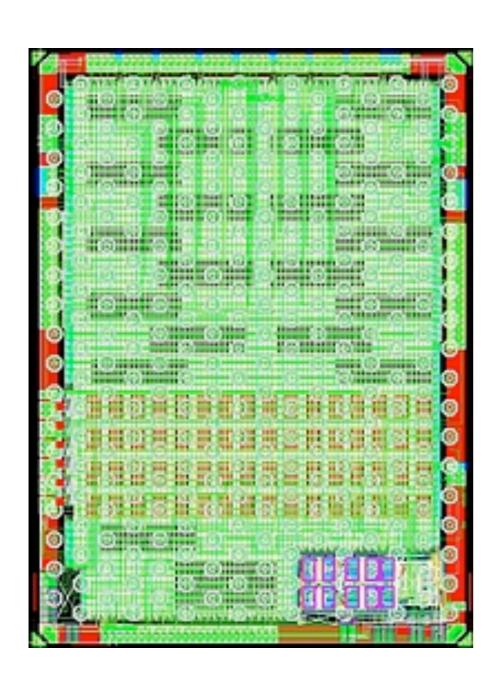

### Front-end ASIC #2: DCD (Drain Current Digitizer)

- UMC 180 nm

- Designed by Uni. Heidelberg

- Size: 3.3×5.0 mm<sup>2</sup>

- Noise: 40 nA

- Irradiation up to 7 Mrad

#### Requirements to the ASIC

- Low-noise & fast settling current receiver (Rs= $200\Omega$ , Cd=50 pF)

- 10 M Sample/s

- 256 input channels

- Trans-impedance amplifier

- performance adjustment with DACs

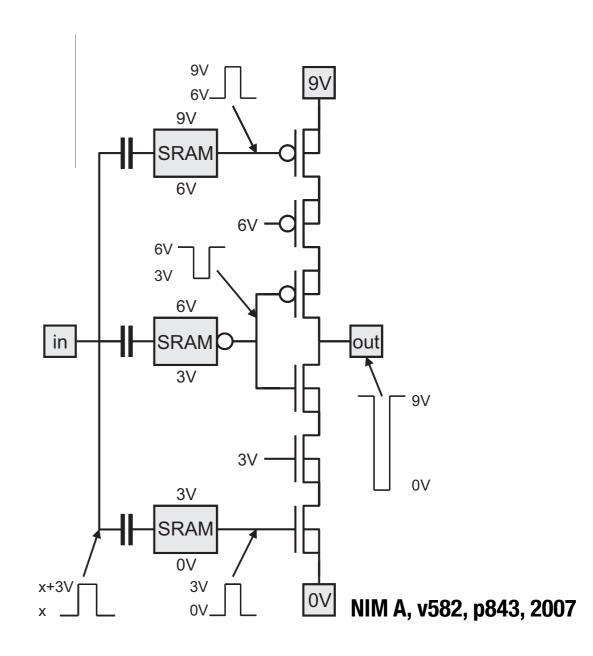

- Each channel with two current mode cyclic ADCs based on current-memory cells

- 80 ns sampling period with 8 bits resolution

### **Performance Verification**

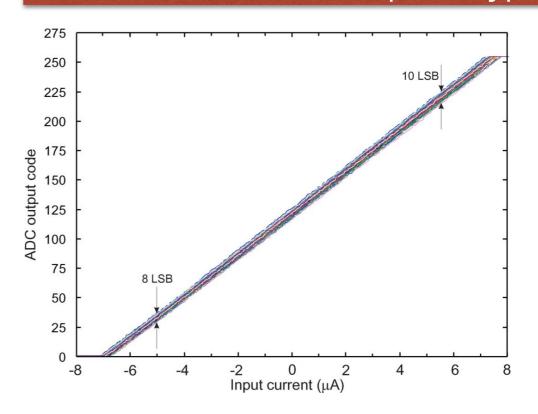

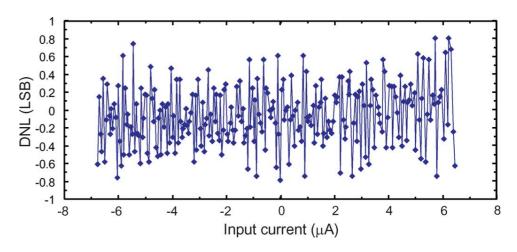

| Technology                        | 180 nm CMOS                                                                          |

|-----------------------------------|--------------------------------------------------------------------------------------|

| Resolution                        | 8 bits                                                                               |

| Simulated settling time $(3\tau)$ | $\sim 9\mathrm{ns}$ (fast ADC: $\sim 4.5\mathrm{ns}$ )                               |

| Conversion rate                   | $40 \mathrm{ns}/bit$ (fast ADC: $20 \mathrm{ns}/bit$ )                               |

| Full-scale current                | $\pm 8\mu\mathrm{A}$                                                                 |

| DNL                               | $\pm 0.8 LSB$                                                                        |

| INL                               | $\pm 1LSB$                                                                           |

| SNR                               | 56 dB (fast ADC: 54 dB)                                                              |

| Power supply                      | 1.8 V                                                                                |

| Active area                       | $40  \mu \mathrm{m} \times 55  \mu \mathrm{m}   \mathrm{or}   0.0022  \mathrm{mm}^2$ |

| Static power consumption          | $0.96\mathrm{mW}$                                                                    |

#### Transfer curve of the prototype

IEEE TNS, v. 57, p. 743, 2010

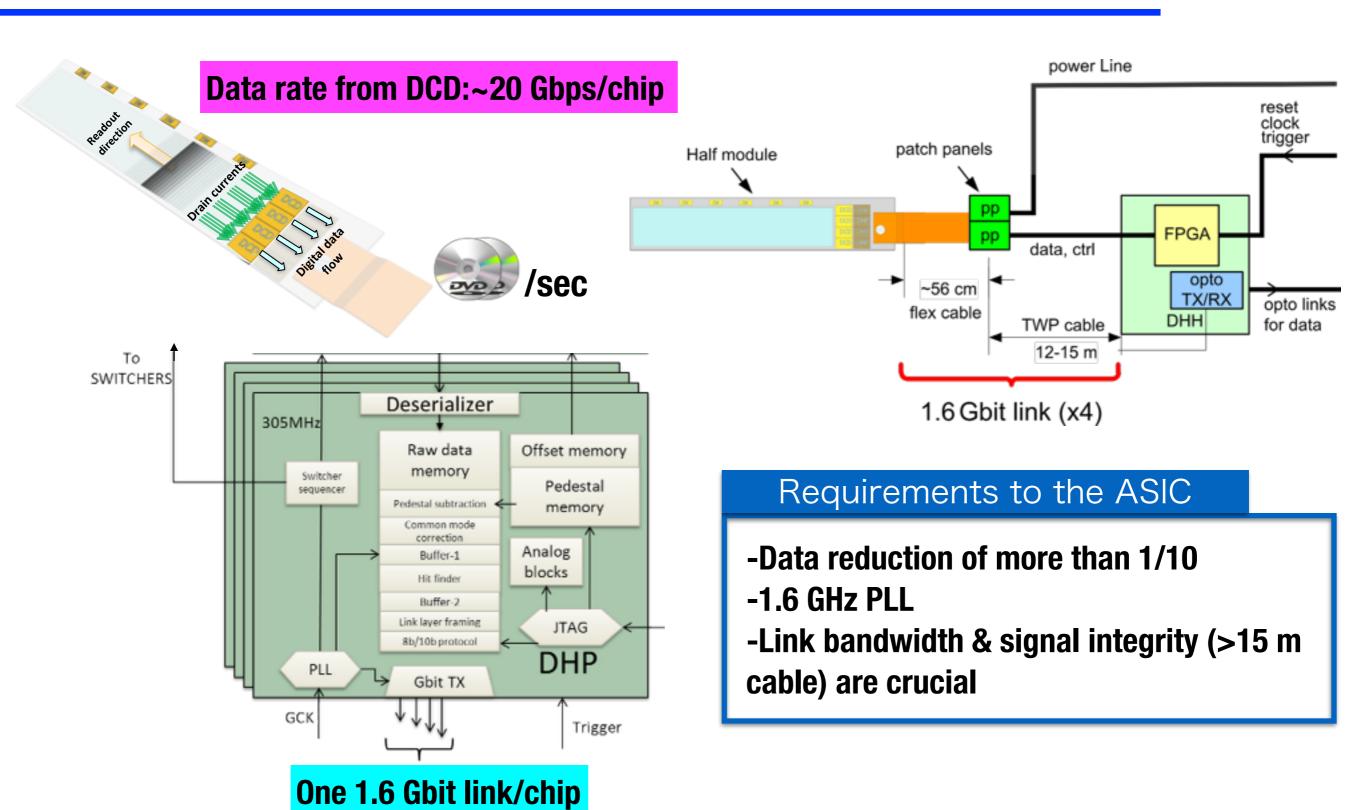

### Front-end ASIC #3: DHP (Data Handling Processor)

- TSMC 65 nm CMOS

- Designed by Uni. Bonn

- Size of 3×4 mm<sup>2</sup>

#### Functions of the ASIC

- Timing generation (1.6 GHz) + clock distribution

- Data processing

**Zero-suppression**

Only triggered data readout

Raw data buffering

**Fixed pattern noise correction**

**Hit finder**

Framing (AURORA)

Serializer and Gbit link driver

### DHP Chip History at Bonn

#### DHP 0.1, 2010, IBM 90nm

Half size prototype chip, 1.6 GHz PLL, Gbit link, memories, analog test structures, 200µm pitch bump bonds

#### DHP 0.2, 2011, IBM 90nm

Second prototype (full size), 1.6 GHz PLL, Gigabit driver with programmable pre-emphasis, onchip bias DACs

#### DHPT 0.2, 2012, TSMC 65 nm

test structures for future ATLAS and **DEPFET** projects.

LVDS 10 8-bit, 10 Mbps ADC **Analog Pixel Front-end Temperature sensor**

#### DHPT 1.0, 2013, TSMC 65 nm

First production version

12 mm<sup>2</sup> 296 bumps **3Mbit memory** 1.6 GHz data link

#### DHPT 0.1, 2011, TSMC 65 nm

test structures for future ATLAS and DEPFET projects.

PLL + GBit link driver Charge sensitive amplifier **Memory test structures DAC**, current reference (U Barcelona)

## **Data Link Specifications**

TIPP 2014, 2-6 June. Amsterdam

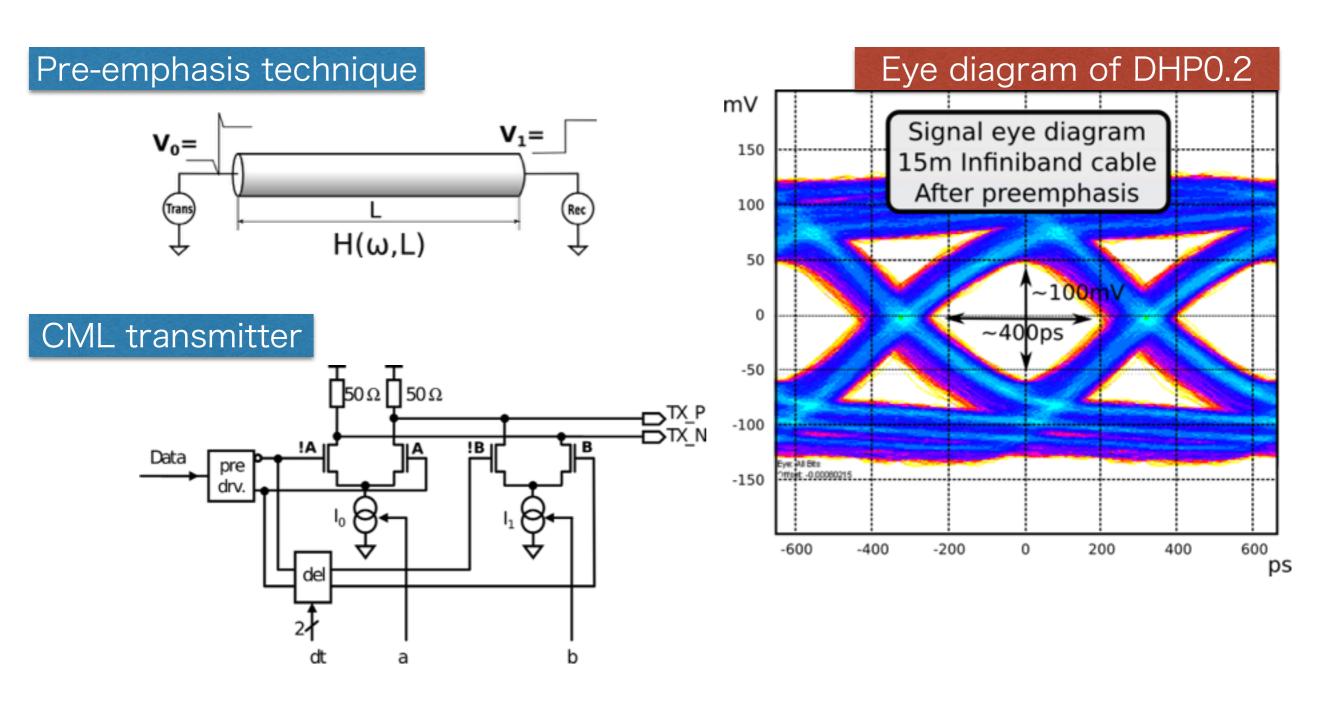

### Pre-emphasis with Gbit link driver

Idea: boost high frequency components of the transmitted signal to compensate to cable attenuation

TIPP 2014, 2-6 June. Amsterdam

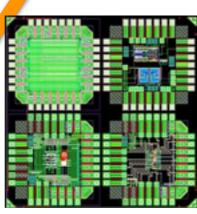

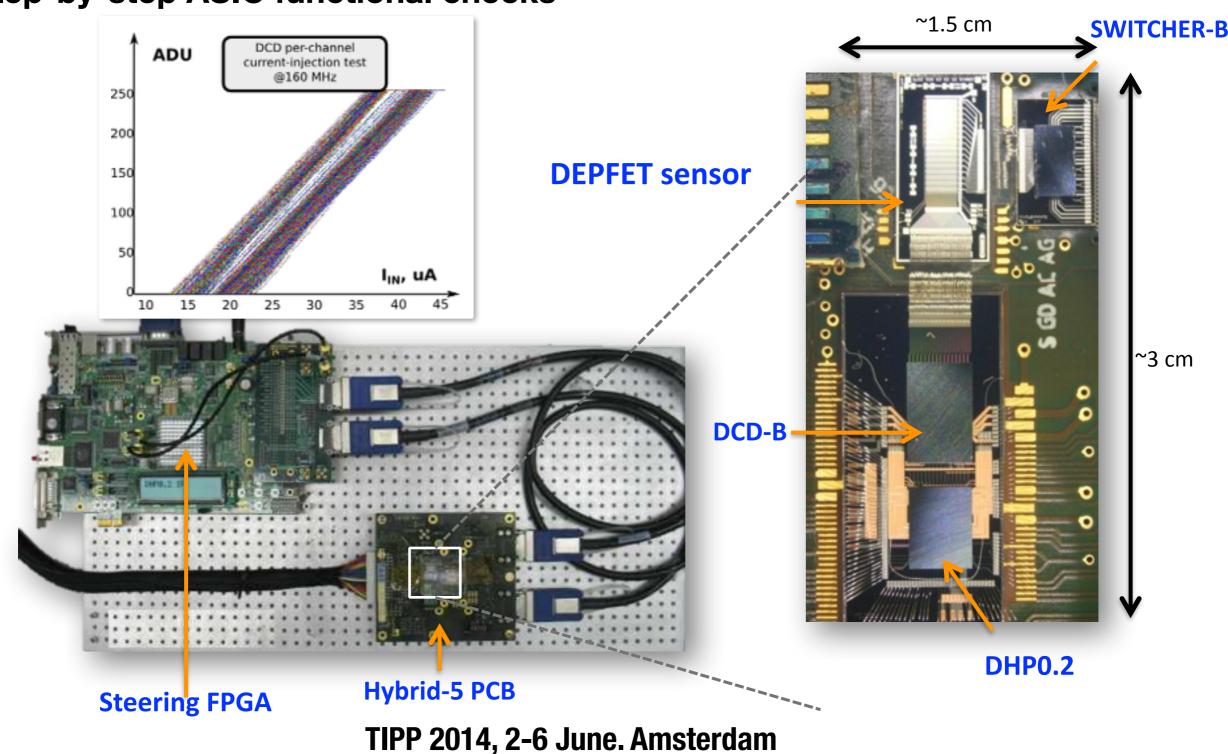

### Full Scale Module Prototype

- Assembly with bump-bonding

- Step-by-step ASIC functional checks

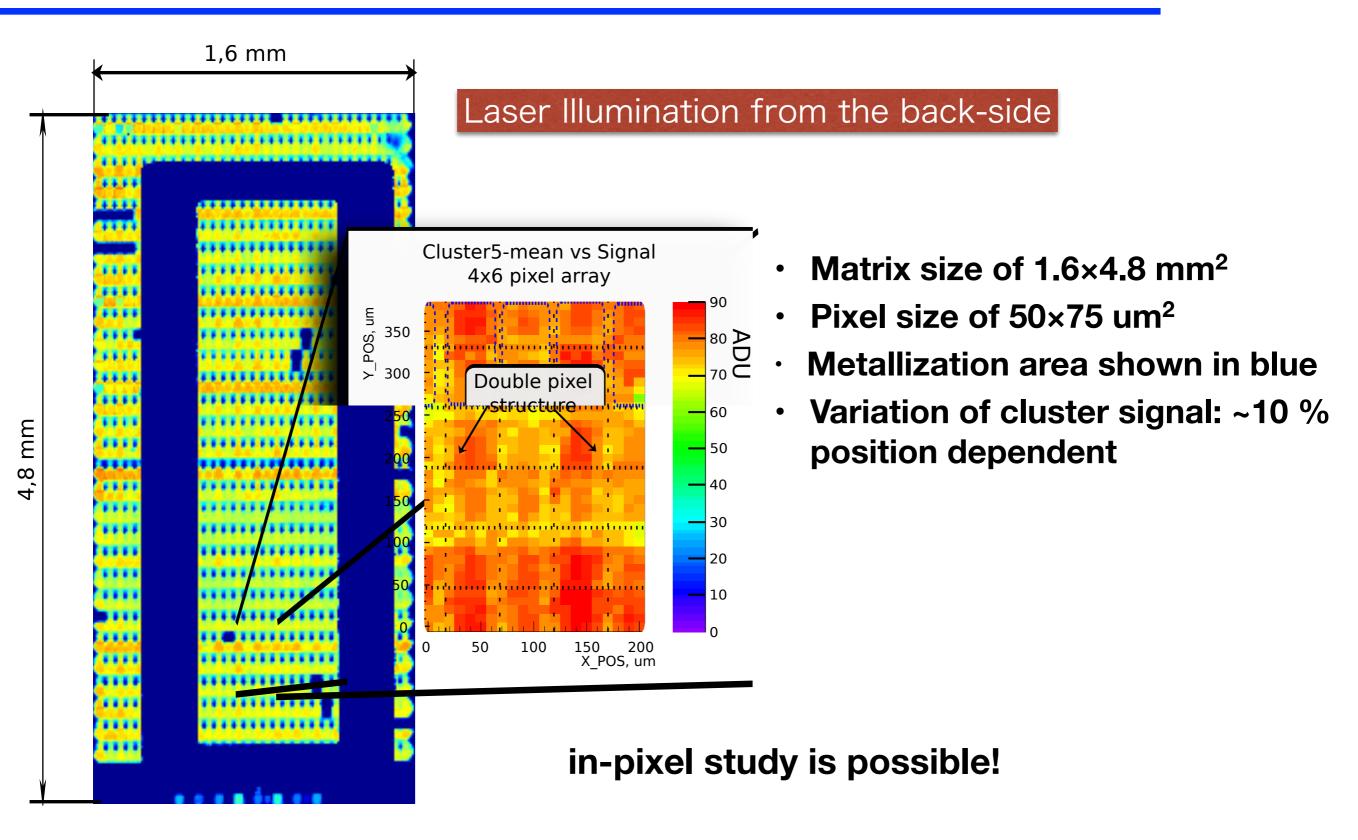

### Laser test

TIPP 2014, 2-6 June. Amsterdam

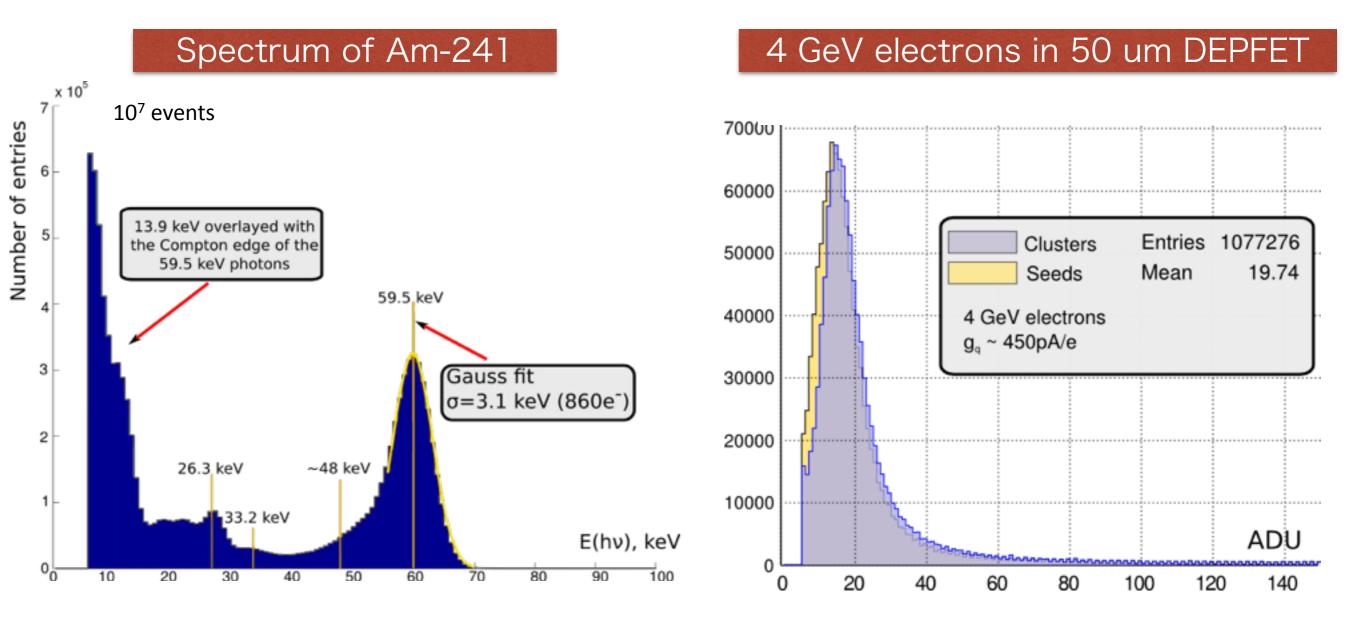

### **IR-Source and Test beam results**

All ASICs are working correctly with DEPFET sensor!!

### Summary

- -The Belle II PXD has been developed based on DEPFET sensors.

- -All front-end electronics are almost ready to be integrated into modules.

- -Currently three prototype DHPs have been produced with different technology and the first production version designed with a 65-nm CMOS has been delivered.

- -The full-scale prototype module shows promising results in IR-source and test beam.

#### Thank you for your attention.