# Review of the Phase 1 Pixel Upgrade Workshop

Robert Stringer (KU)

# Grindelwald

### Phase 1 Pixel TDR

- Internal CMS area: https://twiki.cern.ch/twiki/bin/ view/CMS/PixelPhase1TDR

- Public version for LHCC: https://cmsdocdb.cern.ch/cgi-bin/PublicDocDB/ShowDocument?docid=5669

- Sept. 18: "We learned today that the US DOE has approved Critical Decision 0 (CD0) for the US CMS Phase 1 Upgrade project. This means that DOE has accepted the upgrade as part of its "mission" and will start it along the path to final approval and funding. We still have many steps to go before we can start construction but this is a big first step."

# Working Groups

- Pilot System

- Power & DC-DC Conversion

- CO2 Cooling

- Testbeams

- Xray Testing

- Datalink

- FED

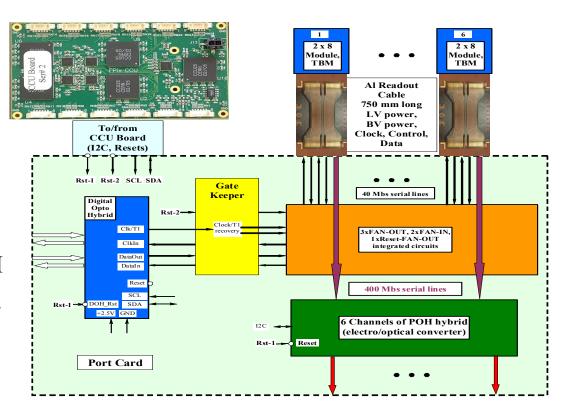

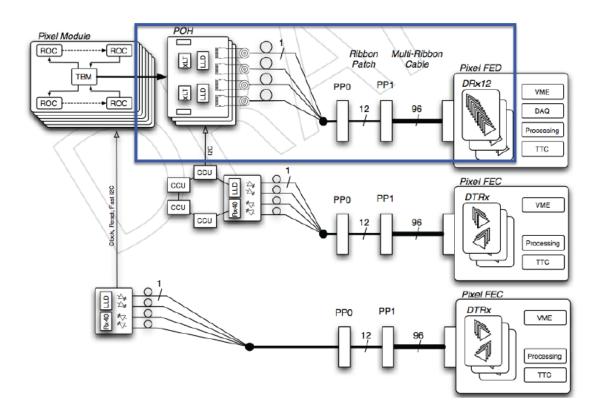

# FPix Readout for Pilot Disk (using TBM8, and aluminum readout cables)

- Pilot Run system will use:

- 2x8 detector module

- TBM8 with digital readout

- Aluminum readout cable

- A new Port card with up to 16 readout channels (4 POHs) (only 4 channels will be needed)

- Data are sent from detector modules to Port card via aluminum flex readout cables, and converted to optical signals there (4-channel POH hybrid)

- ROC registers download used DOH/ GateKeeper/TBM/ROC communication channel

- TPLL is used to recover commands from the Clock/Control channel

- Delay25 is used to align clock, commands, and data

- I2C slow control uses existing design of a CCU board (including resets)

Port Card uses the same architecture, as the current one, plus it incorporates FAN-IN/OUT ics, that used to be on the Adapter Board. Not shown are TPLL, and Delay25 ASICs

### DC-DC

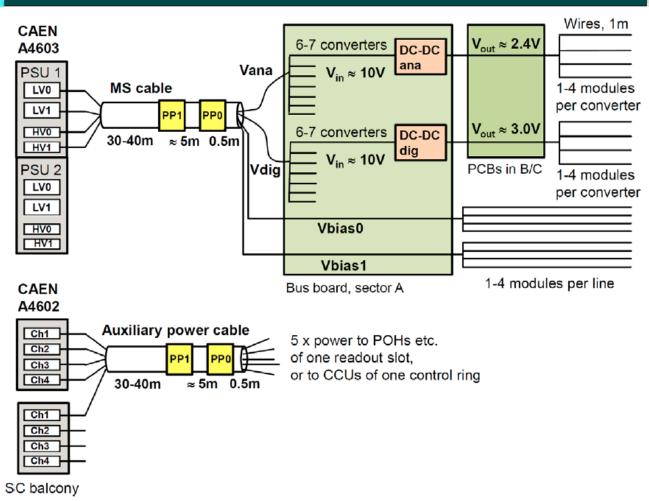

#### **Phase-1 Power System**

Katja Klein

Power WG Summary

3

### DC-DC

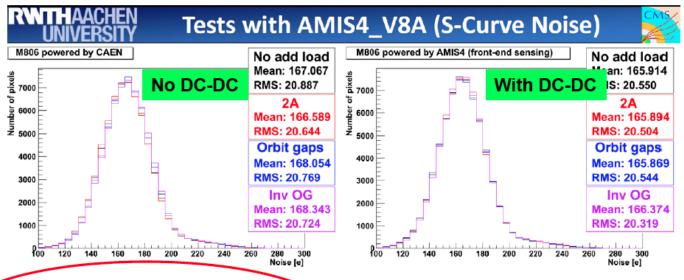

### System Tests with DC-DC Converters

#### Hardware configuration:

- Single module

- One pair of AMIS4\_V8A / equivalent CAEN

- Front-end sensing

#### Results:

- Noise with AMIS4 slightly lower (1e<sup>-</sup> / 0.6%) than with AMIS2

- With AMIS4 and (inv.) orbit gaps, no significant increase in noise

- With CAEN and const. load no significant increase in noise

- With CAEN and (inv.) orbit gaps, noise increases by ~ 1e<sup>-</sup> (0.6%)

7

#### Software configuration:

- Trimmed threshold = 60 Vcal DACs

- Use Vana and all other parameters from configuration with testboard

Katja Klein 29.08.2012 Jan Sammet -9 -

# CO2 Cooling

### Cooling plant (H. Postema – R. Becker)

Main components already ordered

31/8/12

# CO2 Cooling

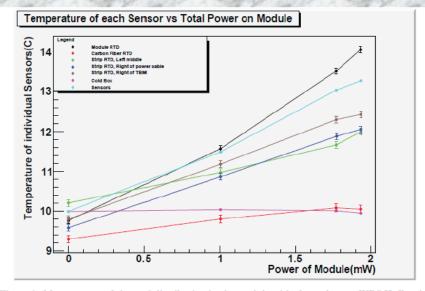

#### TESTS: $\Delta T$ between CO2 & sensor

CMS

air gap between ROCs and CFK filled with thermal paste (rad-hardness to be verified).

Figure 8: Measurement of thermal distribution in the module with thermal paste WPS II. For the highest power consumption, the temperature of the cabron fiber  $10\,^{\circ}$ C. The strips are even more consistent in temperature with a temperature of  $12\,^{\circ}$ C. The temperature of the silicon sensor is now  $13\,^{\circ}$ C. The HDI's temperature now is at  $14\,^{\circ}$ C.

Temperature rise from CFK to sensor ~3° (8.5 if no thermal paste), with module power of 2W

Extrapolation to max 6.5 W/module gives up to 27 C DT without paste (i.e. 10 C with paste)

Contact is done on a cold plate: plans to repeat with final CFK and small pipes

Pixel Upgrade WS Aug. 30, 2012

W. Bertl, PSI

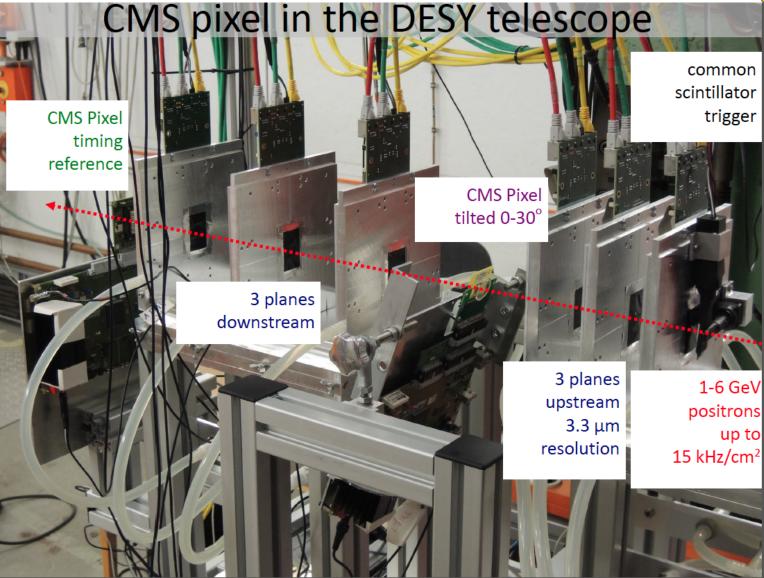

### **Testbeams**

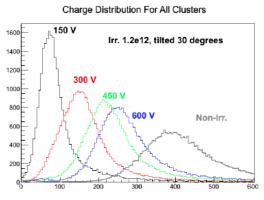

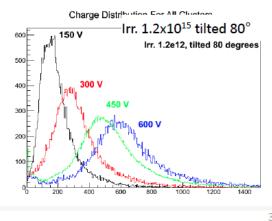

# Preliminary analysis: Pulse heights • We have looked at | Pulse heights | Pul

- irradiated sample with equivalent dose 1.2x10<sup>15</sup> p/cm<sup>2</sup>

- Temperature -18±1 °C

- The cluster pulse height increases with bias voltage

- Does not yet reach pulse height of non-irradiated sample at 600 V bias

D. Hits

### **Testbeams**

### **Testbeams**

#### CERN H4irrad: plans for October 24-28 test

July test readout

Get rid of Altera board For October test

#### Xilinx board standalone

- •bears connection to telescope anyway

- receives external triggers anyway

- •has GBit ethernet link to PC

- •happens to be the UK FED/FEC

- •development system (manpower!)

- needs new bridge board (ROC power)

- (prototype exists, partially tested)

- •needs more firmware

Kristian Harder

28/08/2012 Anna Peisert

# **Xray Testing**

#### T.Weiler (KIT)

## X-ray calibration at KIT

### Karlsnuher Institut für Technologie

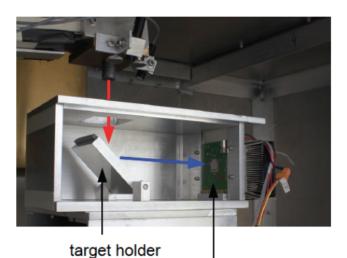

#### Test setup – X-Ray Tube

- Targets: Mo, Ag, In, Sn und Nd

- Excitation by continuous X-ray spectrum

- Flexible irradiation intensity,

U up to 60 kV, I = 2 33 mA

- High rates: up to 6.5 MHz/cm² → Measurements with random trigger without stretching the sensitive time ("clock stretch") possible

- Peltier element for temperature tar stabilization → essential for reproducibility

single chip sensor

Mainly used for investigations on rate dependencies of the signal height and ROC calibration

31/08/2012 A.Starodumov 4

# **Xray Testing**

## Tests with X-rays at ETHZ: Experiences and challenges

M.Rossini (ETH)

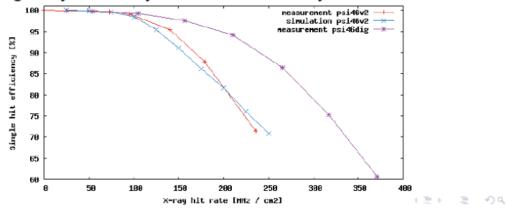

#### Single hit efficiency vs rate

Single hit efficiency is determined by reading out injected calibrate signals during x-ray irradiation.

- Should not be expected to be the same for particle tracks (no clustering).

- ► First simulation for x-rays shows similarity to measurement with PSI46v2, however not complete agreement.

- PSI46dig x-ray efficiency was not simulated yet.

#### Data Link: Module to FED

Data Link from Module to FED involves a number of components and subsystems, that will need to be working together in very reliable way.

# FED Session Roll-up

- uTCA FED development proceeding

- RAL DAQ board used in test beams

- Other developments proceeding until funding kicks it

- Should establish regular working group meetings

- · Work on detailed specifications and architecture

- Rate calculations (Mostly homework)

- Clear the FPiX inner disk needs 1 fiber/module

- Interesting rate variation within layers of BPiX

(Lyr1 ~30%; Lyr2 ~20%; Lyr3 ~15%; Lyr4 ~12%)

- How much do beam misalignments effect rates?

- How does present simulation compare with data radially?

- Is FPiX inner layer necessary?

- Increases eta acceptance, useful for Lumi possibly

- · Difficult to measure efficiency though

- Can always mask pixels if there is a rate emergency

- Should replace FPiX inner disk ~ if we replace layer 2

### Conclusions

- The Grindelwald Workshop was a very productive 4 days.

- Much more was discussed than I could cover here. If you're interested: <a href="https://indico.cern.ch/conferenceTimeTable.py?confld=196414#20120828">https://indico.cern.ch/conferenceTimeTable.py?confld=196414#20120828</a>

- PIRE research was presented/discussed during the workshop.

- Lots more to do! Potentially things for future PIRE projects.