# First experience with radiation-hard active sensors in 180 nm HV CMOS technology

Daniel Muenstermann (CERN) on behalf of the participating institutes: U Bonn, CERN, CPPM Marseille, U Geneva, U Glasgow, U Heidelberg, LBNL

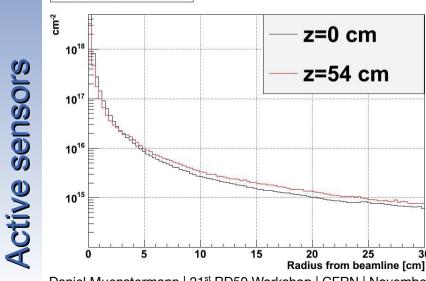

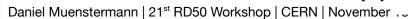

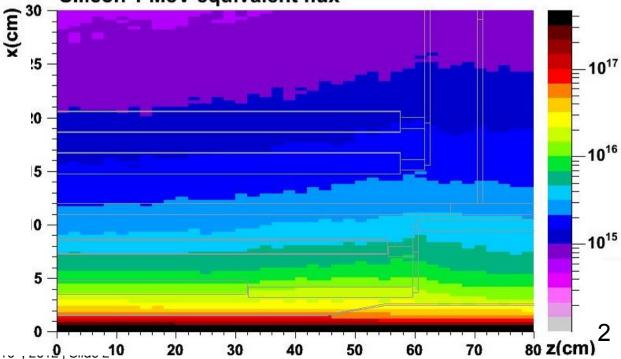

## Reminder: fluences at HL-LHC

- integrated luminosity: 3000 fb<sup>-1</sup>

- including a safety factor of 2 to account for all uncertainties this yields for ATLAS:

- at 5 cm radius:

- ~2•10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>

- ~1500 MRad

- at 25 cm radius

1 MeV neutron eq. predictions

- up to 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup>

- ~100 MRad

- several m<sup>2</sup> of silicon

#### Silicon 1 MeV-equivalent flux

## **Implications**

- High fluences: trapping dominant

- reduce drift distance, increase field  $\rightarrow$  reduce drift time:

- 3D sensors

- thin silicon

- Iow depletion depth 'on purpose':

- Iow(er) resistivity silicon

- dedicated annealing to increase N<sub>eff</sub>

- Large areas: low cost of prime importance

- industrialised processes

- Iarge wafer sizes

- cheap interconnection technologies

#### Idea: explore industry standard CMOS processes as sensors

- commercially available by variety of foundries

- Iarge volumes, more than one vendor possible

- 8" to 12" wafers

- Iow cost per area: "as cheap as chips"

- (partially too) low resistivity p-type Cz silicon

- thin active layer

- wafer thinning possible

## AMS H18 HV-CMOS

- Project initiated by Ivan Peric (U Heidelberg)

- Austria Micro Systems offers HV-CMOS processes with 180 nm feature size in cooperation with IBM

- biasing of substrate to ~60-100V possible

- substrate resistivity ~20 Ohm\*cm  $\rightarrow N_{eff} > 10^{14}/cm^3$

- radiation induced N<sub>eff</sub> insignificant even for innermost layers

- depletion depth in the order of 10-20  $\mu m \rightarrow$  signal ~1-2 ke<sup>-</sup>

- on-sensor amplification possible and necessary for good S/N

- key: small pixel sizes  $\rightarrow$  low capacitance  $\rightarrow$  low noise

- additional circuits possible, e.g. discriminator

- beware of 'digital' crosstalk

- full-sized radiation hard drift-based MAPS feasible, but challenging

- aim for 'active sensors' in conjunction with rad-hard readout electronics first

#### Scope of the talk:

- Briefly repeat the concept

- Summarise results with MAPS test chips

- Present first measurements with the active sensor prototype chip

- Outlook: how small can pixels get?

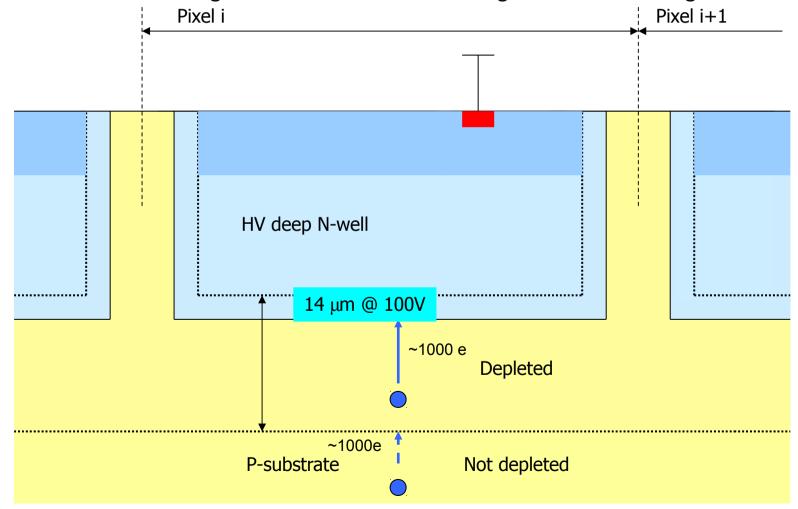

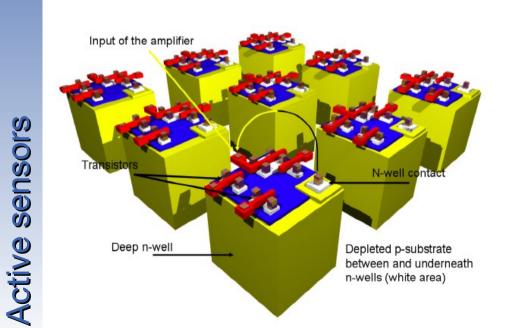

## A HV-CMOS sensor...

- essentially a standard n-in-p sensor

- depletion zone 10-20 µm: signal in the order of 1-2ke<sup>-</sup>

- challenging for hybrid pixel readout electronics

- new ATLAS ROC FE-I4 might be able to reach this region but no margin

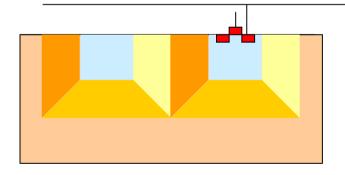

The depleted high-voltage diode used as sensor (n-well in p-substrate diode)

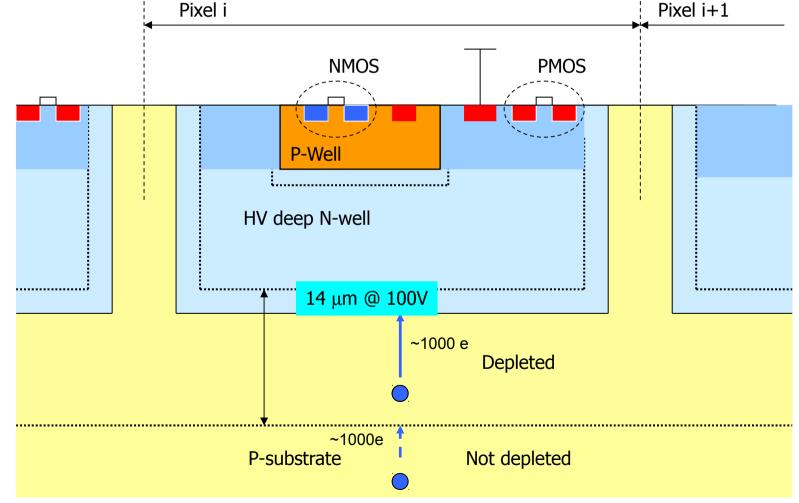

## ...including active circuits: smart diode array (SDA)

- implementation of

- first amplifier stages

- additional cuircuits: discriminators, impedance converters, logic, ...

- deep sub-micron technology intrinsically rad-hard

CMOS electronics placed inside the diode (inside the n-well)

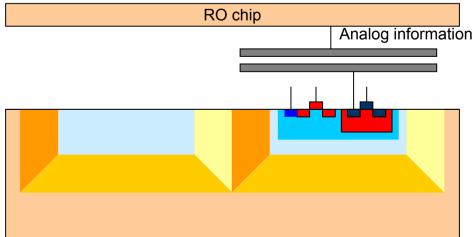

Several test-chips already existing, see backup slides for more detailed results

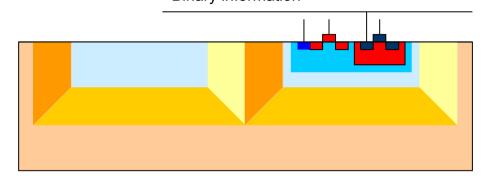

Binary information

Analog information

SDA with frame readout (simple PMOS pixels) HVM chip

SDA with sparse readout ("intelligent" CMOS pixels) HV2/MuPixel chip

SDA with capacitive readout ("intelligent" pixels) Capacitive coupled pixel detectors CCPD1 and CCPD2 detectors

\*If work, these features would allow to operate the readout chip without any

Da

16<sup>th</sup>, 2012 | Slide 8

## From MAPS to active sensors

- Existing prototypes would not suitable for HL-LHC, mainly because

- readout too slow

- time resolution not compatible with 40 MHz operation

- high-speed digital circuits might affect noise performance

- Idea: use HV-CMOS as sensor in combination with existing readout technology

- fully transparent, can be easily compared to other sensors

- can be combined with several readout chips

- makes use of highly optimised readout circuits

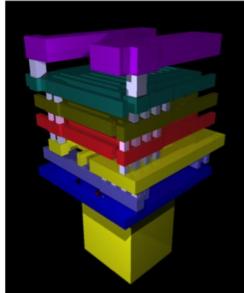

- can be seen as first step towards a sensor being integrated into a 3Dstacked readout chip (not only analogue circuits but also charge collection)

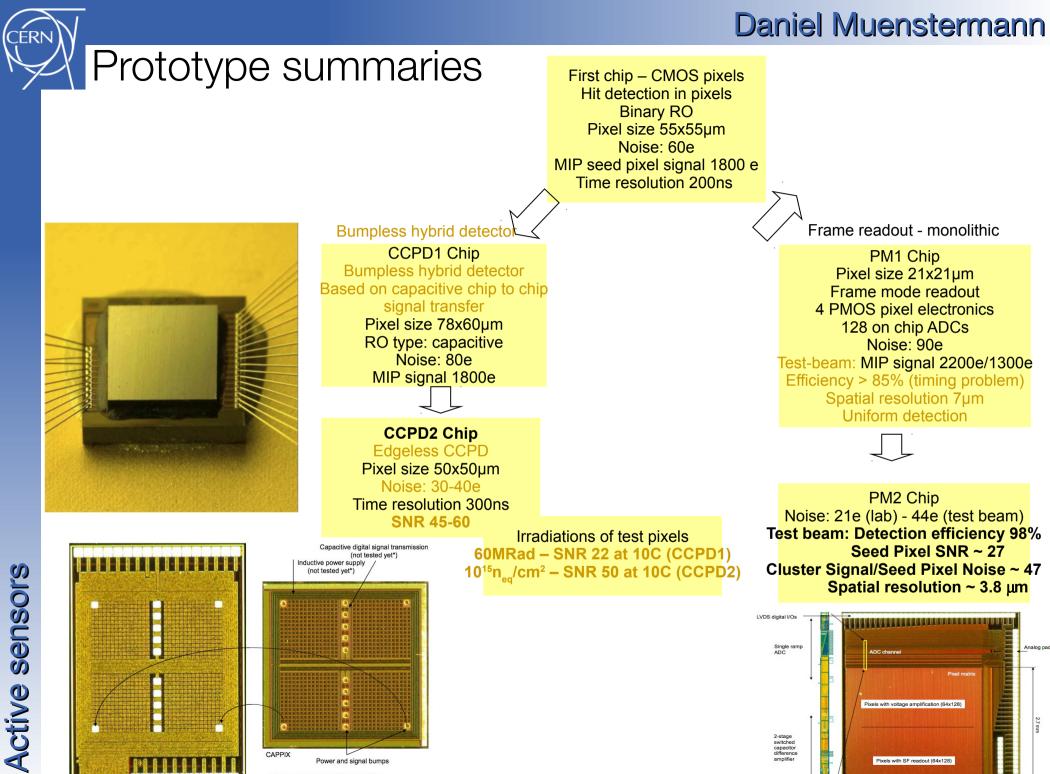

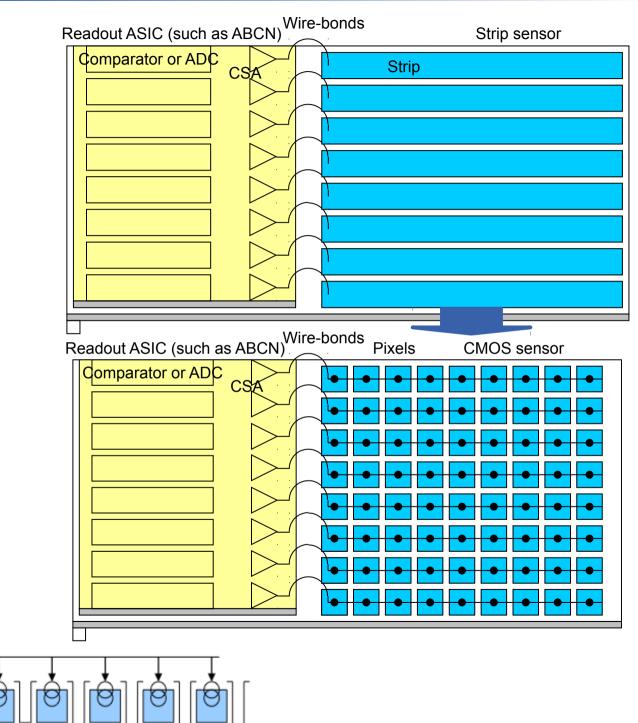

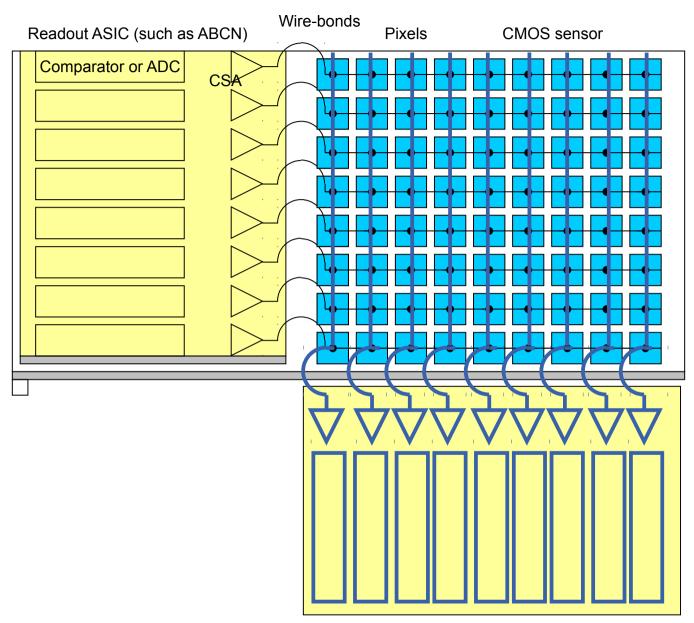

- Basic building blocks: small pixels (low capacitance, low noise)

- can be connected in any conceivable way to match existing readout granularity, e.g.

- (larger) pixels

- strips

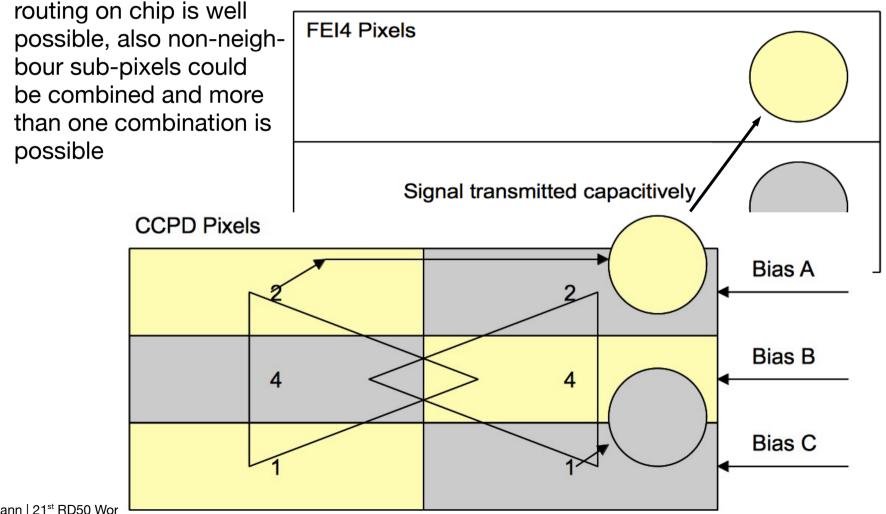

## Pixels: sizes and combinations

- Possible/sensible pixel sizes: 20x20 to 50x125 µm

- 50x250 µm (current ATLAS FE-I4 chip) too large

- combine several sensor "sub-pixels" to one ROC-pixel

- sub-Pixels encode their address/position into the signal as pulse-heightinformation instead of signal proportional to collected charge

Active sensors

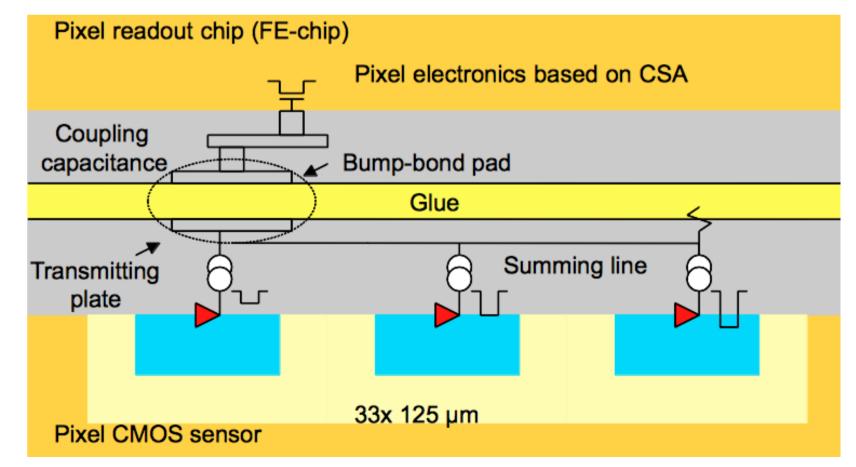

## Pixels: bonding?

- Only reason not to use AC coupling with pixel sensors up to now was small coupling capacitance in association with low signal

- amplification possible, hence AC transmission not a problem at all

- allows to get rid of costly bump-bonding

- variations in glue thickness are handled by tuning procedures and offline corrections if necessary

- Easiest idea would be to simply sum all pixels within a virtual strip

- Hit position along the strip can be again encoded by pulse height for analogue readout chips (e.g. Beetle)

Summing line

Active sensors

## Strips

- Signals are digital so multiple connections are possible, e.g.

- "crossed strips"

- strips with double length but only half the pitch in r-phi

## Reticule size/stitching

- Sensor size is currently limited by reticule size of ~2x2 cm

- however, the yield should be excellent (very simple circuit, essentially no "central" parts) so it might be interesting to cut large arrays of sensors from a wafer and connect individual reticules by

- wire-bonding

- post-processing (one metal layer, large feature size)

- There are HV-CMOS processes/foundries which allow for stitching

- Very slim dicing streets

- Gaps between 1-chip modules could be rather narrow

|                               | Chip2 |       |

|-------------------------------|-------|-------|

| Pads Chip to chip connections | Chip1 |       |

| Reticle1                      | Reti  | icle2 |

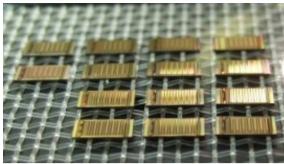

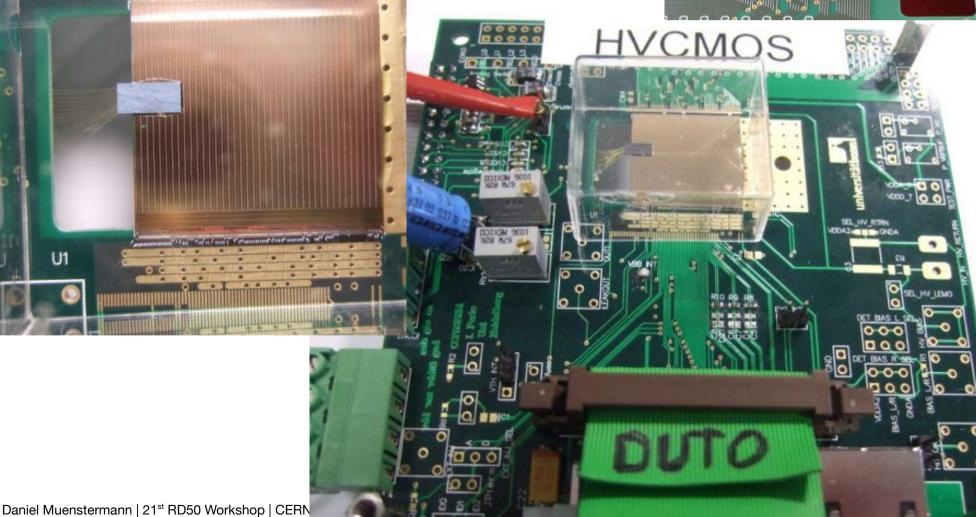

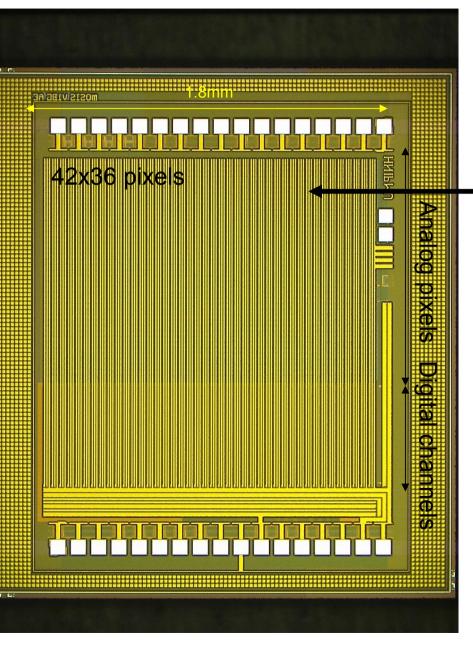

## HV2FEI4

A combined active strip/pixel sensor was designed and produced

Tune DAC

Amplifier

33 µm

Comparator

- strips compatible with ATLAS ABCN and LHCb/Alibava Beetle

- pixels match new ATLAS FE-I4 readout chip

- capacitive coupling

- bump-bonding possible

- Structure

- 6 sub-pixels form basic element

- each 33 x 125 µm

- connect to 2 FE-I4 pads

- form a 100 µm pitch strip

- small fill factor future options:

- more circuits possible

- smaller sub-pixels

## HV2FEI4

- Chip size: 2.2mm x 4.4mm

- Pixel matrix: 60x24 (sub-)pixels of 33 µm x 125 µm

- 21 IO pads at the lower side for CCPD operation

- 40 strip-readout pads (100 µm pitch) at the lower side and 22 IO pads at the upper side for (virtual) strip operation

- On chip bias DACs

- Pixels contain charge sensitive amplifier, comparator and tune DAC

- Configuration via FPGA or  $\mu$ C: 4 CMOS lines (1.8V)

#### 3 possible operation modes

- standalone on test PCB

- strip-like operation

Sensors

*<u>ctive</u>*

pixel (FE-I4) readout

#### **Daniel Muenstermann**

IO pads for CCPD operation

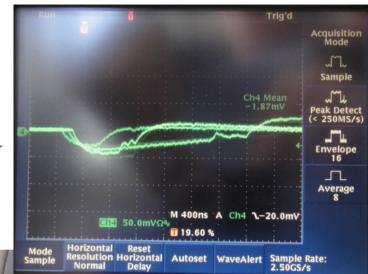

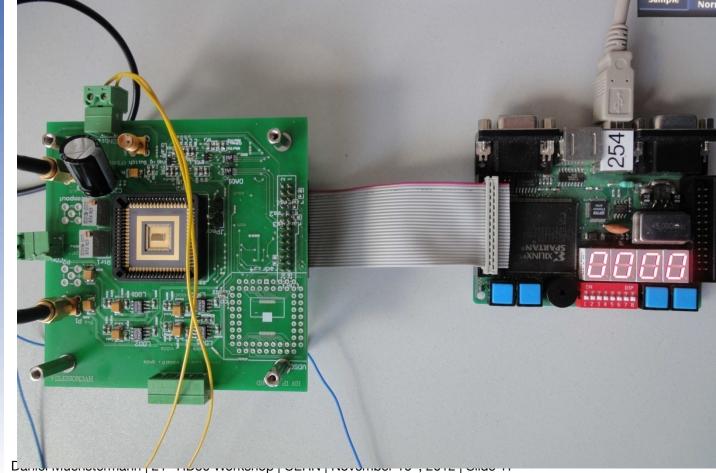

## HV2FEI4: characterisation

Standalone tests

Active sensors

- first measurements at Mannheim

- behaviour as expected

- monitor output showing physics (radioactive source events)

Daniel Muenstermann | 21<sup>st</sup> RD50 Workshop | CERN | November 16<sup>th</sup>, 2012 | Slide 18

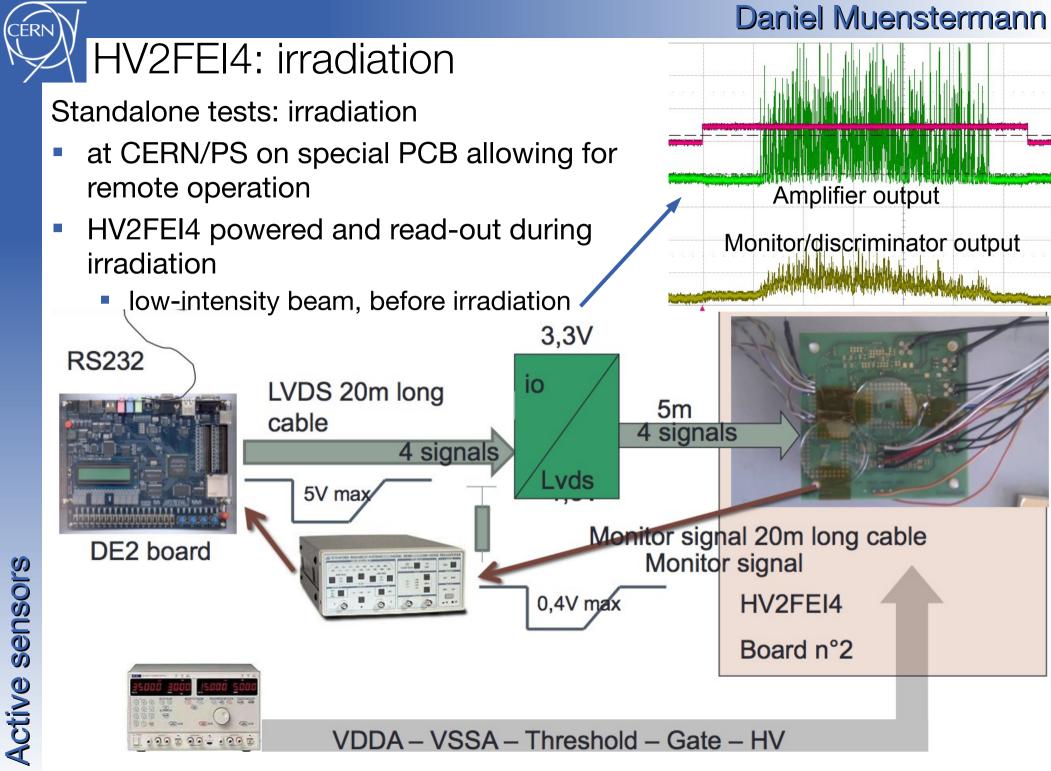

## Results after 144 MRad

- The rate of detected particles depends on the high voltage bias, superposition of two effects:

- Positive effect: The increase of HV bias leads to an increase of the depleted region depth => better detection efficiency.

- Negative effect: The increase of the leakage current leads to a signal loss.

- Measured leakage current dependence on the high voltage bias

- Leakage current depends on the volume of the depleted region

Daniel Muenstermann | 21<sup>st</sup> RD50 Workshop | CERN | November 16<sup>th</sup>, 2012 | Slide 19

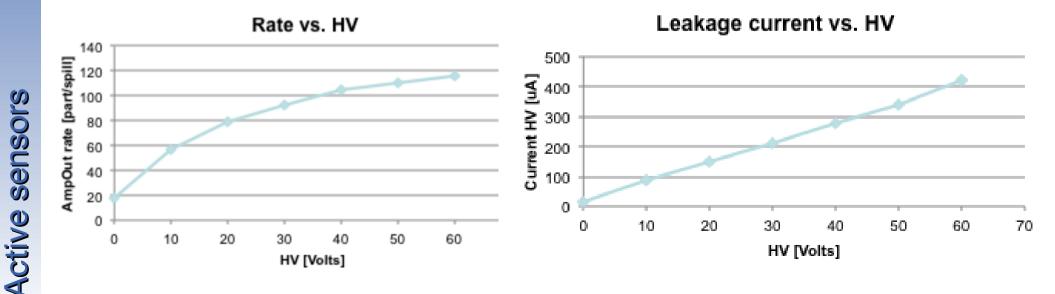

## Results after 200 MRad

Preliminary irradiation results after ~200 Mrad (about IBL fluence!)

- significant radiation effects seen

- discriminator output decreases with current settings after ~110 MRad

- "lower" count rate, but physics still seen

- high gain settings failing

- Iow gain still works

- strong leakage current increase (as expected): nA → ~mA

- full characterisation difficult:

- Iimited access

- radiation vs. temperature effects

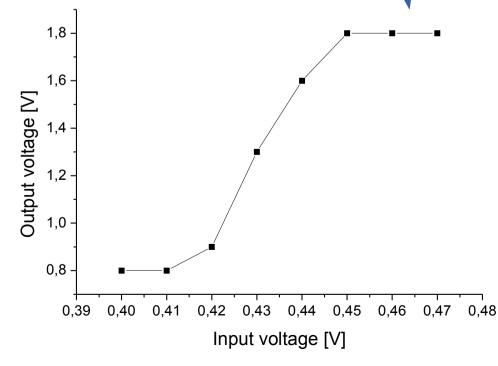

## Results after 380 MRad and $\sim 8 \times 10^{15} \text{ n}_{eq}/\text{cm}^2$

Preliminary irradiation results:

- Output of the amplifier: the chip still works, particles are measured when the chip is in the beam

- Comparator characteristics

- many open questions, need better understanding

Daniel Muenstermann | 21<sup>st</sup> RD50 Workshop | CERN | November 16<sup>th</sup>, 2012 | Slide 21

Active sensors

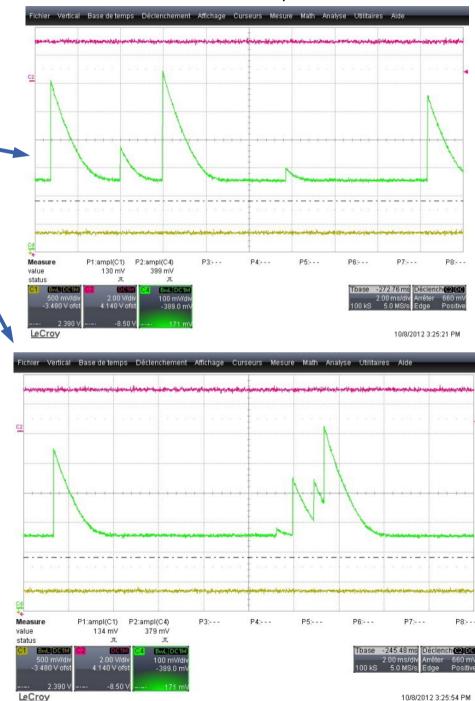

## HV2FEI4: strip readout

- ABCN readout being set-up

- Beetle readout in place, but issues with noise pickup

- also present if HV2FEI4 not powered...

- configuration works, "strips" can be switched on/off

- position-encoding works:

- monitor output on scope

- same principle on strip readout pads

Active sensors

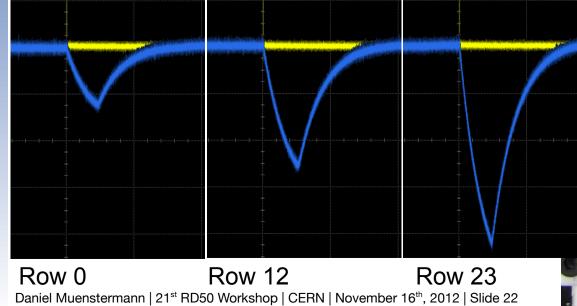

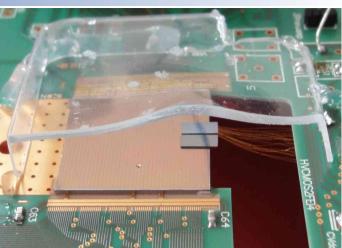

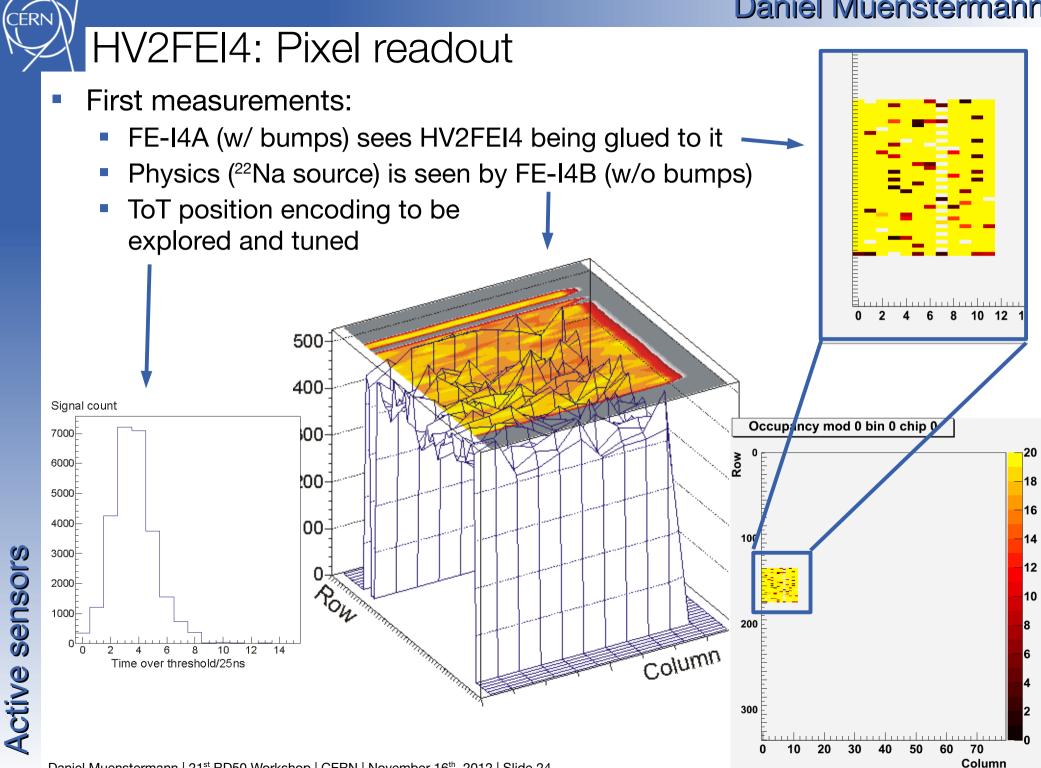

## HV2FEI4: Pixel readout

- First HV2FEI4s glued (!) to FE-I4A and FE-I4B

- HV2FEI4 wirebonds done through hole in PCB

- could be bumps or TSVs later

## Outlook: back to MAPS?

- 3 aspects for further improvement:

- reduce pixel sizes further how far can one go?

- reduce thickness of "module" to save radiation length

- reduce cost for large scale usage of a system with pixel-resolution

#### smaller pixel sizes

- go to smaller feature size

- digital part directly scales

- analogue part at least partially

- lower capacitance

- even lower noise

- less preamp-power (but of course more channels)

- interconnect

- no bump-bonding for pixels in the order of 10x10 µm (maybe SLID)

- capacitive coupling, but also here very dense

- go to 3D interconnect? Maybe even 180nm HV-CMOS to 130nm CMOS?

- go towards drift-based MAPS? In the end it's all a CMOS flavour...

Active sensors

## CMOS MAPS

- What feature size/pixel size should be used?

- test chips in 350 and 180nm HV-CMOS had different pixel sizes and varying levels of intelligence, but were generally not fast enough/did not have time stamps with 40 MHz

- FE-I4 in 130nm has a cell size of  $50x250 \text{ um} \rightarrow \text{probably too large}$

- 65nm aimed for by several chip developers within ATLAS

- suitable as sensor/MAPS?

- 65nm process features

Active sensors

- 20 Ohm\*cm resistivity (!)

- deep n-wells (not as deep as in HV processes, but might do)

- work on 65nm chips has anyway started within ATLAS  $\rightarrow$  synergy

- first test chip containing tiny pixels (standard n-well) already done:

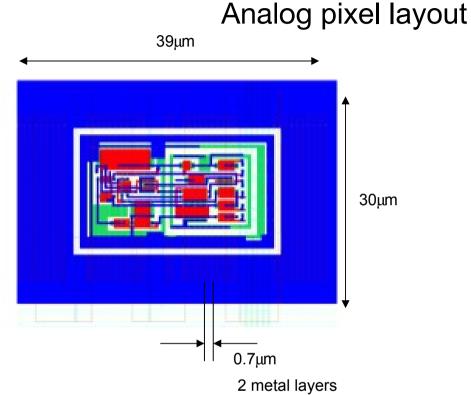

## 65nm test chip

- Tiny pixels (2.5 µm pitch) with charge storage read-out sequentially

- obviously not for HL-LHC, but 2.5 µm shows what is possible

- 1 µm gaps between pixels, ~1V bias voltage (!)

- minimal charge sharing due to very shallow depetion zone: <sup>22</sup>Na clusters are 2-3 pixels

Slic

- spatial resolution (~binary) of  $2.5\mu m/\sqrt{12}=0.7\mu m$  (!!)

- <sup>55</sup>Fe-shadow of a 16 µm thick golden bond-wire

#### **Daniel Muenstermann**

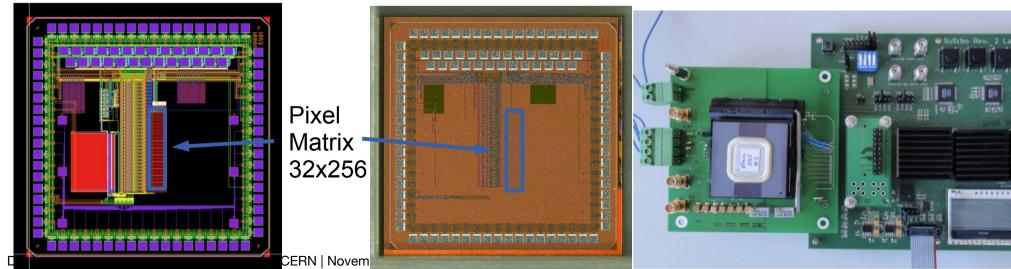

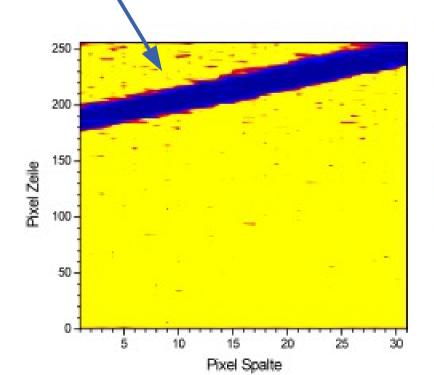

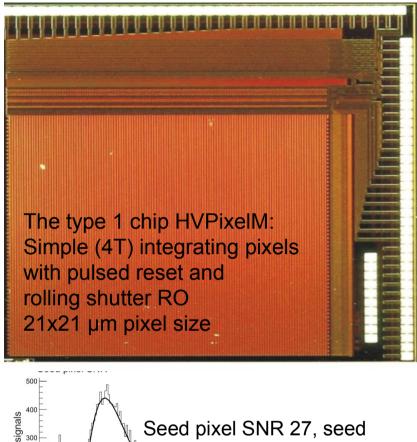

## HV-CMOS technology: Mu3e-chip

Monolithic HV-CMOS-chip for the mu3e-experiment at PSI

- Test-chip dimensions: 42x36 pixels

- Pixel size 39x30 µm

- separated digital and analogue blocks

- signal amplitude can be measured as ToT

Daniel Muenstermann | 21<sup>st</sup> RD50 Workshop | CERN | November 16<sup>th</sup>, 2012 | Slide 28

Reverse bias [V]

## Mu3e-chip: charge multiplication?

- LED light pulses can be detected

- Signal amplitude was measured as ToT

- Above about 60V bias voltage, an exponential increase in ToT signal has been observed

- Time over threshold [µs] charge multiplication? usable effect? 11 ¥ investigating... 10 9 8 7 6 5 20 40 60 80 0

## Realistically – what is desirable?

- resolution of tracks in dense jets would be highly welcome for various reasons

- very thin depletion zone would help to avoid large clusters at high eta in innermost layers

- realistic pixels sizes (area matters, not shape can be sqare or rectangular)

- ~10x10 µm with little intelligence, but with LHC-speed, sparse readout, ...

- ~20x40 µm should be able to contain all features one could wish for

- track-trigger applications?

- current ATLAS concepts work with short-strip layers without stereo-angle

- 3 double-layers necessary due to fake-rate

- improved resolution (in particular in z) would significantly reduce this

- no loss of z-information for tracking purposes

- better track resolution  $\rightarrow$  better spacer thickness/pT resolution ratio

- MAPS-chips could already contain the combination logic

| MAPS-1 |                 |  |

|--------|-----------------|--|

|        | Spacer          |  |

| MAPS-2 |                 |  |

|        | Stave with Flex |  |

Daniel Muenstermann | 21<sup>st</sup> RD50 Workshop | CERN | November 16<sup>th</sup>, 2012 | Slide 30

## Conclusions

- HV-CMOS processes might yield radiation-hard, low-cost, improvedresolution, low-bias-voltage, low-mass sensors

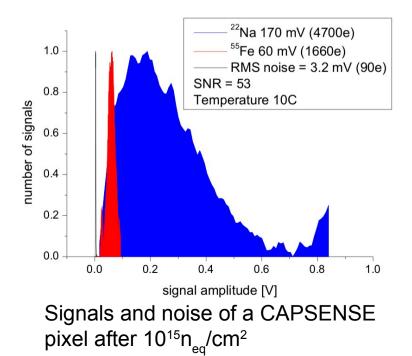

- First test chips indicate rad-hardness up to at least 1e15 n<sub>eq</sub>/cm<sup>2</sup>

- general principles suggest rad-hardness up to full HL-LHC fluence

- Process can be used for

Sensors

Active

- 'active' n-in-p sensors

- drift-based MAPS chips (baseline for µ3e-Experiment at PSI)

- First active sensor prototypes being explored within ATLAS

- capacitively coupled pixel sensors first results look promising

- "virtual" strip sensors z-position encoding working

- Irradiation and testbeam campaign ongoing

- goal: up to HL-LHC fluences at CERN-PS and Ljubljana

- Outlook: 65nm CMOS process for sensors?

- test array existing with 2.5 μm pitch, though no intelligence

- only ~µm depletion, but S/N still good (low capacitance)

- should try deep n-well allowing more bias voltage and some more realistic pixel size/intelligence

- Possibly charge amplification seen under investigation

## Backup slides

CERN

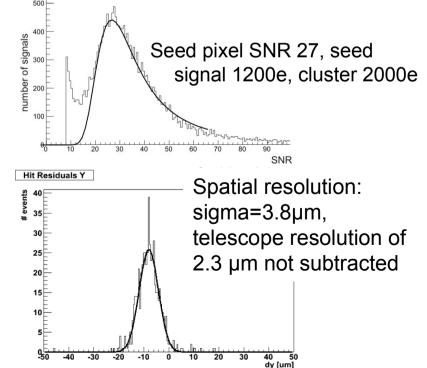

## Test beam results: monolithic 📠

- excellent resolution

- very good S/N ratio

- efficiency limited by readout artifacts:

- column-based readout

- row not active during readout

- data analysis did not correct for this

- very small chip  $\rightarrow$  low statistics

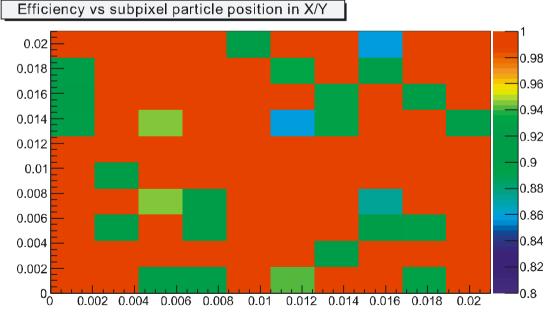

Efficiency vs. the in-pixel position of the fitted hit. Efficiency at TB: ~98% (probably due to a rolling shutter effect)

## CPPD prototype results

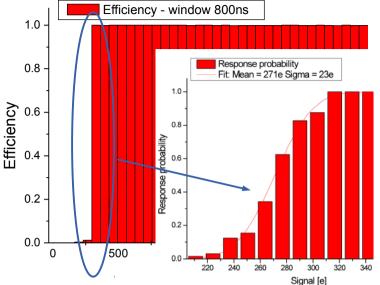

- excellent noise behaviour: stable threshold at ~330 electrons

- good performance also after irradiation

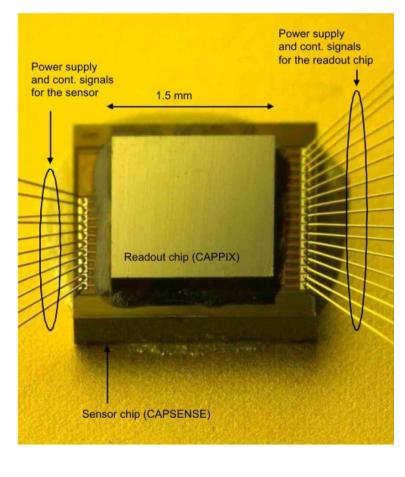

## CAPPIX/CAPSENSE edgeless CCPD 50x50 µm pixel size

Daniel Muenstermann | 21st RD50 Workshop | CERN | November 16th, 2012 | Slide 34

Detection efficiency vs. amplitude Detection of signals above 330e possible with >99% efficiency.

## CPPD prototype results

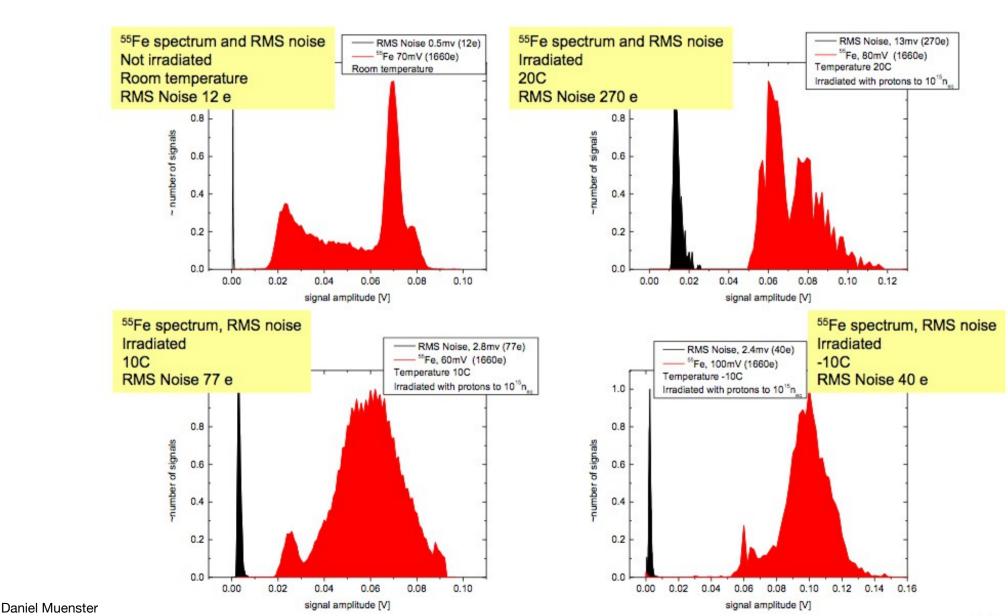

- Irradiation with 23 MeV protons: 1e15 neq/cm2, 150MRad

- FE-55 performance recovers after slight cooling