# BPM stripline acquisition in CLEX

Sébastien Vilalte

Acquisition in base band:

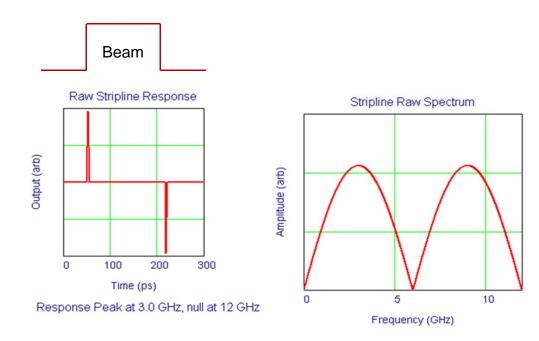

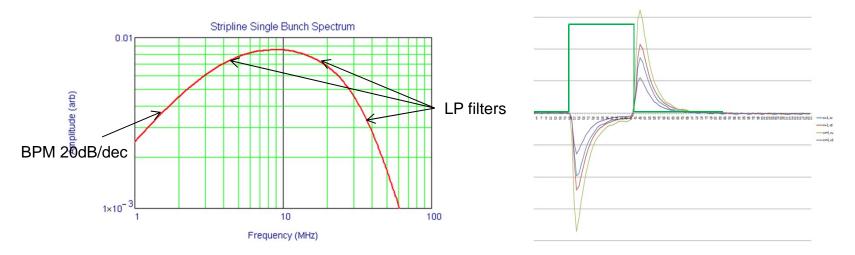

BPM transfer function  $\sim sin(\pi f/6GHz)$ .

$\rightarrow$  for low frequencies sin( $\pi f/6GHz$ )~f, BPM behaves as a derivative part (kind of 1<sup>st</sup> HP filter).

<u>Output BPM signal:</u> beam edges result in pulses at the beginning and at the end of the train. (intermediate pulses if deviation)

Pulses too short to be acquired: integration by filtering.

$\rightarrow$  For a ~240ns train length, a "window" about 4-40MHz is a good choice.

Implementation of LP filters at 4MHz, 20MHz (1<sup>st</sup> order) and 35MHz (2<sup>nd</sup> order).

$\rightarrow$  No local process, electrodes acquisition & raw data transmission.

$\rightarrow$  Knowing the (BPM + electronics) response, the train can be reconstructed by deconvoluting the signal.

Need to measure/calibrate the transfer function (BPM+electronics): not simple...

Acquisition has to be synchronous with the machine.

#### LAPP developments for CLIC module / CLEX:

- $\rightarrow$  Local shaping and acquisition of the BPM, synchronous with the machine.

- $\rightarrow$  Synchronous network based on a single optical link (no copper).

- $\rightarrow$  Interface and software: control and process (position reconstruction...)

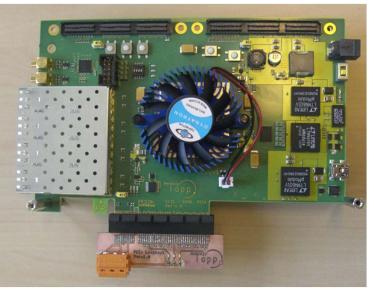

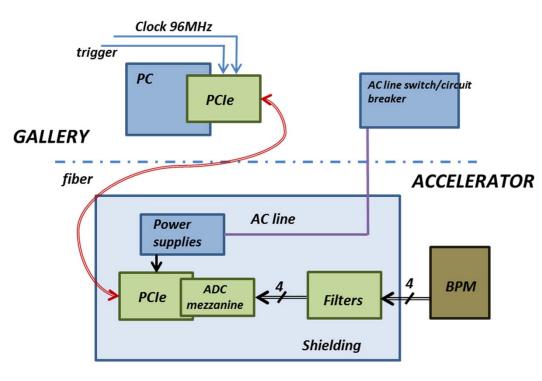

## PCIe Board X8: synchronous optical network.

<u>Versatile board:</u> In a PC or in stand-alone. Can host 2 mezzanines: local acquisition in CLEX.

→ forces the optical carrier frequency to a multiple of the machine clock. Transmits the trigger. Local reconstruction of the clock.

4 SFPTrigger and Clk inputs.2 mezzanines connectors.

PCIe board

Sébastien VILALTE

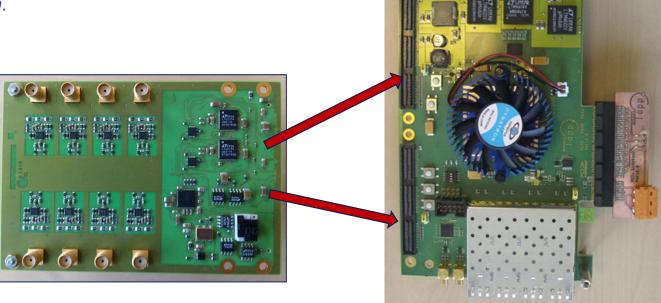

## Acquisition mezzanine:

<u>#1 prototype</u>: generic, gains and attenuators. Tests of components and principles (amps, ADC, synchronisation...)

$\rightarrow$  8 channels, Fs=96Msps (CTF3 clock), 11,7bits.

Used with external lumped elements filters for BPM acquisition.

## PCIe board used for:

→ front-end acquisition: stand alone, host the ADC mezzanine, recovers clk & trigger. tunable acquisition window length up to 85µs.

→ back-end acquisition: plugged in a computer, clk & trigger inputs, manages the synchronous network.

## Computer software & processing:

- $\rightarrow$  driver for the PCIe boards: trigger delay, attenuators switches, controls...

- $\rightarrow$  FFT processing, beam reconstruction (deconvolution).

- $\rightarrow$  user interface: options, controls, display windows...

Tool developped in order to test the synchronous architecture & BPM. Drawback: yet no link with the CERN network. All electronics shielded, CERN radiation monitoring.

Architecture tested with success for BPM tests in lab (wire method). Good results in beam reconstruction. All installed and tested in gallery/CLEX last weeks.

## Future

#### Beam acquisition:

tests of electronics and tuning. participation to the BPM qualification. Radiation tests.

#### Future developments:

#### New acquisition mezzanine:

192Msps ADC, filters implementation, digital attenuators. Implementation of an auto-trigger: more flexible and compatible with future back-end. Implementation of a DAC chain in order to test calibration  $\rightarrow$  transfer function issue.

Network: collaboration with CO for integration in the CERN infrastructure (FESA class):

CO develops  $\mu$ TCA back-end solution with synchronized fiber and common protocol  $\rightarrow$  Data recovering on the CERN network.

$\rightarrow$  Developments for CLIC module.

Study of remote FPGA reprogramming: benefit for configurations and radiation hardness.

Next instrument acquisition:

collaboration to the next BPM...

# references

Technical notes:

Drive beam stripline BPM electronics and acquisition <u>http://hal.in2p3.fr/in2p3-00778069</u>

Study of the CLIC module front-end acquisition and evaluation electronics: <u>http://hal.in2p3.fr/in2p3-00666173</u>