# The New ROD Complex (NRC)

For the ATLAS CSC Electronics

# **Conceptual Design Report**

Document Version: Document Issue: Document Edition: Document Status: Document ID: Document Date:

1.1 1 English First release to reviewers XXX-TD-xxxxx September 23, 2012

This document has been prepared using the Software Documentation Layout Templates that have been prepared by the IPT Group (Information, Process and Technology), IT Division, CERN (The European Laboratory for Particle Physics). For more information, go to http://framemaker.cern.ch/.

### Abstract

This document describes a joint SLAC National Accelerator Laboratory and UCI (University of *California at Irivine*) design proposal, which addresses the need for a replacement of the current set of ATLAS CSC RODs (Read-Out-Drivers). The current set is not simply a collection of VME boards, but is instead composed of a complex aggregate of *hardware* (PCB boards, VME crates, power supplies), *firmware*<sup>1</sup> and *software*. It is that aggregate, not just its 9U VME boards which is to be replaced. We reference that aggregate as the ROD *Complex*, its existing implementation as the Current ROD Complex and its replacement as the New ROD Complex or NRC. The replacement is driven solely by the need to address performance limitations of the current complex. Those limitations are described in [16] and it is those limitations that must be addressed over the LHC's first long shutdown. There are neither requirements to add to or subtract from the functionality of the current complex. Therefore, there is a strong desire to satisfy those performance limitations within the constraints imposed by the complex's current functionality as well as its external interfaces. In short, the proposal must satisfy performance requirements, do so within its external interfaces and without compromise of current functionality, and establish robust and reliable operation before data taking restarts after the long shutdown.

### Intended audience

The major impetus for this document is the upcoming conceptual design review and subsequently, its principal audience is that review's committee. However, the document also serves as the initial blueprint for its corresponding design and may therefore, be profitably read by the audience responsible for its implementation.

### **Conventions used in this document**

Certain special typographical conventions are used in this document. They are documented here for the convenience of the reader:

- Acronyms are shown in small caps (*e.g.*, SLAC or CSC).

- C++ coding statements are shown in Courier bold (*e.g.*, RIGHT\_FIRST or LAYER\_MASK)

<sup>1.</sup> Where here the term *firmware* is meant to express the coding languages used in FPGAs.

### References

- 1 G. Aad et al. [ATLAS Collaboration], The ATLAS Experiment at the CERN Large Hadron Collider, J. Inst. 3 S08003 (2008), pp. 178-186. Describes the ATLAS Experiment, Muon spectrometer, TDAQ, Cathode Strip Chambers and front-end electronics. A copy is available here: http://www.iop.org/EJ/article/1748-0221/3/08/S08003/jinst8\_08\_s08003.pdf

- 2 P. O'Connor et al., READOUT ELECTRONICS FOR A HIGH-RATE CSC DETECTOR, Fifth Workshop on Electronics for LHC Experiments (Snowmass 1999). Describes the front-end electronics, but some details have changed. ATLAS detector paper has the up-to-date information. A copy is available here: https://twiki.cern.ch/twiki/pub/Atlas/CscDocuments/leb99\_oconnor.pdf

- 3 Gough Eschrich [for the ATLAS Muon Collaboration], Readout Electronics of the ATLAS Muon Cathode Strip Chambers, in Proceedings of the Topical Workshop on Electronics for Particle Physics (TWEPP08), Naxos, Greece, 15-19 September 2008, CERN Yellow Report CERN-2008-008 (also available as CERN-ATL-COM-MUON-2008-018). Most up-to-date description of CSC readout, emphasis on the off-detector electronics. A copy is available here: https://twiki.cern.ch/twiki/pub/Atlas/CscDocuments/TWEPP08.pdf

- 4 D. Hawkins, ATLAS Particle Detector CSC ROD Software Design and Implementation, CERN-ATL-COM-MUON-2006-002. DPU software description; extract from Donovan's thesis. A copy is available here: http://positron.ps.uci.edu/~ivo/ATLAS/DPU\_Documentation.pdf

- 5 ATCA short specification: http://www.picmg.org/pdf/picmg\_3\_0\_shortform.pdf

- 6 ATCA PICMG 3.0 specification: http://www.picmg.org/v2internal/specifications.htm

- 7 ASIS 5-slot shelf specification (no longer in production?): http://www.asis-pro.com/

- 8 SNAP-12 MSA: http://www.physik.unizh.ch/~avollhar/snap12msa\_051502.pdf

- 9 Data sheet for Micrel Ulta-Precision 1:8 CML FANOUT BUFFER WITH INTERNAL I/O TERMINATION. Precision Edge SY58031U

- 10 MPO/MTP cable. A Very Short Reach (VSR) OC-192 four fiber Interface based on Parallel Optics. Implementation Agreement OIF-VSR4-03.0

- 11 Yazaki LC connector product specification. DOC No. OCD-EE-401-1 Version 1.2, July07

- 12 Pulser Calibration Board: D. Tompkins, "CSC Pulser rev. H", https://twiki.cern.ch/twiki/pub/Atlas/CscPulser/CSC\_Pulser\_H.pdf

- 13 A. Anjos, H. P. Beck, B. Gorini, W. Vandelli, "The raw event format in the ATLAS Trigger & DAQ", https://edms.cern.ch/file/445840/4.0e/eformat.pdf

| 14 | CSC Event Format:<br>http://positron.ps.uci.edu/~schernau/ROD/2rt/CSCDataFormat.html                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 | Private communication David Francis (September 4th, 2012)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16 | The New ROD Complex (NRC) Requirements. V0.4 Raul Murillo-Garcia<br>https://indico.cern.ch/getFile.py/access?contribId=0&resId=0&materialId=slides&confI<br>d=208888                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17 | PICMG 3.8:<br>http://www.picmg.org/v2internal/resourcepage2.cfm?id=2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18 | IPMI specification:<br>http://www.intel.com/design/servers/ipmi/spec.htm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19 | Private communication, Markus Joos (September 4th, 2012)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20 | SFP Committee. INF-8074i Specification for (Small Formfactor Pluggable) Transceiver.<br>Rev 1.0 May 12, 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21 | Kugel, A. et al., ATLAS ROBIN User Manual, CERN, ATL-DQ-ON-0018, Apr<br>2006, https://edms.cern.ch/file/719553/1/robinUserManual.pdf,<br>Cranfield, R. et al., The ATLAS ROBIN, Journal of Instrumentation, JINST 3<br>T01002, Jan 2008, http://dx.doi.org/10.1088/1748-0221/3/01/T01002,<br>Crone, G. et al., The ATLAS ReadOut System - performance with first data and<br>perspective for the future, Acc. for publication in proceedings of The 1st international<br>conference on Technology and Instrumentation in Particle Physics, Tsukuba,<br>Japan, Mar 12-172009,<br>http://cdsweb.cern.ch/record/1193091/files/ATL-DAQ-PROC-2009-025.pdf |

| 22 | http://positron.ps.uci.edu/~schernau/sparse.ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23 | http://positron.ps.uci.edu/~pier/csc/CTM/CTM_ReferenceManual_01.pdf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24 | http://positron.ps.uci.edu/~pier/csc/ROD_ASMII_Interface0.pdf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25 | http://hsi.web.cern.ch/hsi/s-link/devices/hola/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26 | O. Boyle1, R. McLaren and E. v. der Bij, "The S-LINK Interface Specification",<br>https://edms.cern.ch/file/110828/4/s-link.pdf<br>http://hsi.web.cern.ch/HSI/s-link/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27 | http://subversion.apache.org/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28 | https://svnweb.cern.ch/cern/wsvn/muondaq?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 29 | ATLAS CSC wiki, https://twiki.cern.ch/twiki/bin/viewauth/Atlas/CathodeStripChambers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 30 | SLAC Detector R&D DAQ wiki,<br>https://confluence.slac.stanford.edu/display/CCI/DAT+Home                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 31 | RTEMS Real Time Operating System, http://www.rtems.com/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32 | http://www.xilinx.com/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 33 | http://en.wikipedia.org/wiki/VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 34 | http://www.gnu.org/                                                                                                                                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35 | https://twiki.cern.ch/twiki/bin/viewauth/Atlas/CSCTestProcedures                                                                                       |

| 36 | https://twiki.cern.ch/twiki/bin/viewauth/Atlas/ReleaseNotes                                                                                            |

| 37 | http://positron.ps.uci.edu/~pier/                                                                                                                      |

| 38 | Fulcrum Focalpoint FM2224, 24-port 10G Ethernet L2 Switch Chip. Advanced<br>Information Data Sheet. February 2006 (revision 0.7)                       |

| 39 | P. Gällnö, "ATLAS ROD Busy Module. Technical description and users manual",<br>https://edms.cern.ch/file/319209/1/rod_busy_manual_2.pdf                |

| 40 | P. Gällnö, "ATLAS Local Trigger Processor - LTP. Technical description and users manual", https://edms.cern.ch/file/551992/2/LTP_manual_041.pdf        |

| 41 | Pigeon-Point documentation<br>http://www.pigeonpoint.com/pdf/ShelfManagerUG.pdf                                                                        |

| 42 | "ATLAS Level-1 Trigger Technical Design Report (Chapter 16) ",<br>http://atlas.web.cern.ch/Atlas/GROUPS/DAQTRIG/TDR/V1REV1/L1TDR_TTC. pdf              |

| 43 | J. Christiansen, A. Marchioro, P. Moreira and T. Toifl, "TTCrx Reference Manual",<br>https://edms.cern.ch/file/1148404/1/TTCrx_manual3.11.pdf          |

| 44 | The ATLAS Level-1 Central Trigger Processor Core Module (CTP_CORE), cdsweb.cern.ch/record/801863/files/n22-4-slides.pdf                                |

| 45 | G. Lehmann, "ATLAS TDAQ Controls: Operations at Different Activity Stages", https://edms.cern.ch/file/675671/1/ATLAS_OperationsAndTransitions.pdf      |

| 46 | ATLAS Detector Control System (DCS),<br>https://twiki.cern.ch/twiki/bin/viewauth/Atlas/AtlasDcs                                                        |

| 47 | I. Soloviev, "ATLAS TDAQ Config Packages",<br>http://atlas-tdaq-sw.web.cern.ch/atlas-tdaq-sw/doxygen/tdaq/production/html/ConfigPac<br>kages.html      |

| 48 | S. Kolos, "ATLAS TDAQ How to use the ERS package", http://atlas-tdaq-<br>sw.web.cern.ch/atlas-tdaq-sw/doxygen/tdaq-common/production/html/main.html    |

| 49 | http://atlasdaq.cern.ch/jnlp/logmanager/logmanager.jnlp                                                                                                |

| 50 | S. Kolos, "Information Service user's guide",<br>http://atlas-tdaq-monitoring.web.cern.ch/atlas-tdaq-monitoring/IS/doc/userguide/is-user<br>sguide.pdf |

| 51 | "Online Histogramming", http://atlas-onlsw.web.cern.ch/Atlas-onlsw/oh/oh.htm                                                                           |

| 52 | "OHP Monitoring", https://twiki.cern.ch/twiki/bin/viewauth/Atlas/OhpMonitoring                                                                         |

| 53 | <i>"Incremental Design Reuse with Partitions. Xilinx application note: XAPP918 (v1.0) June 7, 2007.</i>                                                |

| 54 | Zynq-7000 All programmable SoC Overview DS190 (v1.2) August 21, 2012.                                                                                  |

| 55 | Virtex-5 Family overview. DS100 (v5.0) February 6, 2009                                                                                                |

| 56 | Embedded Processor Block in Virtex-5 FPGAs. Reference Guide. UG200 (v1.8).<br>February 24, 2010                                                        |

## **Document Control Sheet**

| Document   | Title:               | The New ROD Complex (NRC) Conceptual Design Report                                                                                                                                                                      |              |                    |  |  |  |  |  |  |  |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|--|--|--|--|--|--|--|

|            | Version:             | 1.1                                                                                                                                                                                                                     |              |                    |  |  |  |  |  |  |  |

|            | Issue:               | 1                                                                                                                                                                                                                       | 1            |                    |  |  |  |  |  |  |  |

|            | Edition:             | English                                                                                                                                                                                                                 |              |                    |  |  |  |  |  |  |  |

|            | ID:                  | XXX-TD-xxxxx                                                                                                                                                                                                            | XXX-TD-xxxxx |                    |  |  |  |  |  |  |  |

|            | Status:              | First release to reviewers                                                                                                                                                                                              |              |                    |  |  |  |  |  |  |  |

|            | Created:             | September 1, 2012                                                                                                                                                                                                       |              |                    |  |  |  |  |  |  |  |

|            | Date:                | September 23, 2012                                                                                                                                                                                                      |              |                    |  |  |  |  |  |  |  |

|            | Access:              | V:\REG\Detector Rand D\NRC\CDR\V1.1\frontmatter.fm                                                                                                                                                                      |              |                    |  |  |  |  |  |  |  |

|            | Keywords:            | CSC ROD                                                                                                                                                                                                                 |              |                    |  |  |  |  |  |  |  |

| Tools      | DTP System:          | Adobe FrameMaker                                                                                                                                                                                                        | Version:     | 6.0                |  |  |  |  |  |  |  |

|            | Layout<br>Template:  | Software Documentation<br>Layout Templates                                                                                                                                                                              | Version:     | V2.0 - 5 July 1999 |  |  |  |  |  |  |  |

|            | Content<br>Template: | Version:                                                                                                                                                                                                                |              |                    |  |  |  |  |  |  |  |

| Authorship | Coordinator:         | Michael Huffer, SLAC                                                                                                                                                                                                    |              |                    |  |  |  |  |  |  |  |

|            | Written by:          | Richard Claus (SLAC), Raul Murillo Garcia (UCI), Ryan T. Herbst<br>(SLAC), Andrew J. Lankford (UCI), Andrew Nelson (UCI), Su Dong<br>(SLAC), Nicoletta Garelli (SLAC), Rainer Bartoldus (SLAC), James<br>Russell (SLAC) |              |                    |  |  |  |  |  |  |  |

#### Table 1 Document Control Sheet

### **Document Status Sheet**

| Title:     | The New ROD Complex (NRC) Conceptual Design Report |           |                                                                                                                                                                          |  |  |  |  |

|------------|----------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ID: XXX-TD |                                                    | XXXXX     |                                                                                                                                                                          |  |  |  |  |

| Version    | Issue                                              | Date      | Reason for change                                                                                                                                                        |  |  |  |  |

| 0.1        | 1                                                  | 9/1/2012  | First (very rough) look for the SLAC and UCI folk                                                                                                                        |  |  |  |  |

| 0.5        | 1                                                  | 9/18/2012 | Finished COB and RTM sections, general cleanup of chapter 3.                                                                                                             |  |  |  |  |

| 0.6        | 1                                                  | 9/20/2012 | Finished FTM, Base board, Control Processor, Mezzanine<br>board sections. Did some other general cleanup. Updated<br>chapter 3 reflecting input from yesterday's review. |  |  |  |  |

| 0.7        | 1                                                  | 9/21/2012 | Initial draft of RCE section. Did some other general cleanup.<br>More cleanup of chapter 3.                                                                              |  |  |  |  |

| 0.8        | 1                                                  | 9/22/2012 | Initial draft of CE software section. Added detail to photo-<br>graphs. Added to references and did other general cleanup.                                               |  |  |  |  |

| 1.0        | 1                                                  | 9/23/2012 | First release for reviewers                                                                                                                                              |  |  |  |  |

| 1.1        | 1                                                  | 9/24/2012 | First typos found by Rainer & Raul                                                                                                                                       |  |  |  |  |

#### Table 2 Document Status Sheet

# **List of Tables**

- Table 1p. 7Document Control Sheet

- Table 2p. 8Document Status Sheet

# **Table of Contents**

| Abstract                                    | 3  |

|---------------------------------------------|----|

| Intended audience                           | 3  |

| Conventions used in this document           | 3  |

| References                                  | 4  |

| Document Control Sheet.                     | 7  |

| Document Status Sheet                       | 8  |

| List of Tables.                             | 9  |

| List of Figures                             | .5 |

| List of Listings                            | .7 |

| Chapter 1                                   |    |

| <b>Overview</b>                             | .9 |

| 1.1 Introduction                            | .9 |

| 1.2 The CSC and its On-Detector Electronics | 20 |

| 1.3 Input rates                             | 21 |

| 1.4 The ROS Complex                         | 21 |

| 1.5 Feature extraction & output rates       | 22 |

| 1.6 Power and footprint                     | 22 |

| 1.7 Environmental Monitoring & Control      | 22 |

| 1.8 Trigger & Timing Control (TTC)          |    |

| 1.9 Busy handling                           |    |

| 1.10 TDAQ Control and Monitoring            |    |

| Chapte |                               |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|--------|-------------------------------|-----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| -      | al Design                     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 25 |

| 2      | .1 ATCA as the implementation | -   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | 2.1.1 The Shelf               |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | 2.1.2 Shelf Power             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | 2.1.3 The Front-Board         |     | •   | • | • | • | • | • |   | • |   | • | • | • | • |   | • | 28 |

|        | 2.1.4 The RTM                 |     |     | • | • | • | • | • | • | • | • | • | • | • | • |   | • | 29 |

|        | 2.1.5 IPMI and the Shelf Man  | age | er. |   |   |   | • |   |   | • |   | • |   | • | • |   | • | 30 |

| 2      | 2 Overview                    |     |     |   |   |   |   |   |   |   |   | • |   | • |   |   |   | 31 |

| 2      | 3 Shelf choice                |     |     |   |   |   |   | • |   |   |   | • |   | • | • |   |   | 33 |

| 2      | 4 Shelf Power                 |     |     |   |   |   |   |   |   | • |   | • |   | • |   |   |   | 34 |

| 2      | .5 Shelf Manager & IPMI       |     |     |   |   |   |   |   |   | • |   |   |   | • | • |   |   | 34 |

| 2      | .6 The COB                    |     |     |   |   |   | • |   |   | • |   | • |   | • | • |   |   | 35 |

|        | 2.6.1 The DTM Bay             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 36 |

|        | 2.6.2 The DPM bay             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 37 |

|        | 2.6.3 Fabric Interconnect .   |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 37 |

|        | 2.6.4 Base Interconnect .     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

|        | 2.6.5 The ATLAS FTM           |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 39 |

|        | 2.6.6 The ATLAS Base Board    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 39 |

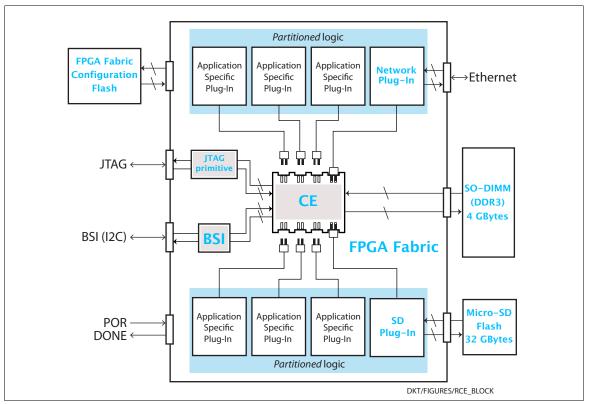

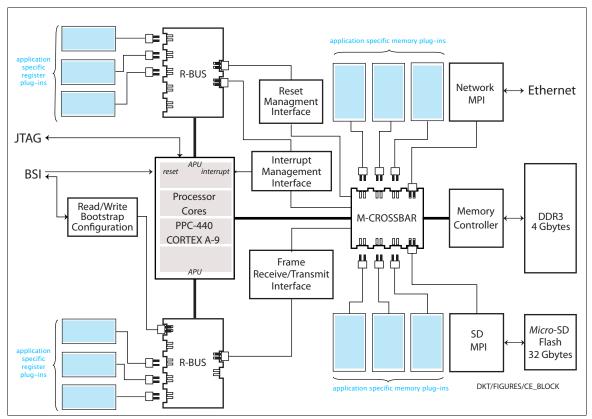

| 2      | 7 The RCE                     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 40 |

|        | 2.7.1 The Protocol-Plug-In    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 42 |

|        | 2.7.2 The Cluster Element     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 43 |

|        | 2.7.3 CE Software Services    |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 44 |

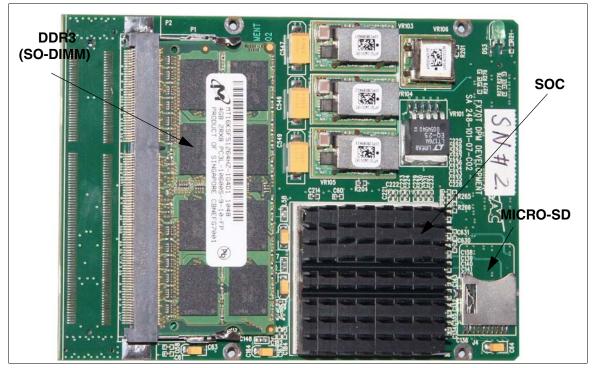

|        | 2.7.4 The Mezzanine board     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 45 |

| 2      | 8 The CSC RTM                 |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 47 |

| 2      | 9 The SFP RTM                 |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 48 |

| 2      | .10 The Control Processor     |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 49 |

| 2      | .11 Networking                |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 49 |

|        | 0                             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| Chapte |                               |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | are and Software design       |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | 1 Introduction                |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 3      | 2 The Event Plane             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|        | 3.2.1 Input Plug-in           |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 54 |

|        | 3.2.2 FEX Plug-in             |     |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 55 |

|        | 3.2.3 S-Link Plug-in          |     |     |   |   |   |   |   | • | • |   | • | • | • | • |   |   | 55 |

|        | 3.2.4 Usage                   |     |     |   |   |   |   |   |   | • |   | • | • | • | • |   |   | 55 |

| 3      | 3 Trigger Plane               |     |     | • |   | • |   | • | • | • |   | • | • | • | • | • |   | 56 |

|        | 3.3.1 SCA Controller          |     |     |   |   |   |   |   |   | • |   |   |   | • | • |   |   | 56 |

|        | 3.3.2 TTC Receiver Plug-in    |     | •   |   |   |   | • |   |   | • |   | • | • | • | • |   |   | 58 |

|        | 3.3.3 TTC Transmitter Plug-i  | n.  |     |   |   |   |   |   |   | • |   | • |   | • | • |   |   | 58 |

| 3      | 4 Busy Plane                  |     |     |   |   |   | • |   |   | • |   | • |   | • | • |   |   | 58 |

| 3.4.1 Busy Source Plug-in             |  |   | • |  | • |   |    |   | 60 |

|---------------------------------------|--|---|---|--|---|---|----|---|----|

| 3.4.2 Busy Destination Plug-in        |  |   |   |  |   |   |    |   | 60 |

| 3.5 TDAQ Plane                        |  |   |   |  | • |   |    |   | 60 |

| 3.6 Firmware and Software Maintenance |  |   |   |  |   |   | 62 |   |    |

| 3.7 Software tools                    |  |   |   |  | • |   |    |   | 62 |

| 3.8 Test and Release plan             |  |   |   |  | • |   |    |   | 62 |

| 3.9 System monitoring                 |  |   |   |  | • |   |    |   | 63 |

| 3.10 Calibration                      |  | • | • |  | • | • | •  | • | 63 |

# **List of Figures**

| Figure 1  | p. 19 | Interfaces for the The ROD Complex                    |

|-----------|-------|-------------------------------------------------------|

| Figure 2  | p. 26 | Front view of an ASIS 5-slot ATCA shelf               |

| Figure 3  | p. 27 | Rear view of an ASIS 5-slot ATCA shelf                |

| Figure 4  | p. 28 | Exposed view of an ASIS 5-slot ATCA shelf's backplane |

| Figure 5  | p. 29 | Representative ATCA Front-Board                       |

| Figure 6  | p. 30 | Representative ATCA RTM                               |

| Figure 7  | p. 32 | Block Diagram of the New ROD Complex                  |

| Figure 8  | p. 35 | Preproduction COB                                     |

| Figure 9  | p. 36 | Block Diagram of the COB                              |

| Figure 10 | p. 39 | Prototype FTM                                         |

| Figure 11 | p. 41 | Block Diagram of the RCE                              |

| Figure 12 | p. 43 | Block Diagram of the CE                               |

| Figure 13 | p. 46 | Preproduction COB-Mezzanine-Board (CMB)               |

| Figure 14 | p. 47 | Block diagram of the CSC RTM                          |

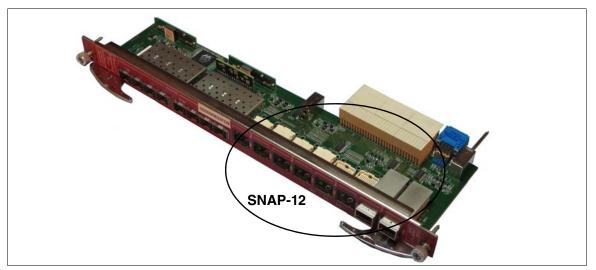

| Figure 15 | p. 48 | An RTM containing SNAP-12s                            |

| Figure 16 | p. 48 | Block diagram of the SFP RTM                          |

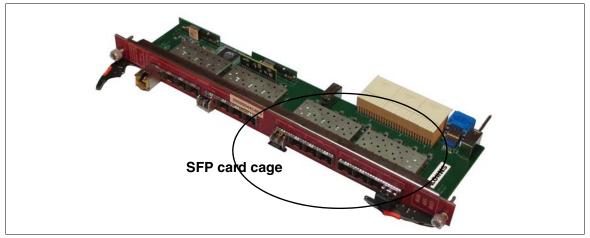

| Figure 17 | p. 49 | An RTM containing SFPs                                |

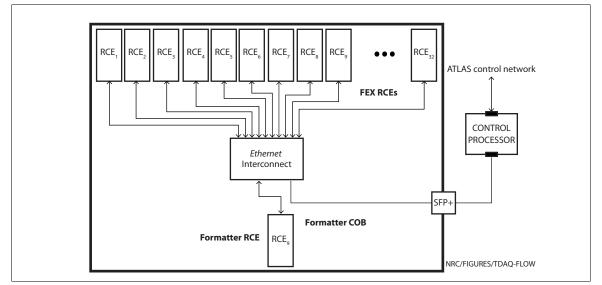

| Figure 18 | p. 51 | NRC dataflow through it interfaces                    |

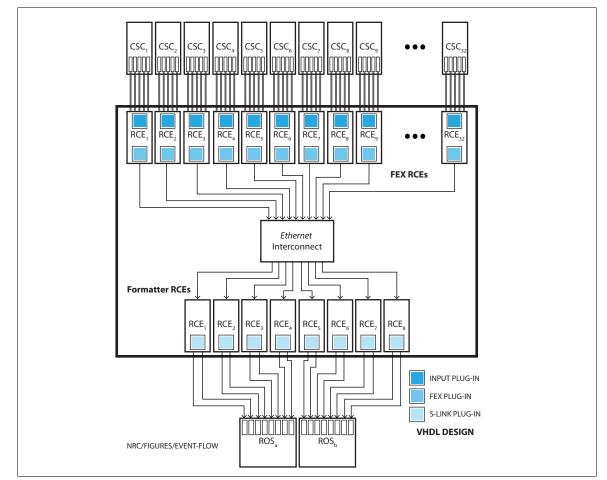

| Figure 19 | p. 53 | Event Flow                                            |

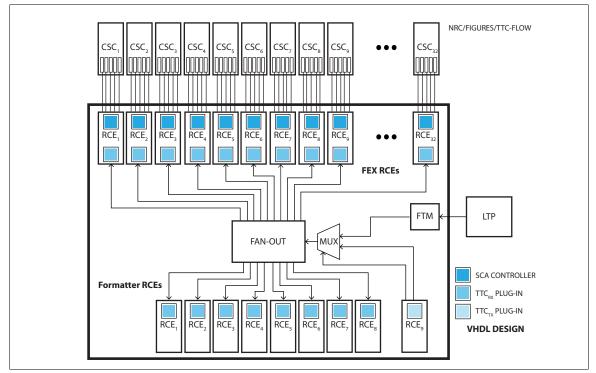

| Figure 20 | p. 56 | Trigger Flow                                          |

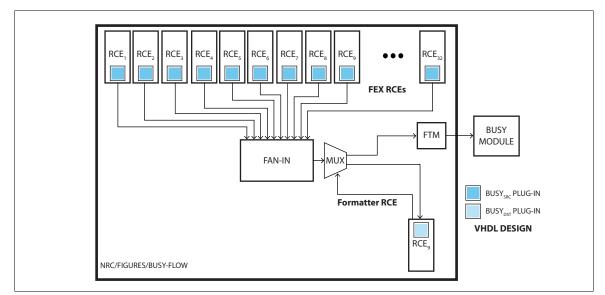

| Figure 21 | p. 59 | Busy Flow                                             |

| Figure 22 | p. 60 | Run-Control Flow                                      |

|           |       |                                                       |

# **List of Listings**

## Chapter 1 Overview

#### 1.1 Introduction

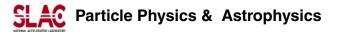

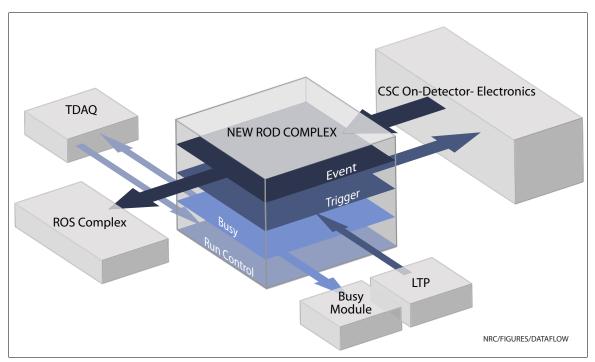

The ROD Complex's principal responsibility is for the acquisition and extraction of data from the ATLAS muon system's *Cathode Strip Chambers* (CSC) along with their resulting transfer to the ATLAS TDAQ system. Acquisition is driven externally by the ATLAS central trigger system at its *L1A* rate. To support this activity the complex is also responsible for the setup, control and monitoring of the on-detector electronics associated with those chambers. Treating for the moment that complex as a black box, its potential replacement must, at a minimum, satisfy its *interfaces*. Those interfaces are illustrated in Figure 1:

Figure 1 Interfaces for the The ROD Complex

The remainder of this chapter serves as an introduction to those interfaces as well as to the performance required of its replacement. Note that much of the identical information is contained, albeit with a different emphasis, in [16].

Chapter 2 introduces the *physical* design of its replacement. Two somewhat unique features of the replacement proposal are:

- i. The substitution of ATCA for VME as an implementation platform.

- ii. The usage of building blocks from SLAC'S DAQ tool-box (the RCE and COB).

Consequently, to fully communicate the proposal requires some rudimentary understanding of ATCA as well as the above mentioned building blocks. The second chapter is intended to provide background for both.

The usage of both ATCA and these blocks is the principal feature of this proposal. Within the constraints of an 18 month schedule this feature makes it practical to propose the design, fabrication, testing & integration of what logistically amounts to the production of an entirely new set of RODs.

Further, this feature turns its replacement from a hardware to software-centric design. The amount of hardware to be designed and fabricated as compared to what must be purchased and integrated is quite modest. Therefore, the bulk of engineering entailed by this proposal resides in its firmware and software. Chapter 3 introduces and describes that firmware and software design.

#### **1.2 The CSC and its On-Detector Electronics**

The CSC consists of *thirty-two* (32) chambers. Each chamber contains *four* (4) precision layers of 192 channels each and *four* (4) transverse layers of 48 channels each. The on-detector electronics are partitioned into units of *ASM-II Boards* [2]. One ASM-II board is designed to process 192 channels of data. Consequently, each chamber contains five *ASM-II* boards; four managing the chamber's precision layers and one its transverse layer. Chamber data are sampled every 50 *ns*. One sample from one channel produces *12-bits* of data. One sample from *all* 192 channels of a chamber is called a *Time-Slice*. In nominal data taking mode each *L1A* from the trigger generates *four* time-slices. Therefore, when configured for nominal operation, the amount of data emitted by one ASM-II is approximately *9.216 Kbits* (*1.15 Kbytes*), and for an entire chamber, five times that value or approximately *1.475 Mbits* (*1.84 Kbytes*). Note, the chambers emit data which is *not* sparse and therefore the amount of data transmitted by an ASM-II per event is *independent* of beam conditions as well as *L1A* rate.

Each ASM-II has *three* (3) fiber-optic links. Two of its three links operate as a pair and are used for transmission (downlink) of chamber data, while the third receives (uplinks) external control and timing. Independent of their direction all links are synchronized to the ATLAS system clock (40 MHZ) and operate at *640 Megabits/second*. However, as transmitters work in pairs the downlink capacity of one ASM-II is twice that value, or *1.28 Gigabits/second*<sup>1</sup>.

The downlink for one chamber requires *ten* (10) fiber-optic links. Those ten links are bundled into one, *twelve* (12) strand fiber-optic MPO cable [10], leaving two of the twelve strands

<sup>1.</sup> Roughly 160 Mbytes/second.

unused. The uplink for a single chamber requires *six* (6) fiber-optic links. Five of those links receive the ASM-II's timing and control, while the sixth is used to drive the chamber's pulser calibration board [11]. The uplinks for *two* chambers are bundled together into a *single* MPO cable. It is these existing MPO uplink and downlink cables which define the on-detector electronics interface to the complex. As the CSC contains thirty-two chambers, there are in total *forty-eight* (48) cables, *thirty-two* (32) downlink and *sixteen* (16) uplink.

#### 1.3 Input rates

To satisfy its primary performance requirement the complex must process chamber data up to the maximum *L1A rate*, which is defined as 100 KHZ *Poisson* averaged. This implies the maximum data rate produced by a single ASM-II board is approximately 115 *MBytes/second* and for a single chamber five times that value or approximately *576 Mbytes/second*. With *thirty-two* (32) chambers the entire complex must absorb thirty-two times that value, or a value somewhat greater than *18 GBytes/second*.

#### 1.4 The ROS Complex

Feature extracted event data are the product of the complex. Those data are sent in parallel from the ROD complex to the TDAQ system. That unit of parallelism is the ROL (*Read-Out Link*). The ROL is a single, full-duplex, fiber-optic link operating at *1.28 Gigabits/second* [21]. Data are sent on one duplex and flow-control received on its other. Physically, the ROL uses single mode fiber and is terminated at both ends with L/C connectors [11].

Data transmitted by the ROL must conform to the envelope dictated by the protocol specified in [13]. That protocol specifies that one event produces one frame. For the CSC, the event data produced from two (2) chambers is carried on *one* (1) ROL. The structure of one frame is described in [14].

Data for the entire complex is sent on *sixteen* (16) ROLs. The component of the TDAQ system that receives and manages output from ROLS is the ROS (*Read-Out-System*). The CSC requires *two* (2), one allocated to each of its two endcaps. That is, each ROS services the CSC data from *eight* (8) ROLs.

In short, it is those existing sixteen ROLs which define the TDAQ *event* or ROS interface to the complex.

#### 1.5 Feature extraction & output rates

The data volume numbers described in Section 1.3 represent the *input* rate to the complex. However, it's important to note, unlike most ATLAS subsystems the amount of data *into* the CSC's complex is *not* equal to the amount of data *out of* its complex. For any given event, the CSC's chambers emit their *entire* response, presenting a somewhat significant data volume. However, as chamber occupancy for any given event is quite modest, the amount of corresponding signal emitted by the CSC is also quite modest. It remains the complex's responsibility as well as one of its principal requirements to extract that signal and forward only those data representing hit channels in the CSC chambers. The process of identifying that signal will be referred to as *Feature Extraction* (FEX). Although described in detail in [4], feature extraction involves a threshold cut, out-of-time rejection as well as cluster finding. Its implementation for the NRC is described in Section 3.2.

Output size is then, of course, a function of chamber occupancy, which in turn varies with luminosity, pile-up and background. These effects can be parameterized by the single number *mu*, which is the average number of interactions per bunch crossing. For example, at a *mu* of *thirty* (30), representative of today's typical operating conditions, the size of an output event is on the order of *150 bytes* per chamber.

To insure a healthy safety margin the requirements on the NRC are set at a *mu* expected after Phase-1 turn-on. That *mu* is *eighty* (80), resulting in an expected output event size of approximately *570 bytes* per chamber, per event [16].

Recall (see above, Section 1.4) that data from two chambers are carried on one ROL, giving at a *mu* of 80, *1140 bytes* per ROL, per event.

At an *L1A* rate of 100 KHZ, this leads to an output data rate of about *57 Mbytes/second* per chamber or for a single ROL double that value or *114 Mbytes/second* per ROL. Assuming a normal distribution between the CSC's two endcaps this corresponds to somewhat less than *one* (1) *Gbyte/second* per ROS.

#### **1.6 Power and footprint**

See [16].

#### 1.7 Environmental Monitoring & Control

The Detector Control System (DCS) [46] has the responsibility to monitor and control detector infrastructure such as power supplies and ventilation.

### **1.8 Trigger & Timing Control (TTC)**

The Trigger and Timing Control system is described in [42] and [43]. It consists of a Central Trigger Processor (CTP) [44] and a distributed set of Local Trigger Processors (LTPs) [40].

#### 1.9 Busy handling

The 'BUSY' signal generated by the ROD Complex is consumed by the Busy Module [39]. This module aggregates the BUSY signals on its inputs into a single output signal that is ultimately, possibly via other Busy Modules, forwarded to the Central Trigger Processor (CTP) [44]. When BUSY is assert to the CTP, triggers are inhibited from being propagated to the subsystems via their individual Local Trigger Processors (LTP) [40].

#### 1.10 TDAQ Control and Monitoring

The TDAQ Control system is based on a Finite State Machine (FSM) model, as described in [45]. Besides controlling the operation of the ATLAS experiment for taking data, the system monitors various aspects of the operation.

The TDAQ software suite is comprised of a variety of packages such as the Configuration Package [47], the Error Reporting System [48], the Log Manager [49][50], Histogramming [51][52], etc. Through the use of these packages, the CSC subsystem can be put through its paces, in both stand-alone situations as well as combined ATLAS running.

# Chapter 2 Physical Design

#### 2.1 ATCA as the implementation platform

The *New ROD Complex* (NRC) is designed as a plug compatible replacement for the current complex. The interfaces necessary to satisfy that plug compatibility were described in Chapter 1. At one level of abstraction the physical implementation of the NRC could be simply represented as an arbitrary aggregate of PCB boards. But, of course, because these boards operate to a single purpose, they will also necessarily require connections between them. Typically, for reasons of understanding, modularity and maintenance, those connections follow predefined, accepted mechanical and electrical standards. In this document any such usage which employs a specific standard will be referenced as a *Platform*. For example, VME would constitute one such platform. For the NRC that platform is based on an existing standard developed by the *PCI Industrial Computer Manufactures Group* (PICMG) commonly referred to as the *Advanced Tele-Communication Architecture*, or ATCA, whose current revision is referred to within that consortium as *PICMG 3.0*. As a platform ATCA is now quite mature, having been in existence for more than ten years, with a broad design base and a wealth of equipment deployed in the field as well as a burgeoning eco-structure within the telecommunication and defence industries.

ATCA usage by the NRC will be entirely compliant with the PICMG 3.0 specification. That specification is described in [6] with an introduction available from [5]. However, the remainder of this section is intended to provide sufficient background to gain a thorough understanding of the physical design description.

#### 2.1.1 The Shelf

The ATCA shelf is known historically as the *chassis* and is by analogy, equivalent to a VME *crate*. Shelves house the Front-Boards and RTMs described below (see Sections 2.1.3 and 2.1.4). They contain, from front to rear, pairs of slots with each pair housing a Front-Board in the front and the Front-Boards's corresponding RTM in the rear. The shelf allows for *hot-swap* of any board in any slot. Depending on form factor the number of its slot pairs varies from *two* (2) to *sixteen*

(16). The orientation of those slots also varies, as shelves are offered with either *horizontal* or *vertical* orientation. In turn, that orientation affects the flow of air; from either left to right (*horizontal*), or top to bottom (*vertical*).

Broadly, the shelf is composed of a *subrack, backplane, filters* and cooling devices (*fans*). The subrack provides the infrastructure to contain the Front-Boards and RTMs described below. This includes guide rails, ESD discharge, alignment, keying, and backplane interface. Backplanes are passive circuit boards which carry the connections between slots. Although somewhat more complicated in detail, for this document, those connections can be partitioned into three logical groups: power, control and differential data pairs. The topology for both power and control connections is invariant of backplane. However, in order to accommodate different applications the connection topology of data pairs can vary. Two commonly used topologies are the dual star and full mesh. The backplane (and ATCA) is protocol *agnostic* with respect to the usage of these differential pairs with the choice delegated to the shelf's specific Front-Boards.

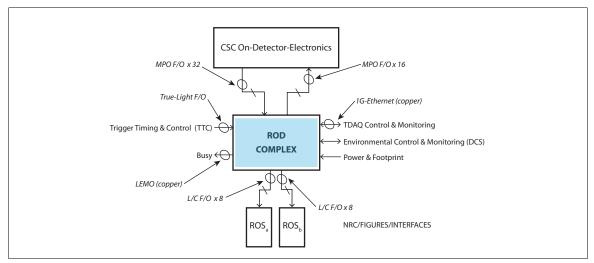

Figure 2 provides a front view of a representative ATCA shelf as used for development by SLAC's *Detector R & D* program:

Figure 2 Front view of an ASIS 5-slot ATCA shelf

This photograph is of a COTS<sup>1</sup> shelf purchased from ASIS [7]. It has a horizontal orientation within its corresponding rack with airflow from left to right. It contains a replicated, full mesh backplane. Two of its five *front* slots are populated with Front-Boards, while its unused slots are populated with dummy air baffles. Note the RJ45 connector located on the front-panel of its *Shelf-Manager* (ShMC). This provides the shelf manager access to the *Ethernet* from which control and monitoring (through IPMI) of the shelf would be accomplished. Further, note the integral power supplies. These supplies are *not* required by the ATCA standard, but are provided by ASIS as a convenient feature for bench-top usage. The same shelf viewed from the rear is illustrated in Figure 3:

<sup>1.</sup> Commercial-Off-The-Shelf.

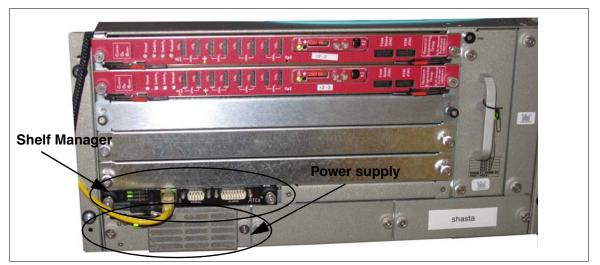

Figure 3 Rear view of an ASIS 5-slot ATCA shelf

As was the case for the front, two of its five *rear* slots are also populated, however, with RTMs (see Section 2.1.4) rather than Front-boards. Note, as was the case for the front slots, unused slots are populated with dummy air baffles. Further, note the power pins provided for external input of shelf power (+48 VDC). Last, Figure 4 provides an identical view, although now unpopulated, offering an unobstructed view of its backplane. Note the open area on the right allowing access to the P3 zones between Front-boards and corresponding RTM.

Figure 4 Exposed view of an ASIS 5-slot ATCA shelf's backplane

*The choice of shelf for the NRC is discussed in Section 2.1.1.*

#### 2.1.2 Shelf Power

An ATCA shelf does not have any requirement for provision of its own power. Further, a shelf also has no explicit requirement for the control and monitoring of that power *independent* of source. Instead, its minimum requirement is to simply support external connections for both primary and redundant supplies. Those supplies must provide +48 VDC. In a large scale installation this "feature" allows for rack aggregation of power over many shelves.

Power for the NRC shelf is discussed in Section 2.4.

#### 2.1.3 The Front-Board

The *Front-Board* constitutes the heart of the ATCA eco-system. From a shelf's perspective that board is simply a PCB board, 8U wide *x* 280 *mm* deep and which plugs into one of its front slots. That board, although following ATCA mechanical and electrical interface standards, contains logic which is application specific. And from that logic's perspective the shelf exists simply to provide a platform to serve its application specific *content*.

On its near side the board's front-panel contains a hot-swap handle as well as four ATCA defined LEDs to help direct an operator in board insertion and removal. The remainder of the panel is considered application specific. The board's rear side contains three logical "Zones". Zones 1 and 2 connect directly to a shelf's backplane. Zone 1 provides access to shelf power (+48 VDC) as well as the I<sup>2</sup>C communication channels which the board uses to communicate with its shelf manager. Zone 2 provides access to the high-speed, differential pairs connecting boards together. The area encompassed by Zone 3 is application defined, but reserved for connections to the board's RTM. PICMG defines an extension to the standard which allocates

that area. This standard is PICMG 3.8 ("ATCA for physics", [23]), which follows the convention of Zone 1 and 2 and partitions its area into two zones, one for power/control and the other for signals. The connector used for signals allows for allocation of up to 120 differential pairs between board and RTM.

Any and all boards used by the NRC adhere to PICMG 3.8.

Note, that independent of any allocation scheme for Zone 3 the power for an RTM, if defined, must go *through* the Front-Board.

Each board must also contain a local controller called its *IPM Controller*, or IPMC. The IPMC manages the board's activation/deactivation policy as well as monitors its health and safety. It serves as a proxy to the board's shelf manager and communicates using the I<sup>2</sup>C channels on Zone 1. The IPMC, as was the case for the board itself, must satisfy ATCA interface standards, but its implementation is also, necessarily, application specific.

The standard specifies that the sum of the power drawn from a Front-Board and its corresponding (if any) RTM must not exceed *300 Watts*.

The NRC requires one application specific Front-Board. That board is described in Section 2.6.

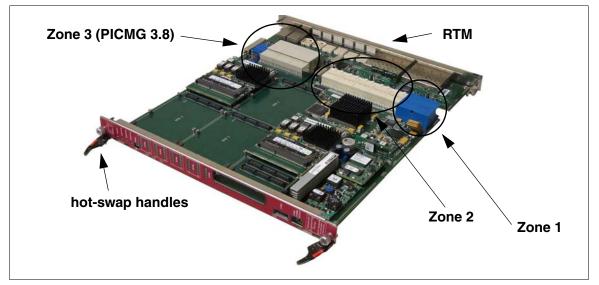

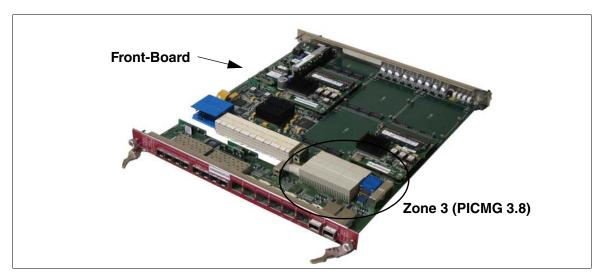

A photograph of a representative Front-Board, showing connectivity to an RTM (using PICMG 3.8) is illustrated in Figure 5:

Figure 5 Representative ATCA Front-Board

#### 2.1.4 The RTM

The RTM (*Rear-Transition-Module*) is simply a PCB board, 8U wide *x* 70 *mm* deep which is used to *extend* a Front-Board (see Section 2.1.3). Although not required, that extension is typically

found necessary for two reasons: First, to increase the useful footprint of the Front-Board and second, to house a board's external, I/O interface. The RTM shares the same hot-swap model as the Front-Board and specifies an identical pitch (1.2"). This allows the RTM to reuse the same panel, handle switches, and LEDs as its Front-board. The RTM connects to its Front-board through Zone 3. The form of that connection is application specific. However, if power for the RTM is necessary, it must be provided by the Front-board and must be brought through Zone 3. The ATCA specification is somewhat ambiguous with respect to the maximum power drawn by an RTM. A shelf is required to provide at a minimum 15 watts of cooling, but is, however, free to provide more. This is typically the case for all shelf manufacturers with maximum numbers more in the 40 to 70 watt range.

The RTMs employed by the NRC standardize the usage of Zone 3 by application of PICMG 3.8 [17]. That standardization allows such an RTM to "plug and play" with the NRC's Front-Board (see Section 2.6). PICMG 3.8 populates Zone 3 with two connectors, one for power and one for signal. Power provided through the power connector is +12 VDC and that connector also contains pins for JTAG as well as I<sup>2</sup>C support. The I<sup>2</sup>C channel is expected to be used by the Front-Board for control of the RTM's hot-swap switch as well as its front panel LEDs.

The signal connector provides up to 120 differential pairs. How those pairs are assigned between Front-Board and RTM is considered application specific. However, for the NRC's Front-Board, each one of its four DPM bays is assigned 1/4 of those pins or *thirty* (30) pairs (see Section 2.6).

The two types of RTMs contained in the NRC are described in Sections 2.8 and 2.9. Figure 6 illustrates a representative RTM showing its PICMG 3.8 interface connected to a Front-Board:

Figure 6 Representative ATCA RTM

#### 2.1.5 IPMI and the Shelf Manager

ATCA adapts a somewhat locally autonomous philosophy with respect to environmental control and monitoring. As part of this model, each shelf has associated with it a single entity

responsible for maintaining the health and safety of its infrastructure. That entity is called the *Shelf Manager* (ShMC). Front-Boards, through their own local controller (or IPMC) negotiate both individually and independently with their shelf manager for their own activation or deactivation. They do so by publishing changes to their state through dedicated I<sup>2</sup>C channels on the backplane.

The shelf manager determines, based on hot-swap interface, when a board requires activation or deactivation. Power levels are negotiated based on both a board's request and the shelf's total available power. Shelf temperatures are maintained at safe levels autonomously by the shelf manager using information published by each board and adjusting power levels and fan-speeds accordingly.

In short, once a shelf's power is applied and while its shelf manager is active, no external monitoring or control is necessary to maintain the shelf's health and safety.

Although the health and safety of its shelf is maintained autonomously, the shelf manager still has provision for an external interface. Through this interface any information published to the shelf manager can be exported and the shelf manager can itself be configured. That physical interface is *Ethernet* and the shelf manager contains a TCP/IP Stack through which external communication is maintained. The logical interface for control and monitoring of the shelf is IPMI [18] and a wealth of tools exist, which interact with this interface.

#### 2.2 Overview

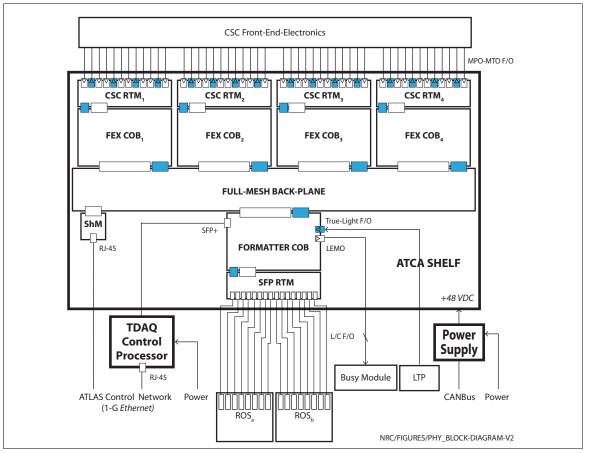

A block diagram of the NRC illustrating its major components as well as the connections to its interfaces, is shown in Figure 7:

Figure 7 Block Diagram of the New ROD Complex

There are *three* components:

- 1. A single, COTS<sup>1</sup> ATCA Shelf and its components.

- 2. An external *Power Supply* used to energize that shelf.

- 3. A COTS *Processor* hosting TDAQ software interfaces to control and monitor the NRC.

Each of these three components is separately described below, in sections 2.3, 2.4 and 2.10. However, the bulk of the design is contained within the components of the shelf. Those components are described in Section 2.6 and Section 2.7.

The NRC's shelf contains *five* (5) ATCA Front-Boards each paired with its corresponding RTM. The shelf's backplane's *fabric* interface is organized as a full mesh. That interface is used to provide transport of 10-Gigabit *Ethernet* between front boards. The backplane's *base* interface is organized as a dual-star and is used for two different functions:<sup>2</sup> First, it fans *out* TTC information from the NRC's LTP to each of the shelf's front boards. Second, it fans *in* busy information from each of the shelf's front boards to the NRC's Busy Module.

<sup>1.</sup> Commercial-Off-The-Shelf.

<sup>2.</sup> As long as *Ethernet* is available through the fabric interface, reuse of the base interface's is permitted.

Front-Board and RTM are custom designs. However, although custom, their design is entirely PICMG 3.0 compliant, including hot-swap features, IPMI monitoring & control as well as E-keying. Both Front-Board and RTM are *independently* hot-swapable. The interface between Front-Board and RTM is PICMG 3.8 [23].

The five Front-Boards are all instances of a single design called the COB (*Cluster-On-Board*). This board is *not* specific to the NRC, but was instead designed from its inception to serve as a generic tool for the construction of massively parallel, high rate, high volume DAQ systems. The function of any one board is intended to be application specific and is dictated solely by the firmware and software programmed into it. This board, including its design, fabrication and production is a deliverable of SLAC's *Detector R & D* program on DAQ. A photograph of a preproduction COB is found in Figure 8 and a more detailed description of its functionality in Section 2.6.

For the case of the NRC, four of its five COBs contain application specific firmware and software to acquire and feature extract event data. These are the *FEX* COBs. Those feature extracted data are transferred (through a combination of *Ethernet* switching and mesh backplane) to the *Formatter* COB. In turn, that boards's application specific firmware and software receive and format those data for transmission to the ROS complex. Chapter 3 contains a description of each board's firmware as well as the software used to manage the NRC.

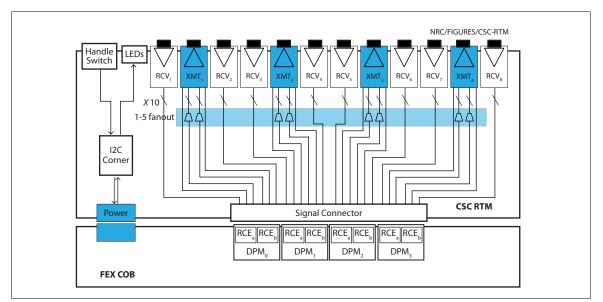

The NRC employs two RTM designs: one is purpose built for the NRC while the other is delivered by the same program providing the COB. While differing in implementation, both share the same principal function: Conversion of light to copper and copper to light. One RTM is designed to interface the fiber-optics connecting the NRC to the CSC's detector electronics, while the other interfaces the fiber-optics connecting the NRC to the ROS complex.

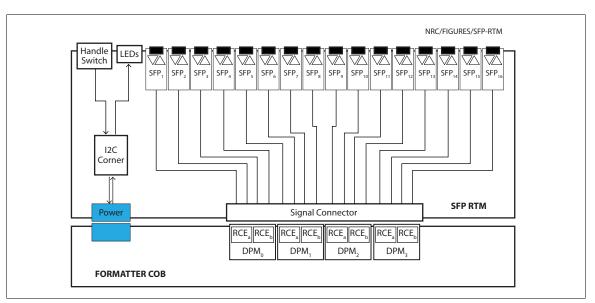

The RTM connecting the NRC to its on detector electronics is called the *CSC RTM* and the RTM connecting the NRC to its ROS complex, the *SFP RTM*. The NRC contains *four* (4) instances of the CSC RTM, one for each *FEX* COB, while there is only a single instance of the SFP RTM. That RTM is paired with the *Formatter* COB. The CSC RTM is described in Section 2.8, while the SFP RTM is described in Section 2.9.

#### 2.3 Shelf choice

The shelf will be purchased from a commercial vendor. As all boards installed in the NRC's shelf are PICMG 3.0 compliant the NRC makes no demands on shelf choice and only three modest demands regarding the choice of its back-plane: A full *mesh* backplane containing at least *five* (5) slots, using *Ethernet* as its fabric protocol. Those demands can be satisfied by any commercial ATCA shelf manufacturer.

Any further demands on that choice will be determined by constraints imposed by the requirement to operate safely and reliably in USA-15 under the control and monitoring of ATLAS operations. This could, for example, include shelf orientation, redundancy, air flow, etc.

We are aware that ATLAS has constituted a"VME Bus Replacement" committee [19] to study, for the upgrade era, a suitable replacement platform for VME. Further, that committee has selected ATCA as its candidate replacement platform. However, at this point its recommendations with respect to the ATCA standard remain unpublished. Nonetheless it is our intent to closely follow that committee's deliberations as they evolve and mature and wherever necessary apply its recommendations.

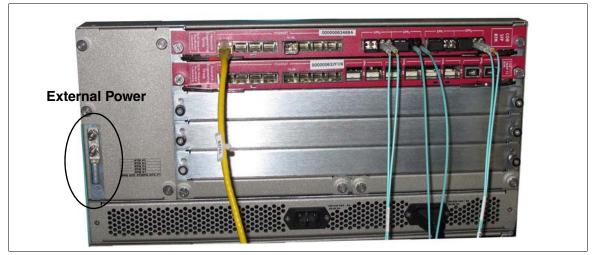

#### 2.4 Shelf Power

As discussed in Section 2.1.2 an ATCA shelf does not have any requirement for provision of its own power. Neither does it have any explicit requirement for the control and monitoring of that power *independent* of its source. Therefore, in order to minimize further demands on shelf choice, the NRC specifies *external* power supplies for its shelf. Its principal requirements are as follows:

- An input line voltage and frequency as determined by ATLAS standards

- An output voltage of +48 VDC

- A minimum power rating of 1500 *Watts*

- Provision for monitoring and control as determined by ATLAS DCS standards

- Must be mountable within the existing ATLAS rack infrastructure

For purposes of robustness and reliability we intend to provide *redundant* power supplies. Any further requirements will be driven by the need to satisfy the standards established by ATLAS for power supplies installed in USA-15.

#### 2.5 Shelf Manager & IPMI

At this point we do not believe, given the shelf manager's autonomous behavior, that any internal access to the shelf is required by ATLAS systems [15]. This includes, for example, any need for DCS to interface directly with IPMI. However, should that access be required, there is no fundamental feature of ATCA that would prevent it. This remains an area of active discussion and the specifics of the usage of IPMI by ATLAS still remain to be worked out.

For purposes of robustness and reliability we intend to provide *redundant* shelf managers. For internal development we plan to connect both shelf managers to the ATLAS control network. The networking requirements imposed by those shelf managers are described in Section 2.11.

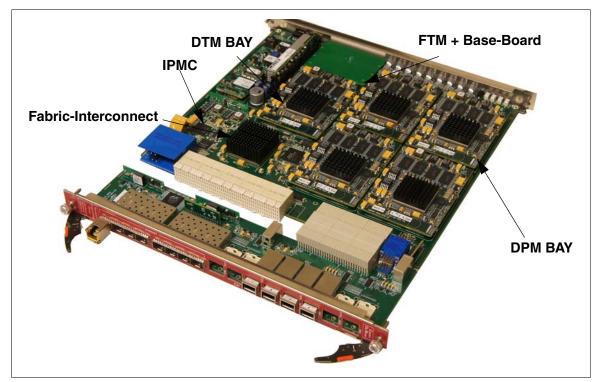

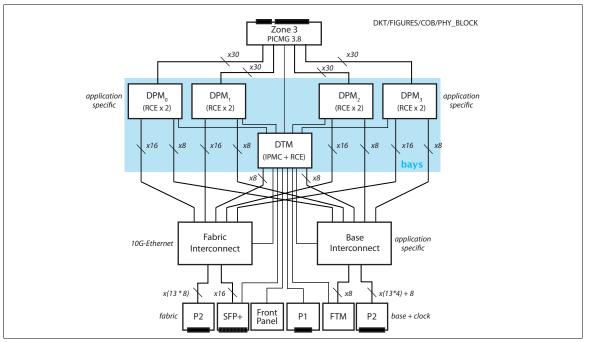

### 2.6 The COB

The COB (*Cluster-On-Board*) is an 8U, ATCA compliant Front-Board (see Section 2.1.3) with a PICMG 3.8 Zone 3. Functionally, the COB serves as a carrier board for the RCEs hosting the firmware and software developed for the NRC (see Section 2.7). Those RCEs are mounted on mezzanine boards (see Section 2.7.4), which in turn plug into *Bays* on the COB. Bays are connected to the COB's two separate, independent *Interconnects* as well as its Zone 3 connectors. Interconnects provide arbitrary, high speed communication paths between the elements contained on the bay's mezzanine boards, both (it is important to note), inter *and* intra COB.

Although rated up to 300 watts, when fully populated with five mezzanine boards, a COB draws closer to 120 watts. This board is one deliverable from SLAC's R & D program on high-speed DAQ. As such, the NRC simply purchases this board and from its perspective, that board consequently requires neither design nor development. A photograph of that COB (in preproduction form) with its five bays occupied is shown in Figure 8:

Figure 8 Preproduction COB

And a block diagram of the COB is shown in Figure 9:

Figure 9 Block Diagram of the COB

The COB contains *five* (5) bays; *one* (1) DTM bay (see Section 2.6.1) and *four* (4) DPM (see Section 2.6.2) bays. Although all bays share identical form factors and connectors (see Section 2.7.4), they can be differentiated, primarily by how they connect to Zone 3, with the DTM connecting only to its *power* connector and the DPM only to its *signal* connectors. In turn, those connections determine the function of their corresponding mezzanine boards. The DTM, interacting with its shelf manager, manages the health and safety of both COB and RTM, while DPMs acquire and process data originating from the RTM. Those data, their interface, acquisition and processing are all intended to be application specific.

#### 2.6.1 The DTM Bay

The mezzanine board plugged into the DTM (*Data-Transport-Module*) bay contains one RCE as well as the COB's *IPM Controller* (IPMC). The IPMC is the element responsible for monitoring the underlying health and safety of the COB as well as its corresponding RTM. It is also responsible, in conjunction with its corresponding shelf manager, for board and RTM activation/deactivation. It performs all these activities by interacting with various components on the COB, specifically with the RCEs contained within the COB's five bays. That interaction is accomplished through dedicated, local  $I^2C$  busses. The IPMC is a SOC (*System-On-Chip*), containing a dedicated ARM based (M3) processor. That processor runs de-facto, industry standard *Pigeon-Point* IPMC firmware and software [41], suitably modified to control and monitor the specific functionality of the COB.

Although in capability and form no different than any other RCE, the DTM's RCE has the fixed, dedicated responsibility for managing both of the board's interconnects. For this purpose it contains specific firmware and software. For example, as one responsibility, it must maintain

the configuration and supervise the *10G-Ethernet* switch contained within the fabric interconnect. That switch's management interface is a single lane PCIe. To communicate with this switch, the RCE contains a PCIe *Protocol-Plug-In (firmware,* see Section 2.7.1) as well as the tools (*software*) to configure and monitor that switch. Note, however, that while the DCM's RCE has predefined, base responsibilities it also remains accessible for user applications. For example, the NRC uses this RCE as a trigger simulation and that RCE has the capability to drive TTC protocol to not only the elements of its own board, but also to the elements of the entire shelf (see Section 3.3.3).

For the NRC, the RCE on the DTM is connected to eight (8) differential pairs of the fabric interconnect and four (4) pairs on the base interconnect. For the fabric interconnect, although those eight pairs can be configured a variety of ways, they will for the NRC, be configured as one (1) channel of 10G-Ethernet (XAUI). For the base interconnect two pairs receive <u>TTC</u> (one primary and one redundant) and two pairs transmit <u>BUSY</u> (one primary and one redundant). The four remaining pairs are unallocated.

#### 2.6.2 The DPM bay

The mezzanine board plugged into a DPM (*Data-Processing-Module*) bay contains two (2) RCEs. Each DPM provides connections to *thirty* (30) differential pairs originating from the RTM, but carried through the COB's Zone 3 signal connector. The mapping of those thirty pairs to the mezzanine board's two RCEs is arbitrary and determined by application. The function of either RCE is determined not only by the mapping of those thirty pairs, but by the firmware and software it contains.

For the NRC, that function will be either as a *Feature Extractor* or as a *Formatter* (see Section 2.2).

For the NRC, each RCE on the DPM is connected to eight (8) differential pairs of the fabric interconnect and four (4) pairs on the base interconnect. For the fabric interconnect, although those eight pairs can be configured a variety of ways, they will, for the NRC be configured as one (1) channel of 10G-Ethernet (XAUI). For the base interconnect two pairs receive <u>TTC</u> (one primary and one redundant) and two pairs transmit <u>BUSY</u> (one primary and one redundant).

#### 2.6.3 Fabric Interconnect

The *Fabric* interconnect contains, as its principal feature, a local, *10-Gigabit Ethernet* (10-GE). Packets are switched on that network using a commercial, 1163 ball ASIC [38]. That ASIC is a fully compliant *Layer-2*, *10G-Ethernet* switch. Although fully provisioned for buffered transfer, switch operation is, by default, *cut-through* with an ingress/egress latency of less than 200 *Nanoseconds*. It is also a fully managed switch with a PCI*e* interface connected to the DTM's RCE. Through its interconnect the COB's RCEs appear as *nodes* on that *Ethernet*. The interconnect allows its physical network to be extended to both nodes and networks *external* to the COB. Those networks could be, for example, other COBs residing in the same shelf, or even nodes physically disjoint from both COB and its shelf.

*Internal* to its shelf, the interconnect extends its network through its connections to Zone 2 of its backplane, specifically those connections to that backplane's *fabric* interface. The interconnect has individual connections to each of the thirteen slots of the shelf's backplane. With a full mesh backplane, this allows each network of every COB to be connected to each network of every other COB. *External* to its shelf the interconnect extends its network through its connections to the COB's fiber-optic transceiver bay. That bay can contain up to *eight* (8) SFP+ transceivers [20].

The interconnect's switch is organized in units of *Ports*. Each port is composed of four *lanes* and each lane is constructed from two differential pairs. Each lane forms a full-duplex channel with one pair allocated for transmission and one pair for reception. Each lane of each port is capable of operating independently at a fixed set of speeds ranging from *1.0 Gigabits/second* up to *12.5 Gigabits/second*. Lanes may also be bound together to form a single *Ethernet* channel which operates at four times the speed of any one lane. For the NRC, which carries 10-GE, the switch is configured to run XAUI, requiring four lanes, each operating at *3.125 Gigabits/second*. The switch contains *twenty-four* (24) ports. Those twenty-four ports are allocated to the fabric interconnect as follows:

- One (1) port connected to the DTM bay (one RCE).

- *Eight* (8) ports connected to the four DPM bays (two per bay, one for each RCE).

- *Two* (2) ports are connected to the SFP+ transceiver cage.

- *Thirteen* (13) ports are connected to the fabric interface (P2).

In short, within a shelf, the fabric interconnect allows for the formation of a uniform *Ethernet* populated with a flat space of RCE nodes.

#### 2.6.4 Base Interconnect

The base interconnect's principal function is to manage and distribute *synchronous* timing to the COB's five bays. Note that unlike the fabric interconnect the protocol distributed over this interconnect is *application specific*. In further contrast to the fabric interconnect which functions identically *independent* of the shelf slot it occupies, the base interconnect has slot dependent responsibilities. This is a consequence of the fact that while the fabric interconnect uses ATCA's *fabric* interface, the base interconnect uses its *base* interface. That interface employs a backplane topology that is fixed by the standard at *dual-star*. ATCA refers to slots at its *roots* as *Hub* slots and slots at its *leaves* as *Node* slots. Necessarily, the behavior of a board, specifically its base interconnect, must vary depending on whether it occupies either a hub or a node slot. While boards in node slots need only distribute timing locally, boards occupying node slots must distribute timing not only locally, but also to other boards occupying its shelf. In short, while occupying a hub slot the base interconnect *drives* its base interface, but while occupying a node slot *receives* timing.

The distribution model for the base interconnect allows timing to originate from one of three potential sources:

- *Internal*, where the source is the *base* interface.

- *External,* where the source is the COB's *Front-Transition-Module* (FTM).

— *Local*, where the source is the COB's DTM.