# THE MEDIPIX3 TSV PROJECT

Jerome Alozy and Michael Campbell CERN Geneva, Switzerland 10 April 2013

2<sup>nd</sup> AIDA Annual meeting

Summary of project plans Medipix3 – designed for TSVs LETI process reminder Status of project Some key numbers for the LETI process Future plans

- Phase 1: TSV processing of Medipix3 wafers

- Process 10 wafers in CEA LETI

- Separated in 3 lots in order to improve the process step by

- step

- Third lot gave good preliminary results!

- Phase 2: Hybridization of the TSV processed chips

- Chip pick up and selection of KGD

- Preparation of sensors

- Flip chip to KGD

- Test of single assemblies

#### Phase 3: Demonstrator Module

- Mount single chip assembly on appropriate support cards

- Demonstrate multichip module operations

\* LETI contract supported at the level of 14% by AIDA Other partners: Alice, LCD, Medipix3 Collaboration

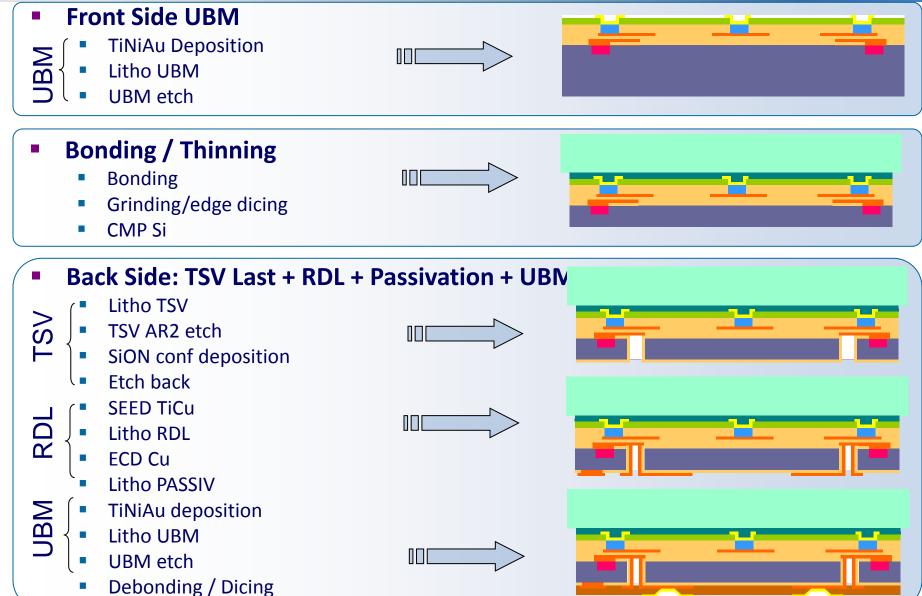

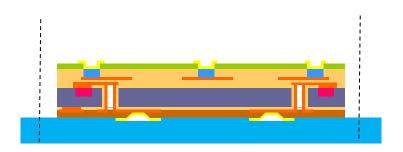

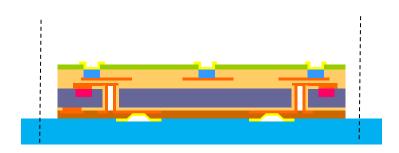

## **Reminder of LETI Process**

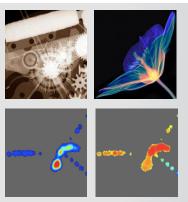

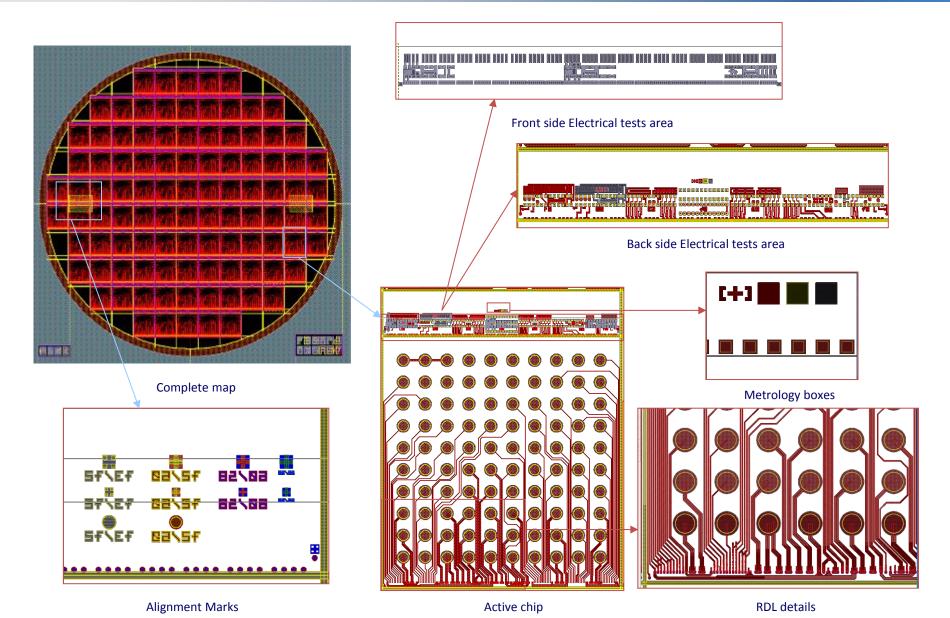

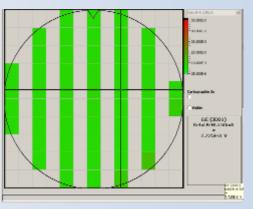

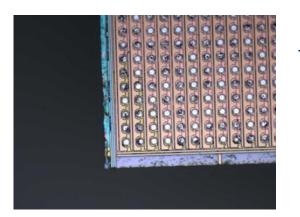

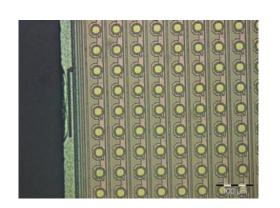

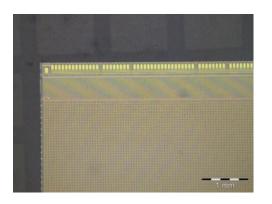

### Medipix3 chip photo

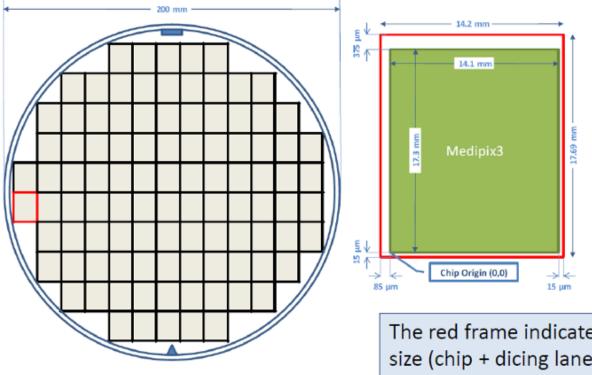

## **Medipix3 ready for Through Silicon Vias**

All IO logic and pads contained within one strip of 800µm width

All IO's have TSV landing pads in place

Permits 4-side butting

94% sensitive area

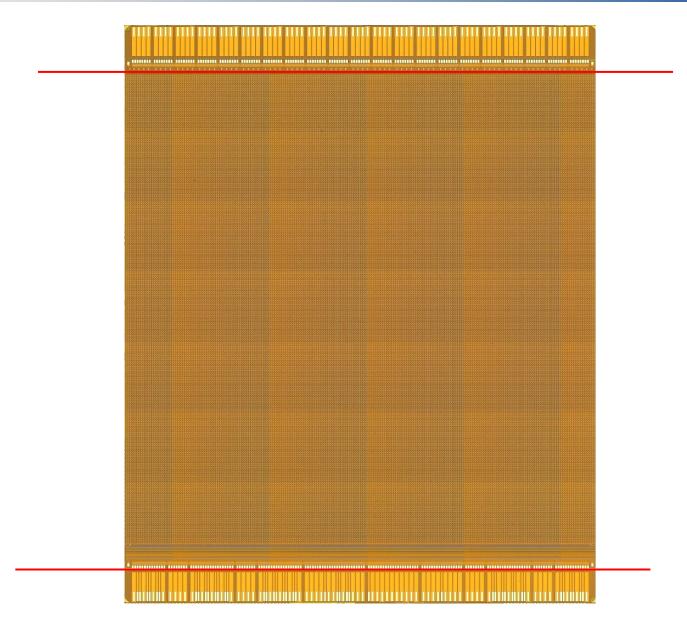

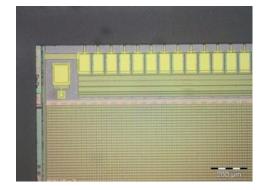

Wafer Layout

#### Approximatively 100 chips per wafer

Chip frame's outer size (metal ring) is 14099.600 um in X and 17299.6 um in Y.

The red frame indicates the reticle size (chip + dicing lane)

## **RDL** design (Timo Tick)

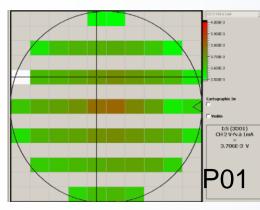

## Medipix 3 project results / electrical tests (non exhaustive)

#### UBM/ Al contact resistance

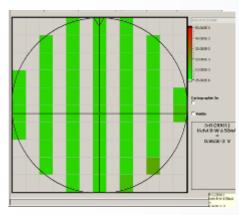

P01

0.22 0.24 0.26 0.28

0.2

Ohms

0.3

Cumulative resistance UBM/Alu Mean value : ~ 150 mohms

#### Conclusions:

☺ Isolation between UBM lines OK

0.1 0.12 0.14 0.16 0.18

☺ Alu/UBM contact resistance is OK

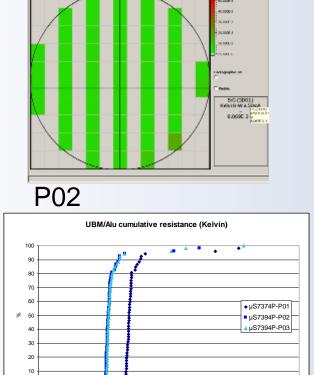

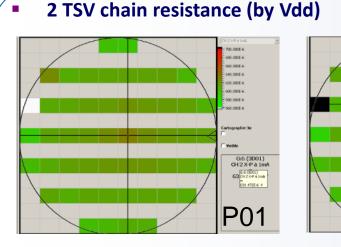

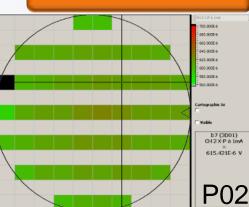

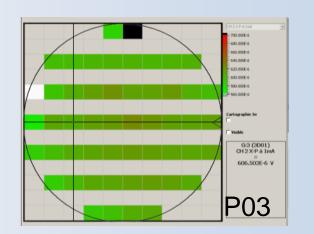

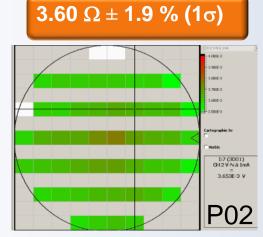

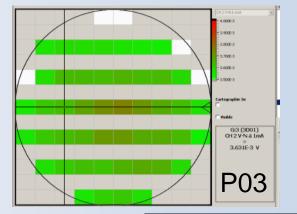

# Medipix 3 project results / electrical tests (non exhaustive)

**1.23**  $\Omega \pm$  **3.6** % (1 $\sigma$ )

2 TSV chain resistance (by Vss)

D. Henry, LETI

Conclusions:

$\odot$  Uniform distribution of values  $\rightarrow$  no comparizon with reference value possible

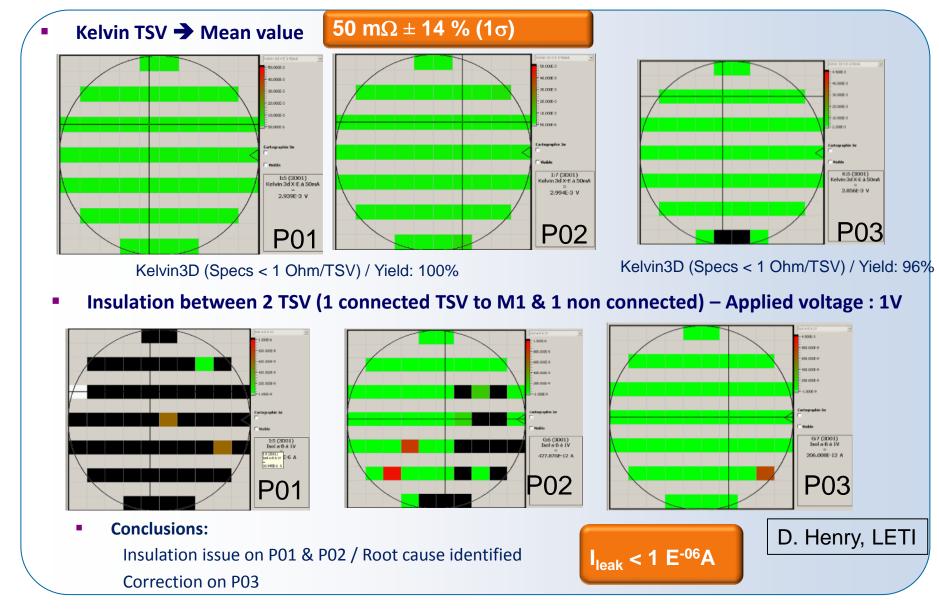

# Medipix 3 project results / electrical tests (non exhaustive)

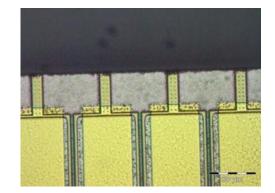

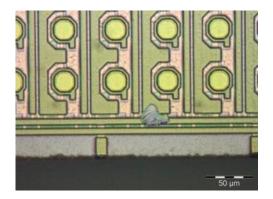

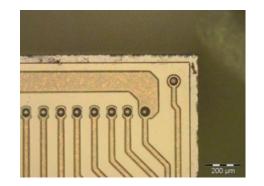

# **Dicing/chip pickup issues**

- Chips Dicing & boxes packaging

- First delivered wafers :

- Metal delaminations on front side

- High chipping on the edges

- Chips breaking during pick out process

- Tape residues on pixel side

High chipping + pad delamination

#### Tape residues

- Need to develop an optimized dicing process :

- DISCO collaboration

Backside chipping

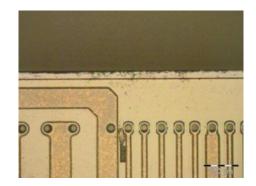

# **Dicing/chip pickup issues**

#### Dicing trials on DISCO plant (Munchen)

- Taping of BGA side on the tape

- UV tape

- Fine blade

- High Blade rotation

- Low Blade speed

#### Pixel side observations

- Lower chipping compare to previous dicing

- Every defects localized on dicing streets

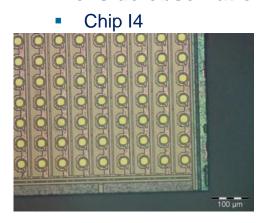

# **Dicing/chip pickup issues**

- Pixel side observations

- Chip I4

BGA side observations

- Higher chipping than on the pixel side  $\rightarrow$  contact with tape

- All defects localized on the dicing streets → polymer seal ring effect

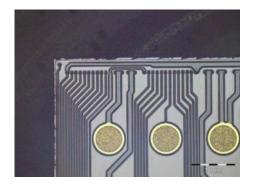

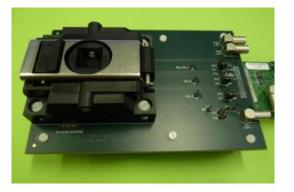

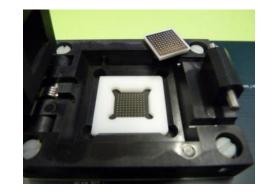

### **Test setup at CERN**

- Test set-up :

- Test board realize the interface between Medipix3 chip and readout interface

- Test socket is embedded on test board to establish contact to the bga pads of the chip

- We are using a custom readout interface (USB) common to most of MEDIPIX chip family

Test board

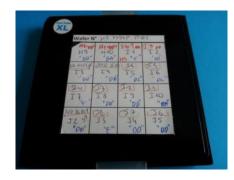

#### Test samples

- LETI sent a complete GELPAK of 16 diced chips. (DISCO dicing)

- Parts are from IBM wafer # AZNW5VH, at CERN it was identified as Wafer # 24

#### Test socket

#### Readout interface

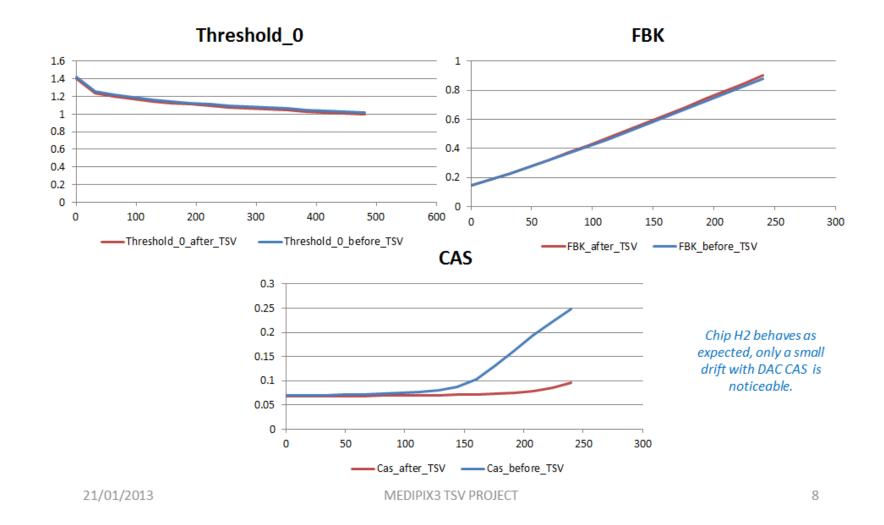

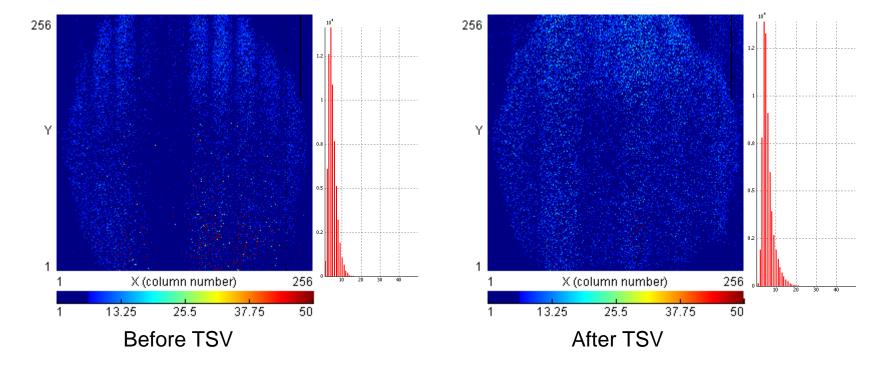

### DAC scans (normal for Medipix3)

### Noise floor comparison

We could notice only a slight difference

- AR (wafer thickness to TSV diameter) max 3:1

- Minimum TSV pitch 80um

- Minimum TSV diameter 40um

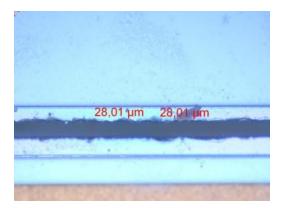

- RDL min track width 20um

- RDL min track space 40um

- RDL thickness range 2um to 12um Cu

- Front side UBM min space 30um

- Front side UBM min width 20um (For ref MPIX3 25um diameter on 55um pitch)

- Back side UBM min space 30um

- Back side UBM min width 20um

- TSV typical resistance 50mohm (60um on 120um thickness)

- TSV typical isolation >= 1Gohm

- Resistance UBM to AI pad 150mohm for 25um diameter.

### AIDA project

- First 2 assemblies have been received (VTT/Advacam)

- More to follow soon (need to bump sensors)

- Test card ready

- Low melting point BGA spheres ordered

### Future work (Medipix3 Collaboration/LCD)

- Process a further 6 Medipix3RX wafers at CEA

- Cover large area

- Smallpix edgeless chip design