#### SiPM Interconnections to 3D electronics

- SiMPs basics

- •Why do we need 3D interconnections

- •Concept of SiPMs with Bulk Integrated Quench Resistors SiPMI concept

- •What we want to do

Jelena Ninkovic

Max-Planck-Institute for Physics, Munich, Germany

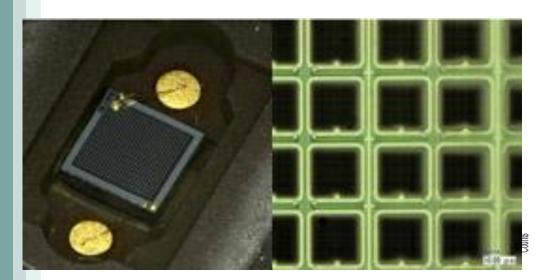

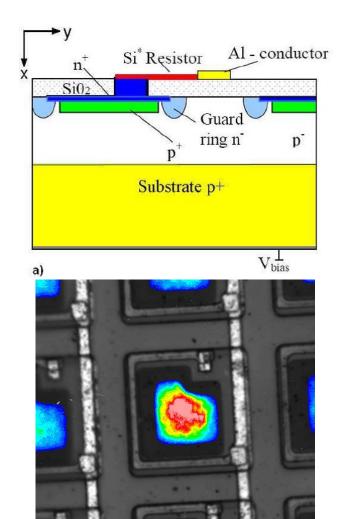

# What is a Silicon Photomultiplier - SiPM

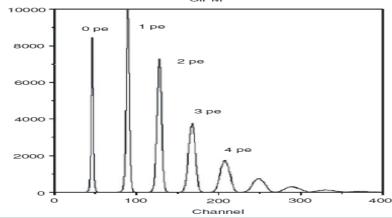

- An array of avalanche photodiodes

- operated in Geiger mode → binary device

- passive quenching by integrated resistor

- read out in parallel → signal is sum of all fired cells

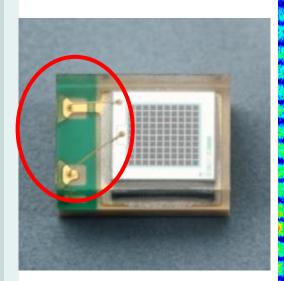

What is available? Uhalhlaitarlahar BI SI>BI T4 U2 PD Individual surface resistors Metal (Al) grid SiPM Pixels of the SiPM

#### Why do we need 3D integration?

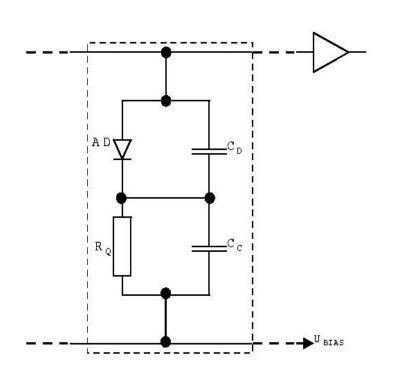

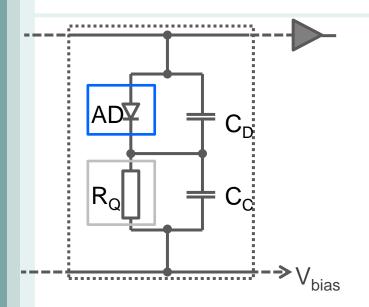

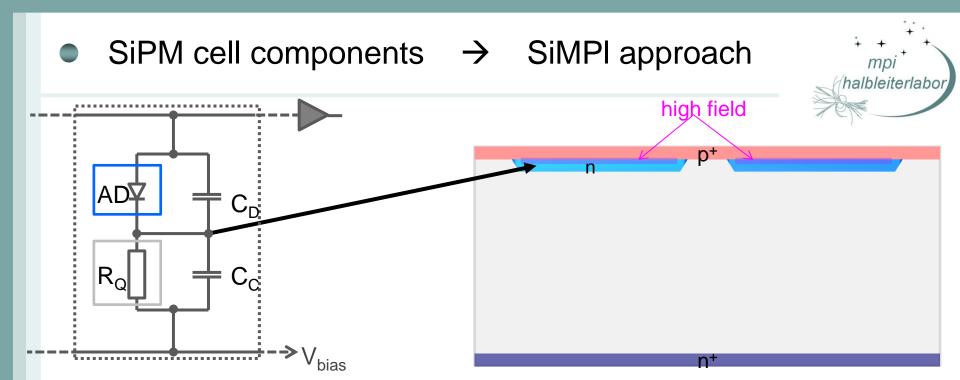

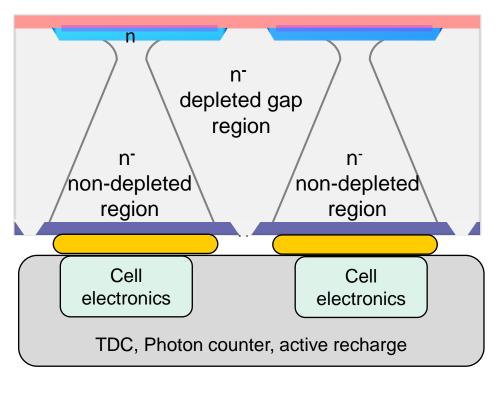

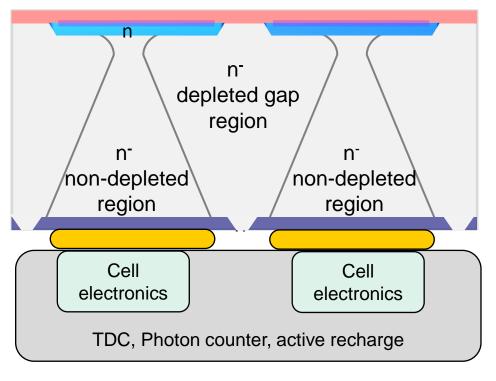

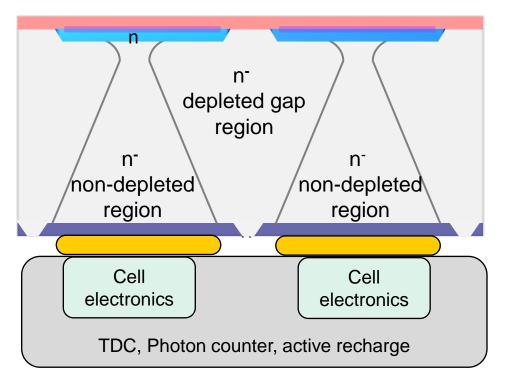

# Components of a SiPM cell

T

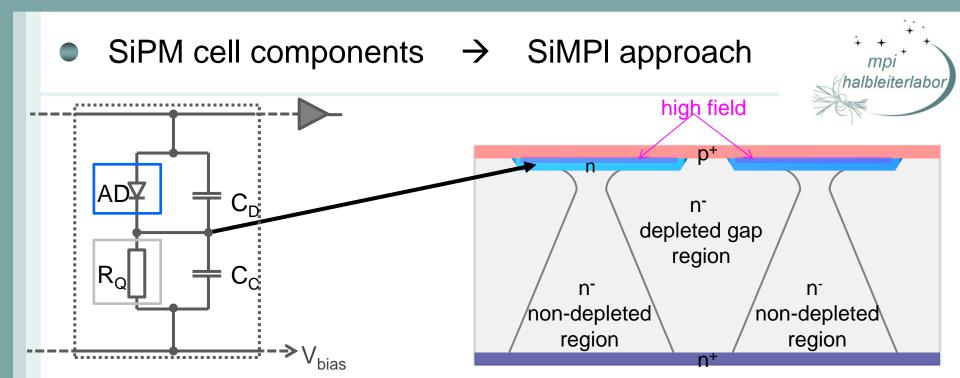

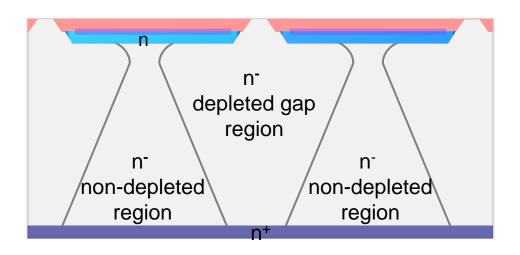

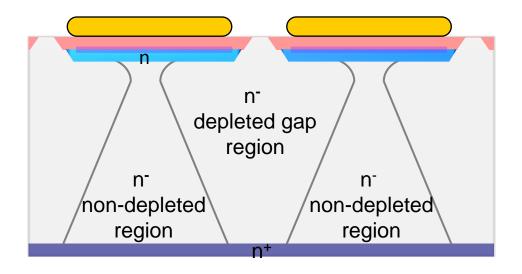

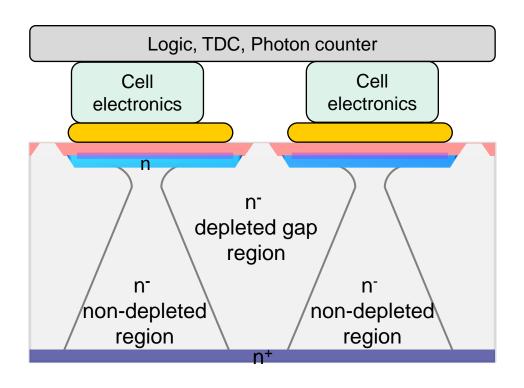

SiPM cell components → SiMPl approach

Concept developed at

Max-Planck-Society Semiconductor Laboratory

## Advantages and Disadvantages

#### Advantages:

- no need of polysilicon

- free entrance window for light, no metal necessary within the array

- coarse lithographic level

- simple technology

- inherent diffusion barrier against minorities in the bulk -> less optical cross talk

#### **Drawbacks:**

- required depth for vertical resistors does not match wafer thickness

- wafer bonding is necessary for big pixel sizes

- significant changes of cell size requires change of the material

- vertical 'resistor' is a JFET -> parabolic IV -> longer recovery times

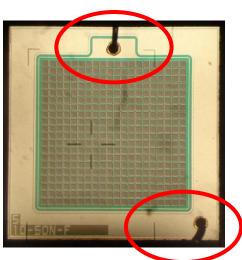

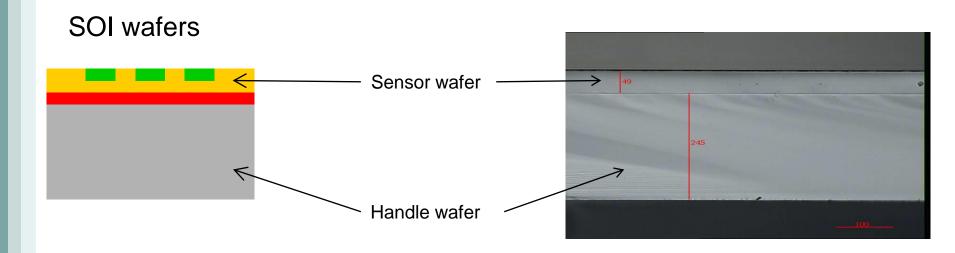

#### Prototype production

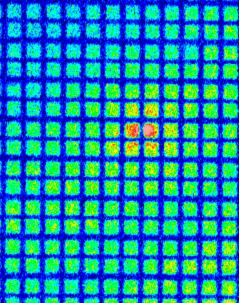

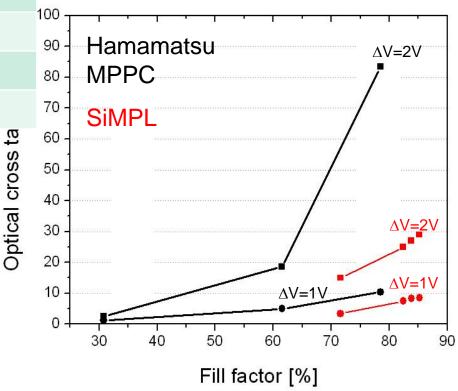

#### Fill factor & Cross Talk

#### Fill factor limited only by the cross talk suppression need!

| Pitch / Gap            | Fill<br>factor | Cross talk<br>meas.<br>(∆V=2V) |

|------------------------|----------------|--------------------------------|

| 130μm / 10μm           | 85.2%          | 29%                            |

| 130μm / 11μm           | 83.8%          | 27%                            |

| 130μm / 12μm           | 82.4%          | 25%                            |

| $130\mu m$ / $20\mu m$ | 71.6%          | 15%                            |

No special cross talk suppression technology applied just intrinsic property of SiMPI devices

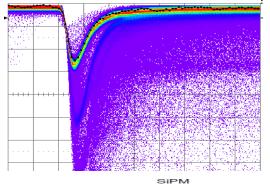

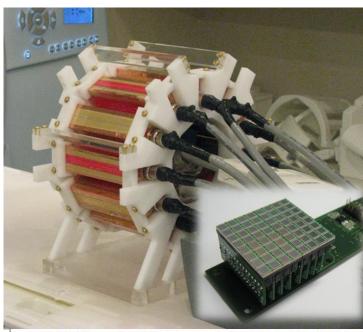

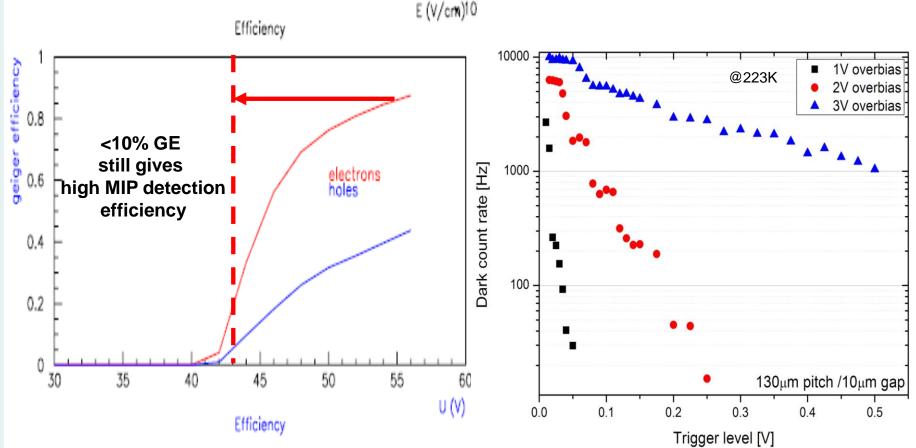

#### Detection of particles

Excellent time stamping due to the fast avalanche process (<1ns)

MIP gives about 80pairs/ $\mu$ m  $\rightarrow$  huge signal in SiPM $\rightarrow$  allows operation at small  $\Delta V$

Reduction of dark rate and cross talk by at least an order of magnitude

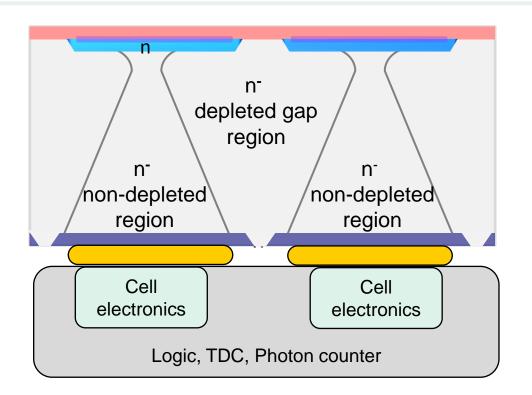

Topologically flat surface

High fill factor

Adjustable resistor value Low RC -> very fast

Active recharge

Ability to turn off noisy pixels

Cell electronics: Active quenching,

Bias control,

Cell activity,

Digital output

Pitch limited by the bump bonding

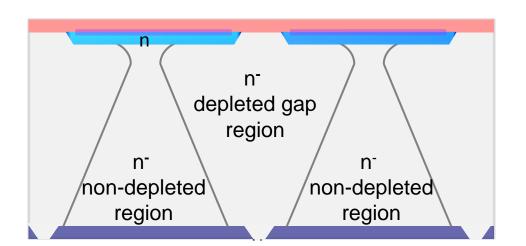

Topologically flat and free surface

High fill factor

Sensitive to light

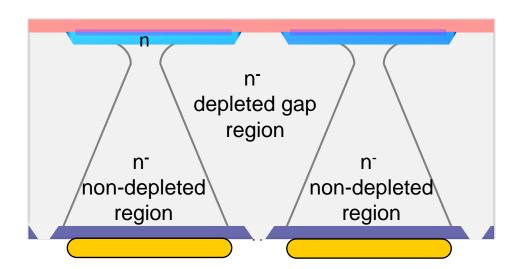

Topologically flat and free surface

High fill factor

Sensitive to light

Topologically flat and free surface

High fill factor

Sensitive to light

Topologically flat and free surface High fill factor Sensitive to light

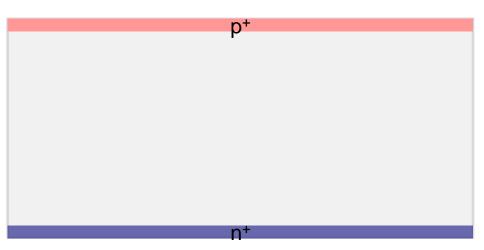

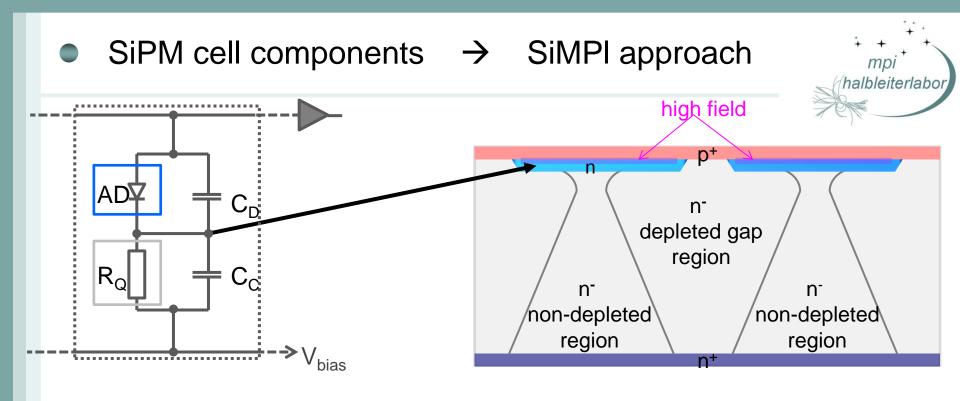

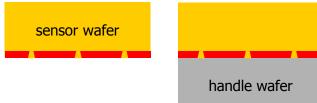

sensor wafer handle wafer

- 1. Structured implant on backside 2. bond sensor wafer on sensor wafer

- to handle wafer

3. thin sensor side to desired thickness

4. process SiMPI arrays on top side

Topologically flat and free surface High fill factor Sensitive to light

1. Structured implant on backside 2. bond sensor wafer to handle wafer

3. thin sensor side to desired thickness

4. process SiMPI arrays on top side

on sensor wafer

Topologically flat and free surface High fill factor Sensitive to light

1. Structured implant on backside 2. bond sensor wafer to handle wafer

3. thin sensor side to desired thickness

4. process SiMPI arrays on top side

on sensor wafer

# Thanks for the attention!!