# DATACENTER IMPERATIVES IN THE NEW ERA

#### HERBERT CORNELIUS TECHNICAL DIRECTOR ADVANCED COMPUTING, EMEA

## Legal Disclaimer

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

All products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright ° 2012, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

## WOVEN INTO THE

# FABRIC OF SCIENCE & BUSINESS

## **DATACENTER EVOLUTION**

#### DATACENTER 1990 - 2000 "DIVERSITY OF SYSTEMS"

#### DATACENTER 2000 - 2010 "VIRTUALIZED RESOURCE POOLS"

## DATACENTER **AS A SYSTEM**

#### FACILITIES NETWORKING HARDWARE SOFTWARE OPERATIONS

#### ENABLING "IT as a SERVICE" seamlessly integrated system architecture operating as one resource

## **IMPERATIVES**

### Competitiveness Performance, Efficiency & Agility

### Convergence Between Compute, Storage, Networking

Capabilities To Unlock Insights of Big Data

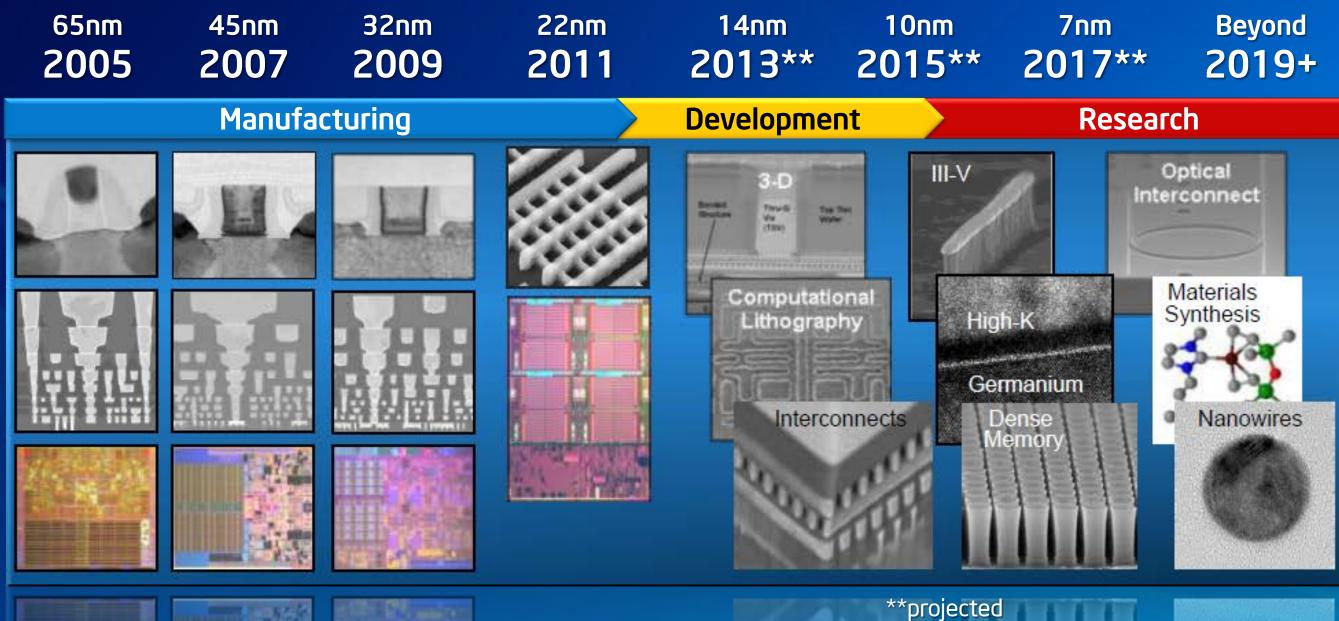

130 nm

200

90 nm

2003

## **TRANSFORMING THE ECONOMICS OF HPC**

Predictable Silicon Track Record **Executing to Moore's Law** Enabling new devices with higher performance and functionality while controlling power, cost, and size

65 nm

2005

180 nm 999

32 nm 2009

45 nm

2007

22 nm 2011

On Track 14nm

## **PROCESS TECHNOLOGY RESEARCH @ INTEL**

Potential future options, no indication of actual product or development, subject to change without notice.

## INTEGRATION

#### Example: Intel<sup>®</sup> Architecture **More Performance and New Capabilities**

integrated Integer ALU + integrated Floating-Point + integrated Cache

- + integrated SIMD + Multi-Core

- + integrated Memory Controller

I/O

New Instructions

#### + integrated Graphics + integrated

9

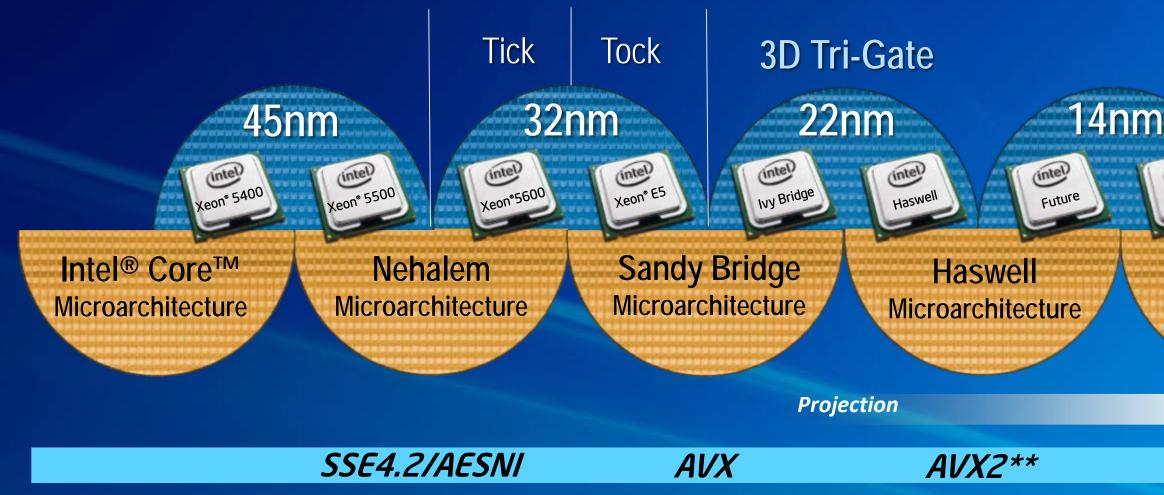

## **TICK-TOCK DEVELOPMENT CYCLES** Integrate. Innovate.

\*\*Intel® Architecture Instruction Set Extensions Programming Reference, #319433-012A, FEBRUARY 2012

Copyright © 2013 Intel Corporation. All rights reserved.

Potential future options, subject to change without notice.

intel

Future

#### **Future Microarchitecture**

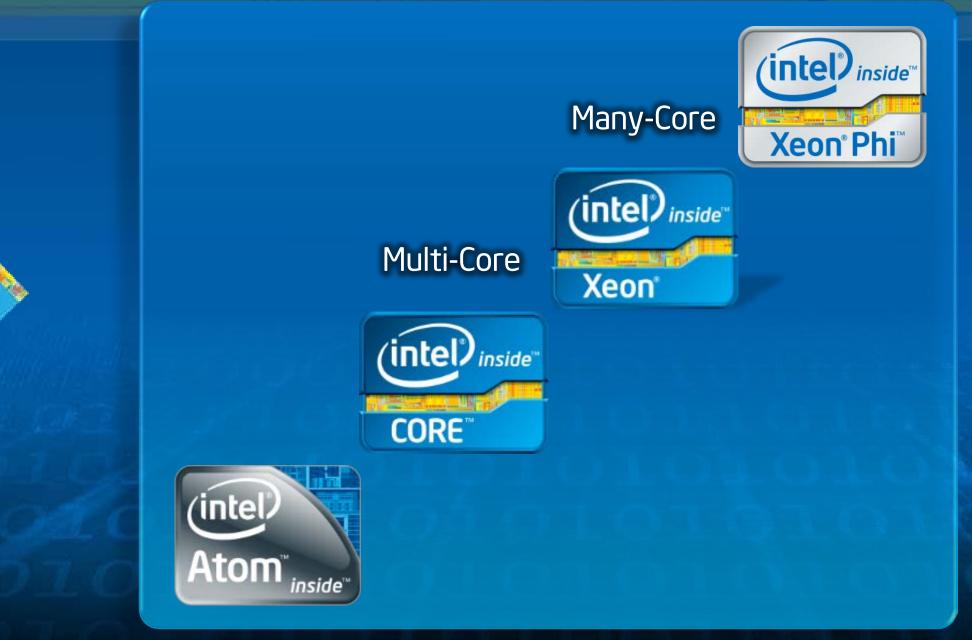

## FROM TERAFLOPS TO MILLIWATTS

#### Energy Efficient

## **EFFICIENCY EXAMPLE AT SCALE**

#### SUPERCOMPUTING

#### Top 500\* (1997 - 2012)

**1500X** Performance

**4X Power Increase**

Driven by Moore's Law & Architecture Innovation

Source: Intel Analysis / Top500

Copyright © 2013 Intel Corporation. All rights reserved.

### **100X** Reduction In cost per **FLOP**

(intel) inside

Xeon<sup>®</sup>Phi

## **WORLD RECORD!** "Beacon" at NICS

Intel<sup>®</sup> Xeon<sup>®</sup> + Intel Xeon Phi<sup>™</sup> Cluster Most Power Efficient on the TOP500 List Nov'2012:

Supercomputer Solutions

2.449 GFLOPS / Watt 70.1% Efficiency

intel)

Xeon

inside

## **INTEL TERASCLAE RESEARCH**

#### **MANY-CORE** COMPUTING

# PROCESSO STACKED N

#### Teraflops of computing power

#### **Terabytes** of memory bandwidth

Future vision, does not represent real products.

Copyright © 2013 Intel Corporation. All rights reserved.

### SILICON **PHOTONICS**

#### **Terabits** of I/O throughput

## **ASSUMING EXASCALE COMPUTING AT 20MW ... BY 2020**

#### New Forms of Energy

Space Exploration

#### **Ecological Sustainability**

#### **Medical Innovation**

And many others....

#### Data Center Sized <u>Exascale</u> System

Lower Volume Higher Cost

#### Rack Sized Petascale System

"Mainstream"

#### **Embedded Terascale** System

Higher Volume Lower Cost

### <u>cale</u> System 20MW

# <u>System</u>

#### e System 20W

## HPC: THE PATH TO EXASCALE

#### **Processors** Intel<sup>®</sup> Xeon<sup>®</sup> Processor

#### Co-Processor

Intel<sup>®</sup> Many Integrated Core

#### Fabrics

#### Parallel Studio XE Parallelism

(intel)

## HPC: THE PATH TO EXASCALE (CONT.)

#### Memory & Storage

#### Networking

#### **Reliability &** Resiliency

#### Power Management

# Energy Efficiency

## HOLISTIC OPTIMIZATION

### Facilities

### Network

Rack

Server

Silicon

### Application

Copyright © 2013 Intel Corporation. All rights reserved.

**TCO**

DISTRIBUTED ANALY

ORTABASE

NOILVISSO

APP SERVER

SERVER

FIREWALL

## The Server, Network, Storage LINES ARE BLURRING

Copyright © 2013 Intel Corporation. All rights reserved.

H) HINS

SUC STORE

NAS

NAS

ORACE

ROUTER

# NEW STORAGE OPTIMIZATIONS DRIVEN BY COMPUTATION

#### Real Time Compression

Thin Provisioning

### **NON VOLATILE MEMORY** Changing The Game In Datacenter Storage

inter

Моге **4**X IOPs vs. HDD LOWER 90% LOWER POWER CONSUMPTION

Ideal For Accelerating I/O & Throughput-bound **Applications**

## **NETWORK BANDWIDTH**

10GbE is required to make the transition to scale evolving to 40GbE to 100GbE ... and beyond

Vision concept, potential future options, subject to change without notice.

## **FABRICS INTEGRATION**

#### Benefits: Performance . Scalability . Efficiency . Power . Space . Costs

Copyright © 2013 Intel Corporation. All rights reserved.

Vision concept, potential future options, subject to change without notice.

## **SOFTWARE DEFINED NETWORKS** Agility And Scale for Next Gen Networks

Network Intelligence

Switch

#### DISCRETE FIXED FUNCTION

VIRTUALIZED SW DEFINED

API

Switch

Network

Intelligence

API

Switch

#### **Physical Switch**

Virtual Switch

## DATA CENTER RACK DESIGN EVOLUTION

• Distributed Switches

- Optical Interconnects

- Storage Appliances

- Shared I/O

#### **Step 1: Physical** Sheet Metal Reduction

**Consolidated Power Supply**

#### **Step 2: Distributed IO**

Switching and Storage Disaggregation

Step 3: Subsystem Compute, Memory & I/O Disaggregation

### **BIG DATA** Challenges and Opportunities

#### BUSINESS GENERATED

#### MACHINE & SENSOR GENERATED

### HUMAN GENERATED

# **IT IS TRANSFORMING** Convergence For Performance, Efficiency & Agility Datacenter Is The System

### INTEL INNOVATION & LEADERSHIP FOR THE ROAD AHEAD

# Thank You.