## **Our designs**

In the FPGA available today, there are purpose applications. A few well-kno products chains, etc. These chain stridentical logic elements. They are ide in our works, the fine TDC for the me performed in two different methods:

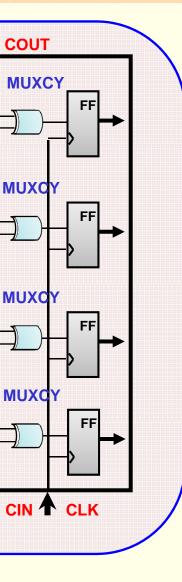

1. The first architecture, shown in Finewest available Xilinx Virtex 5 FPG the pertaining flip-flop on the rising et 2. The second architecture, shown in Finewest available Xilinx Virtex 5 FPG the pertaining flip-flop on the rising et al.

and it makes a differential delay line digital conversion process, the STC latches from the first cell up to the consecutively set.

To implement the designs in FPGA development software, a logic cell depending on the optimization algorithms. LEs may also be unpredictable to the placed and routed in this fashion, the To avoid this, the designer is forced layouts are presented respectively

diagrams of the Virtex 5 is shown.

test the two own in Fig.4. equency we

ased on an PGA based to access a nput a delay as data bus,

**Buffer to latch**

Buffer to