# Evaluation of Two SiGe HBT Technologies for the ATLAS sLHC Upgrade

Miguel Ullán & the SiGe Group

### The SiGe Group

D. Damiani, A.A. Grillo, G. Hare, A. Jones, F. Martinez-McKinney, J. Metcalfe, J. Rice, H.F.-W. Sadrozinski, A. Seiden, E. Spencer, M. Wilder *SCIPP, University of California Santa Cruz, USA*

M. Ullán, S. Díez Centro Nacional de Microelectrónica (CNM-CSIC), Spain.

W. Konnenenko, F. M. Newcomer, Y. Tazawa *University of Pennsylvania, USA*

R. Hackenburg, J. Kierstead, S. Rescia Brookhaven National Laboratory, USA

G. Brooijmans, T. Gadfort, J.A. Parsons, E. Wulf *Columbia University, Nevis Laboratories, USA*

H. Spieler Lawrence Berkeley National Laboratory, Physics Division, USA

> Igor Mandić Jozef Stefan Institute, Slovenia

J.D. Cressler , S. Phillips, A. K. Sutton Georgia Institute of Technology, School of Electrical and Computer Engineering, USA

### Overview

- Framework

- > S-LHC radiation levels

- > SiGe proposal

- SiGe Prototype designs

- ➤ Silicon Tracker (SGST)

- > LAr

- > Test chip

- Radiation Studies

- > Neutrons

- > Gammas

- Conclusions

- On-going work

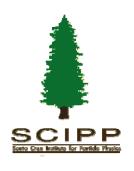

### Fluence in Proposed sATLAS Tracker

5 - 10 x LHC Fluence

Mix of  $n, p, \pi$  depending on radius R

Strips damage largely due to neutrons

ATLAS Radiation Taskforce http://atlas.web.cern.ch/Atlas/GROUPS/PHYSICS/RADIATION/RadiationTF\_document.html

#### **Design fluences for sensors** (includes 2x safety factor):

Innermost Pixel Layer (r=5cm):  $1.4*10^{16}$  neq/cm<sup>2</sup> 712 MRad Outer Pixel Layers (r=11cm):  $3.6*10^{15}$  neq/cm<sup>2</sup> 207 MRad Short strips (r=38cm):  $6.8*10^{14}$  neq/cm<sup>2</sup> 30 MRad Long strips (r=85cm):  $3.2*10^{14}$  neq/cm<sup>2</sup> 8.4 MRad

Pixels Damage due to neutrons+pions

### **Radiation Targets for Now**

There are no firm specifications yet for radiation levels, but based upon these simulation studies and the working "strawman layout" and consistent with the radiation levels to which the silicon sensor group is testing, we are presently targeting these values (which include one safety factor of 2).

| <ul><li>Short Strips</li></ul> | 6.8x10 <sup>14</sup> neq/cm <sup>2</sup> | 30 Mrad  |

|--------------------------------|------------------------------------------|----------|

| <ul><li>Long Strips</li></ul>  | 3.2x10 <sup>14</sup> neq/cm <sup>2</sup> | 8.4 Mrad |

| – LAr                          | 9.6x10 <sup>12</sup> neq/cm <sup>2</sup> | 30 krad  |

# Why SiGe

- The silicon microstrip detector (Si Strip Tracker: 5pF to 16pF) and the liquid argon calorimeter (LAr: 400pF to 1.5nF) for the ATLAS upgrade present rather large capacitive loads to the readout electronics.

- To maintain shaping times in the tens of nanoseconds, CMOS front-ends must increase bias currents to establish large enough transconductance.

- The extremely low base resistances of SiGe HBTs can accomplish this with relatively low bias currents thus affording possible power reduction.

- The low base resistance also minimizes the intrinsic base resistance noise allowing a good S/N ratio

- IBM provides two SiGe technologies along with their 130 nm CMOS as fully BiCMOS technologies.

- ➤ The 8HP process and the less expensive 8WL process.

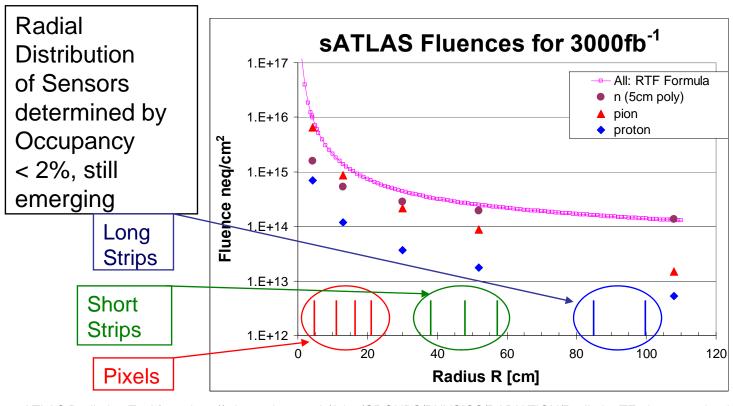

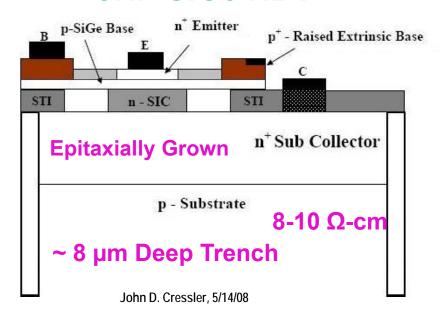

### 2 IBM SiGe techs.

- implanted subcollector (much shallower subcollector-substrate jx)

- "shallow" deep trench isolation ~ 3 μm (vs. 8 μm for 8HP)

- lightly doped substrate ~ 40-80  $\Omega$ -cm (vs. 8-10  $\Omega$ -cm for 8HP)

- $-100 / 200 \text{ GHz peak } f_T / f_{max} \text{ (vs. 200 / 285 GHz for 8HP)}$

#### 8HP SiGe HBT

#### 8WL SiGe HBT

### SGST Overview

#### SiGe Silicon Tracker readout test chip

- Circuit development goal: minimize power and meet SCT noise and 25 ns crossing specs.

- IBM **8WL process** is used, 0.13 μm 8RF CMOS with SiGe 140 Ghz npn added. To be submitted to MOSIS on **October 20**, 2008.

- Two detector loads simulated, including strays, of 5.5 pF for VT= 0.5 fC and 16 pF for VT = 1 fC. This corresponds to 2.5 cm and 10 cm strip lengths.

- Threshold and bias adjustment for device matching skew is included in design, using different strategy than ABCD or ABCNext, for lowered power rail to 1.2 V.

- Resistive front transistor feedback used to reduce shot noise from feedback current source. For long strips, this is good strategy for bias.

- Shaping time adjustable over +/- 15 % range.

- Overall, SiGe allows large current reduction in each analog stage as compared to 0.13 μm CMOS.

- Actual CMOS design is needed to quantify the power difference.

- SGST 0.2 mW/channel for long strips load sets a comparison point with CMOS.

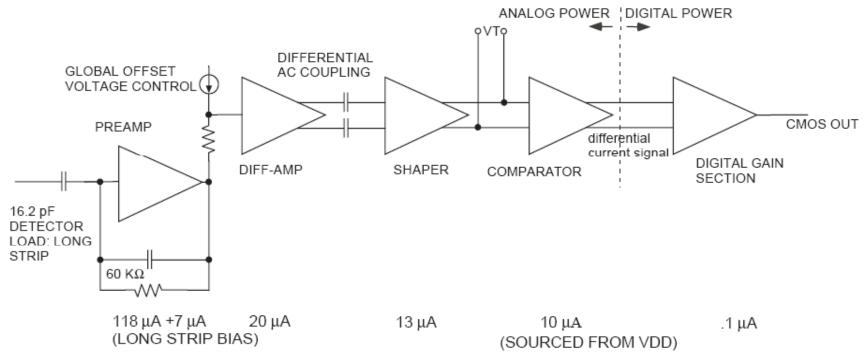

#### BLOCK DIAGRAM AND POWER FOR SIGE SCT FRONT-END

SGST biases total: 168 uA @ 16.2 pF (1350 e-), 108 uA @ 5.5 pF(900 e-)

0.2 mW/channel compares with ~1 mW for current SCT front-end. This is an essential power dissipation improvement!

SiGe technology allows very low power analog design.

Edwin Spencer, SCIPP

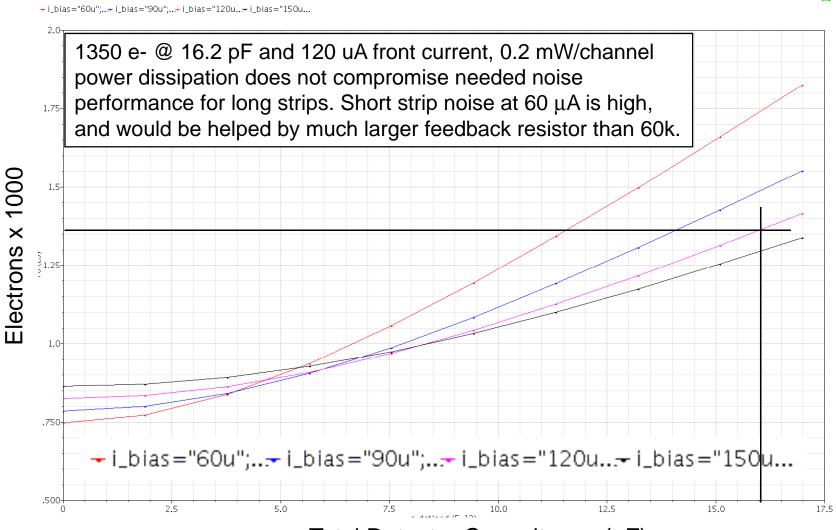

### SGST Simulated ENC performance

Total Detector Capacitance (pF)

600 nA detector leakage is included.

Edwin Spencer, SCIPP

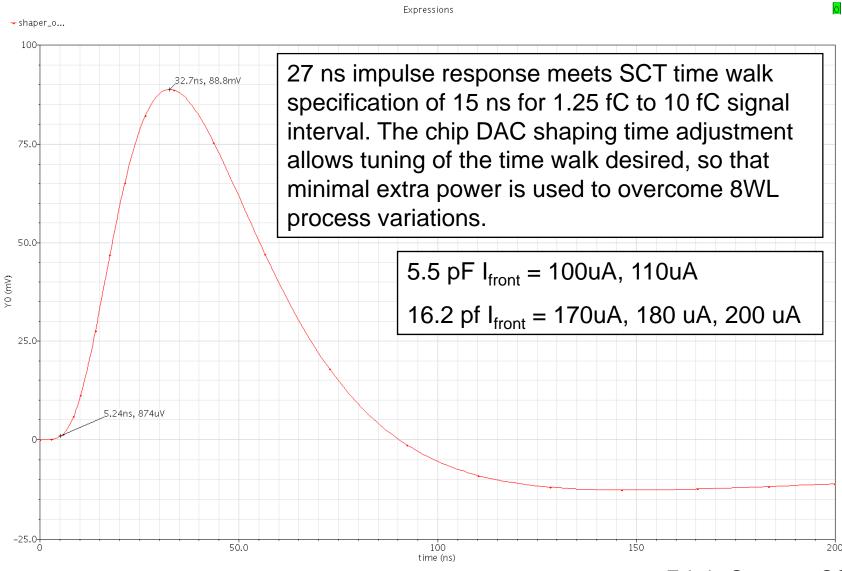

### Impulse Response at Comparator

Edwin Spencer, SCIPP

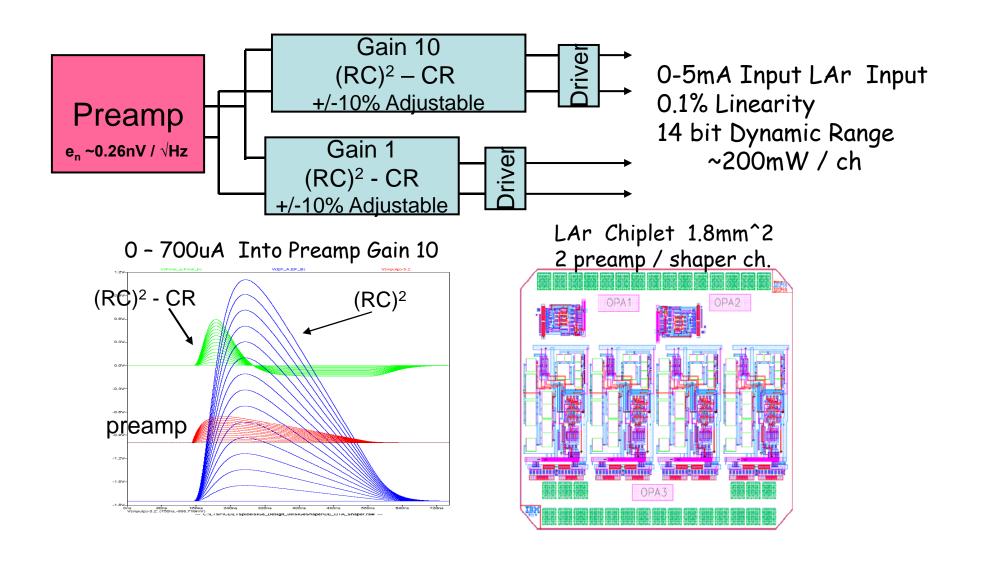

#### Prototype LAr Preamp and Shaper co-submission with SCT in 8WL

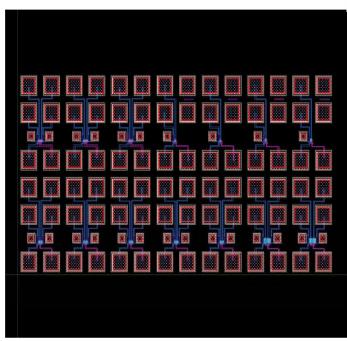

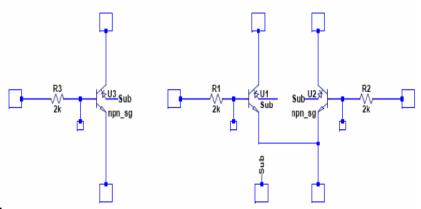

### 8WL Test Structures co-submission with SCT and LAr Chiplets

8WL Bipolar Test Structures Standard Kit Devices All 0.12 emitter width

| Item      | (HP trans<br>Quantity | sistors) |   |

|-----------|-----------------------|----------|---|

|           |                       |          |   |

| 1um diffp | air                   |          | 3 |

| 8um diffp | air                   |          | 5 |

| 20um/2st  | ripe diffpa           | ir       | 2 |

| 4         |                       |          | _ |

| 1um npn   |                       |          | 2 |

| 8um npn   |                       |          | 2 |

| Opndres   |                       |          | 1 |

| Opppcres  | 5                     | 1        |   |

| Oprppres  |                       | 1        |   |

| Oprrpres  | •                     | a.       | 1 |

| Ophibles  |                       |          |   |

|           |                       |          |   |

### CERN Micro Electronics Group CMOS8RF Test Structure Ported to 8WL for Direct CMOS comparison

MPW CERN CMOS Test Structures 0.6mm X 2mm

| Γ                                  | T                         |               |

|------------------------------------|---------------------------|---------------|

| Device                             | Size                      | Pad count     |

| 2.2nm gate oxide devices           |                           |               |

| NMOS W array, L=0.12               | W=0.16, 0.32, 0.48, 0.64, | 8 (s, g, 6xd) |

|                                    | 0.8, 2                    |               |

| NMOS L array, W=10                 | L=1, 10                   | 3 (g, 2xd)    |

| NMOS edgeless (ELT)                | W=min, L=0.12             | 1 (d)         |

| NMOS ZVt                           | W=3, L=0.42               | 1 (d)         |

| NMOS ZVt edgeless (ELT)            | W=min, L=0.42             | 1 (d)         |

| NMOS triple well array, L=0.12     | W=0.16, 1                 | 2 (2xd)       |

| PMOS W array, L=0.12               | W=0.16, 0.48, 0.8, 2      | 6 (s, g, 4xd) |

| PMOS L array, W=10                 | L=1, 10                   | 3 (g, 2xd)    |

|                                    |                           | 25            |

| 5.2nm gate oxide devices           |                           |               |

| NMOS W array, L=0.24               | W=0.36, 0.50, 0.8, 2      | 6 (s, g, 4xd) |

| NMOS L array, W=10                 | L=1, 10                   | 2 (2xd)       |

| NMOS edgeless (ELT)                | W=min, L=0.26             | 1 (d)         |

| NMOS ZVt                           | W=2.94, L=0.56            | 1 (d)         |

| NMOS ZVt edgeless (ELT)            | W=min, L=0.56             | 1 (d)         |

| NMOS triple well array, L=0.24     | W=0.36, 1                 | 2 (2xd)       |

| NMOS with metal filling on top     | W=0.36, L=0.24            | 1 (d)         |

| PMOS W array, L=0.24               | W=0.36, 0.50, 0.8, 2      | 6 (s, g, 4xd) |

| PMOS L array, W=10                 | L=1, 10                   | 2 (2xd)       |

|                                    |                           | 22            |

| Resistors                          |                           |               |

| OP N+ diffusion resistor           | L=0.28, 1.50 (R=11.66 and | 3             |

|                                    | 2.40 kΩ respectively)     |               |

|                                    |                           | 3             |

| FOXFETs                            |                           |               |

| Nwell/Nwell foxfet array, W=200    | L=0.92, 1.48              | 3             |

| N+diff/N+diff foxfet, W=200        | L=0.18                    | 2             |

| N+diff/Nwell foxfet array, W=200   | L=0.3, 0.6                | 2             |

|                                    |                           | 7             |

| Diodes                             |                           |               |

| Forward biased diodes array p+ in  |                           | 3             |

| Nwell, Area = 1680 µm <sup>2</sup> | small perimeter (164µm),  |               |

8WL CMOS

### Radiation Studies

- 2 IBM BiCMOS SiGe technologies being evaluated using "spare" test chips from IBM

- > 8HP

- > 8WL

- Gamma irradiations

- ➤ Brookhaven National Laboratory

- ➤ Doses: 10, 25, 50 Mrads(Si)

- ➤ Biased shorted floating

- Neutron irradiations

- > TRIGA Nuclear Reactor, Jozef Stefan Institute, Ljubljana, Slovenia

- ➤ Fast Neutron Irradiation (FNI) Facility, University of Massachusetts

Lowell Research Reactor

- Fluences: 2 x 10<sup>14</sup>, 6 x 10<sup>14</sup>, 1 x 10<sup>15</sup>, 2 x 10<sup>15</sup> eq. 1 MeV neutrons/cm<sup>2</sup>

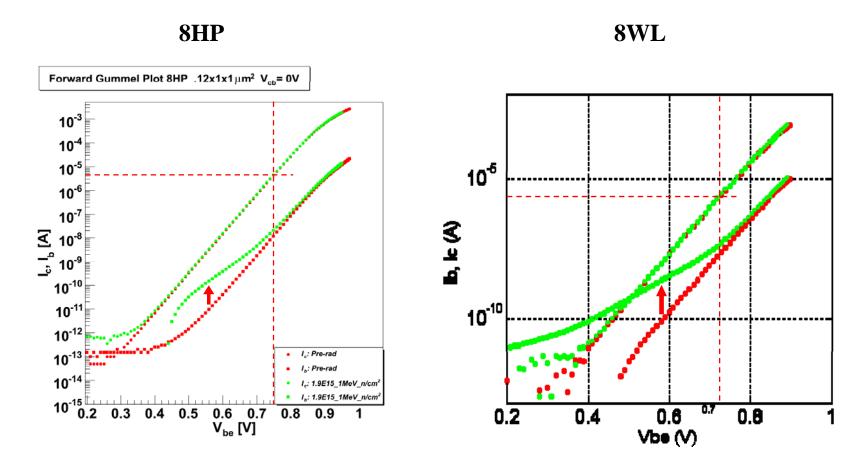

# Radiation Damage – Neutrons

- Forward Gummel Plots of SiGe Bipolar transistors:

- $\triangleright$  Base current increase  $\Rightarrow$  Current gain ( $\beta$ ) decreases at relevant current densities

### Radiation Damage - Gammas

- Forward Gummel Plots of SiGe Bipolar transistors:

- $\triangleright$  Base current increase  $\Rightarrow$  Current gain ( $\beta$ ) decreases at relevant current densities

8HP 8WL

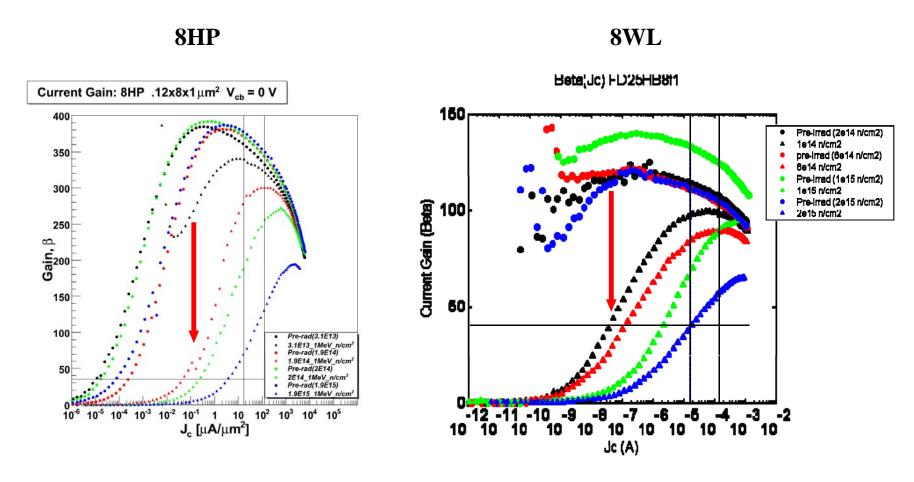

# Current gain ( $\beta$ ) vs. $J_C$ – Neutrons

- Beta vs. injection level (collector current density)

- ➤ High transistor damage although very dependent on injection level

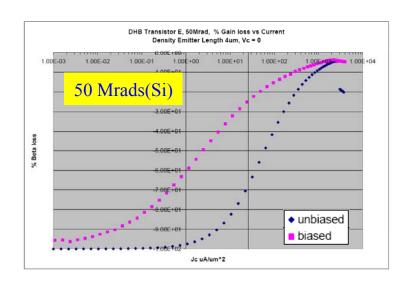

# Current gain ( $\beta$ ) vs. $J_C$ – Gammas

- Beta vs. injection level (collector current density)

- ➤ High transistor damage although very dependent on injection level

8HP 8WL

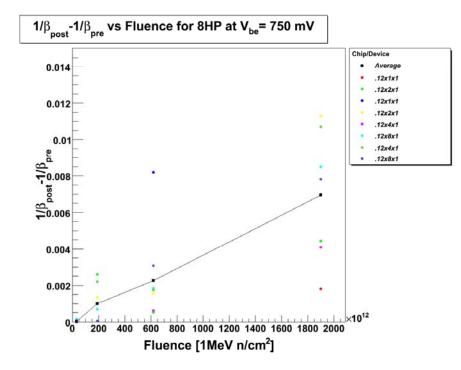

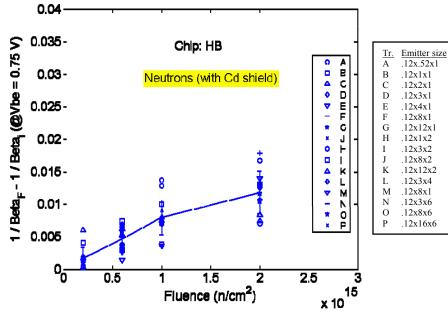

# Reciprocal gain – Neutrons

- $\Delta(1/\beta) = 1/\beta_F 1/\beta_0$  (@V<sub>BE</sub> = 0.75 V)

- Linear with fluence as expected \_\_\_\_\_

- High dispersion among transistor types

G. C. Messenger et al:

$$\frac{1}{h_{fe}} = \frac{1}{h_{fe0}} + K(E)\Phi$$

where the term  $1/h_{fe0}$  is the initial reciprocal gain, K(E) is the particle- and energy-dependent displacement damage factor, and  $\Phi$  is the incident particle fluence.

8HP 8WL

Miguel Ullán

CNM, Barcelona

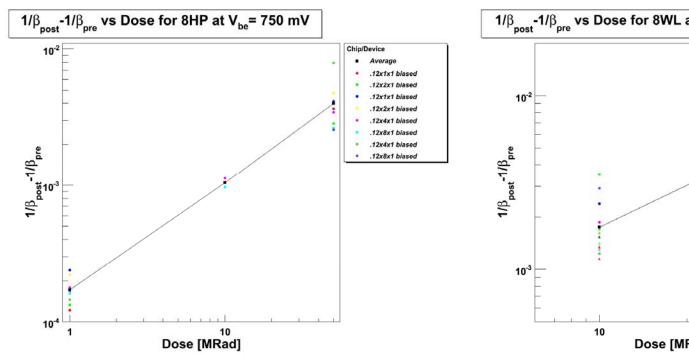

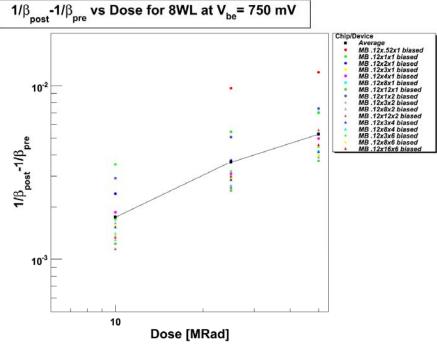

# Reciprocal gain – Gammas

- Linear in the log-log axis  $\Delta(1/\beta) \propto (dose)^a$

- High dispersion in 8WL results

8HP

8WL

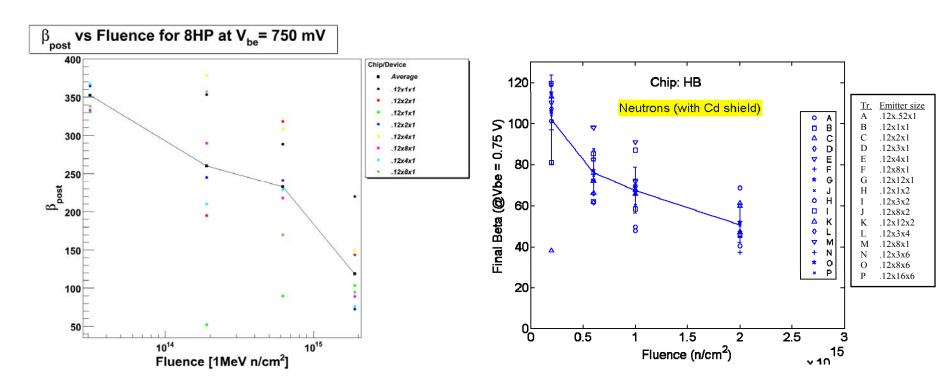

# Final Transistor gain – Neutrons

- $\beta_F >> 50 \ (@V_{BE} = 0.75 \ V) \ after \ 6 \ x \ 10^{14} \ eq. \ 1 \ MeV \ n/cm^2$

- Higher final gains in 8HP transistors (also pre-irrad)

- Some dispersion specially in 8HP transistors

8HP 8WL

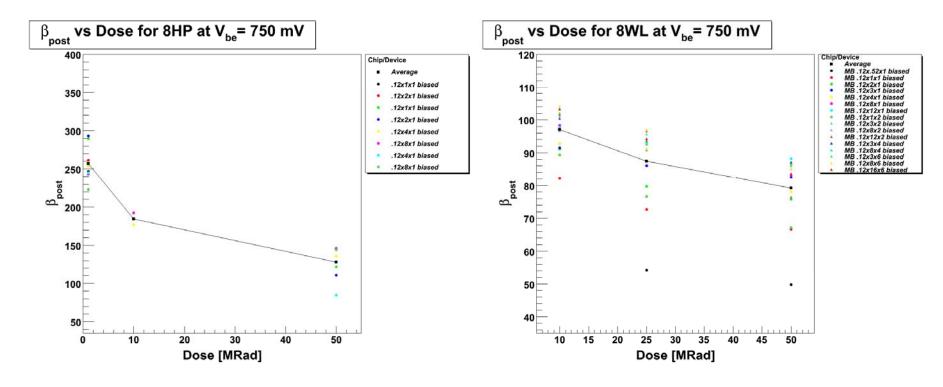

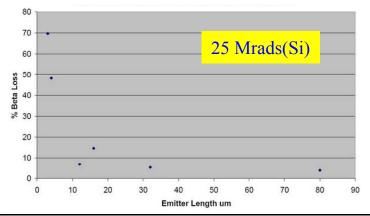

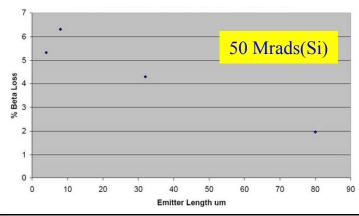

# Final Transistor gain – Gammas

- $\beta_F >> 50 \ (@V_{BE} = 0.75 \ V) \ after 50 \ Mrads$

- Also higher final gains in 8HP transistors

- Some dispersion in 8WL transistors

8HP 8WL

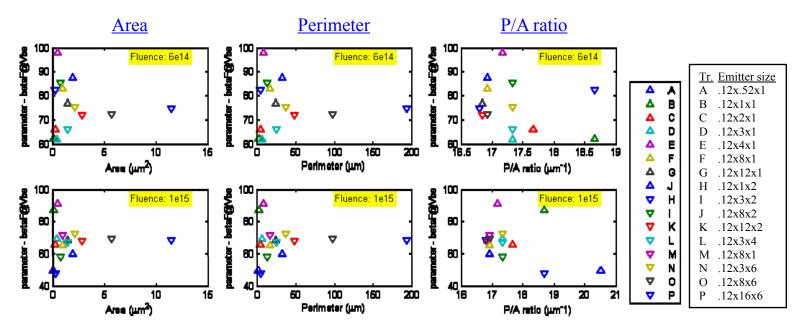

### Dispersion

- High dispersion in radiation results among transistors, especially in 8WL.

- It is not related with emitter geometry:

- We believe it is due to problems or variability in the test structure.

- We do not know the real cause, but we want to try with our own test chip made with design-kit transistors in case it is related to that.

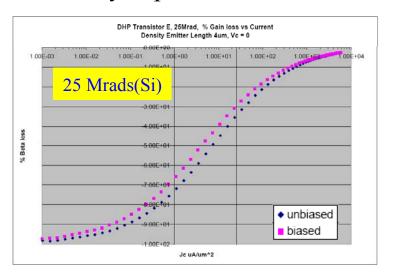

### Bias effects studies

• Effects very dependent on total dose

• Seems to be a strong correlation between emitter length and beta damage for the unbiased transistors

#### Conclusions

- The electrical characteristics of both SiGe technologies make them good candidates for the front-end readout stage for sensors that present large capacitive loads and where short shaping times are required, such as the upgraded ATLAS silicon strip detector (especially long strip version) and the liquid argon calorimeter.

- The devices experience performance degradation from ionization and displacement damage.

- The level of degradation is manageable for the expected radiation levels of the upgraded ATLAS LAr calorimeter and the silicon strip tracker.

- The dispersion of final gains after irradiation may be a concern which warrants further investigation.

- The initial quality of the test structures may be clouding the higher fluence results.

# On-going work

- Fabrication of Si tracker and LAr readout circuits, plus a custom designed test structure array.

- Pre and post irradiation testing of all three fabrications.

- Low Dose Rate Effects (LDRE) study.