**CERN PH-ESE Electronics Seminar**

# Time to Digital Converters and results from a new 5ps TDC prototype ASIC

Lukas Perktold<sup>1</sup> PH-ESE-ME

26 March 2013

<sup>1</sup>Graz University of Technology / CERN lukas.perktold@cern.ch

### Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

## Time-to-Digital Converters in HEP

#### Large systems with many channels (100k or more)

- Electronics distributed over larger area

- Time resolution and stability across whole system Distribution of common time reference to all the channels

- Detector time resolution sets requirements for TDC

#### Drift time in gas based tracking detectors

- Low resolution: ~1ns

- Examples: CMS and ATLAS muon detectors

#### Time of flight detectors

- High resolution: 10ps 100ps

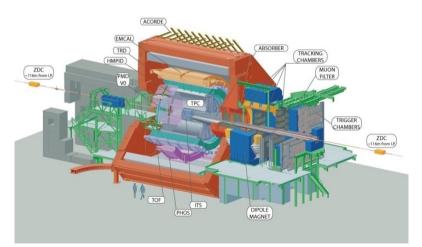

- Example: ALICE TOF

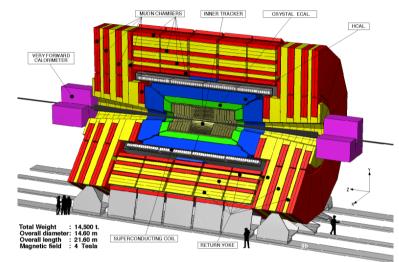

CMS

ALICE

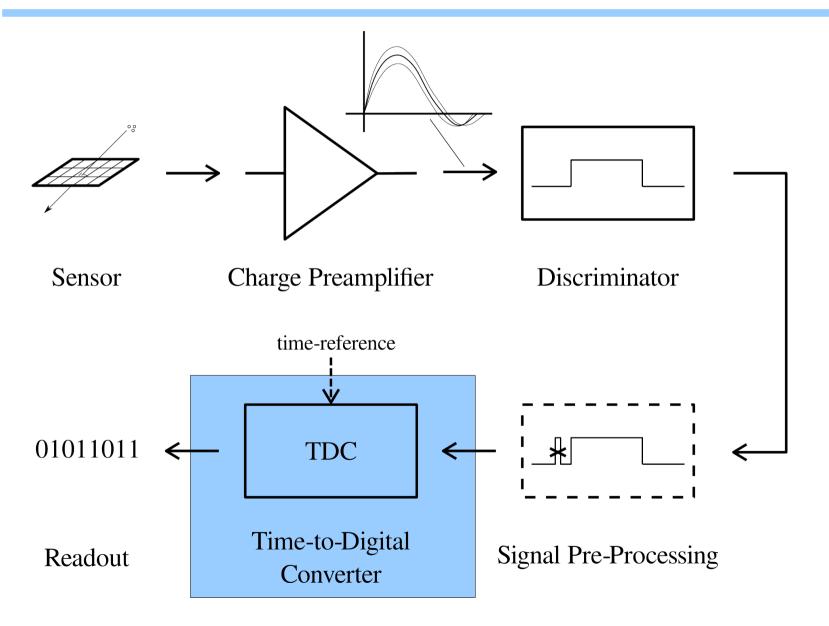

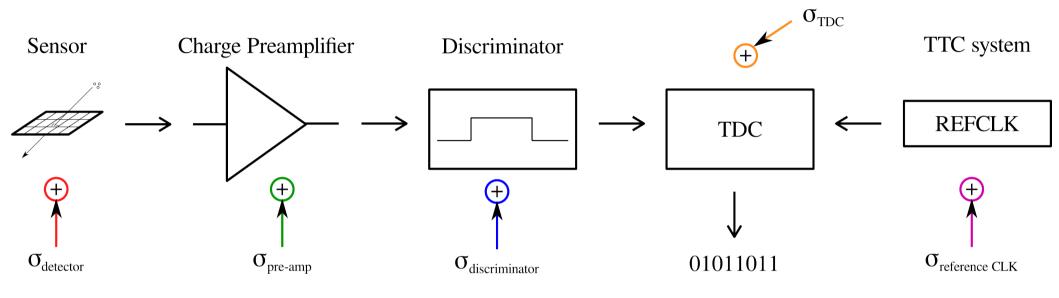

#### Time Measurement Chain

# Special needs for high energy physics

#### **Other Applications**

- Frequency synthesizer (All Digital PLLs)

- Laser Ranging and Radar Applications (distance measurement ...)

- On-Chip Instrumentation (Jitter ...)

- Imaging Systems (Positron Emission Tomography, Time Correlated Single Photon Counting ... )

- •••

#### In HEP often have different needs

- hundred / thousands of channels

- often single shot time precision

- distributed large systems (common time reference)

- high dynamic range (25 ns)

- hit rates (kHz Mhz)

```

• ••

```

### Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

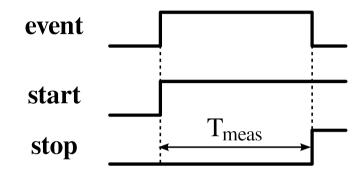

#### Time Measurements

#### **Start - Stop Measurement**

- Used for measuring time interval between two local events

- No absolute time measurements possible

- Often used for small local systems and for low power applications

#### **Time Tagging**

- Used for measuring the time of an event relative to a time reference (e.g. clock)

- Absolute time measurements possible

- For large scale systems with many channels all synchronized to the same reference

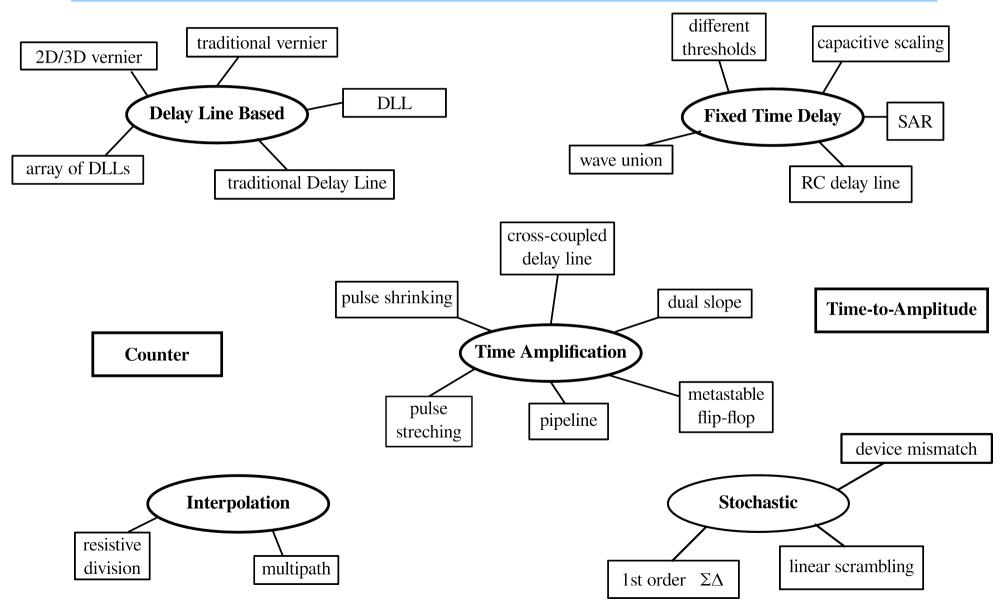

### **TDC** Architectures

**CERN PH-ESE Electronics Seminars**

L. Perktold - 26-March-2013

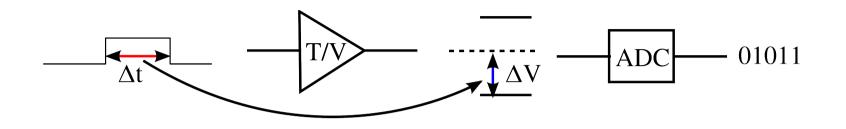

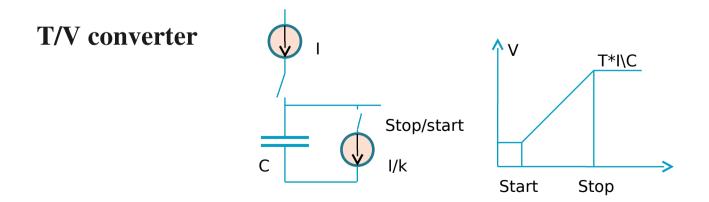

#### Time to Amplitude

- convert time difference into voltage domain

- resolution defined by T/V-converter and ADC

- move complexity to ADC domain

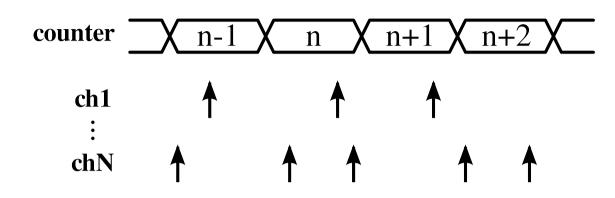

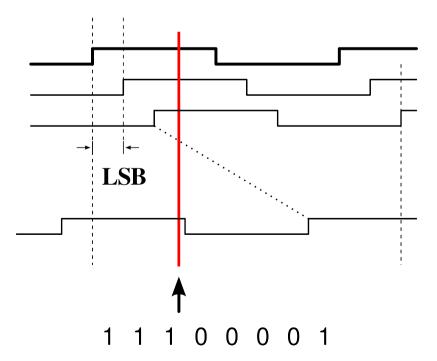

### **Counter Principle**

- on arrival of hit, store counter state

- hit can arrive at switching point of counter

-> synchronize hit to counter / use gray counter

- timing precision limited by clock period = LSB

#### quantization noise

for uniformly distributed hits:

$$\sigma_{TDC} = \frac{LSB}{\sqrt{12}}$$

e.g. 1 GHz counter -> 1ns LSB -> ~ 300 ps-rms

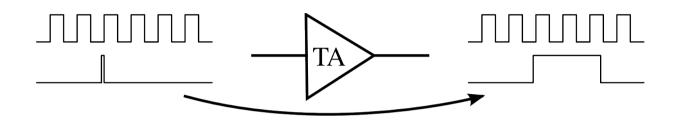

## Time Amplification

• Amplify time difference

-> relaxed second stage TDC (e.g. counter)

- Precision of TA defines resolution

- Dead-Time

#### **TA concepts**

- Dual-slope

- Metastable FF

- Cross-coupled delay line

- Pulse stretching

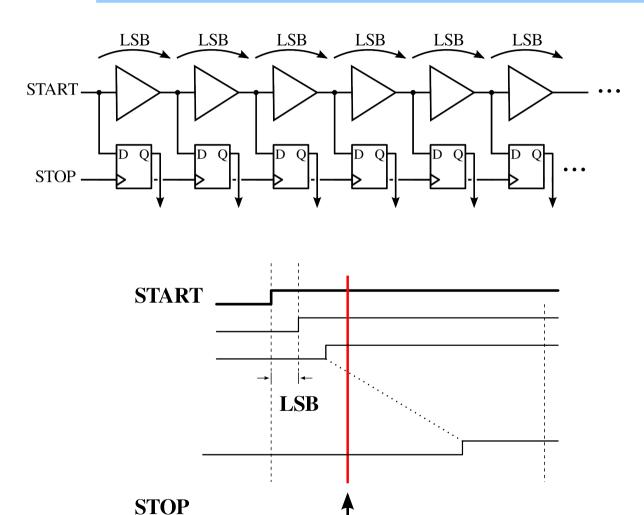

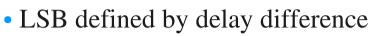

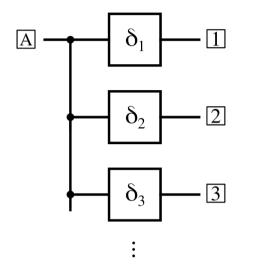

### Delay Line Principle

1

- generate set of delayed signals

- on hit store the state of delay-line

- LSB size limited by the gatedelay of the technology

digital code

0 0 0 0 0

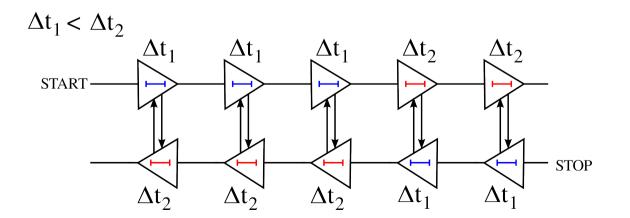

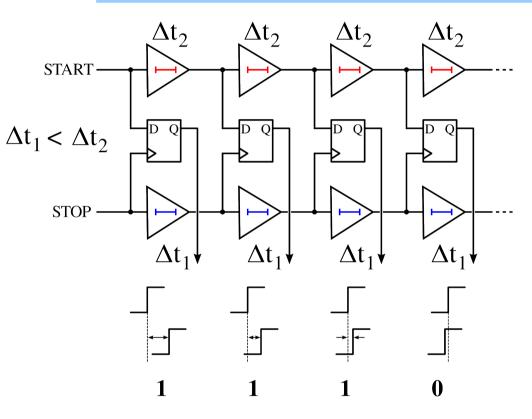

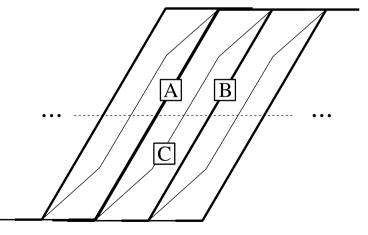

### Vernier Delay Line

#### **TA concepts**

- 2D Vernier Line

- 3D Vernier Line

- Array of DLLs

- ...

- Reduce relative delay between signals in each stage

- Long propagation delays on both paths

#### **Array of DLLs**

# Fixed Time Delay

#### **Fixed time delay concepts**

- <u>Capacitive scaling</u>

- Different thresholds

- Wire Delay / RC delay

- Buffer scaling

- SAR

• ...

- Change signal propagation delay relative to each other

- constant delay

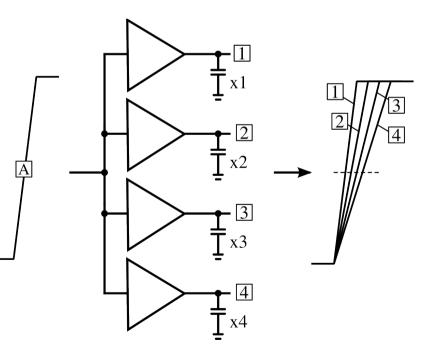

### Interpolation

- Intermediate signals generated out of two time delayed signals

- Allows generation of sub gate delay LSB sizes

- Signal edges need to be overlapping

#### **Interpolation concepts**

- <u>Resistive Division</u>

- Multipath Buffers

•

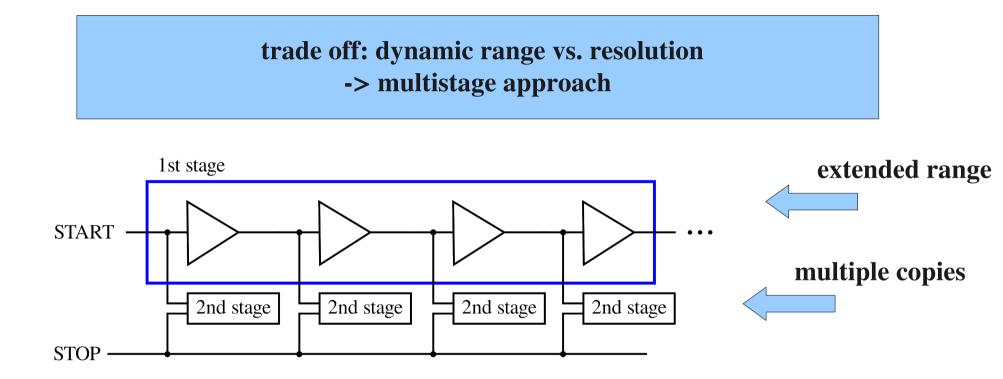

### Multistage Approach

- high resolution 2nd stage w/ small dynamic range

- multiple copies to increase dynamic range

- dynamic range of 2nd stage fits dynamic range of one bin of 1st stage

- long delay lines for large dynamic ranges

CERN PH-ESE Electronics Seminars L. Perktold - 26-March-2013

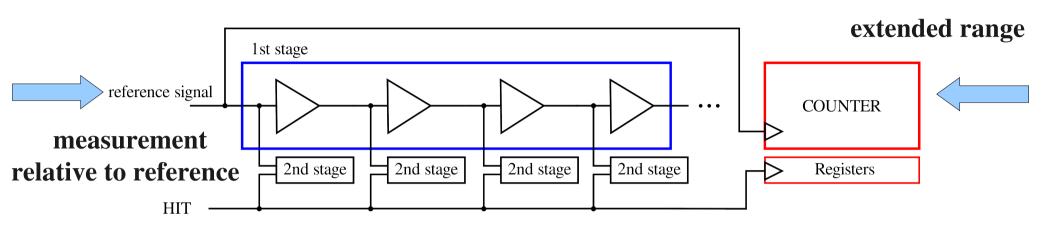

#### **Counter Extension**

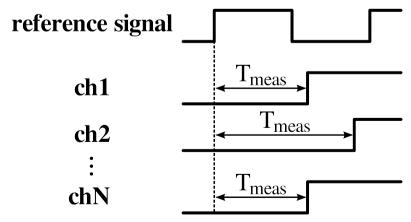

#### relate measurement to reference signal

- delay needs to fit one reference clock cycle

- analog / digital control

#### counter metastability

- hit is an asynchronous event

- double counter / gray & additional bit

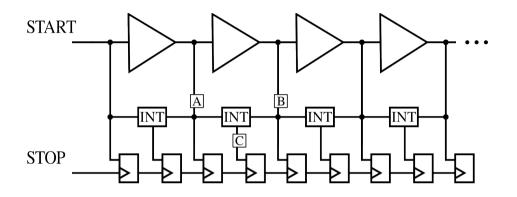

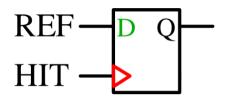

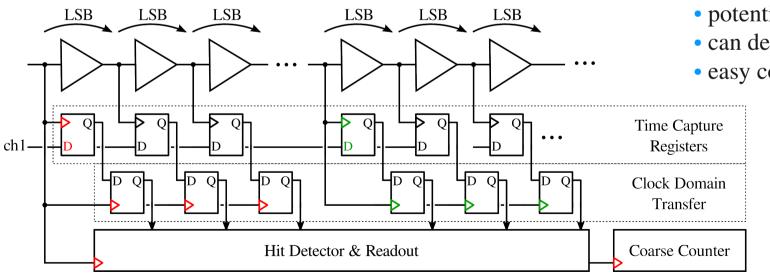

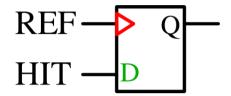

### Event vs. Data Driven Architecture

• sample state of reference signal

#### **Data Driven Example**

**Data Driven**

• sample state of HIT signals

- potentially no dead-time

- can detect multiple transitions

- easy counter synchronization

- constant data flow

- clock domain transfer

- higher power consumption (3x registers)

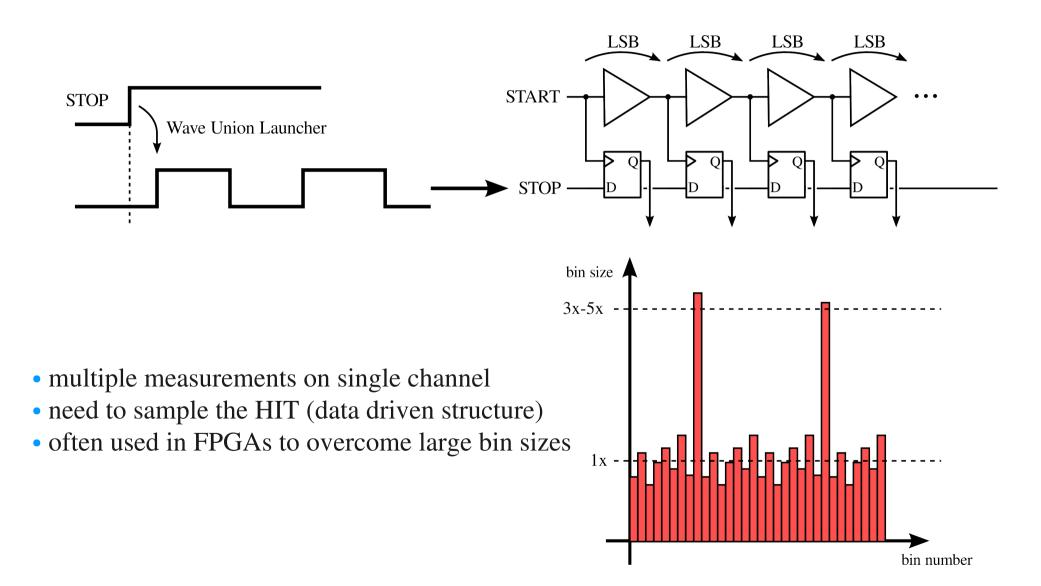

### Wave Union TDC

### Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

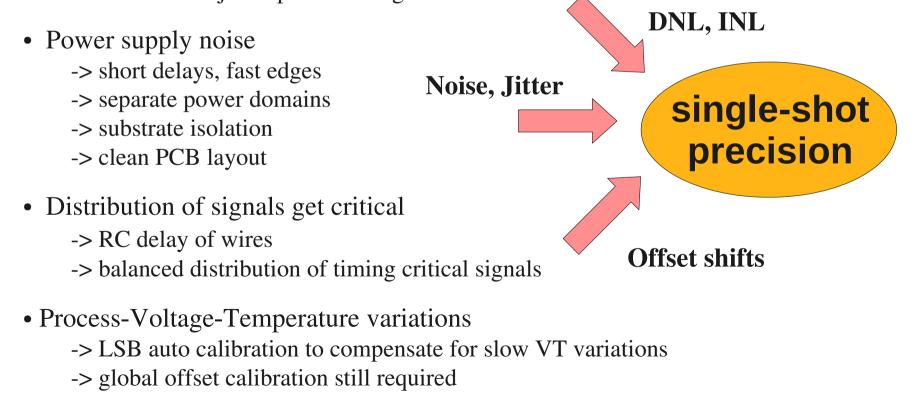

# Difficulties in ps range resolution

#### LSB/sqrt(12) ≠ rms

In sub-ps resolutions device mismatches can become dominant

-> careful simulation & dimensioning during design time

-> can have major impact on design

#### System Level

#### **Complete Measurement Chain**

- Detector Noise

- Analog Front End

- Time Walk Correction

- Time Reference Noise

- TDC Noise

- Inter-channel Crosstalk

- PVT variation ...

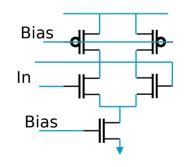

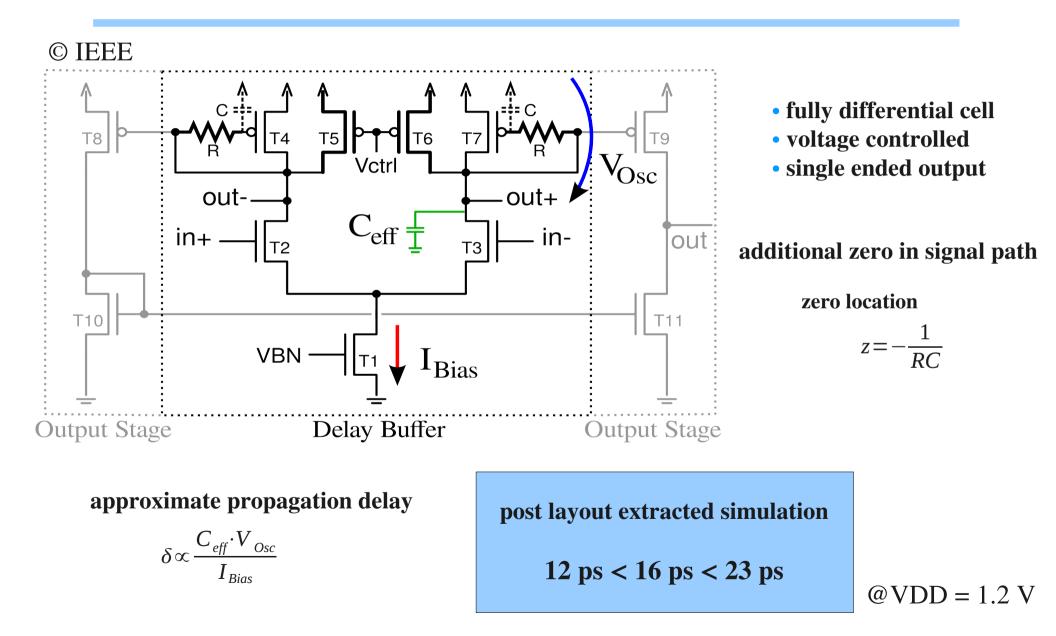

### Delay Element

- Critical building block often longest delay path / used in many architectures

- CMOS inverter double inverter pseudo differential

- Current starved / Voltage Controlled large propagation delay variations slower cell due to control NMOS / PMOS

- Fully Differential

short propagation delay w/ control more robust against power supply noise (depends on design) cross-coupled load / low power

For fine-time TDC designs:

**Fast = Short Propagation Delays = More robust design**

**CERN PH-ESE Electronics Seminars**

L. Perktold - 26-March-2013

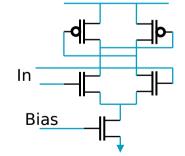

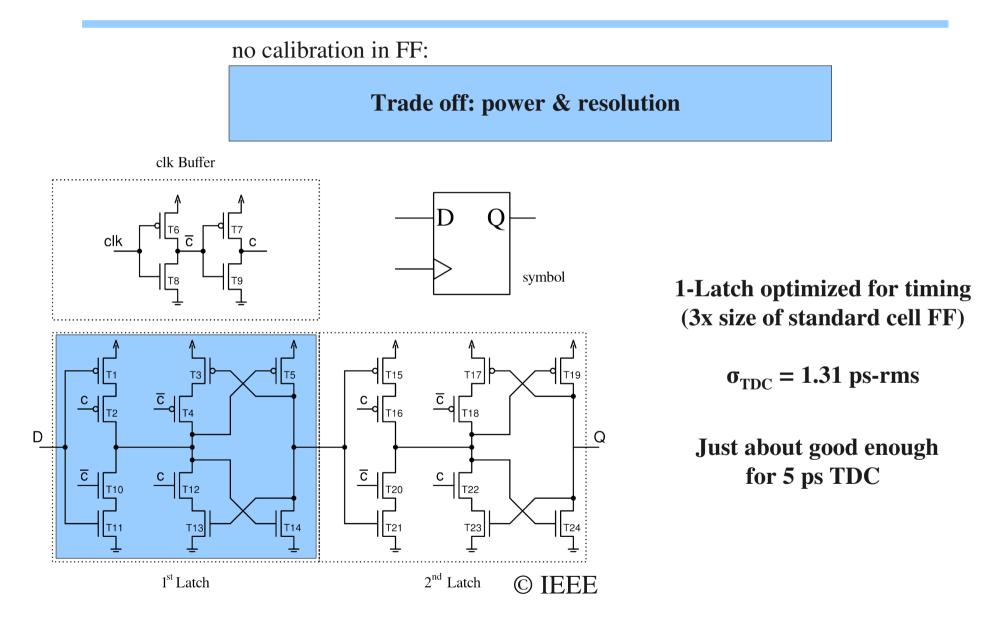

### Time Capture Registers

#### • Critical building block - makes timing decision

S Q • Latch Vdd simple / small area clk clk timing information can be overwritten R S R • Standard D Flip-Flop hit independent readout out single-ended DO  $\overline{\mathbf{D}}$ D Clock • Fully Differential Flip-Flop static current consumption clk S SR fully differential input R latch no conversion if differential signaling Gnd sense-amplifier FF

For fine-time TDC designs:

Fine resolution = good matching / high power OR Fine resolution = FF calibration

### Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

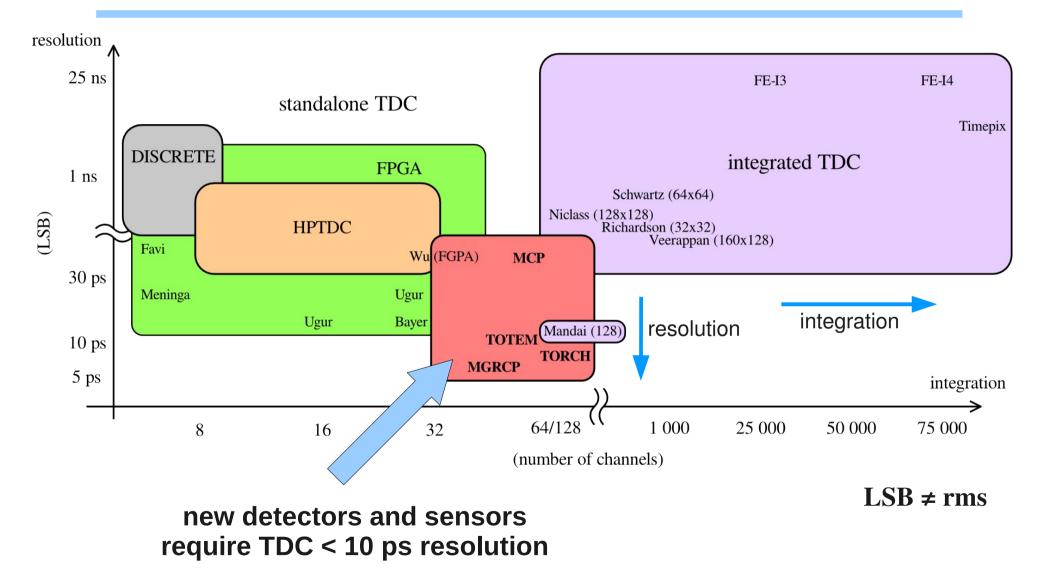

### TDC development trends in HEP

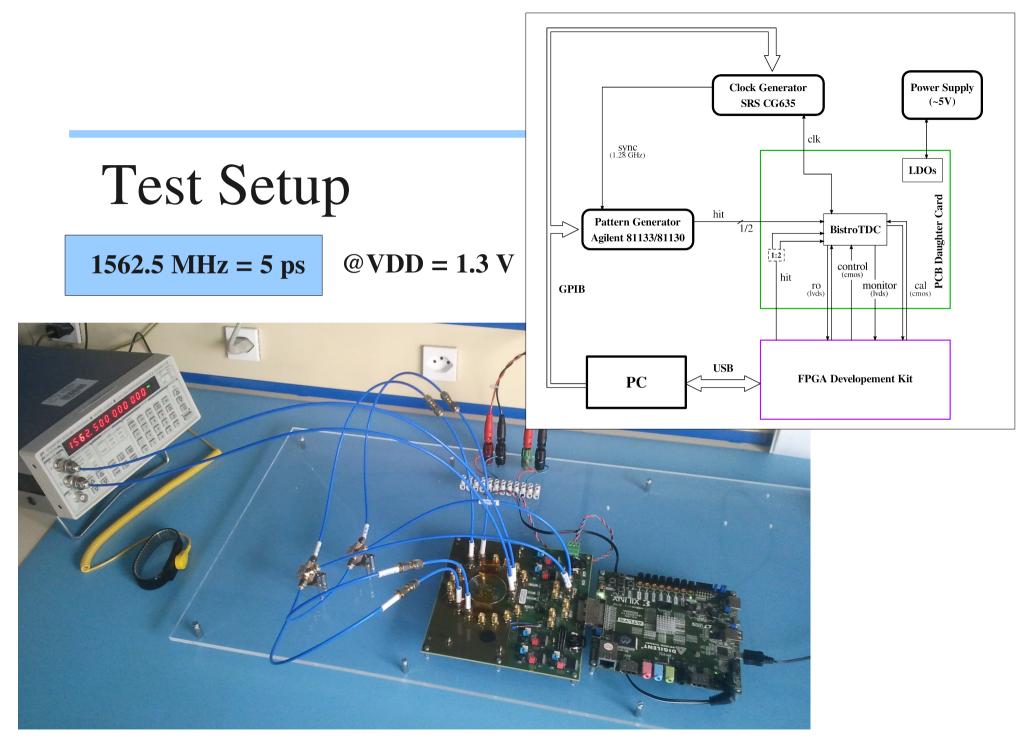

#### Demonstrator ASIC

#### Requirements

- achieve sub 10 ps LSB sizes

-> with rms better than bin-size

- multiple channels (architecture easy extendable)

- large dynamic range

- -> allow to use one common reference

- robust against power supply noise

- flexible in terms of power consumption / time resolution

#### **not a complete TDC -> demonstrates resolution of TDC**

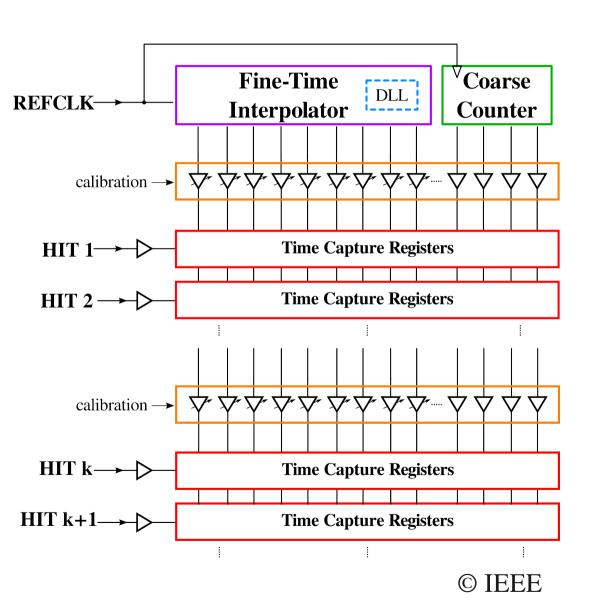

### **TDC** Architecture

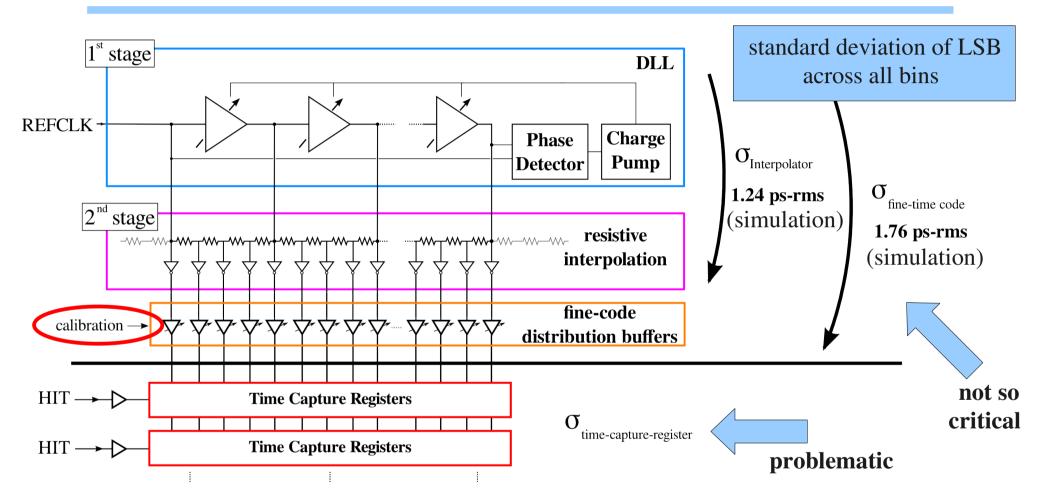

- central interpolator with counter to extend dynamic range

- measurements are referenced to common reference to allow to synchronize multiple TDCs

- DLL for PVT auto calibration and power consumption trade-off

- short propagation delays and fast signal slopes of timing critical signals to reduce jitter

- calibration applied on a group of channels to reduce circuit overhead and calibration time

- relatively constant power consumption make it less sensitive to change in hit rate

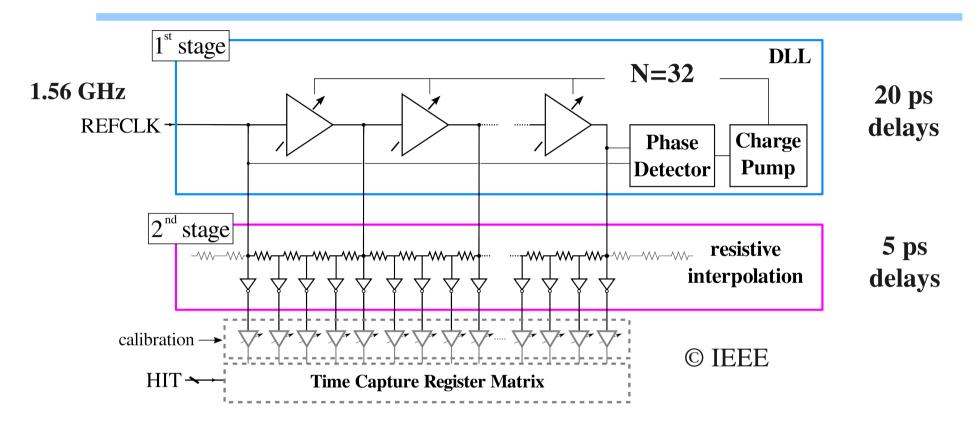

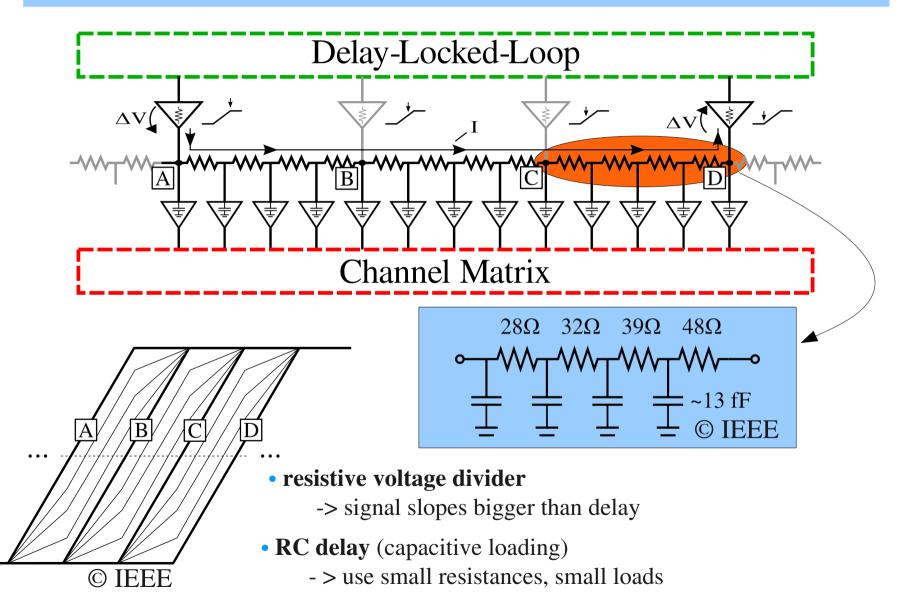

#### **Fine-Time Interpolator**

#### • DLL to control LSB size

-> 32 fast delay elements in first stage - 20 ps-> total delay of DLL 640 ps at 1.56 GHz

#### • Resistive Interpolation to achieve sub - gate delay resolutions -> LSB size of 2nd stage controlled by DLL

CERN PH-ESE Electronics Seminars L. Perktold - 26-March-2013

## Voltage Controlled Delay Cell

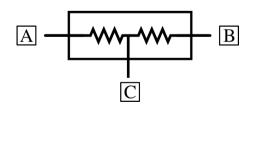

### **Resistive Interpolation**

### Device Mismatch

- Calibration can correct for Fine-Time Interpolator and Distribution Buffer mismatch

- Don't want to calibrate each single register

- -> time capture registers require good matching

### Time Capture Register

### Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

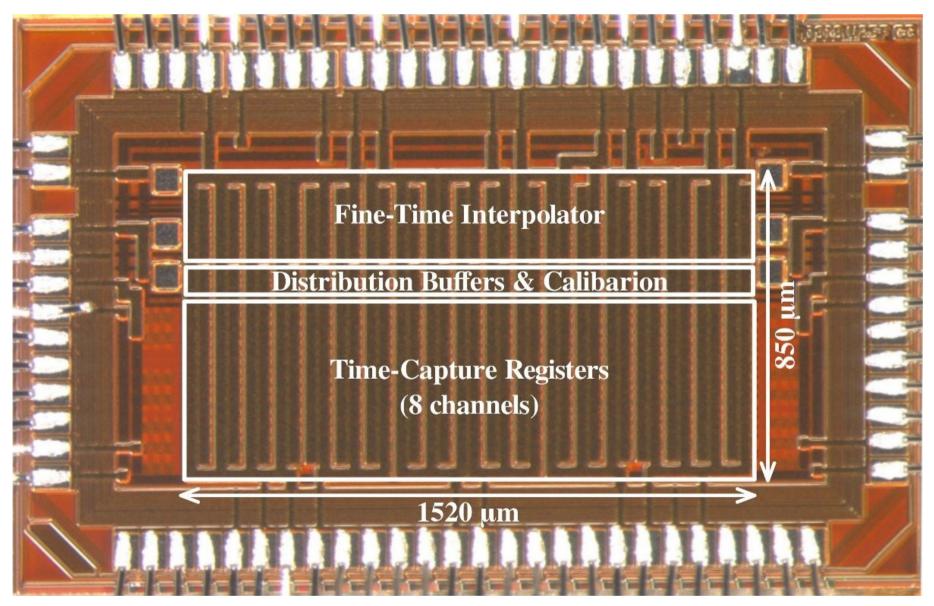

#### Demonstrator Photograph 130 nm technology

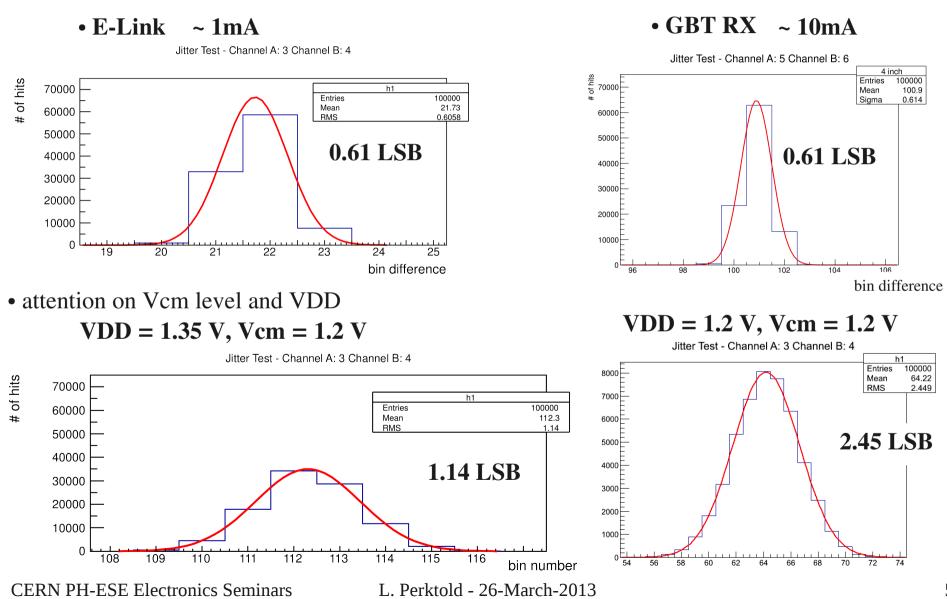

### **Channel Configurations**

• for easing test always two channels of a kind

(not yet characterized)

compare different time capturing schemes

| 1 & 2       GBT RX       direct drive FF (custom)       data driven         3 & 4       E-Link       standard FF (custom)       event driven         5 & 6       GBT RX       standard FF (custom)       event driven         7 & 8       GBT RX       standard FF (cell lib)       event driven         compare input         buffer architectures |         |              |                          |                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|--------------------------|-------------------|

| 3 & 4       E-Link       standard FF (custom)       event driven         5 & 6       GBT RX       standard FF (custom)       event driven         7 & 8       GBT RX       standard FF (cell lib)       event driven         compare input         buffer architectures                                                                             | Channel | Input Buffer | Time Capture Register    | Capturing Concept |

| 5 & 6       GBT RX       standard FF (custom)       event driven         7 & 8       GBT RX       standard FF (cell lib)       event driven         compare input       event driven       event driven         buffer architectures       compare different time-                                                                                  | 1&2     | GBT RX       | direct drive FF (custom) | data driven       |

| 7 & 8       GBT RX       standard FF (cell lib)       event driven         compare input<br>buffer architectures       compare different time-                                                                                                                                                                                                      | 3 & 4   | E-Link       | standard FF (custom)     | event driven      |

| compare input<br>buffer architectures<br>compare different time-                                                                                                                                                                                                                                                                                    | 5&6     | GBT RX       | standard FF (custom)     | event driven      |

| buffer architectures compare different time-                                                                                                                                                                                                                                                                                                        | 7&8     | GBT RX       | standard FF (cell lib)   | event driven      |

| capture-register sizes                                                                                                                                                                                                                                                                                                                              |         | s            | -                        |                   |

CERN PH-ESE Electronics Seminars

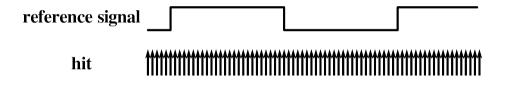

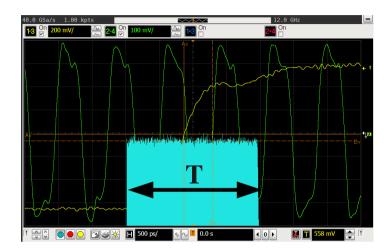

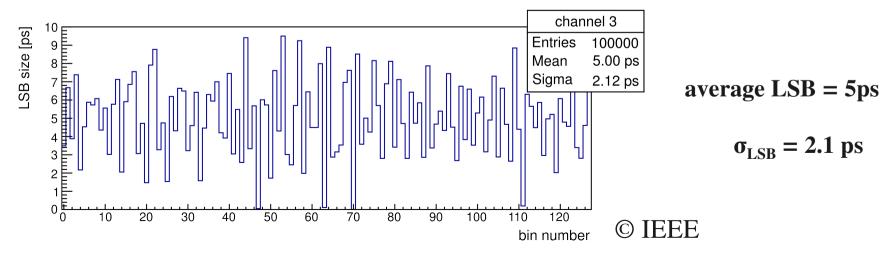

# Code Density Test

- Uniformly distributed events across clock cycle - asynchronous clock domains

- Number of collected hits => bin size

#### Before Global Calibration

### Interpolator Linearity

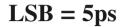

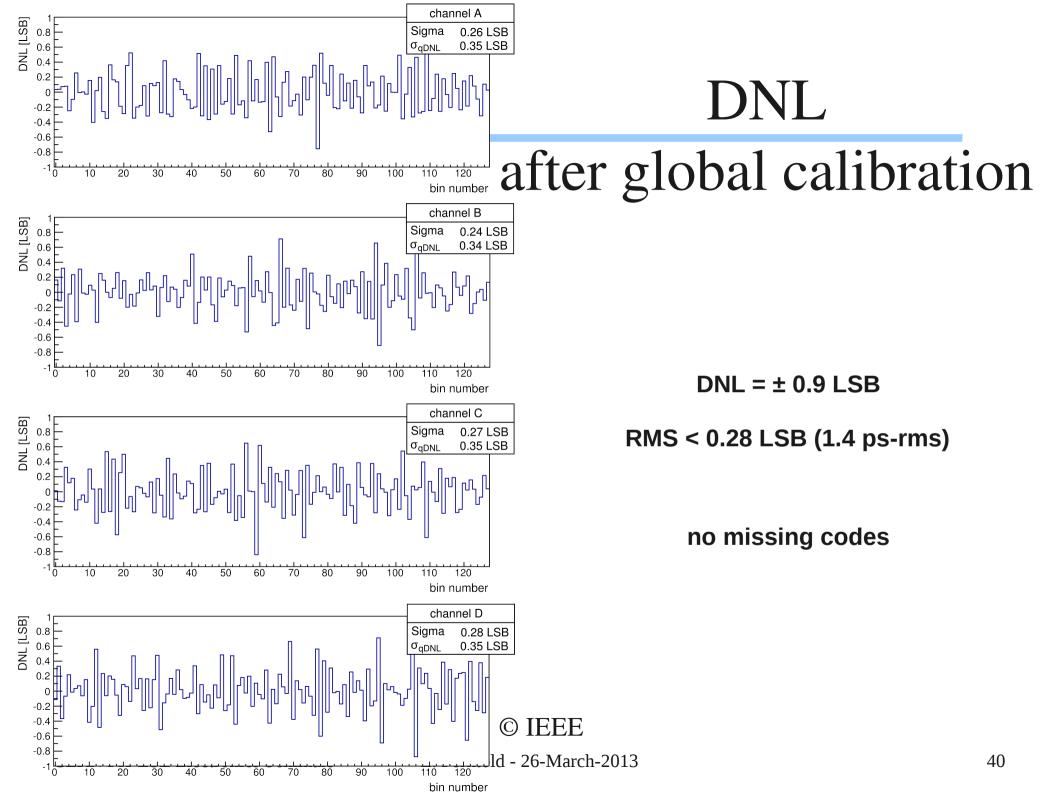

#### • After Global Calibration

channel 3 -SB size [ps] before calibration: Entries 100000 Mean 5.00 ps  $\sigma_{LSB} = 2.1 \text{ ps}$ Sigma 1.31 ps after calibration: 3  $\sigma_{LSB} = 1.3 \text{ ps}$ 2 0 20 30 50 70 90 100 120 10 80 40 60 110 no missing codes bin number © IEEE Integral-**Differential-Non-Linearity Non-Linearity**

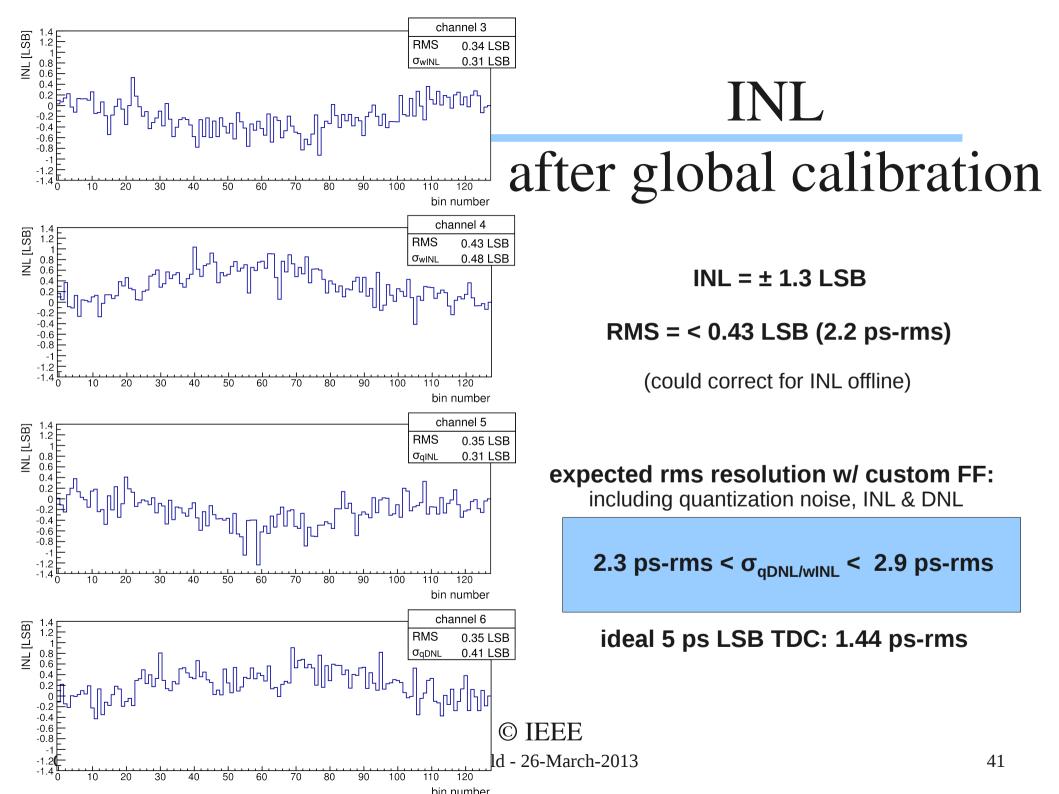

# Standard Cell FF - Weak Matching

expected time resolution: < 5.9 ps-rms (w/ standard cell FF)

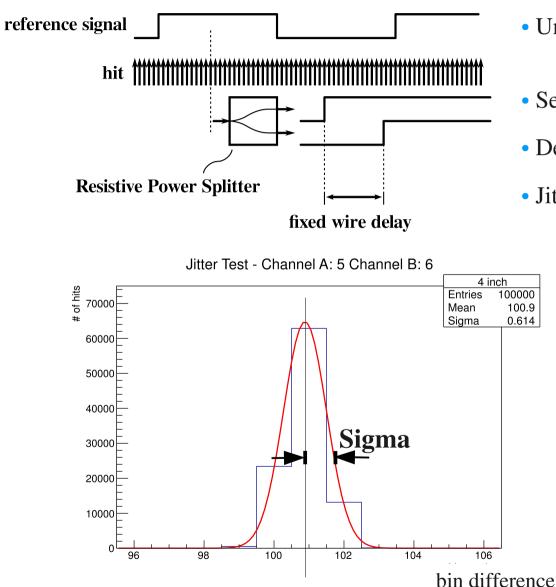

# Double Shot Measurement Principle

- Uniformly distributed events across 1 clock cycle - asynchronous clock domains

- Send same hit to two distinct channels

- Delay fixed by wire length differences

- Jitter contribution of hit not canceled out

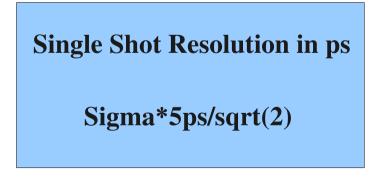

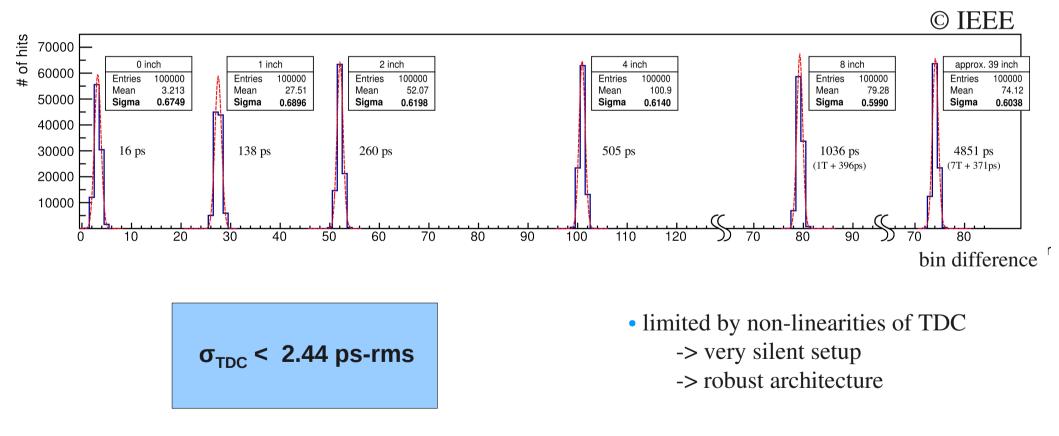

# Measured Single Shot Precision

- Three measurement series

- both hits arriving within one reference clock cycle

- second hit arrives one clock cycle later

- second hit arrives multiple clock cycles later (~5ns)

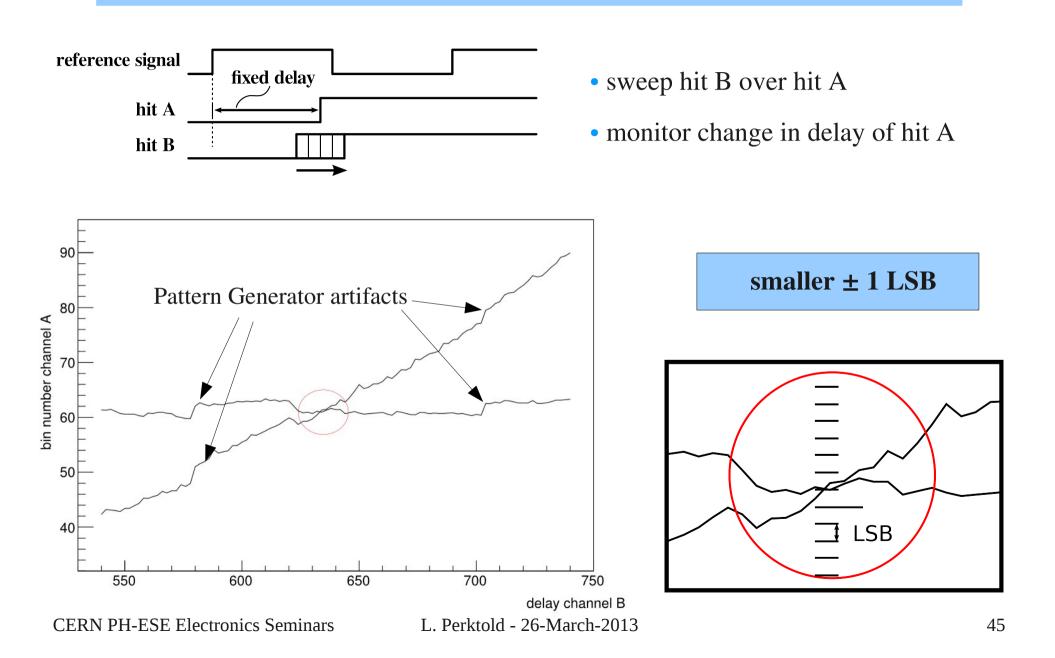

### Inter Channel Crosstalk

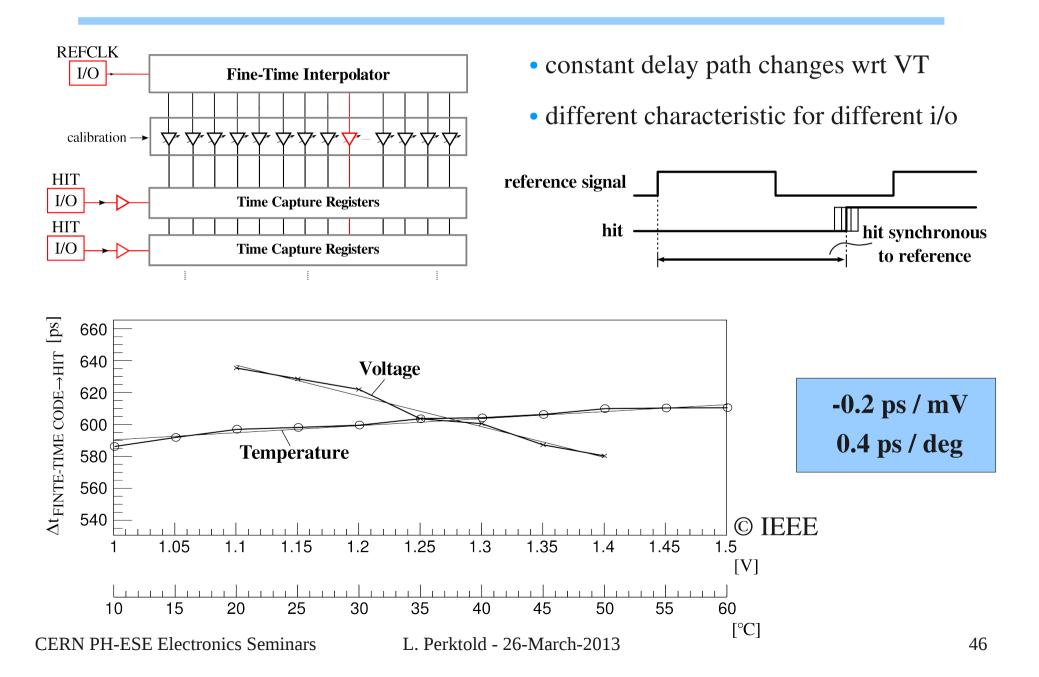

# **PVT** variations

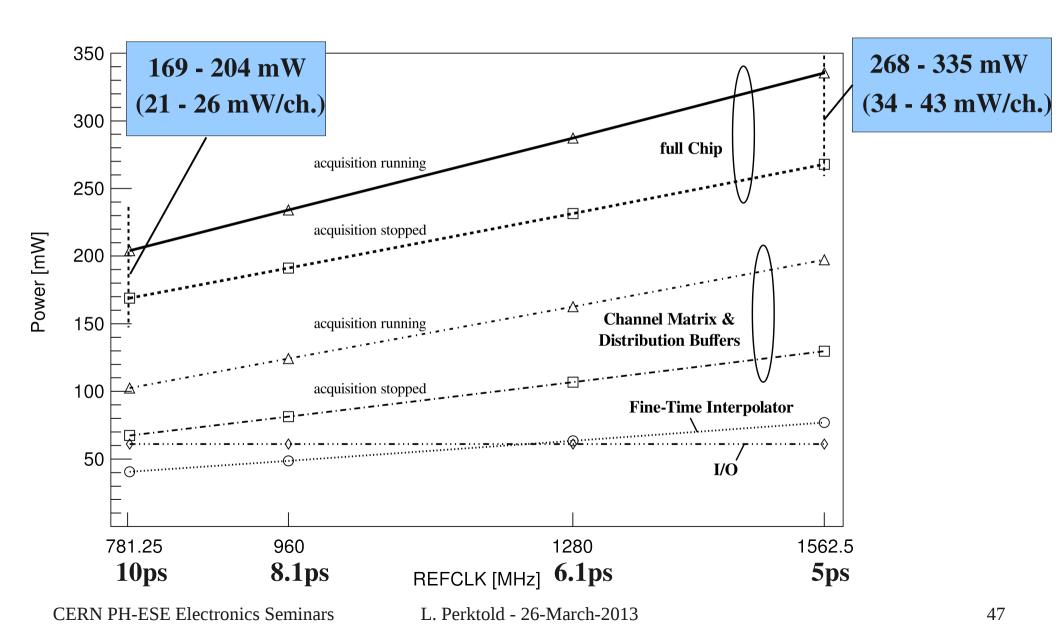

#### Power consumption

**8** channels

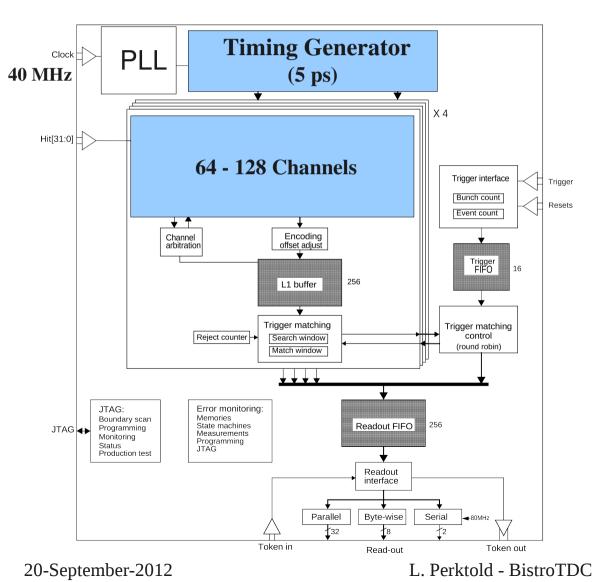

# Full TDC ASIC

#### **TDC Architecture:**

#### **Demonstrator ASIC**

- < 3 ps-rms resolution

- < 50 mW/channel

- missing counter, PLL and digital logic

#### **Full TDC**

- based on HPTDC

- 64 128 channels per ASIC

- 40 MHz input clock

- < 5 ps-rms timing precision

- radiation tolerant

- flexible readout architecture

48

# Outline

- Time measurements in HEP

- Time-to-Digital Converter Concepts

- Challenges in Fine-Time Resolution TDC Design

- Demonstrator Architecture

- Measurement Results

- Conclusion

## Conclusion

- A demonstrator ASIC has been designed, constructed and successfully tested.

- Time resolutions as low as 3 ps-rms have been demonstrated

- Device mismatches considerably affect design in the ps-domain

-> trade off power & resolution & calibration effort

- Macro suitable for a full fine-time resolution general purpose TDC

# The end

# Thank you for your attention!

| Demonstrator Performance Summary |                     |

|----------------------------------|---------------------|

| Technology                       | 130 nm              |

| Supply Voltage                   | 1.3 V               |

| Area                             | 1.2 mm <sup>2</sup> |

| Power Consumption                | 34 - 42 mW/channel  |

|                                  |                     |

| # of Channels                    | 8                   |

| LSB size                         | 5 ps                |

| DNL                              | ± 0.9 ps            |

| INL                              | ± 1.3 ps            |

| Single Shot Precision            | < 3 ps-rms          |

| Dynamic Range                    | 640 ps (on chip)    |

# IEEE copyright notice

Copyright 2012/2013 IEEE. Parts of the work presented here have been or are to be published in the proceedings of the 2012 IEEE Ph.D. Research in Microelectronics & Electronics conference, June 12-15, 2012, Aachen, Germany and in the proceedings of the 2013 IEEE International Instrumentation and Measurement Conference, May 6-9, 2013, Minneapolis, USA respectively. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works, must be obtained from the IEEE.

#### BACKUP

CERN PH-ESE Electronics Seminars

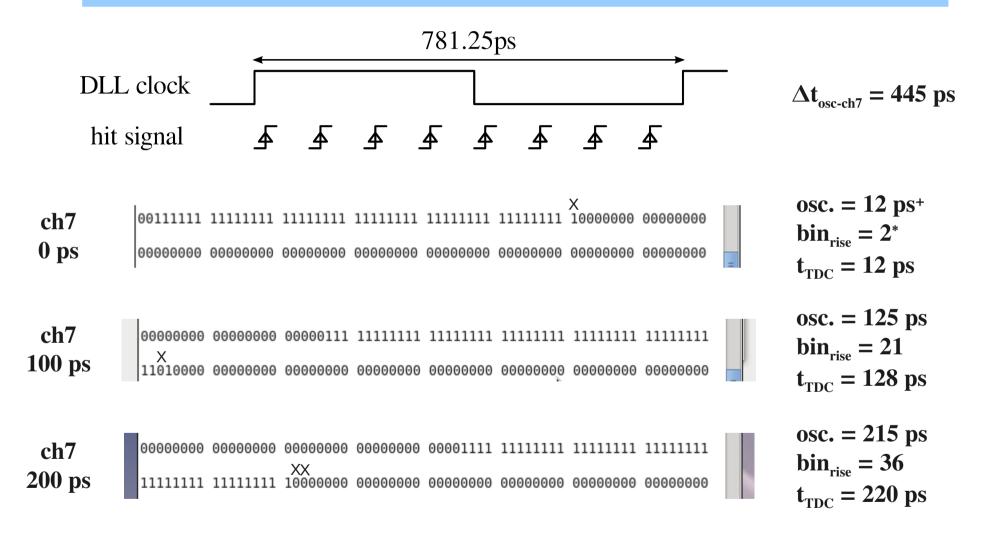

### Functional Test (uncal/ DLL)

5-10 measurements

+ reference calibration point

\* 00-11 transitions represents falling edge. DLL sends inverted signal to profit from stronger NMOS devices.

Duty-Cycle = 37 %

L. Perktold - 26-March-2013

#### I/O Buffer Influence

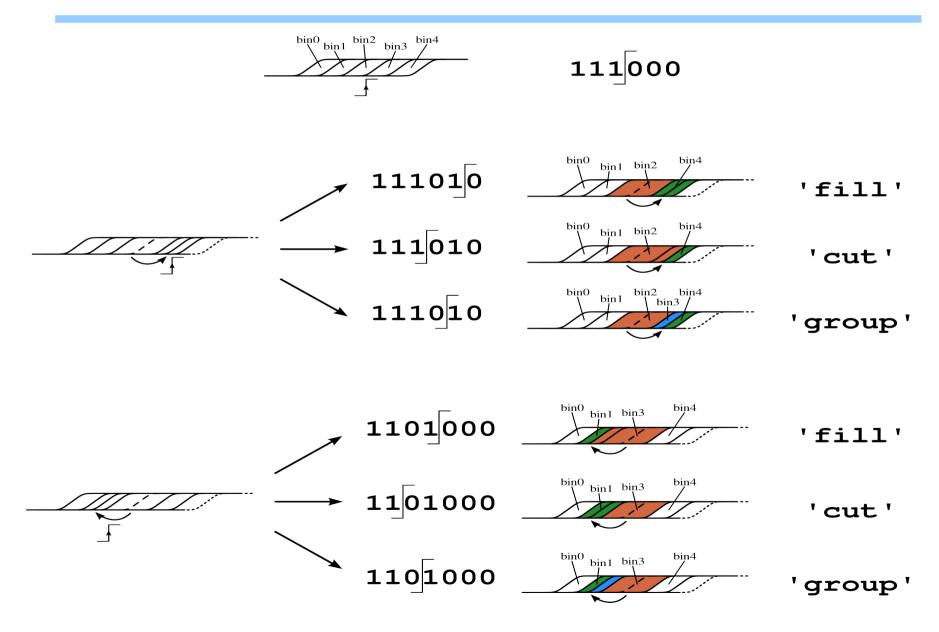

# Bin Assignment

L. Perktold - 26-March-2013

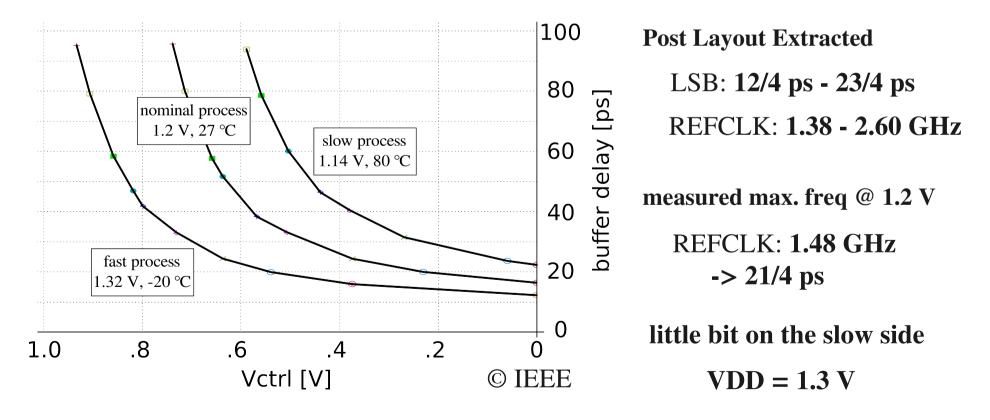

# Reference Clock Frequency

5 ps = 1562.5 MHz

• How fast the delay line can go depends on process variations and operating conditions

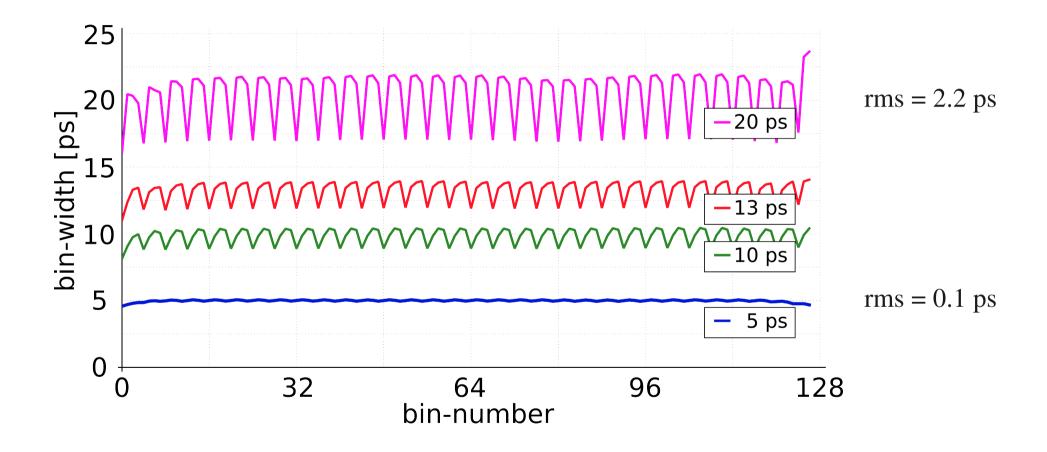

#### Simulated Bin-Widths

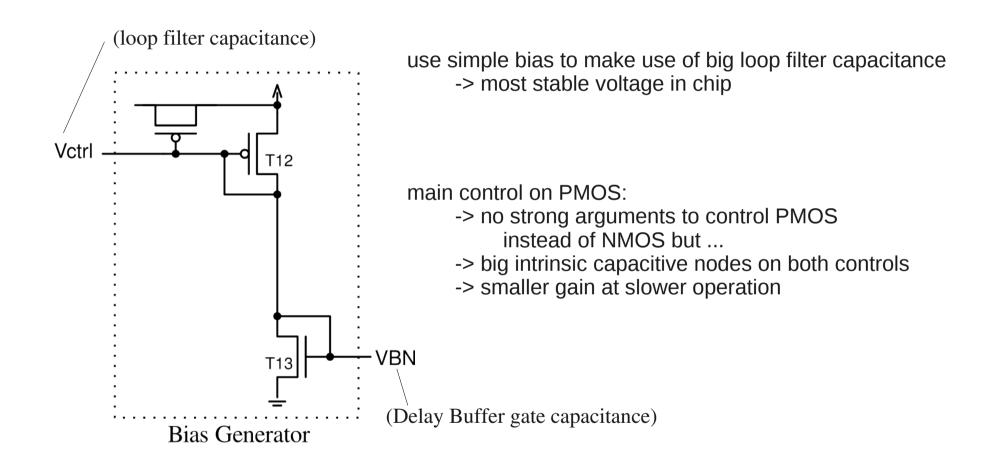

# Delay Buffer Biasing

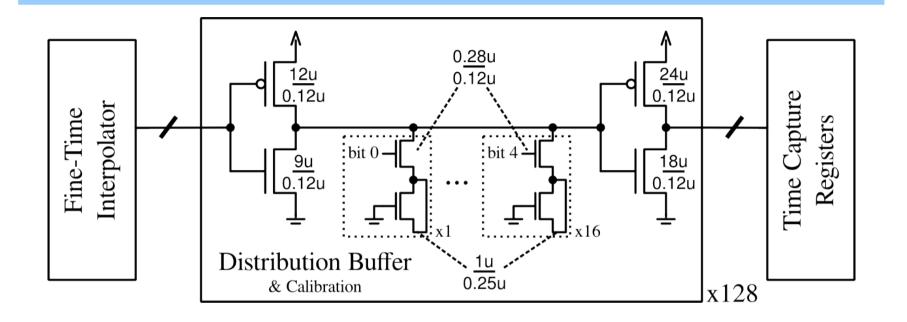

# Distribution Buffer w/ Calibration

- binary weighted calibration (5 bits)

- delay can be varied from -16 ps to +15 ps in 1 ps steps (2fF per step)

- can correct INL errors up to 6.4 LSB