# Update on the integration of SRS into the ATLAS DAQ environment

A. Zibell Ludwig-Maximilians-Universität München

RD51 mini week 23.4.2013

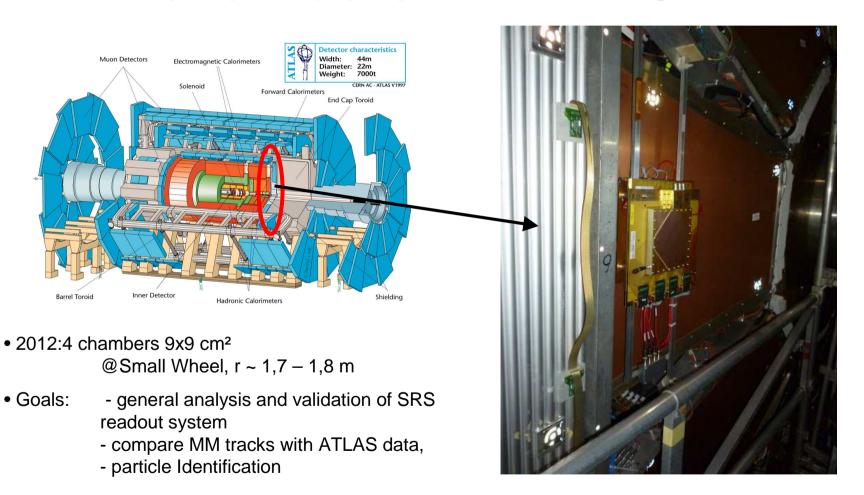

### Installation of prototype chambers in ATLAS

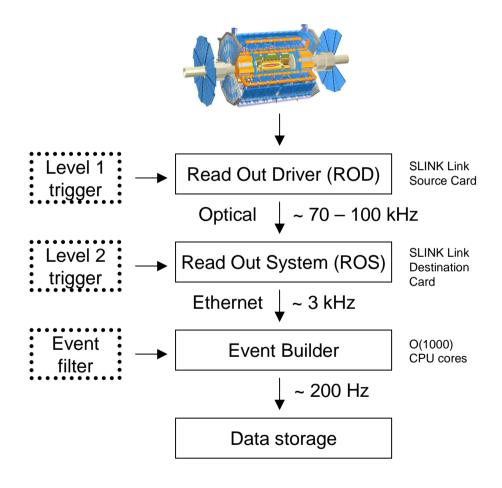

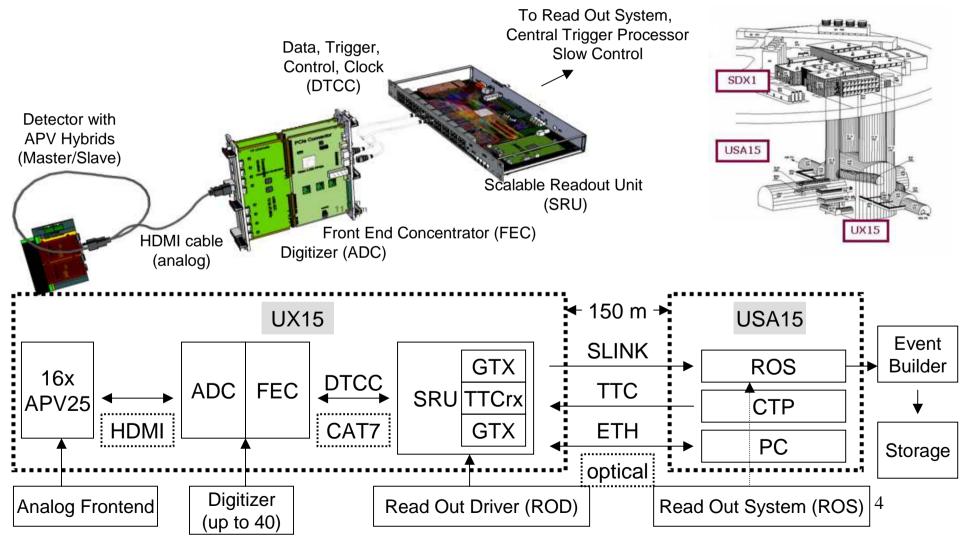

#### ATLAS data acquisition chain

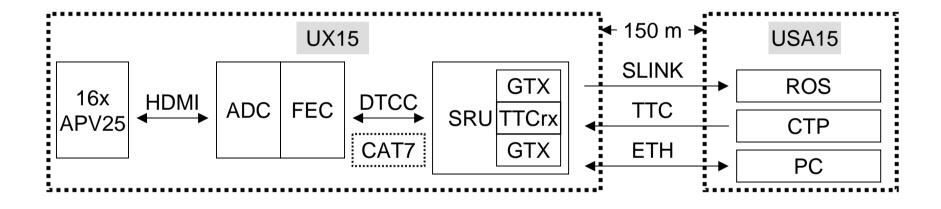

## SRS (Scalable Readout System, RD51 Development)

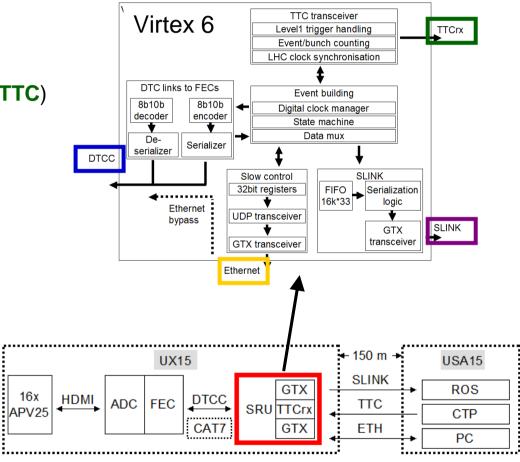

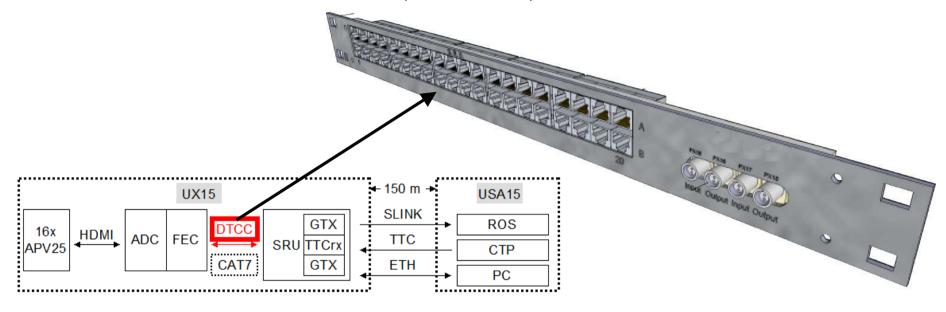

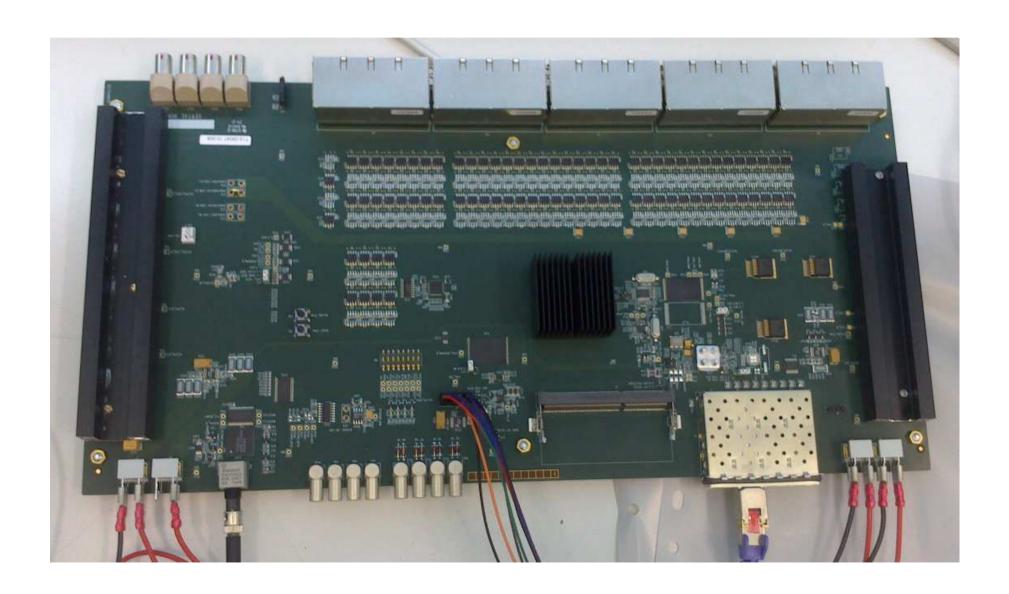

#### SRU (Scalable Readout Unit)

#### Main tasks:

- Reception and distribution of Level1 triggers, LHC synchronization (TTC)

- Event Counter

- Bunch Counter

- Clock Phase

- Bunch Counter reset

- Event Counter reset

- Detector data collection and event building (DTCC)

(BCID, EVID, ..., Data)

- Data transmission to ROS PC via SLINK

- Slow control / DCS / Data preview via Ethernet:

Register setting on APV, FEC, SRU, ..

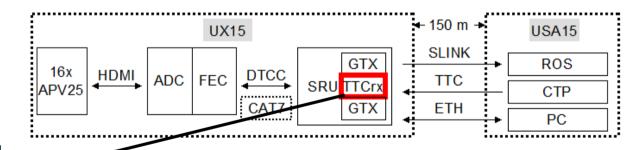

## TTC interface (Trigger, Timing, Control)

- Communication with standard ATLAS trigger electronics ("TTC-Crate", ...)

- Receives L1A (Level 1 Accept) trigger, Bunch clock, triggertype, resets of eventcounter and bunchcounter as well as directed or broadcast configuration data

#### **DTCC Link**

(A. Martinez)

- Connects FEC Card(s) and SRU to transmit:

- <= LHC Clock, L1 Triggers and configuration commands from SRU to FEC

- => Detector- and configuration data at 640 Mbit/s from FEC to SRU

- Hot plug ability and automatic resynchronisation

- Support for 40 FEC cards (~82k channels with APV25 Hybrids)

- Conventional CAT cable with RJ45 plugs

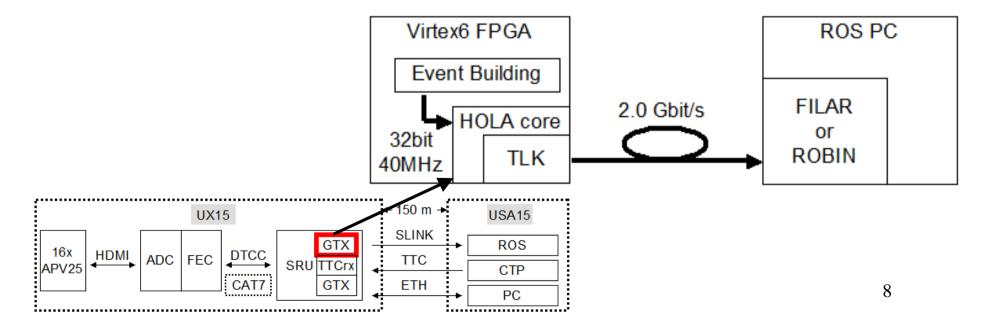

#### SLINK implementation

(M. Della Volpe, R. Giordano, V. Izzo, S. Perrella)

- ATLAS transmits event data from ROD to ROS using SLINK

- Now: No longer need of a seperate HOLA daughter card (as used widely in ATLAS), due to implementation of the SLINK serialisation logic IP core in the Virtex6 FPGA (uses one of the FPGA's GTX transceivers)

- Successfully tested data transfer to a standard ROS PC.

Valid ATLAS data frames are received.

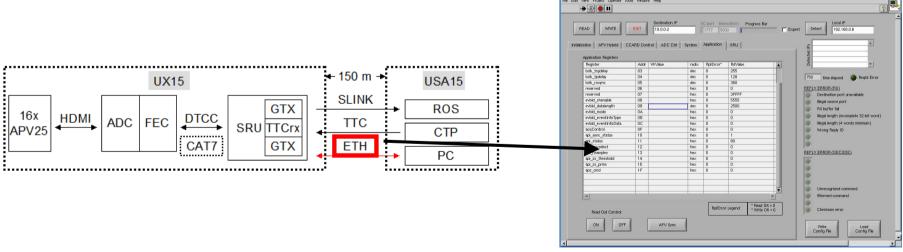

#### DCS / Slow control

- Slow control via optical Gbit ethernet connection to the SRU

- SRU DCS requests are handled directly, packets for FEC and APV are forewarded via DTC links (ethernet switch functionality within SRU)

- Online access to parameters like run control, error conditions, ...

- Fine tuning of TTCrx, APVs, etc...

- Online results of calibration, data preview, ...

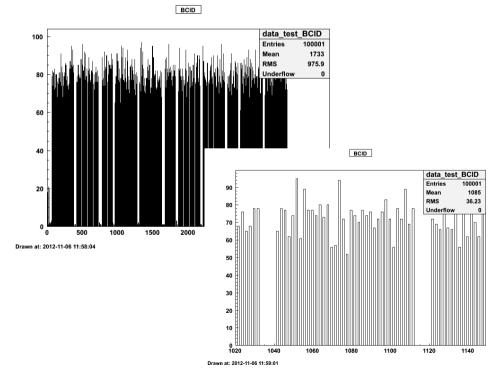

#### First data in ATLAS

- First run taken with ATLAS triggers (L1A 70 kHz)

- LHC bunch structure visible in data -> TTC and DAQ integration works

- Micromegas not included in general ATLAS DAQ ("standalone mode")

- => no Level 2 trigger information

- => no Synchronization with ATLAS muon tracks

#### Status and outlook

- Event building firmware on SRU is running and generates valid ATLAS ROD fragments from APV data

- Successful run-taking in standalone DAQ mode within ATLAS infrastructure

- LHC run period ended on 14.2.2013

- => Setup complete aquisition chain at LMU/Garching cosmic ray facility

- => Readout of large (O(m²)) Micromegas in ATLAS, once LHC restarts after 2014

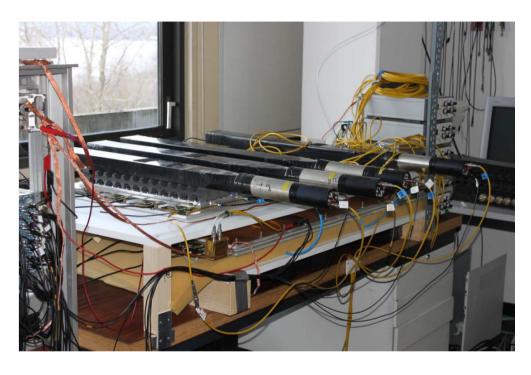

### L1 Micromegas chamber

- MAMMA L1 chamber arrived in Munich

- Active area: 0.92 x 1.02 m<sup>2</sup>, 2048 channels

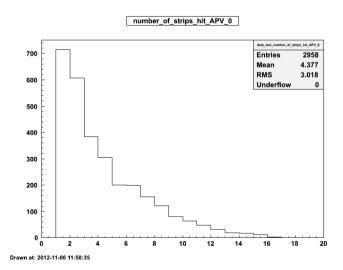

- Several successfull lab-runs with cosmics, reading FEC card via Ethernet

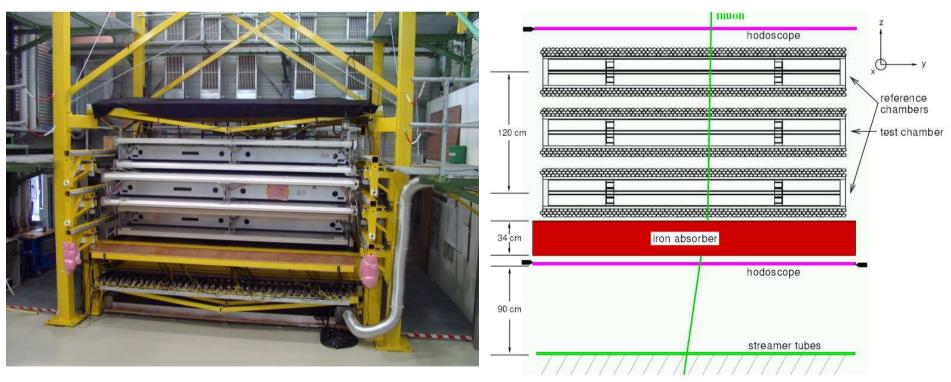

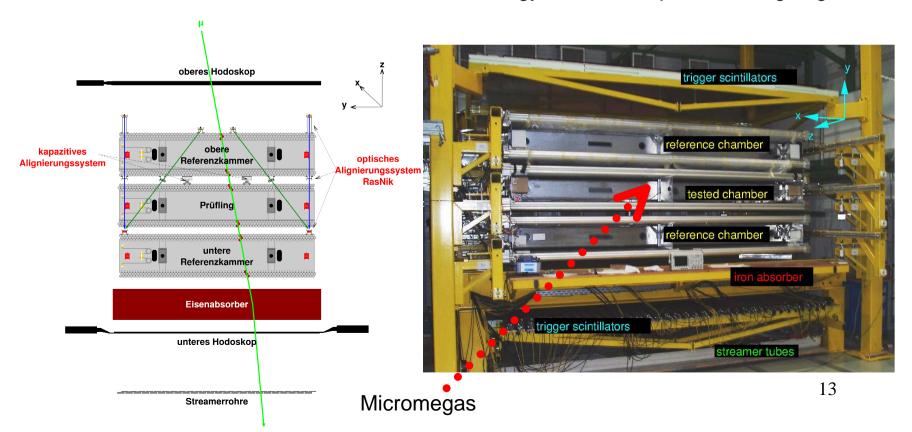

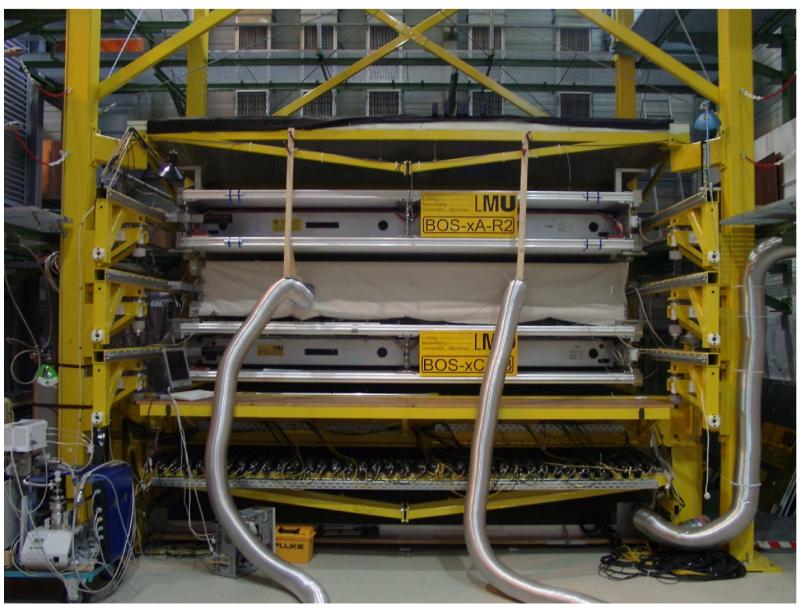

#### Garching cosmic ray facility

- Two full sized ATLAS BOS MDT muon chambers

- 10cm broad Trigger scintillators cover the full area of 4 x 2.2 m<sup>2</sup>, segmentation along tubes as second coordinate

- Irion absorber and streamer tubes to allow energy cut via multiple scattering angle

#### Cosmic ray facility DAQ

- Measurement

- Tracking of cosmic muons with Micromegas (SRU) and calibrated reference MDTs (Filar)

- Trigger time and trigger pattern recorded using VME

- Goals

- comparison of Micromegas tracks with MDT tracks

- Analysis of residuals and determine position of strips as function of x

- Analysis of Micromegas angular resolution (microTPC mode)

- Check of the homogenity of the Micromegas chamber's efficiency and mechanical precision

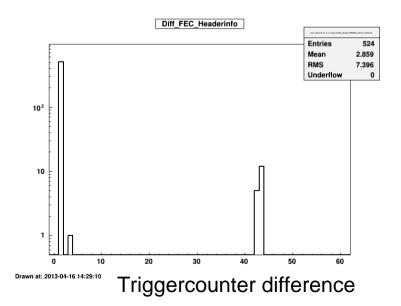

- Three data streams have to be aligned:

- VME crate data for trigger, trigger timing and trigger hit pattern

- FILAR card data from the MDT tubes

- ROBIN card data from the Micromegas/SRS

- All neccessary drivers and software, including ATLAS tdaq, installed on a 4-core machine, running scientific linux 5

- Estimated time for measurements: 2 4 weeks

#### Current issues

- Non-zero suppression firmware with DTC support works flawless

- Zero-suppression firmware without DTC support (direct ethernet connetion) works

- Zero suppression firmware with support for DTC links shows "bunches" of missing events in the raw data stream.

- Analysis of raw binary data shows a repeating sequence of ~25 good events, ~40 missing, ~25 good events, ~40 missing, etc...

- Under investigation together with FEC firmware developers

#### Standard ATLAS Event Data

- L1A trigger (from **TTCrx** (ATLAS), NIM input (Lab) or slow control (debug)) stored in FIFO memory

- ATLAS Event fragment generated for each trigger

- Header and Trailer information to identify Detector, Run and Event metadata

- Converted data from the APV chips will be zerosuppressed by the FEC and then written (via DTC link) to FIFO memorys in the SRU FPGA

- Full event fragment is formed and sent out via SLINK to the ROS PC

|       | 32 bit                       |

|-------|------------------------------|

| 1     | Begin of Fragment            |

| 2     | Start of Header              |

| 3     | Header Size                  |

| 4     | Format Version               |

| 5     | Source Identifier            |

| 6     | Run Number                   |

| 7     | Ext. L1 ID                   |

| 8     | BCID                         |

| 9     | L1 Trigger Type              |

| 10    | Detector Event Type          |

|       | (ROD fragement payload)      |

|       |                              |

| N – 4 | Status Element n             |

| N – 3 | Number of Status<br>Elements |

| N – 2 | Number of Data Elements      |

| N – 1 | Status Block Position        |

| N     | End of Fragment              |

22 hit

#### Upcoming plans

- Mechanical:

- Mechanical structure to integrate the L1 chamber into the Garching/Munich cosmic ray test stand is ready

- Installation in week 17 18

#### DAQ:

- FEC card standalone (Ethernet without SRU) (mmdaq1, mmdaq3)

- Synchronized setup with MDTs and full data from SRS (~20 Tbytes/month)

- Synchronized setup with MDTs and zero-suppressed data (O(Gbytes)/month)

#### Analysis:

- Integration of the ATLAS event format into Micromegas Analysis framework completed

- Comparison of Micromegas tracks with MDT track predictions for several Micromegas operational parameters (mmdaq1, mmdaq3, ATLAS DAQ) and measurement of efficiency, residuals, angular resolution, ...

### Garching cosmic ray facility

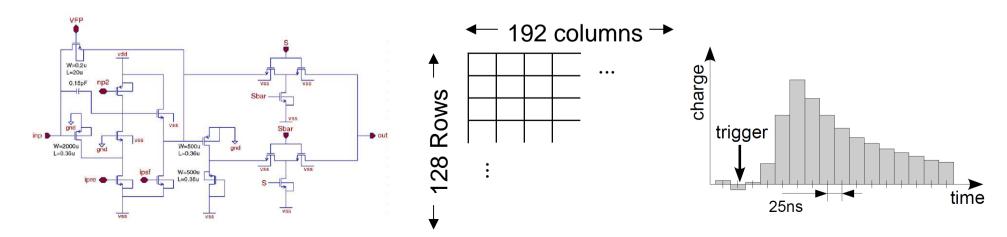

### APV25 Charge Sensitive Analog Frontend

- Analogue pipeline ASIC used for read-out of silicon strip detectors in the CMS tracker

- 128 charge sensitive amplifier channels

- Pipeline buffer of 192 cells depth for each input channel, filled consecutively with every clock cycle (40.08 MHz @LHC)

- Blocks of one or more pipeline columns can be read out for each trigger

- => Time evolution of integrated charge signal for each detector channel in steps of ~25 ns

128 preamplifier channels → Analogue pipeline buffer → Selected columns output

#### L1A rate vs. APV readout time

- APV readout: 140 clock cycles @40.08 MHz LHC clock frequency

( 128 channels + 12 overhead)

- MicroMegas detectors require 10 20 time bins to sample signal shape

(1400 2800 clock cycles)

- => Mean time difference between Level 1 triggers:

- ~600 clock cycles @70 kHz trigger rate

- Implementation of busy-logic to decide, which event to process fully (trigger to APV chips), and which not

- Skipped events also generate ATLAS event frame with no data content in FIFO buffer to satisfy ROS requirements

- Tested and working with up to 100 kHz random trigger rate

## Garching/LMU Cosmic Ray Facility