# **SRS + Timepix**

#### A readout system for the Timepix chip

#### Michael Lupberger University of Bonn

RD51 Mini week, April 23rd 2013, CERN

- Timepix chip

- First system on Xilinx Evaluation Board

- SRS based readout system

- First steps

- Common code used

- Status

- Test beam

# **Timepix chip**

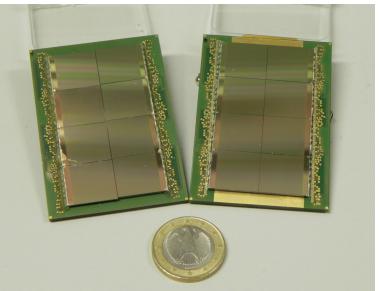

• Digital readout chip: The Timepix ASIC

- Properties

- 1.4 x 1.4 cm<sup>2</sup> active surface

- 256 x 256 pixel matrix

- CMOS 250 nm technology, IBM

- 55 x 55 µm<sup>2</sup> per pixel

- amplifier/shaper ( $t_{rise} \sim 150 \text{ ns}$ )

- 14 bits count clock cycles  $\rightarrow$  Pixel pit when/how long

- clock up to 100 MHz in every pixel

- lower threshold

- threshold level ~ 500  $e^{-}$  (90  $e^{-}$  ENC)

Used as readout anode plane in gaseous detectors

#### New readout system

Goals:

- ultimately read out ~100 chips

- $\rightarrow$  large area detector (full TPC endplate module)

- modular system, Virtex FPGA  $\rightarrow$  use SRS

- ethernet based

- open source firmware and software code

- highest data rate possible (Timepix is slow)

- triggerable, integrate slow control & calibration

- demonstrator for a pixelated TPCs

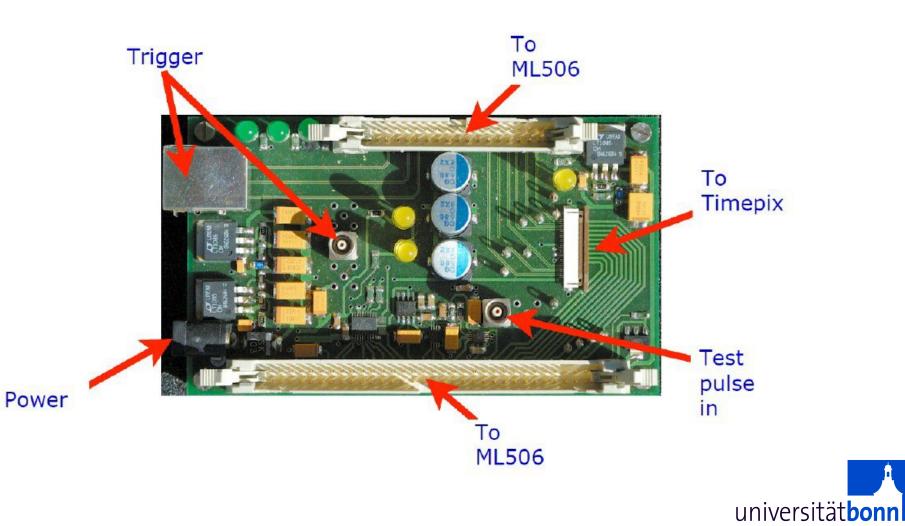

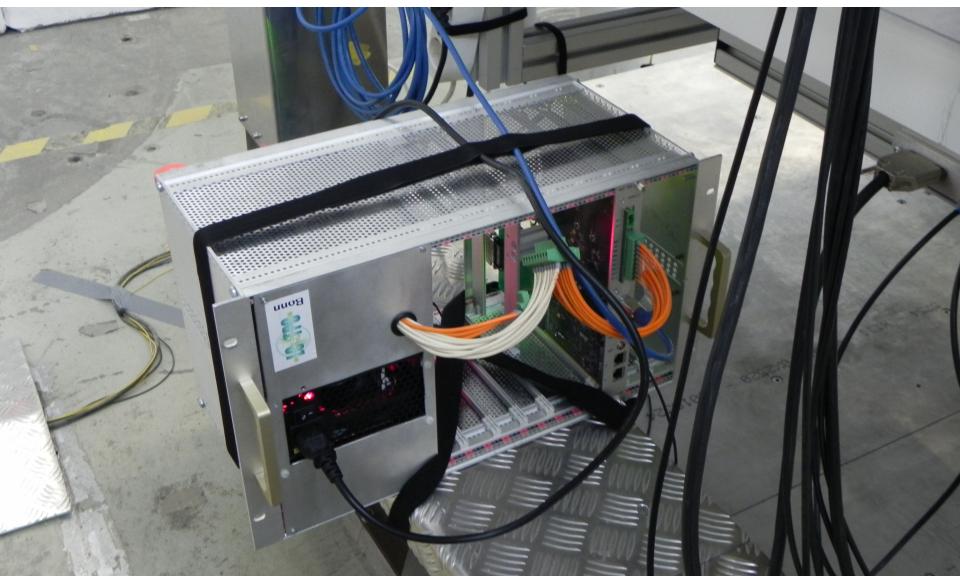

#### Mainz readout system

### Adapter board for Xilinx kit

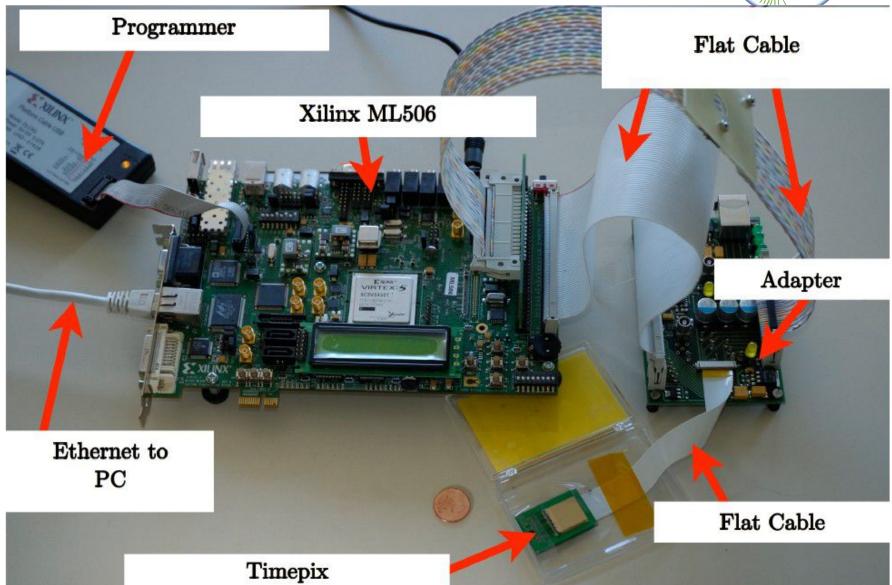

# Activities on Xilinx Boards

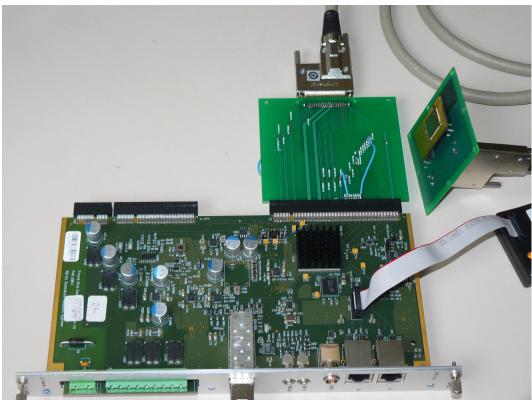

- Setup of second Mainz system in Bonn

- Xilinx ML506 board with Virtex5 FPGA + adapter board

- single Timepix readout

- Re-target to Virtex6

- Xilinx ML605 board with Virtex6 FPGA, new adapter board

- Extension of firmware: zero suppressed, multi threaded readout (maximum readout speed), can handle octoboards

Development still ongoing (updates from modified SRS firmware)

Lately: new adapter board with I2C: ADC for analog DAC\_out DACs + multiplexer for calibration, LVDS drivers, CMOS level shifter

$\rightarrow$  small readout system for Uni Siegen and a new detector at CAST

#### **SRS based readout**

Activities started in November 2011

- Transformation of firmware from Xilinx evaluation board to SRS

- Difficulties:

- SFP ethernet

- use SRS gigabit ethernet modules (gbt\_top + submodules)

- design new adapter board

#### SRS: common code used

- gbt\_top: handling of ethernet frames in SRS,

- dataout bit wise

- Evaluation board used sgmii ethernet

- dataout byte wise

- $\rightarrow$  Merge timepix control modules with SRS gbt

- Future: Want to use DDR2 RAM in SRS

- use memory interface generator (mig)

- need a data handler: Timepix control ↔ DDR2 DAM

Any experience ??? Hints and code is welcome!

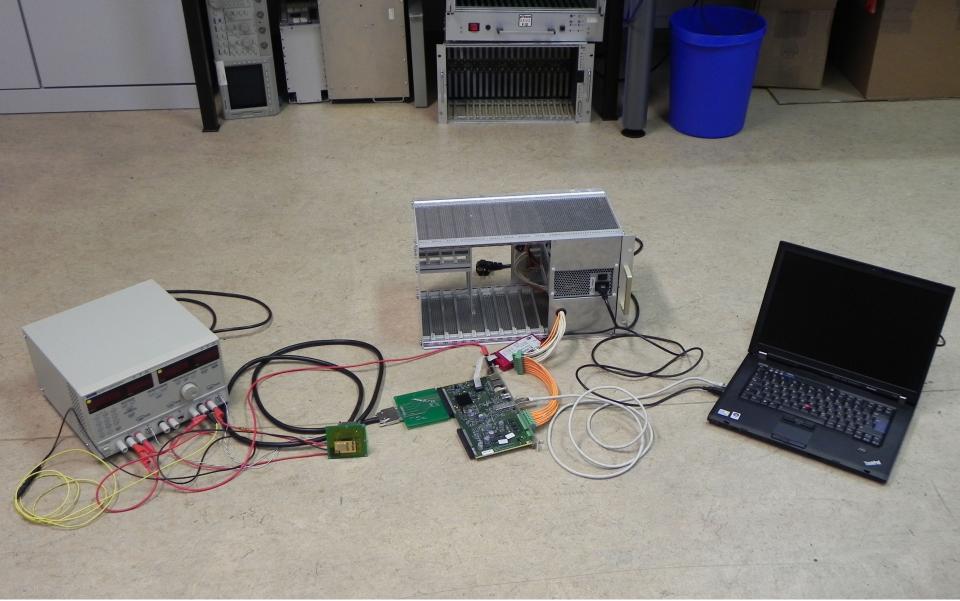

System fully operational for 1-8 chips

- Data readout rate at theoretical maximum (up to 3 chips)

- Software extended to do

- threshold equalisation

- calibration with external test pulses

- fast data taking: triggered, untriggered

- Missing:

- DAC for test pulses generated by multiplexer,

ADC for Timepix analog DAC\_out scan (hardware not implemented)

- DDR2 RAM on SRS (FPGA code not written)

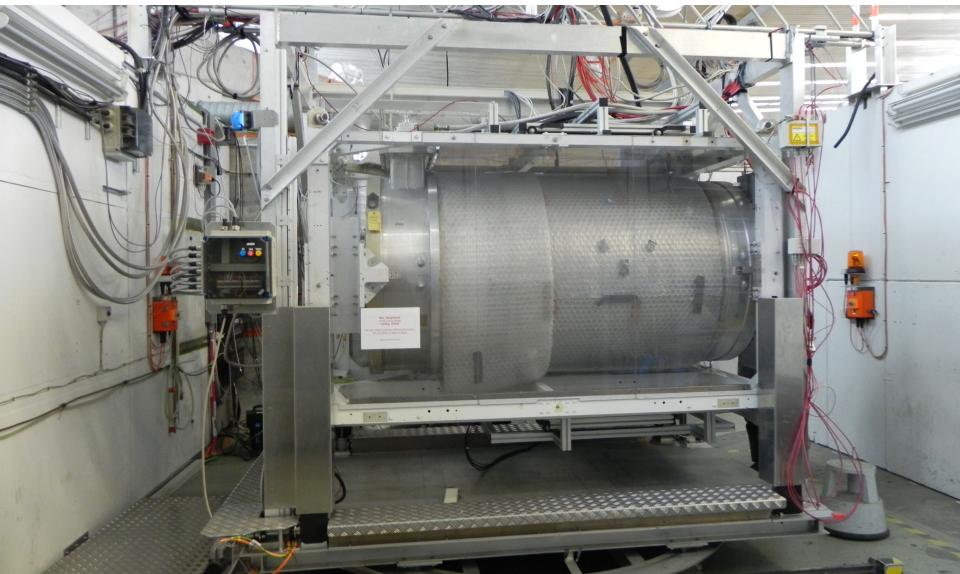

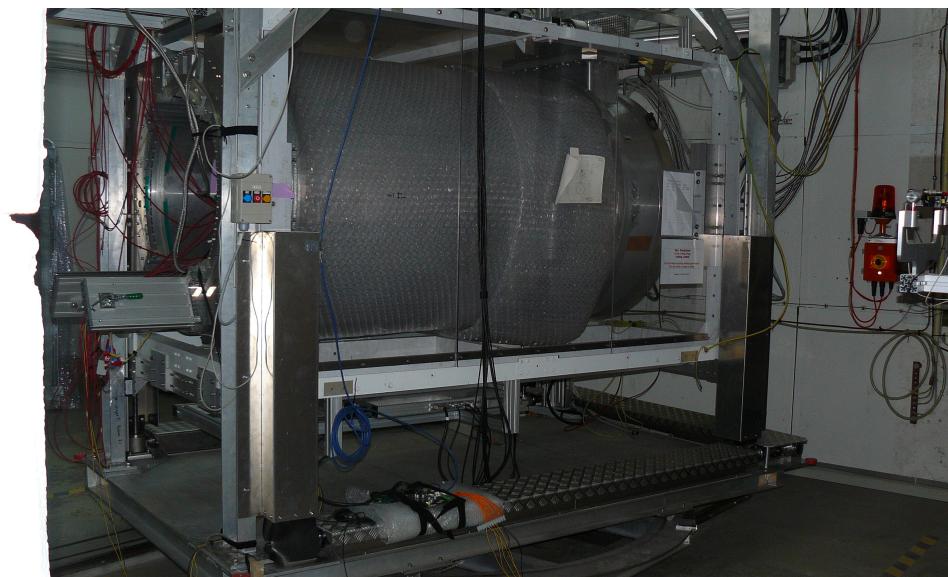

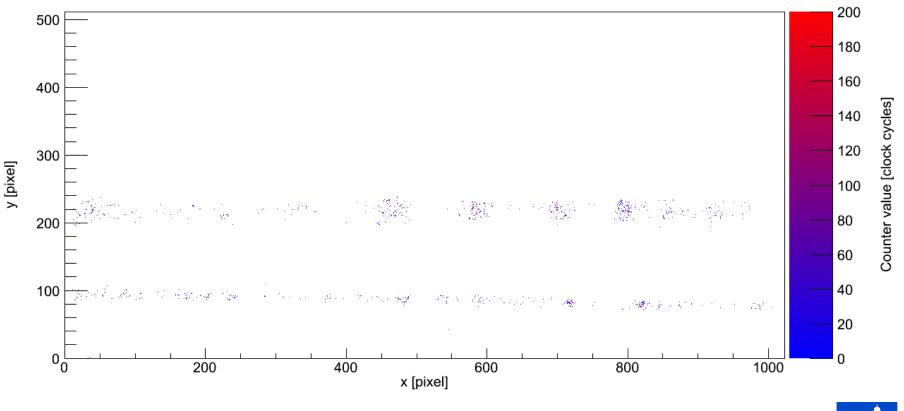

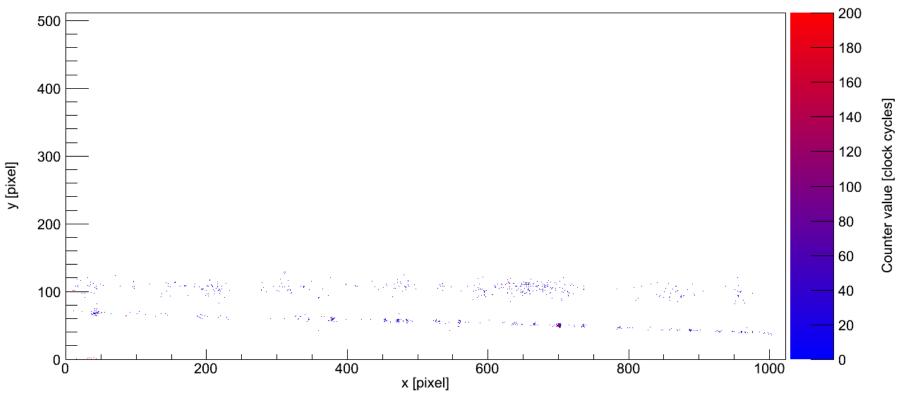

System was used in a two weeks testbeam at DESY in March/April

- $\rightarrow$  excellent performance, expectations were more than met!

- Data recorded with 2,5 Hz, not zero suppressed

- Two LCTPC modules (GEM and InGrid)

- Few runs interrupted by failure of SRS system (bugs in Code?, UDP, receiver time out)

- ATX power supply could not stand stray field of 1T magnet

- crate was placed at position with ~ 0,1 0,3 T

- ATX died during magnet ramp up

- $\rightarrow$  ATX + crate placed further away  $\rightarrow$  longer power cables (~3m)

- FEC stayed next to magnet

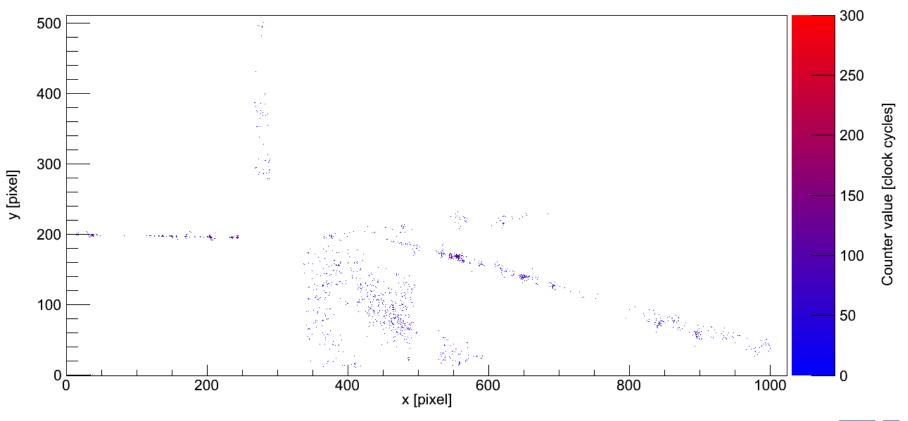

Counter value [clock cycles] y [pixel] 0<sub>ò</sub> x [pixel]

universitätbonn

002251

universitätbonn

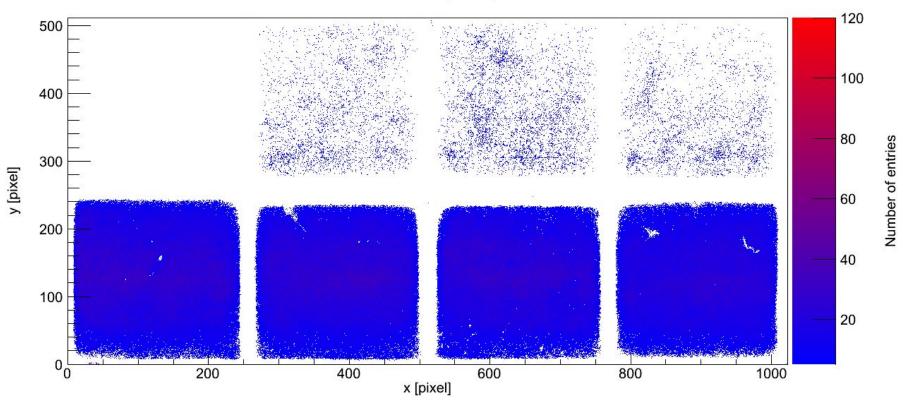

Occupancy

t universität**bonn**

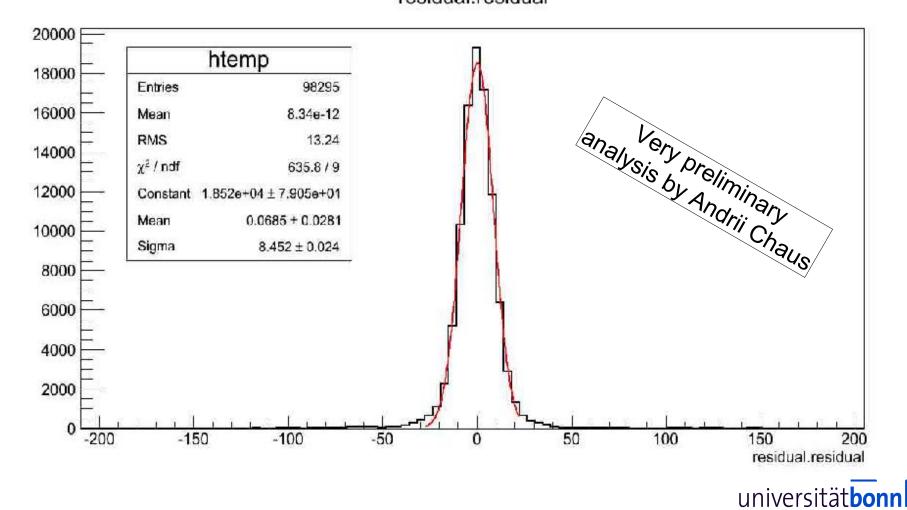

Some physics results and detector development: talk yesterday in WP2 by Jochen Kaminski residual.residual

- System is ready for use

- read out boards with 1-8 Timepix chips

- threshold equalisation and calibration with external pulses possible

- data taking was confirmed in a test beam (~ 2 mio. frames recorded)

- Modified FPGA code used for small scale systems on Xilinx Boards

- Uni Siegen (Timepix + GEM): R&D

- CAST (InGrid): Dark matter search

- Development on FPGA code and hardware (FEC adapter + chip carrier)

- HDMI cables

- DACs and ADC on FEC adapter, I2C communication

- support would be appreciated for DDR2 implementation

<u>Advanced European Infrastructures for Detectors at Accelerators</u>

- 4 year EU FP 7 Research Infrastructures program project

- Started February 2011

- > 80 institutes from 23 European countries

- Budget: 27 million € (8 million € from the EU)

- Coordinated by CERN

Subtask 9.2.3 (Bonn, CEA, Mainz, NIKHEF):

Common readout systems for gaseous detectors. Auxiliary electronics for the read-out of pixellated front-end chips, aimed at highly granular pixel read-out of gas detectors, are to be developed.

- $\rightarrow$  New readout system for pixellated chip (Timepix chip)

- $\rightarrow$  Cover large area for TPC/inner tracker application