# Alice CTP upgrade

#### Marián Krivda on behalf of the ALICE trigger group

The University of Birmingham

**Triggering Discoveries in High Energy Physics** 9-14 September 2013 , Jammu, India

#### Plan of talk

- Short overview of current CTP

- Upgrade requirements for Run 2 (2015–2017)

- LM level

- Extension of classes

- Extension of clusters

- Second link to DAQ

- New L0 board

- Ideas for upgrade for Run3 (2019-2021)

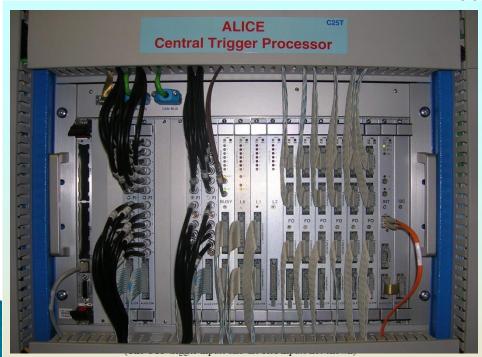

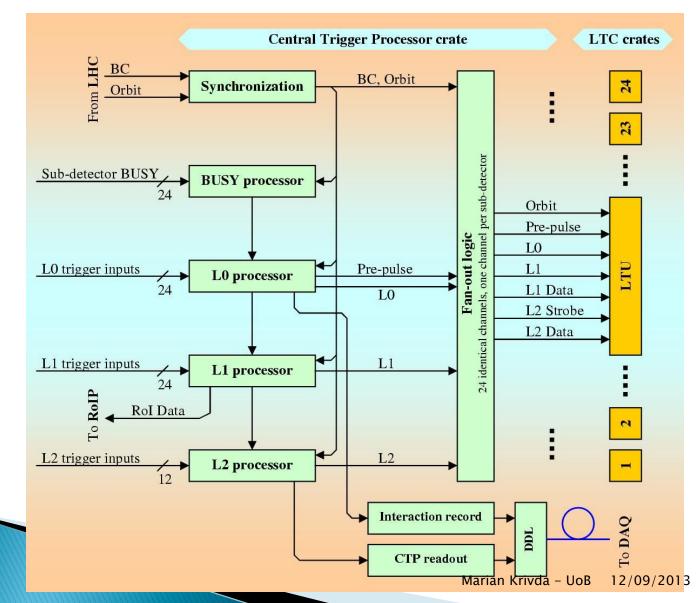

### **Current Alice trigger system**

- Central Trigger Processor (CTP): receives trigger detector inputs, makes decision

- Local Trigger Unit (LTU): interface between CTP and readout detectors

- Trigger and Time Control (TTC): transmits LHC clock and delivers trigger signals to detectors

- Due to short time for L0 latency the CTP is in the experimental cavern

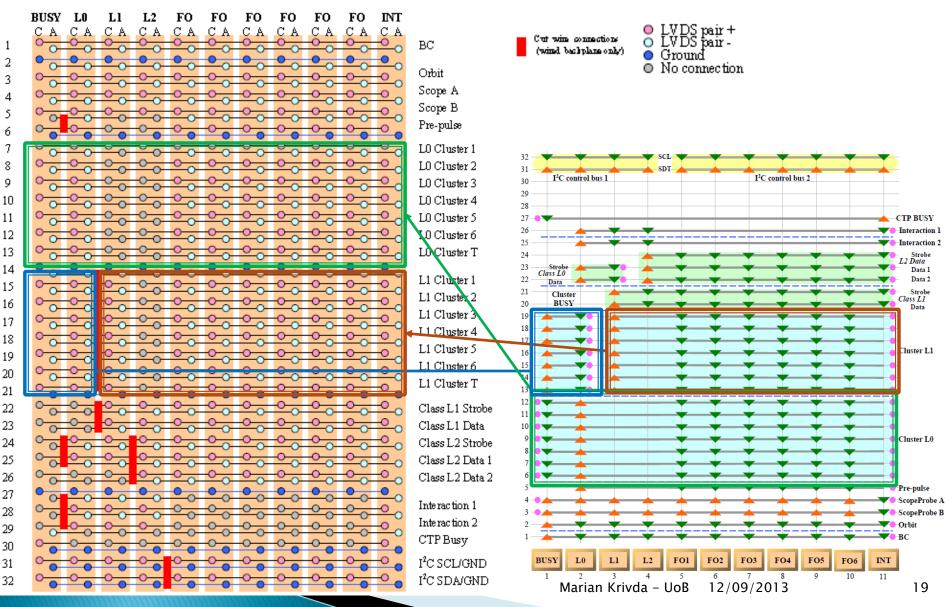

- 6U VME boards

- L0, L1, L2 boards

- BUSY board

- FO boards

- INT board

- I2C board

- LVDS Trigger inputs

- Outputs are sent to Local Trigger Units (LTUs) where conversion to TTC format occurs

#### Current CTP

- 3 HW trigger levels:

- L0 inputs to CTP up to 800 ns, time for making decision 100 ns, time for delivery to detectors up to 300 ns, together is max. 1.2 μs from interaction;

- L1 inputs to CTP up to 6.1 μs; time for making decision 100 ns, together is max. 6.5 μs from interaction;

- L2 delivered to detectors  $105 \ \mu s$  from interaction.

- ▶ 60 trigger inputs

- L0 24; L1 24; L2 12.

- Up to 24 detectors

- 6 independent partitions (*clusters*)

- ► 50 classes

- 4 past/future protection circuits

- Interaction record a list of all the bunch-crossings in which the Interaction signal has been detected; also for past-future protection check and pattern recognition

- Rare event handling

#### **CTP data flow**

#### **Requirements for Run 2**

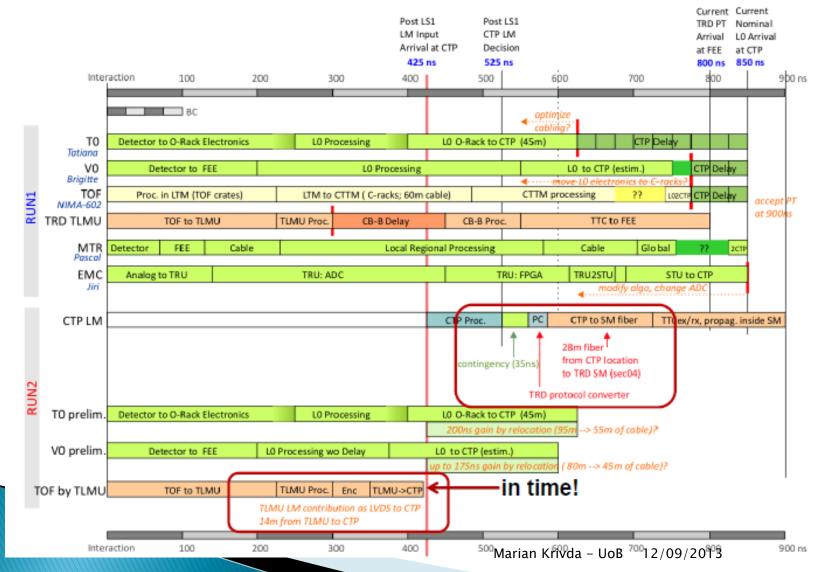

- New CTP level -> LM (instead of TRD pretrigger)

- 100 classes (instead 50)

- 8 physics clusters (instead 6)

#### LM trigger for TRD

#### New trigger level -> LM

- Currently TRD pre-trigger is generated even if CTP is busy i.e. TRD pre-trigger electronics doesn`t see CTP busy signal

- In order to reduce the level of "wasted" pre-triggers currently generated by TRD pre-trigger, the pretrigger electronics will be replaced by a new level (LM) of trigger logic, run at the CTP, which will be used to generate a wake-up signal to the TRD

- Needs new faster inputs from T0, and VZERO

- Needs relocation of T0 and VZERO electronics closer to CTP -> in progress

- Needs re-cabling of T0, VZERO and TRD trigger cables

- -> in progress

Needs new L0 board

# Preliminary timing for TO, VO and TOF trigger inputs

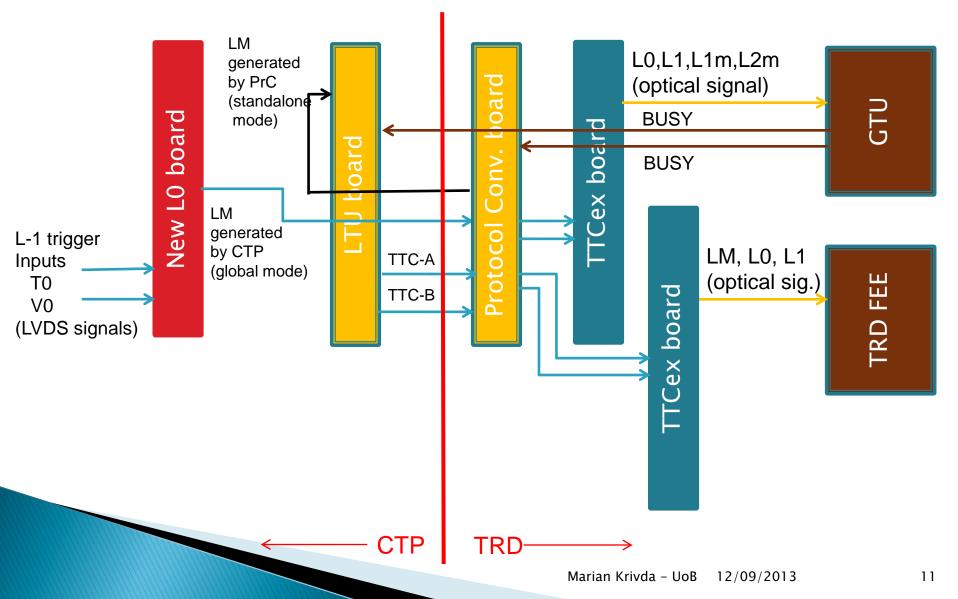

## LM trigger for TRD

- Two trigger sequences for TRD

- GTU receives standard TTC sequence (L0 L1 L2) from LTU –> TTCex

- FEE receives custom trigger sequence (LM L0 L1)

) from CTP -> Protocol Converter -> TTCex

#### Global\Standalone mode

- In global mode CTP generates LM trigger which is sent to Protocol Converter (PC) board

- In standalone mode PC board generates LM trigger which is sent to PULSER input on LTU board

# LM trigger for TRD

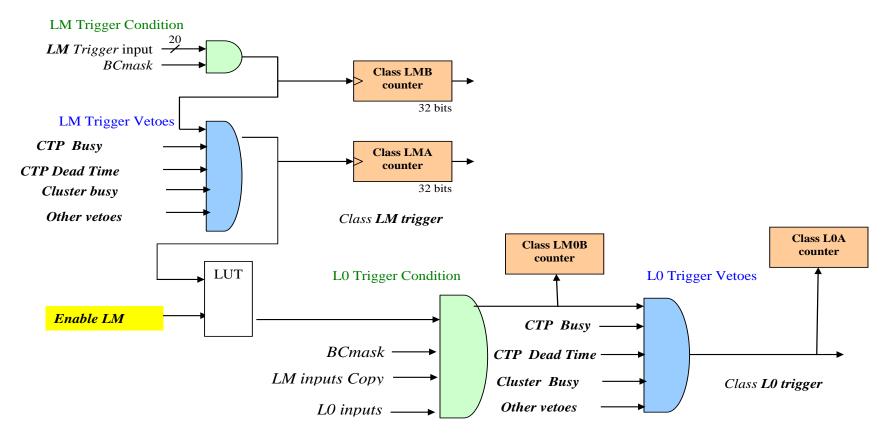

# LM trigger for TRD – FPGA logic

Delayed copy of LM trigger input will be provided at L0 time

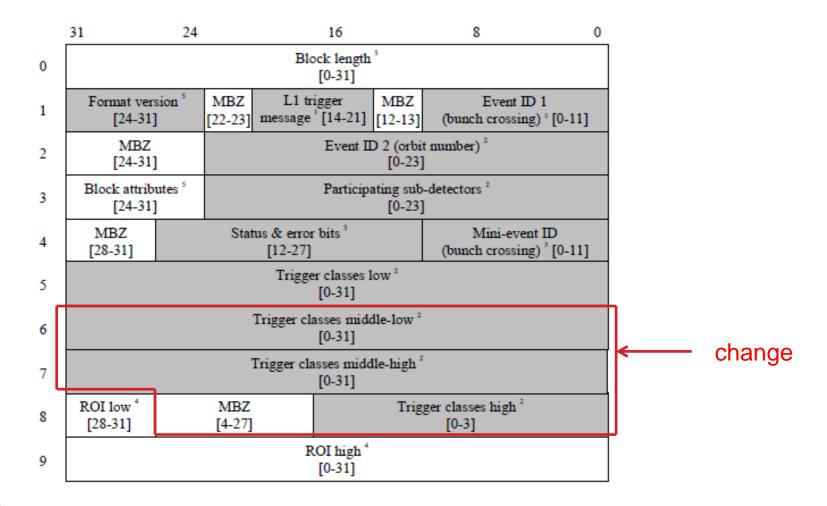

#### **Extension of Classes**

#### 100 classes

- Extension of the number of classes, each defined in the same way as at present

- Simple to implement at CTP (just scaling)

- Need to check space on L1, L2, FO boards (their FPGAs)

- Simple to implement in offline

- no restrictions on attributes e.g. bc masks

- Consequences:

- Change of L2A message (50 bits longer)

- Change of Common Data Header (CDH)

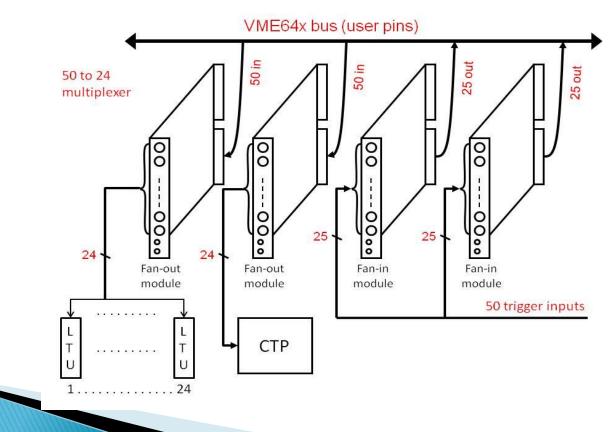

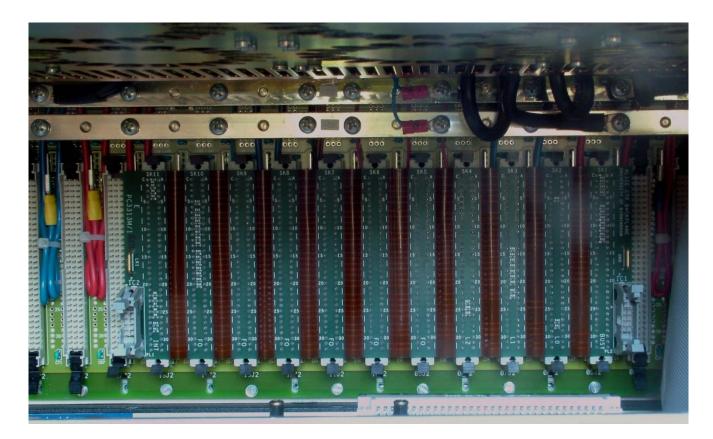

# All connections between CTP boards are on CTP backplane

- Flex PCB with VME connectors

- User Defined (UD) pins on VME are used for connections

Marian Krivda – UoB 12/09/2013

#### 100 classes

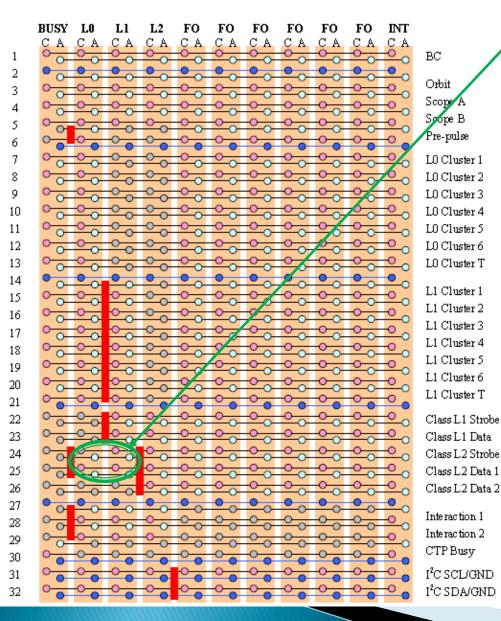

- 2 links:

- L0 Class data

- L0 Class strobe

- L0 Class data used on current CTP to transmit 50 class bits

- L0 Class strobe used on current CTP to transmit "L0 inputs" (sent from INT board to DAQ after each L2a trigger)

- New L0 board => "L0 inputs" sent to DAQ directly (after each L0 trigger)

- L0 Class strobe can be used to transmit another 50 class bits

#### **Extension of Clusters**

#### Clusters

- ▶ 6 physics + 1 software cluster available now

- Limited by number of links on backplane connections between L0/L1/2 and FO boards

- Increasing number of clusters to 8 requires multiplexing on backplane

- Consequences:

- Increased latency of CTP for L0 trigger by at least one BC

- Change in L2a trigger message

#### **CTP** backplane limitations for clusters

### Cluster data on CTP backplane

- Cluster strobe can start at even or odd slice of transmission

- 2 consecutive BCs x 7 links = 14 bits available

- STROBE + 9 data bits + 4 Hamming bits

- 8 clusters + 1 test cluster (sw triggers) + 4 Hamming bits

| CLST_1 | CLST_7     |

|--------|------------|

| CLST_2 | CLST_8     |

| CLST_3 | CLST_9 (T) |

| CLST_4 | Hamming_1  |

| CLST_5 | Hamming_2  |

| CLST_6 | Hamming_3  |

| STROBE | Hamming_4  |

|        |            |

### **Cluster BUSY on CTP backplane**

- $\succ$  2 consecutive BCs x 7 links = 14 bits available

- STROBE + 9 data bits + 4 Hamming bits

- Consequences -> 1 BC delay for BUSY

| CLST_1_B | CLST_7_B     |

|----------|--------------|

| CLST_2_B | CLST_8_B     |

| CLST_3_B | CLST_9_B (T) |

| CLST_4_B | Hamming_1    |

| CLST_5_B | Hamming_2    |

| CLST_6_B | Hamming_3    |

| STROBE   | Hamming_4    |

#### **Current solution for Cluster BUSY**

- If no cluster BUSY => no cluster BUSY strobe active

- Cluster BUSY strobe can start at even or odd slice of transmission

- Always make OR from 2 consecutive BUSY signals in order not to miss BUSY during transmission (50 ns)

- 8 clusters BUSYs + 1 test cluster BUSY (sw triggers) + Hamming bits

#### New format for L1 and L2 trigger data

| L1 Data serial format |                |        |          |       |        |  |  |  |

|-----------------------|----------------|--------|----------|-------|--------|--|--|--|

| Serial                | Data           | Sequen | nce List | L1 Me | essage |  |  |  |

| bit                   | Daia           | Word   | Bit      | Word  | Bit    |  |  |  |

| 1                     | Spare          | 0      | 15       | 1     | 11     |  |  |  |

| 2                     | CIT            | 0      | 14       | 1     | 10     |  |  |  |

| 36                    | <b>RoC[41]</b> | 0      | 1310     | 1     | 96     |  |  |  |

| 7                     | ESR            | 0      | 9        | 1     | 5      |  |  |  |

| 8                     | L1SwC          | 0      | 8        | 1     | 4      |  |  |  |

| 910                   |                | 0      | 76       | 1     | 32     |  |  |  |

| 1112                  |                | 1      | 1514     | 1     | 10     |  |  |  |

| 1324                  |                | 1      | 132      | 2     | 110    |  |  |  |

| 2526                  | L1Class[501]   | 1      | 10       | 3     | 1110   |  |  |  |

| 2736                  |                | 2      | 156      | 3     | 90     |  |  |  |

| 3742                  |                | 2      | 50       | 4     | 116    |  |  |  |

| 4348                  |                | 3      | 1510     | 4     | 50     |  |  |  |

| 4958                  |                | 3      | 90       | 5     | 112    |  |  |  |

| 5970                  | L1Class[10051] | 8      | 110      | б     | 110    |  |  |  |

| 7174                  |                | 8      | 1512     | 7     | 30     |  |  |  |

| 7582                  |                | 9      | 70       | 7     | 114    |  |  |  |

| 8390                  |                | 9      | 158      | 8     | 70     |  |  |  |

| 9194                  |                | 10     | 30       | 8     | 118    |  |  |  |

| 95106                 |                | 10     | 154      | 9     | 110    |  |  |  |

| 107108                |                | 11     | 10       | 10    | 1.0    |  |  |  |

|                       | Spare          |        |          | 10    | 112    |  |  |  |

| L2 Data serial format |                |        |          |             |     |  |  |  |

|-----------------------|----------------|--------|----------|-------------|-----|--|--|--|

| Serial                | Darta          | Sequer | nce List | L2a Message |     |  |  |  |

| bit                   | Data           | Word   | Bit      | Word        | Bit |  |  |  |

| 1                     | L2arF          |        |          |             |     |  |  |  |

| 213                   | BCID[121]      |        |          | 1           | 110 |  |  |  |

| 1425                  | OrbitID[2413]  |        |          | 2           | 110 |  |  |  |

| 2637                  | OrbitID[121]   |        |          | 3           | 110 |  |  |  |

| 38                    | Spare          | 4      | 14       | 4           | 11  |  |  |  |

| 39                    | ESR            | 4      | 13       | 4           | 10  |  |  |  |

| 40                    | CIT            | 4      | 12       | 4           | 9   |  |  |  |

| 41                    | L2SwC          | 4      | 11       | 4           | 8   |  |  |  |

| 4247                  | L2Cluster[61]  | 4      | 105      | 4           | 72  |  |  |  |

| 4849                  | L2Class[5049]  | 4      | 43       | 4           | 10  |  |  |  |

| 5052                  | L2Class[4825]  | 4      | 20       | 5           | 119 |  |  |  |

| 5361                  |                | 5      | 157      | 5           | 80  |  |  |  |

| 6268                  |                | 5      | 60       | 6           | 115 |  |  |  |

| 6973                  | Detector[241]  | 6      | 1511     | 6           | 40  |  |  |  |

| 7484                  |                | 6      | 100      | 7           | 111 |  |  |  |

| 85                    | L2Class[241]   | 7      | 15       | 7           | 0   |  |  |  |

| 8697                  |                | 7      | 143      | 8           | 110 |  |  |  |

| 98109                 | L2Class[10051] | 12     | 110      | 9           | 110 |  |  |  |

| 110113                |                | 12     | 1512     | 10          | 30  |  |  |  |

| 114121                |                | 13     | 70       | 10          | 114 |  |  |  |

| 122129                |                | 13     | 158      | 11          | 70  |  |  |  |

| 130133                |                | 14     | 30       | 11          | 118 |  |  |  |

| 134145                |                | 14     | 154      | 12          | 110 |  |  |  |

| 146148                |                | 11     | 32       | 13          | 10  |  |  |  |

| 149.150               | L2Cluster[87]  | 11     | 54       | 13          | 32  |  |  |  |

|                       | Spare          | 11     | 156      | 13          | 114 |  |  |  |

#### New Common Data Header format

#### Second link to DAQ

## Second (new) link to DAQ

- 10G Ethernet

- New interaction (INT) record -> send 24 (48) inputs with each BC when interaction occurred instead of many INT definitions

- DAQ pick-up L0 trigger inputs from interaction stream (discussion with Alice DAQ group ongoing)

#### New format of CTP readout (via first link to DAQ)

| Wo | ord | [3116]         | [15]        | [1412]         | [110]                 |

|----|-----|----------------|-------------|----------------|-----------------------|

| 1  | L   |                |             |                | BCID[110]             |

| 2  |     | Don't care (0) | BlockID = 0 | Don't care (0) | <b>OrbitID</b> [2312] |

| 3  | ;   |                |             |                | <b>OrbitID</b> [110]  |

Physics trigger

Software trigger

|      | Bit    | Data                 |      | Bit    | Data              |

|------|--------|----------------------|------|--------|-------------------|

|      | [3116] | Don't care (0)       |      | [3116] | $Don't \ care(0)$ |

|      | [15]   | <b>BlockID</b> = $0$ |      | [15]   | BlockID = 0       |

| 4    | [1411] | Don't care (0)       | 4    | [1411] | $Don't \ care(0)$ |

|      | [10]   | ESR                  | rd   | [10]   | $Don't \ care(0)$ |

| Word | [9]    | Don't care (0)       | Word | [9]    | CIT               |

|      | [8]    | L2SwC = 0            |      | [8]    | L2SwC = 1         |

|      | [76]   | L2Cluster [65]       |      | [76]   | $Don't \ care(0)$ |

|      | [52]   | L2Cluster [41]       |      | [52]   | <b>RoC</b> [41]   |

|      | [10]   | L2Class [5049]       |      | [10]   | Don't care (0)    |

| Word | [3116]    | [15] | [1412] | [110]          |

|------|-----------|------|--------|----------------|

| 5    | э         | 0 =  | э      | L2Class [4837] |

| 6    | ()        | Ë    | ))     | L2Class [3625] |

| 7    | )))<br>)) | ock  | ())    | L2Class [2413] |

| 8    | Ď         | B    | D      | L2Class [121]  |

| Word | [3116]    | [15] | [1412]          | [110]             |

|------|-----------|------|-----------------|-------------------|

| 5    | e         | 0 =  | e               | L2Detector [2413] |

| 6    | ()        | Ē    | ()              | L2Detector [121]  |

| 7    | Don't (0) | ock  | ( <i>no</i> ()) | Don't care (0)    |

| 8    |           | BI   | D               | Don't care (0)    |

| Word | [3116]         | [15]           | [1412]      | [110]                 |               |

|------|----------------|----------------|-------------|-----------------------|---------------|

| 9    |                |                | •           | <b>L0TrgIn</b> [2413] |               |

| 10   |                |                |             | L0TrgIn[121]          |               |

| 11   | Don't care (0) | Don't care (0) | BlockID = 0 | Don't care (0)        | L1TrgIn[2413] |

| 12   |                |                |             | L1TrgIn[121]          |               |

| 13   |                |                |             | L2TrgIn[121]          |               |

#### New Interaction record format (proposal)

| Word | [31]      | [30]           | [29] | [2812]     | [110]                    |

|------|-----------|----------------|------|------------|--------------------------|

| 1    | 1 (Orbit) | 1 (first word) | Err  | Don`t care | Orbit number [2312]      |

| 2    | 1         | 0 (second w.)  | Err  | Don't care | Orbit number [110]       |

| 3    | 0 (BC)    | 1 (first word) | L    | 0ti[181]   | <b>BC</b> number [110]   |

| 4    | 0         | 0 (second w.)  |      | ]          | L0ti[4819]               |

| :    |           |                | :    |            | :                        |

| n    | 0         | 1              | L    | 0ti[181]   | <b>BC</b> number [110]   |

| n+1  | 0         | 0              |      | ]          | L0ti[4819]               |

| :    |           |                |      | :          | :                        |

| 251  | 0         | 1              | L    | 0ti[181]   | <b>BC</b> number [110]   |

| 252  | 0         | 0              |      | ]          | L0ti[4819]               |

| 253  | 0         | 0              | 0    | Don`t care | Incomplete record (hFFF) |

#### Discussion with Alice DAQ group ongoing

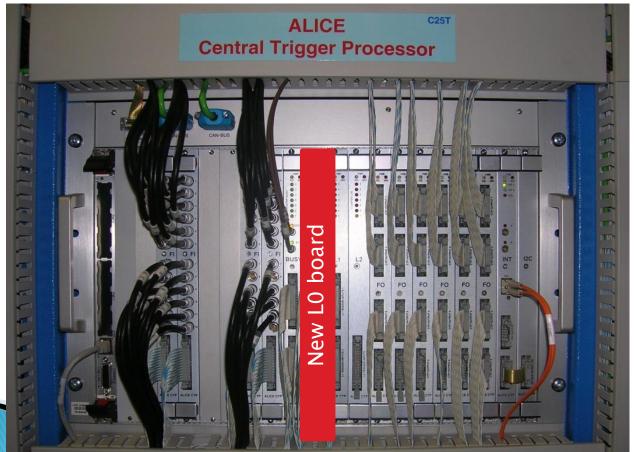

#### New LO board

## Alice trigger system for Run 2

- Faster inputs from T0 and V0

- Upgrade of firmware for L1 ,L2 ,FO, BUSY and INT boards

- Completely new L0 board

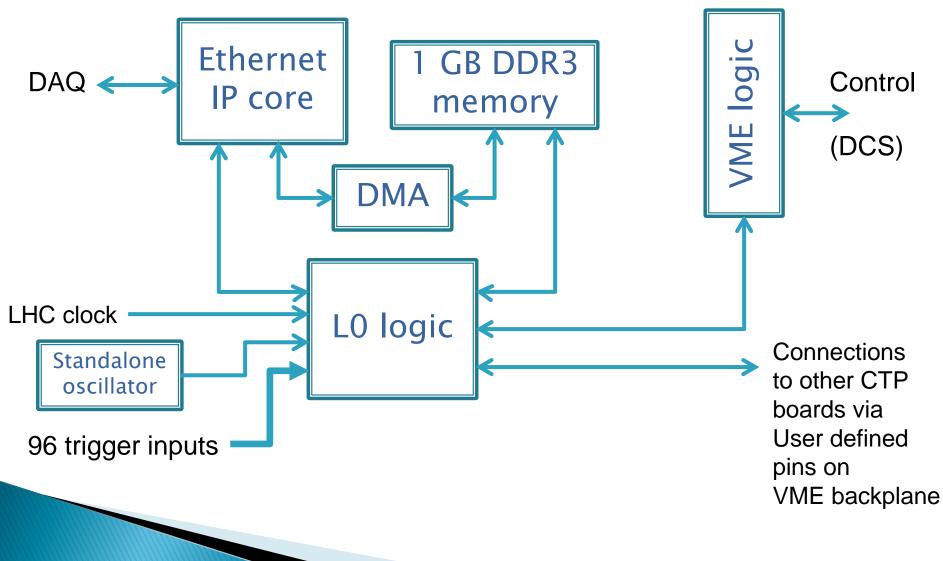

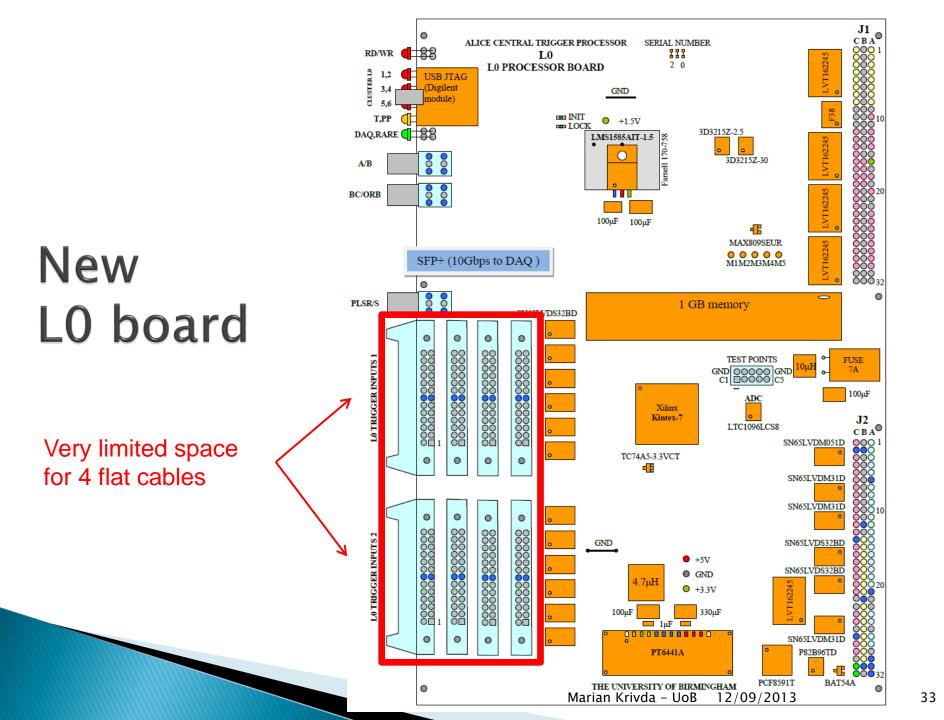

#### New LO board

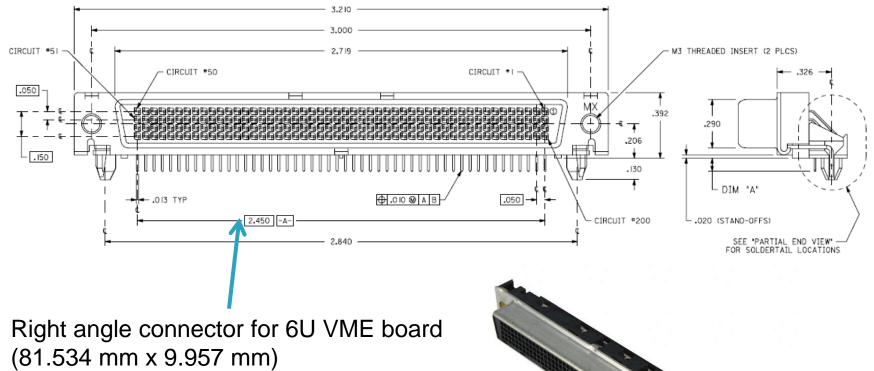

>96 trigger inputs -> new type of connector for front panel (48 inputs for L0 + other possible trigger inputs)

- New FPGA Xilinx Kintex7

- Bigger memory (DDR3 1GB)

- Synchronized downscaling

- >CTP switch for L0 trigger inputs (48->24) inside FPGA

- >More counters i.e. for classes and clusters

- >New 10G link to DAQ from L0 board

- New interaction record -> send 24/48 inputs with each interaction

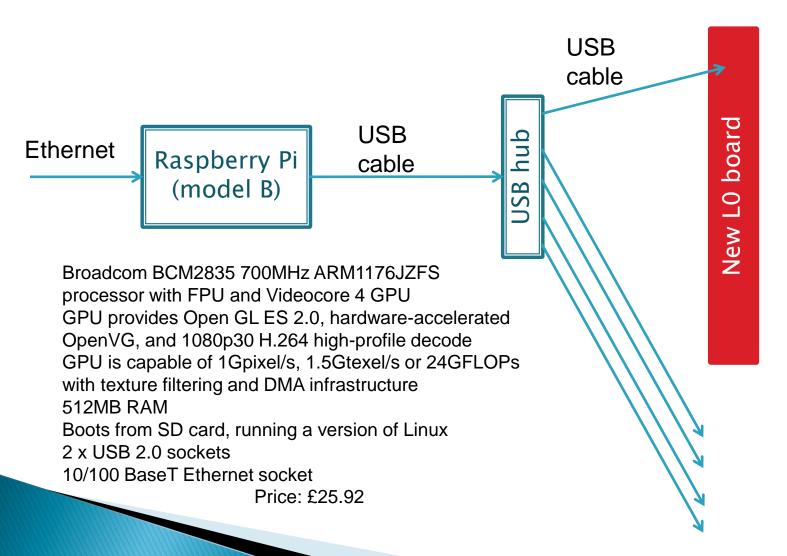

Control of L0 board via 10G Ethernet (or other protocol) in future

#### New LO board - block diagram

#### Front panel connector for 96 LVDS trigger inputs (200 pins – 96 diff. pairs + 8 GND pins)

#### FPGA – Xilinx XC7K325TFFG900

#### Kintex-7 FPGA Feature Summary

Bank 34

HP 50 I/0

Bank 33

Bank 32

50 I/O

HP 50 I/0

Table 5: Kintex-7 FPGA Feature Summary by Device

| Device Lo<br>G | Logic · | Configui<br>Block:    | able Logic<br>s (CLBs) DSP     |                       | Bloc  | llock RAM Blocks <sup>(3)</sup> |         |                      |                     |      | XADC   | Total I/O            | Max                        |

|----------------|---------|-----------------------|--------------------------------|-----------------------|-------|---------------------------------|---------|----------------------|---------------------|------|--------|----------------------|----------------------------|

|                | Cells   | Slices <sup>(†)</sup> | Max<br>Distributed<br>RAM (Kb) | Slices <sup>(2)</sup> | 18 Kb | 36 Kb                           | Max(Kb) | смт.s <sup>(4)</sup> | PCIe <sup>(5)</sup> | GTXs | Blocks | Banks <sup>(6)</sup> | User<br>1/0 <sup>(7)</sup> |

| XC7K70T        | 65,600  | 10,250                | 838                            | 240                   | 270   | 135                             | 4,860   | 6                    | 1                   | 8    | 1      | 6                    | 300                        |

| XC7K160T       | 162,240 | 25,350                | 2,188                          | 600                   | 650   | 325                             | 11,700  | 8                    | 1                   | 8    | 1      | 8                    | 400                        |

| XC7K325T       | 326,080 | 50,950                | 4,000                          | 840                   | 890   | 445                             | 16,020  | 10                   | 1                   | 16   | 1      | 10                   | 500                        |

| XC7K355T       | 356,160 | 55,650                | 5,088                          | 1,440                 | 1,430 | 715                             | 25,740  | 6                    | 1                   | 24   | 1      | 6                    | 300                        |

| XC7K410T       | 406,720 | 63,550                | 5,663                          | 1,540                 | 1,590 | 795                             | 28,620  | 10                   | 1                   | 16   | 1      | 10                   | 500                        |

| XC7K420T       | 416,960 | 65,150                | 5,938                          | 1,680                 | 1,670 | 835                             | 30,060  | 8                    | 1                   | 32   | 1      | 8                    | 400                        |

| XC7K480T       | 477,760 | 74,650                | 6,788                          | 1,920                 | 1,910 | 955                             | 34,380  | 8                    | 1                   | 32   | 1      | 8                    | 400                        |

Bank 18 50 I/O Bank 17 HR 50 I/O Bank 16 HB 50 I/O Bank 15 HR 50 I/O Bank 14 HR 50 I/O Bank 13 HR 50 I/O Bank 12 50 1/0

#### 10 usable I/O banks

7 High Range (HR) banks -> support 1.35 - 3.3V standards

3 High Performance (HP) banks -> support 1.35 - 1.8 V standards

#### Configuration of Xilinx XC7K325T FPGA from memory

- The Master SPI configuration mode supports reading from an SPI flash using a data bus up to four bits wide

- Config. CLK generated by FPGA

- Configuration bitstream length -> 91,548,896

- MICRON N25Q128 (128–Mbit 3 V, 4–data pins, serial flash memory with 108 MHz SPI bus interface

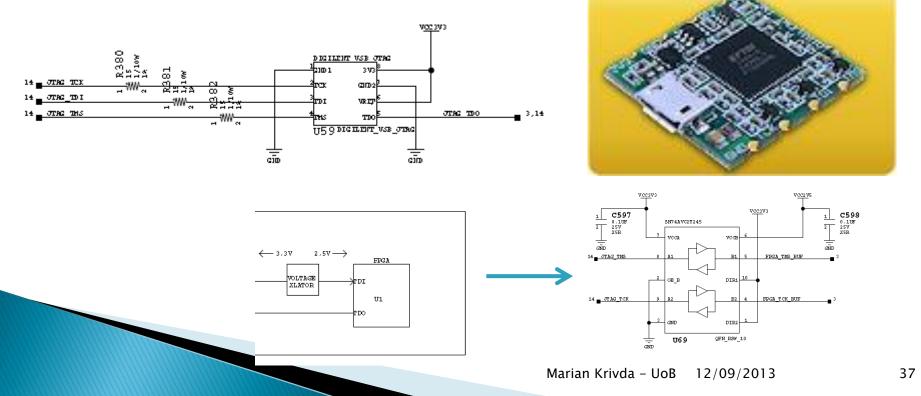

# Configuration of FPGA via JTAG serial interface

- JTAG interface for prototyping and debugging

- On-board JTAG configuration circuitry to enable configuration over USB

- USB JTAG module (DIGILENT, price 40 USD)

# **Remote configuration of FPGA**

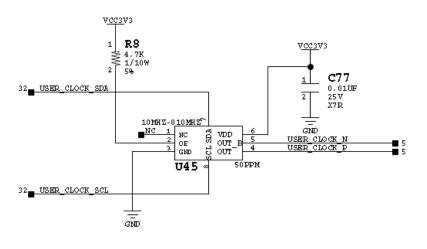

# Clock

- LHC clock as default

- In case LHC clock missing -> "switch over" functionality inside Xilinx Kintex-7 used for onboard oscillator (SILABS 570BAB000544DG)

- Programmable (via I2C) oscillator 10-810 MHz

#### Ideas for CTP upgrade for Run 3

# 3 Trigger levels

- LM: latency 0.8 µs, contribution from interaction trigger (upgraded V0/T0)

- L0: latency 1.2us, possible contribution from EMCAL, PHOS, TOF, ACORDE

- L1: latency 1.2-6 µs (fixed latency, but programmable in the given range), possible contribution from ZDC, EMCAL

- LM would still just be used as TRD pretrigger and would NOT be distributed to the other detectors.

#### **Continuous and Triggered mode**

- ITS, TPC and Muon Chambers can work in continuous AND triggered mode

- ITS is read out upon L0, all other detectors are read out upon L1

- If we do not introduce any selectivity at L1, then L1 can be made equal to L0.

#### Each detector as separate cluster

The default operation for PbPb, pPb and pp reference running would be a readout of all detectors, that are not busy, upon an Minimum Bias (MB) interaction trigger, with ITS, TPC and MCH in continuous readout mode.

# Cluster with more detectors still possible

- Operating at rates beyond the EMCAL readout rate it might then happen that there are a fraction of events with EMCAL data only and another fraction with TRD data only, and very few with both of them. Triggering an additional cluster containing EMCAL and TRD and triggering this cluster with a controlled rate will guarantee a given number of events with both detectors.

- For calibration purposes one might also want to have a fraction of events with ALL detectors present, so there would be an additional cluster with ALL detectors.

# Elimination of CTP dead time

- At 100kHz interaction rate the present CTP deadtime of 1.5 µs would lead to 15% inefficiency, which is of course too much.

- The deadtime must therefore be reduced below 100ns and additional "input FIFO" can eliminate the CTP deadtime (de-randomizing in addition the CTP must be able to accept more than one L0 before arrival of L1).

- In this way the CTP is not responsible for any rejection of data, it will only depend on the detector capabilities what fraction triggers is rejected by their own Busy i.e. by their deadtime and buffering capabilities.

## Heartbeat trigger

- Specific trigger issued by CTP at appropriate ORBIT/BC

- Reduces trigger data bandwidth

- Carrying commands and specific synchronization information

- Used by detectors create "heartbeat events" sent via output links

- Used by processing nodes data segmentation, fault finding, recovery procedures, …

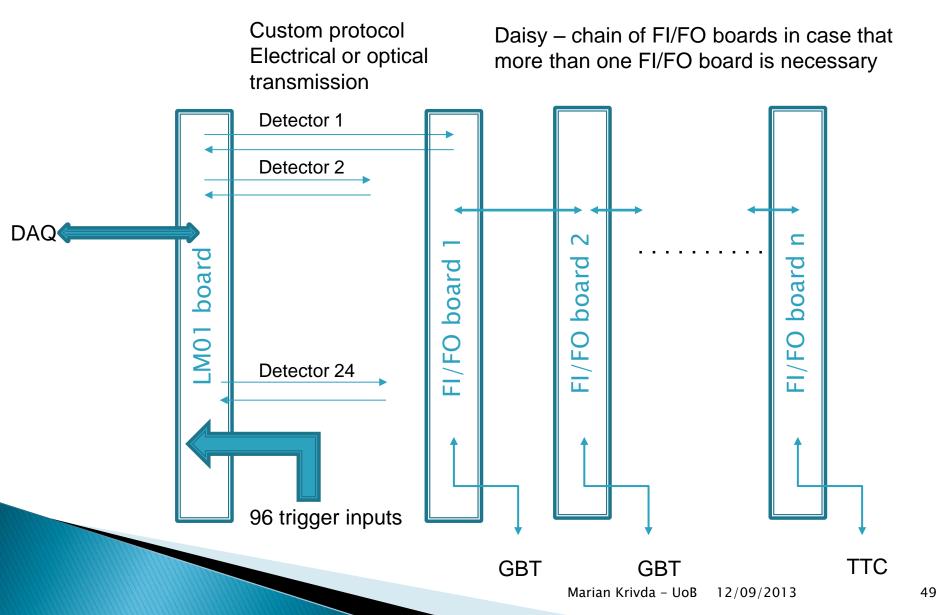

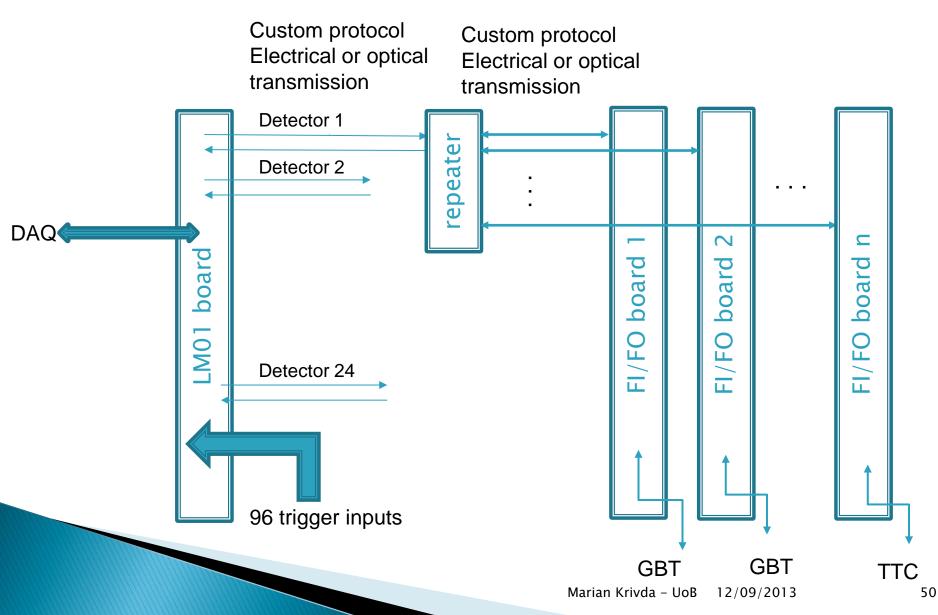

#### Trigger distribution -> GBT/TTC

- Proposal is to use GBT

- Some detectors will keep TTC

- CTP needs to serve both systems

## Detector`s behaviour

- ITS Cont / L0

- TPC Cont / L1

- TRD LM/LM+L1

- TOF L1

- EMC/PHOS L0+L1

- HMPID L0+L1

- MuID L1

- MCH Cont / L1

- ▶ V0/T0 L1

- ZDC L1

# Distribution of trigger signals

# Distribution of trigger signals

## Summary

- Activities for relocation and recabling of T0, V0 and TRD are ongoing.

- A new L0 board is in progress, production expected in Autumn 2013

- Firmware development and testing in 2014

- CTP proposal for run 3 is in preparation

- The upgraded CTP for Run 3 will be able to provide enough flexibility for all foreseen running scenario

## Back up slides

# Summary table (Run 3)

| Detector | type       | МЕВ       | t <sub>ro</sub> PbPb | Max. PbPb<br>readout rate | Max. pp and pPb<br>readout rate |

|----------|------------|-----------|----------------------|---------------------------|---------------------------------|

| ITS      | Cont. / L0 | n.a. / ?  | n.a. / ?             | 100 kHz                   | 400kHz                          |

| TPC      | Cont. / L1 | n.a.      | n.a.                 | n.a.                      | n.a.                            |

| TRD      | LM/LM+L1   | no        | 7-8 µs               | 100 kHz                   | 100kHz                          |

| TOF      | L1         | yes       | 5 µs                 | 200 kHz                   | 400kHz                          |

| EMC/PHOS | L0+L1      | yes at L1 | 20 µs                | 50 kHz                    | 50kHz                           |

| HMPID    | L0+L1      | ?         | ?                    | 10 kHz                    | 10kHz                           |

| MulD     | L1         | yes       | <200 ns              | 100 kHz                   | 400kHz                          |

| MCH      | Cont. / L1 | n.a.      | n.a.                 | 100 kHz                   | 400kHz                          |

| V0/T0    | L1         | yes       | 5us                  | 200 kHz                   | 400kHz                          |

| ZDC      | L1         | yes       | 5 µs                 | 100kHz                    | 400kHz                          |

# Current L0 trigger input switch

In order to handle more L0 trigger inputs the L0 trigger input multiplexer 50:24 has been made from available Faninout boards