## IC Design and Technologies for HL-LHC

A. Marchioro / CERN-PH-ESE

## Outline

- Background and motivation

- Technical roadmap

- Requirements

- Organizational issues

- Summary

## Background

- Modern HEP experiments depend on IC technology as much as they depend on powerful new accelerators.

- There is no distinction any more between detector and electronics, they are inseparable parts of the same instrument.

- COTS ICs are not sufficient because of unique radiation and functionality requirements.

- It is the functionality built into ICs that can add new "capabilities" to the detectors.

#### State of the art 2013: 16 nm FINFET

16 nm

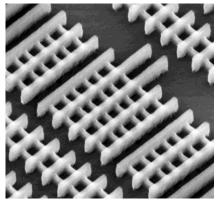

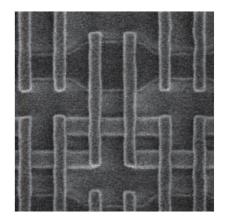

#### Some advanced devices

20 nm FDSOI from ST

22 nm TriGate from Intel

28 nm planar from TSMC

32 nm SOI from IBM

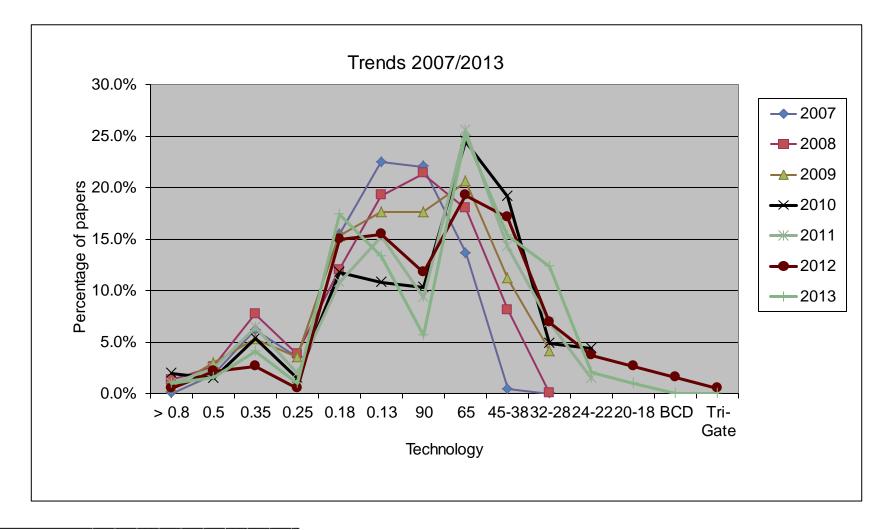

#### Technologies used in ISSCC<sup>[\$]</sup> papers

<sup>&</sup>lt;sup>[\$]</sup> ISSCC: International Solid State Circuits Conference

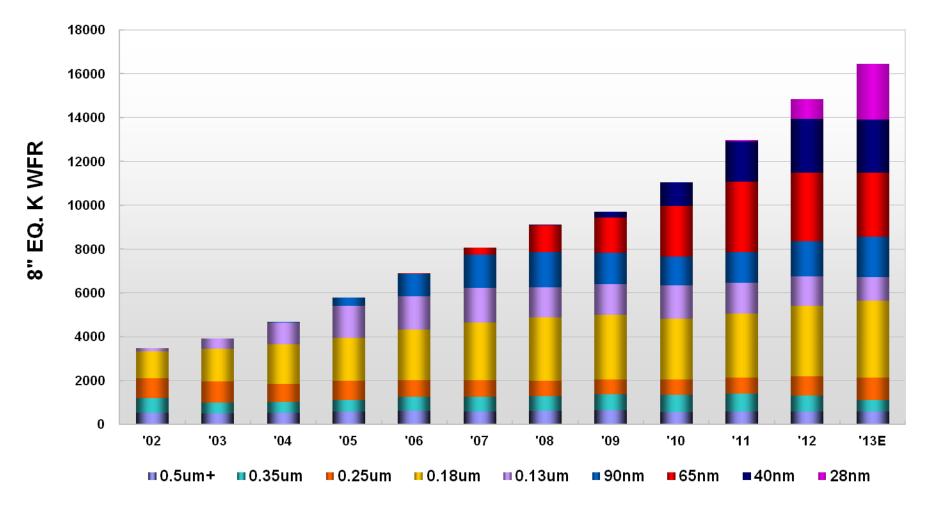

## Installed Capacity by Technology

## **Expected Requirements: CMOS**

|                                | .35 um<br>Power | 250 nm       | 180 nm       | 130 nm       | 65 nm | < 65 nm |

|--------------------------------|-----------------|--------------|--------------|--------------|-------|---------|

| Pixels (Hybrids)               |                 |              |              | 1            | 1     | 1       |

| Pixels (Monolithic)            |                 |              | $\checkmark$ | $\checkmark$ | 1     |         |

| Si Trackers                    |                 |              |              | 1            | 1     |         |

| Calorimeters                   |                 | $\checkmark$ |              | $\checkmark$ |       |         |

| ТРС                            |                 |              |              | 1            | 1     |         |

| MPGD                           |                 |              |              | 1            |       |         |

| Links (Electrical and Optical) |                 |              |              | 1            | 1     | 1       |

| Embedded Power                 | $\checkmark$    |              | 1            |              |       |         |

#### Interconnects

- New High-Density-Interconnect technologies are required:

- To manufacture large area, fully sensitive detectors

- To allow new functionalities to be implemented: mainly stacks of sensor-analog-digital chips with lower dead-material budgets

- For reducing assembly costs of detectors (today's this is the dominating cost)

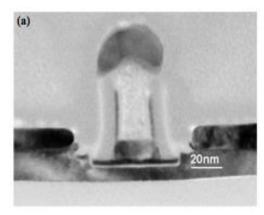

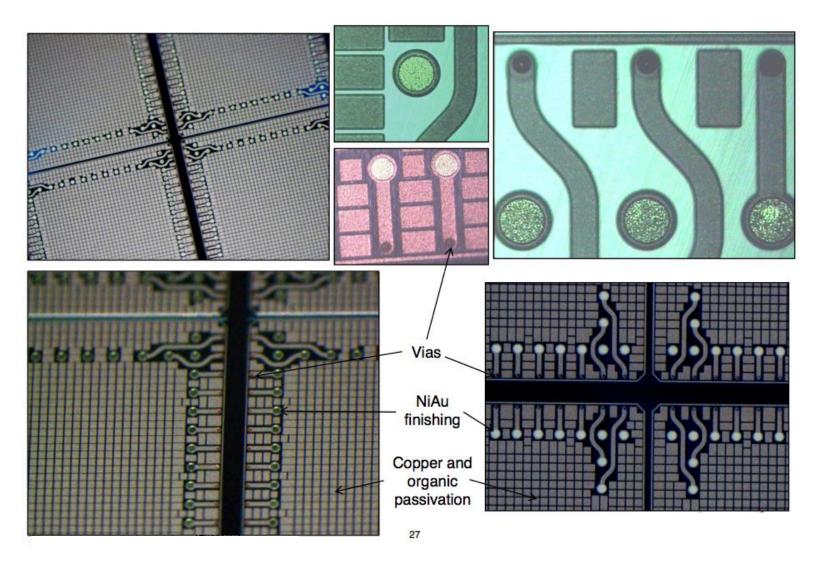

## HDI Example: TSV

### Requirements: High Density Interconnect

|              | Low Density<br>Bump Bonding | High Density<br>Bump Bonding<br>(< 100 um) | LD TSV       | HD TSV<br>(< 25 um) |

|--------------|-----------------------------|--------------------------------------------|--------------|---------------------|

| Pixels       | $\checkmark$                | $\checkmark$                               | $\checkmark$ | 1                   |

| Si Tracker   | $\checkmark$                |                                            | $\checkmark$ |                     |

| Calorimeters | ✓                           |                                            |              |                     |

| Links        | $\checkmark$                |                                            | $\checkmark$ |                     |

| ТРС          | $\checkmark$                |                                            | $\checkmark$ |                     |

| MPGD         | $\checkmark$                |                                            | $\checkmark$ |                     |

| Powering     | ✓                           |                                            | $\checkmark$ |                     |

## Organizational issues

• There is a large discrepancy between industrial and HEP projects cycles:

|          | Product<br>Design Cycle | Technology<br>Cycle |

|----------|-------------------------|---------------------|

| Industry | 6-9 m                   | < 2 y               |

| HEP      | > 3 y                   | > 5 y               |

- Large and complex SoC design require large and hierarchical engineering design teams

- Productivity of teams is a non-linear function of their size

- Many IP blocks can be purchased from external suppliers

- ADC macros, PLLs, SRAMs, IO libraries etc.

- "Routine tasks" can also be purchased

- Chips assembly, P&R services etc.

- Pure R&D is necessary only in relatively few domains

- Under the excuse of "too expensive", HEP rarely uses external design services and duplicates efforts often

# Examples of complexities accompanying technology scaling

- Technical:

- with shrinking the following issues become progressively more important:

- matching, planarity, proximity effects, short channel effects, wide channel effects, NBTI, hot-electron, number of model parameters, on-chip signal coupling, lower intrinsic transistor gain, number of technology options, lower supply voltage, higher gate leakage, atomic variability, line-edge-roughness...

- Thickness of technology design manual:

- 250 nm: ~ 200 pages

- 130 nm: ~ 500 pages

- 65 nm: > 1500 pages

## Costs/Performance<sup>[\$]</sup>

| Generation | Cost / mask | Cost / 8" | Cost      | Density        | Design     | Power per |

|------------|-------------|-----------|-----------|----------------|------------|-----------|

| [nm]       | set         | wafer     | Proto/mm2 | gates/[unit A] | Complexity | gate      |

| 250        | 1.0         | 1.0       | 1.0       | 1              | 1          | 1.00      |

| 130        | 2.9         | 0.9       | 6.0       | 5              | 3-5        | 0.36      |

| 65         | 5.3         | 1.1       | 10.8      | 27             | 10-25      | 0.18      |

| 28         | 15.0        | 2.4       | 36.3      | 50             | 25-125     | 0.09      |

<sup>[\$]</sup> Normalized to 250nm generation

## $\mu$ Technologies in HEP

- New technologies open up many new possibilities for creative physicists/engineers

- There is no doubt that commercial microelectronics technologies available today are well ahead of most requirements foreseen for the HL-LHC generation

- New technologies can only be exploited if:

- The design groups organizations are matched to the challenges and risks accompanying these technologies

- Minimum group sizes to be increased

- Project and personnel continuity to be preserved

- Duplications to be avoided

- The HEP community manages to keep a "privileged" (i.e. non strictly \$ based) access to advanced foundries

## Summary

- Advanced IC technologies are available to satisfy HL-LHC needs

- NRE Costs are high but not out of reach with respect to the size of the HL-LHC upgrade projects

- Radiation robustness to be validated and monitored

- HDI: TSVs may or may not become available for "small" customers

- To use these technologies successfully and efficiently, substantial engineering investments are necessary

- Adapt and evolve our design teams to the structure needed to manage these complex technologies

- Keep resources matched to the ambitions

- Strengthen collaborative support and shared services inside community