ECFA High-Luminosity LHC Experiments Workshop

muon system : #4

## Muon detector readout and <u>(hardware)</u> trigger-electronics upgrades for the HL-LHC

Masaya ISHINO (ATLAS, Kyoto Univ.) with the help of ... Herve Borel (ALICE) Kerstin Hoepfner (CMS) Alessandro Cardini (LHCb) maximize interesting events / time

different physics **target** → **approach** could be different

ATLAS , CMS : <u>high-p<sub>T</sub> μ</u> from heavy particles

**increase purity** of trigger events with sharper turn-on

what is done in Software → Hardware Trigger

LHCb , ALICE :  $\mu$  from B-meson, J/ $\psi$  decays , ...

simpler Hardware-Trigger, increase events processed

```

on Software-trigger

```

→ put more efforts on readout electronics

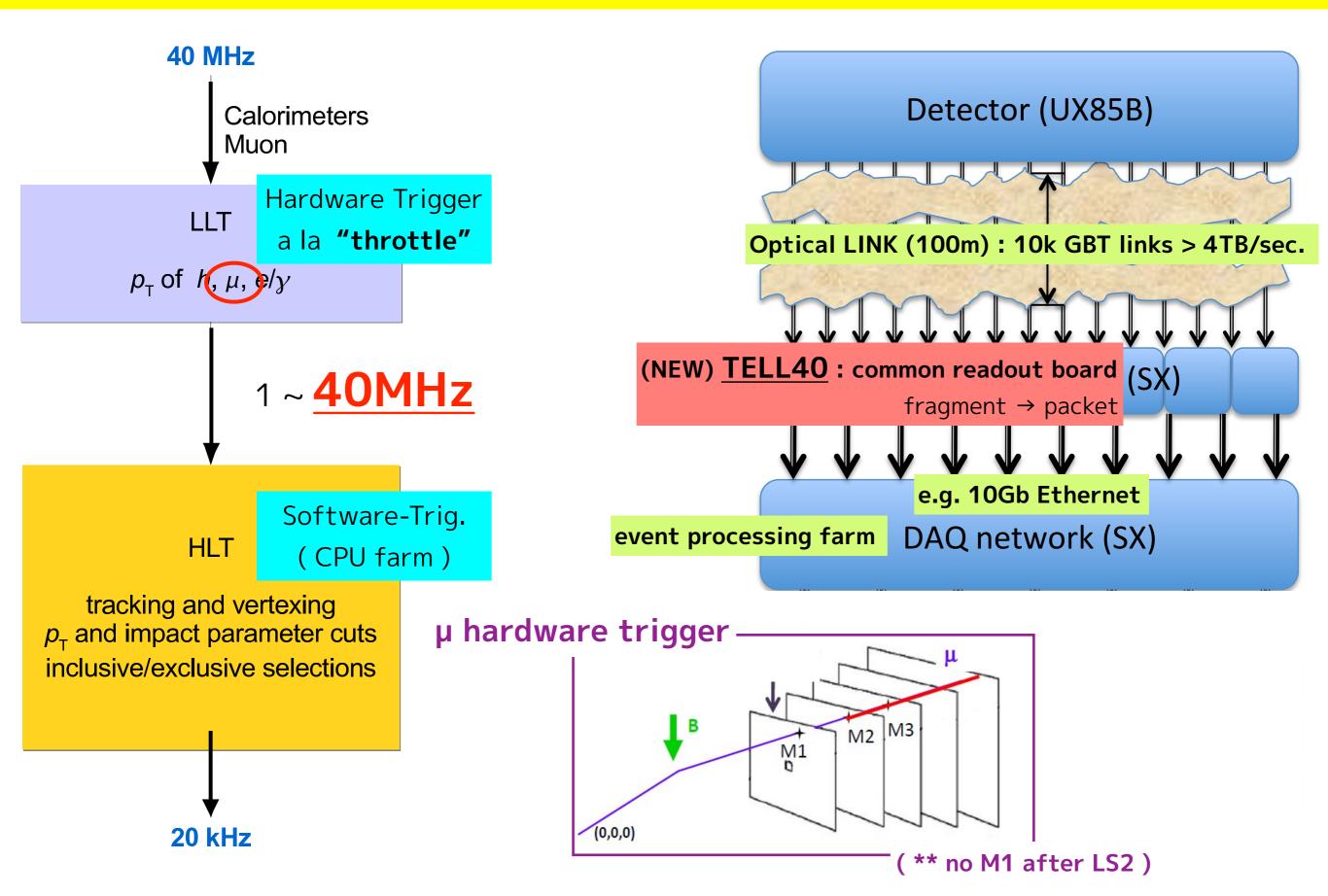

## LHCb DAQ/Trigger scheme

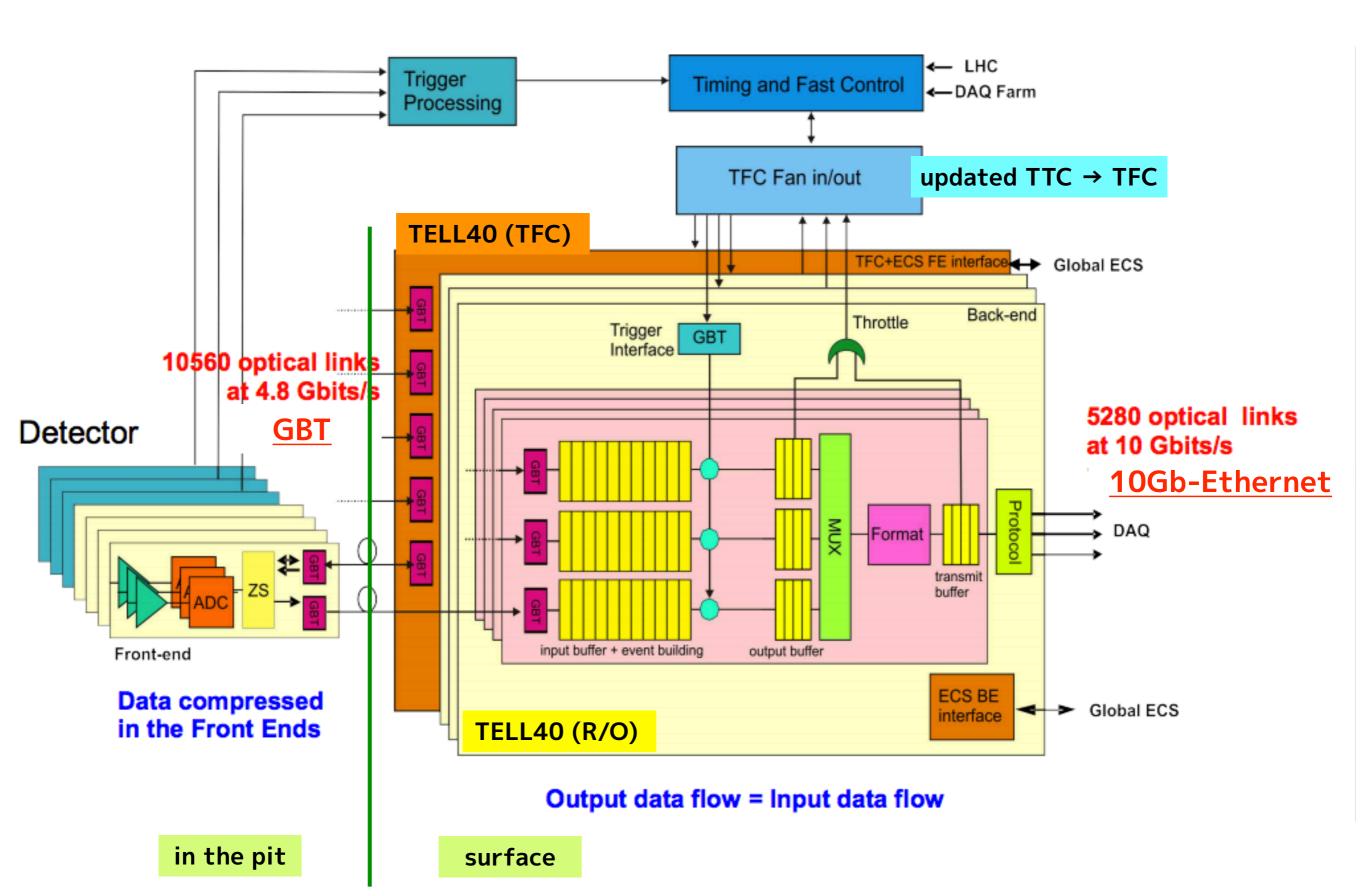

## LHCb Readout

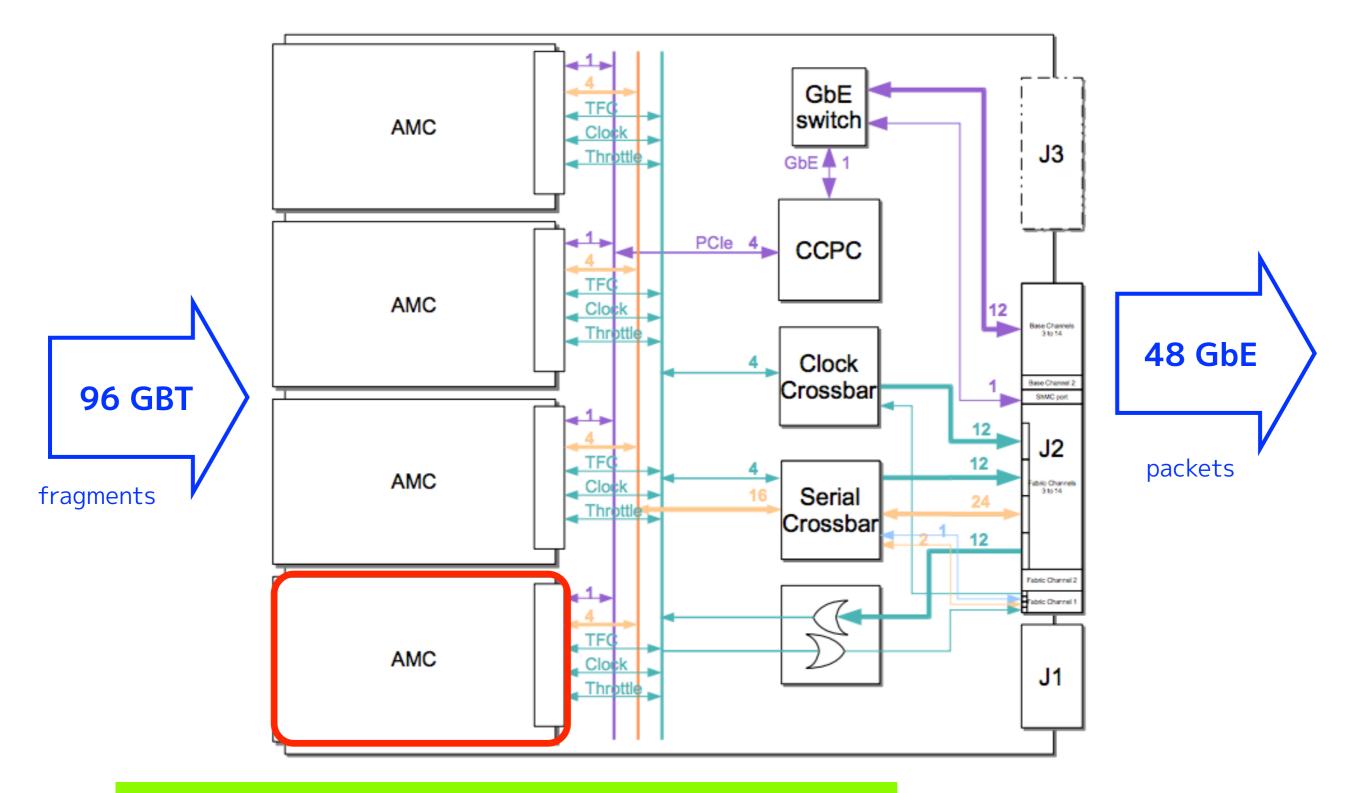

\* 110 boards for the entire LHCb system

\* common hardware for all the sub-system

(housed in ATCA carrier)

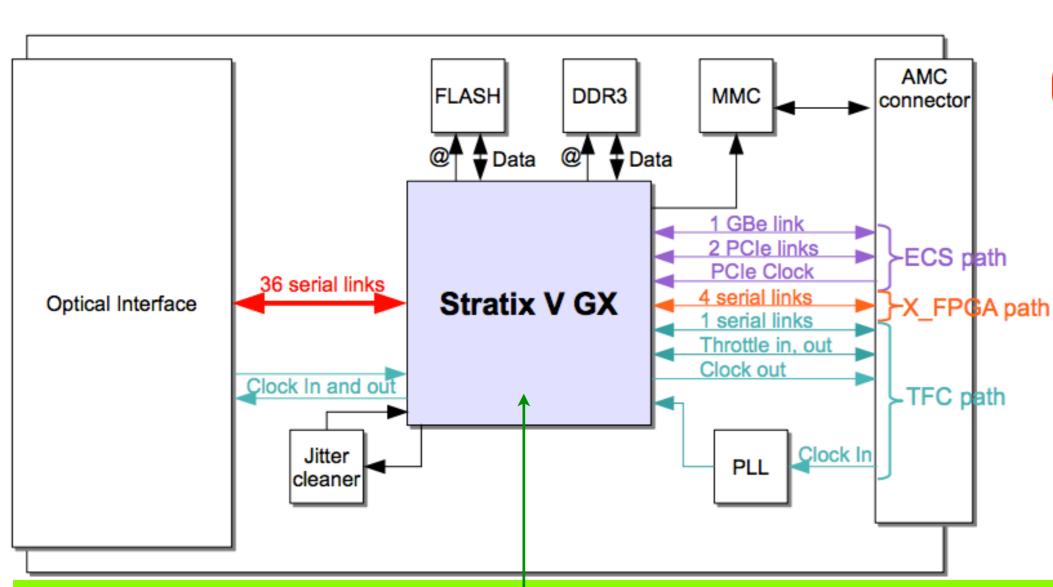

## LHCb – AMC (daughter b. of TELL40)

CCPC

Clock

Serial Crossba

D

AMC

AMC

(1) high density serial link is available

- $[IN] : FE \rightarrow TELL40$

- [ OUT ] : TELL40 → DAQ network

(2) The FPGA is powerful enough to implement **data processing** algorithm e.g. Zero-suppression , data formatting , ...

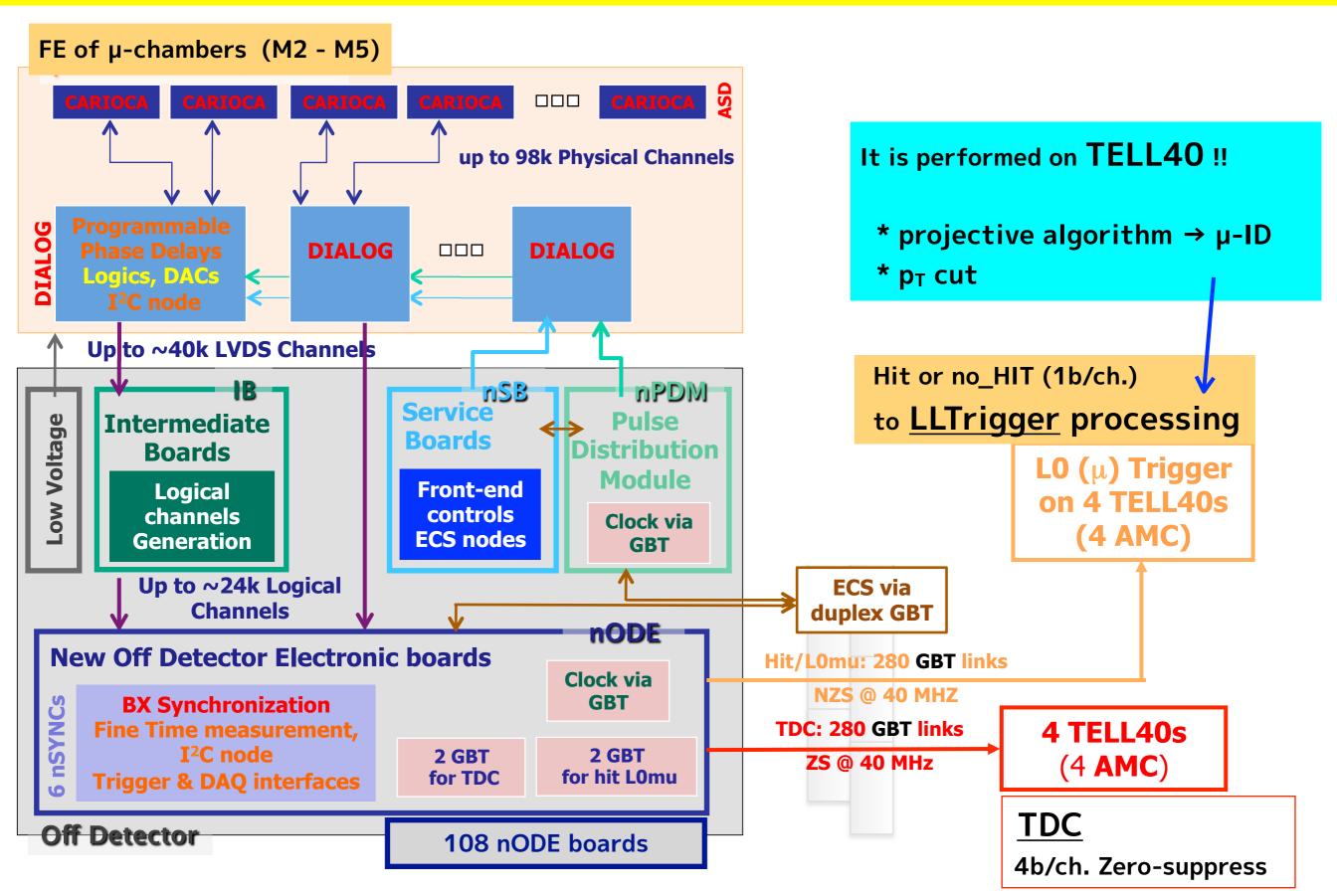

## LHCb - µ Readout & µ-LLT

#### 10

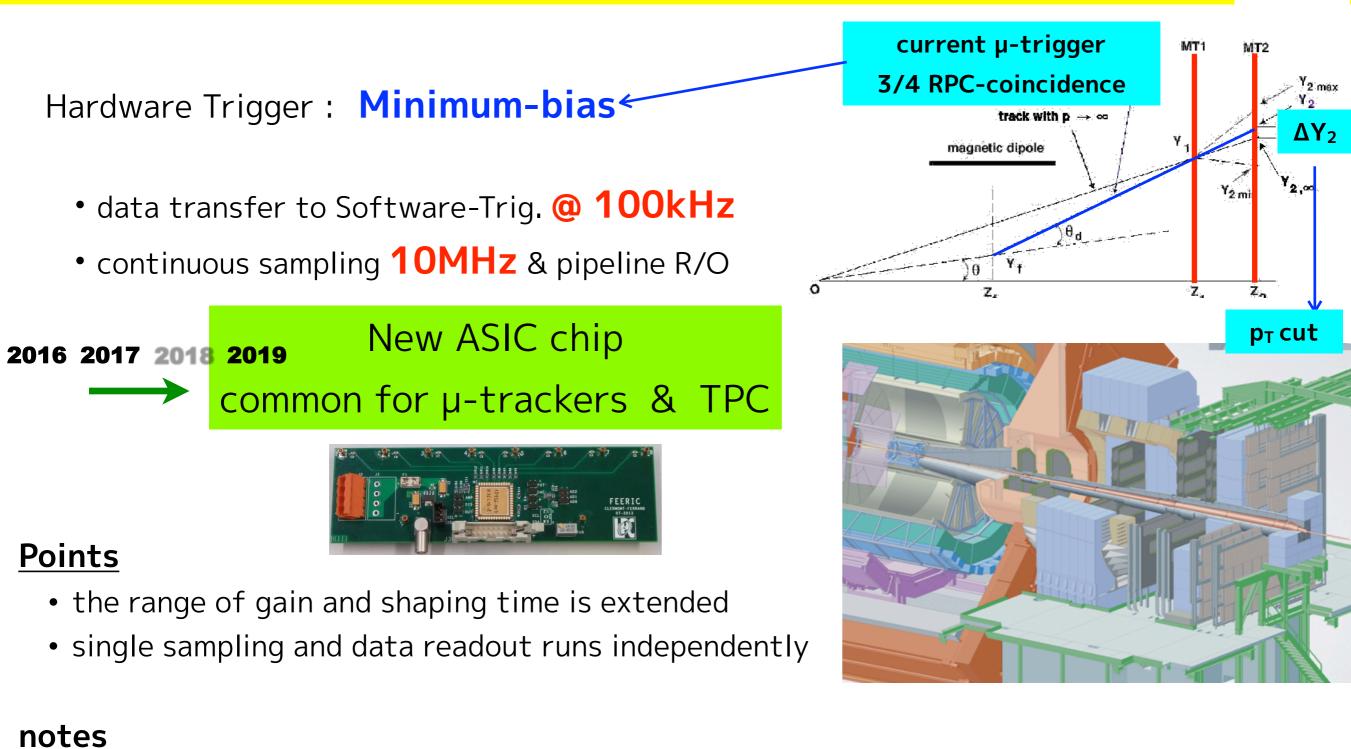

## ALICE µ-electronics @ HL-LHC

- The technology : TSMC 130nm for the ASIC.

- In total 17,000FE cards ( 1 FE Chip = 32ch. , 1FE Card = 2FE chips )

- Power consumption : 15 to 20mW/ch. ( x 1/4 w.r.t. the current chip )

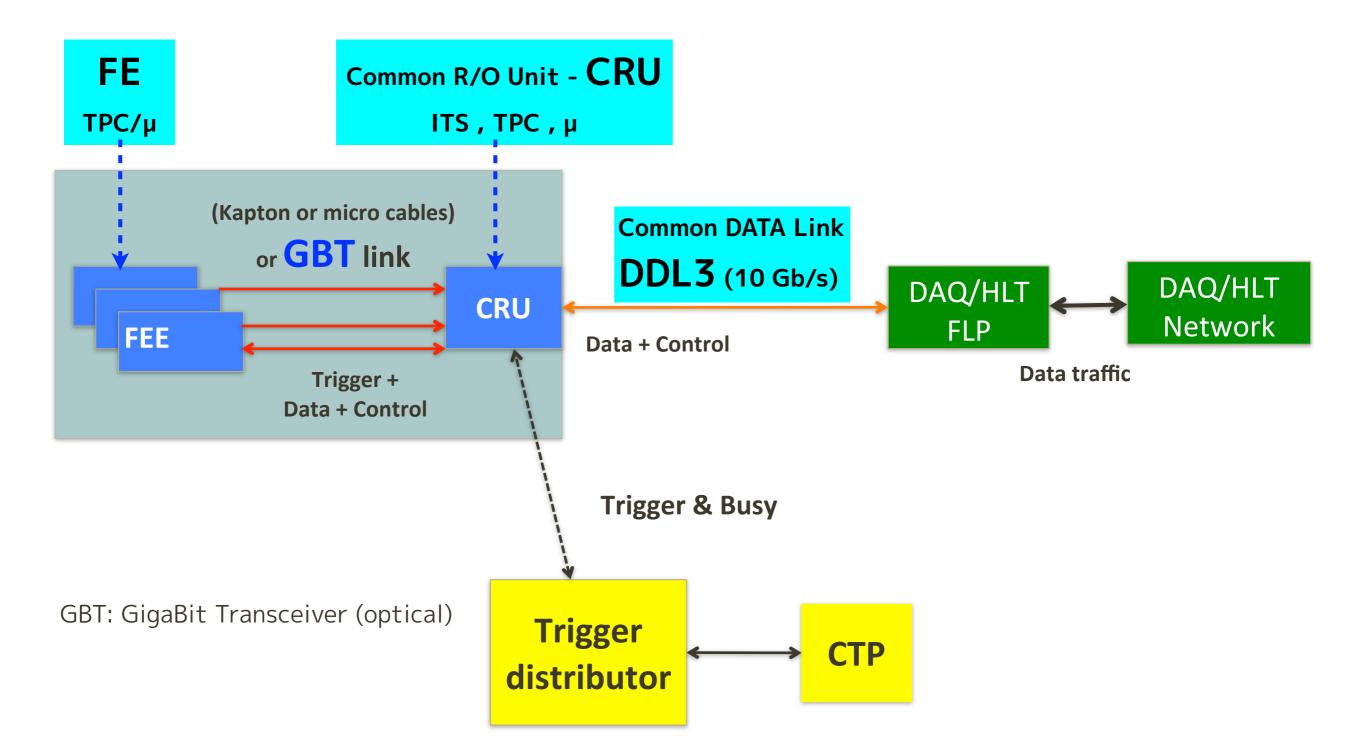

## µ-elec. ↔ common ALICE architecture

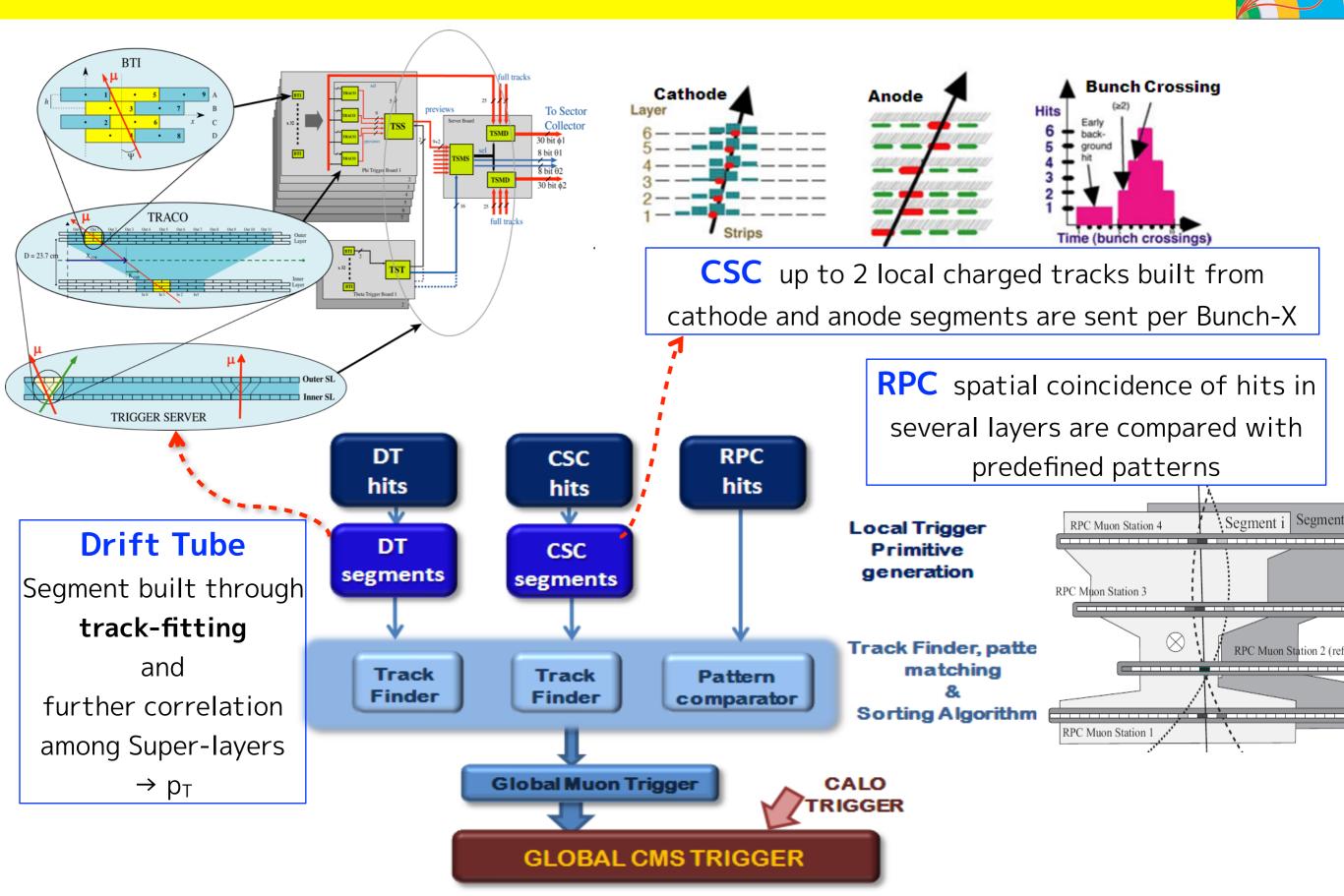

## (current) CMS µ-trigger system

#### 14

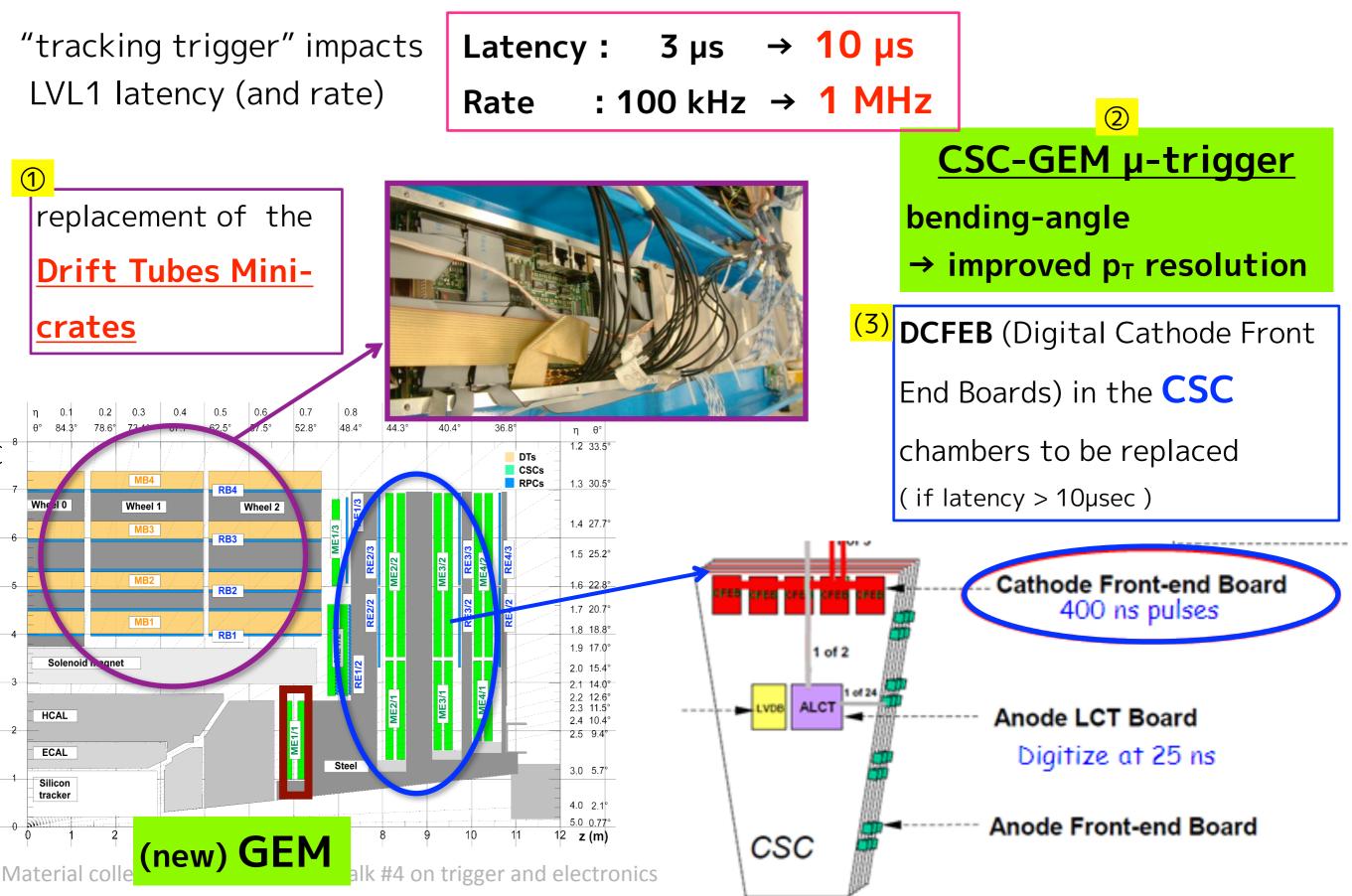

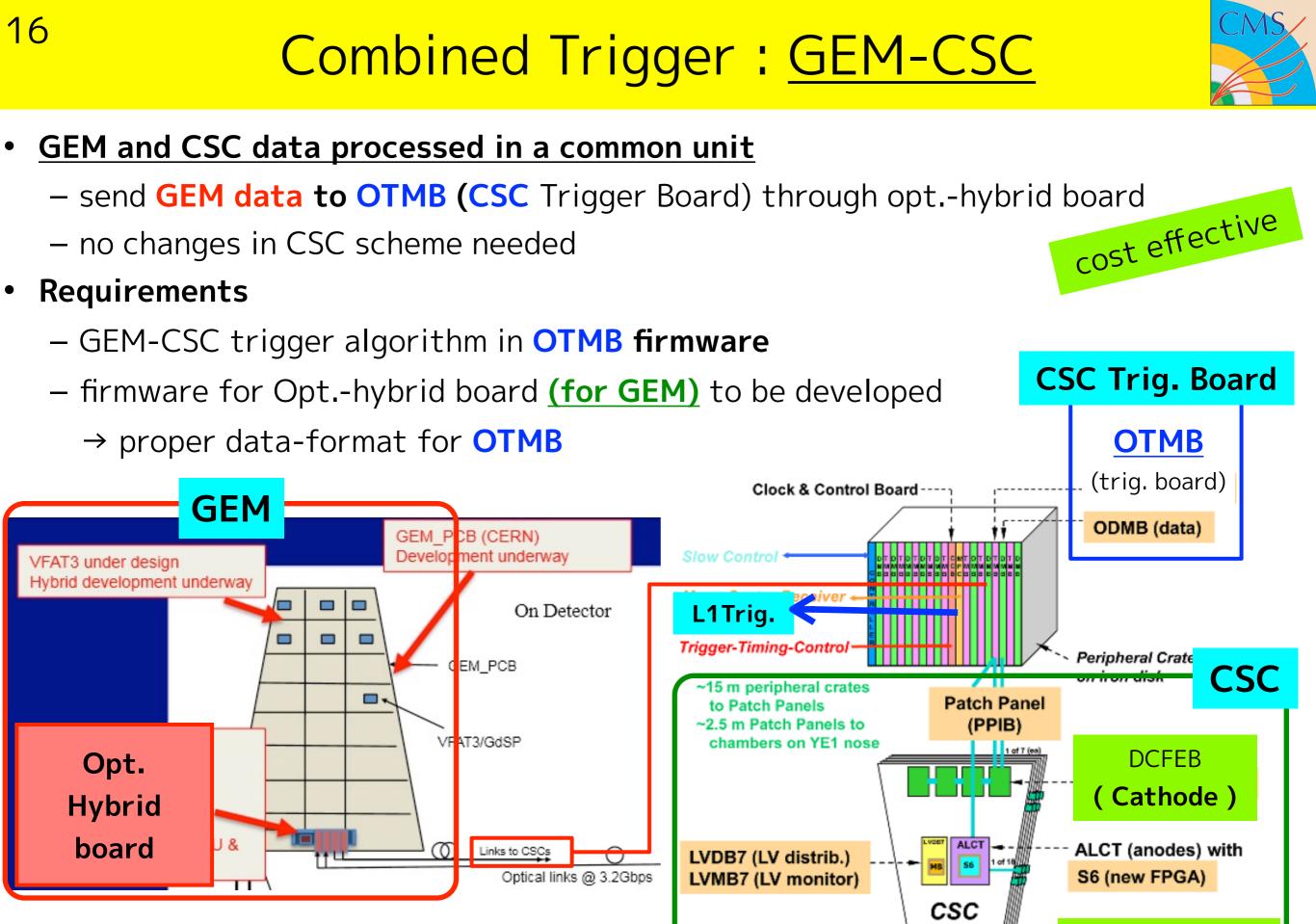

## Phase-2 µ-trigger / elec. upgrade

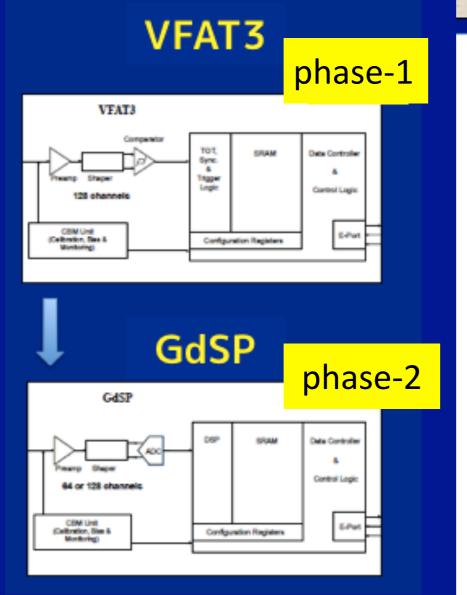

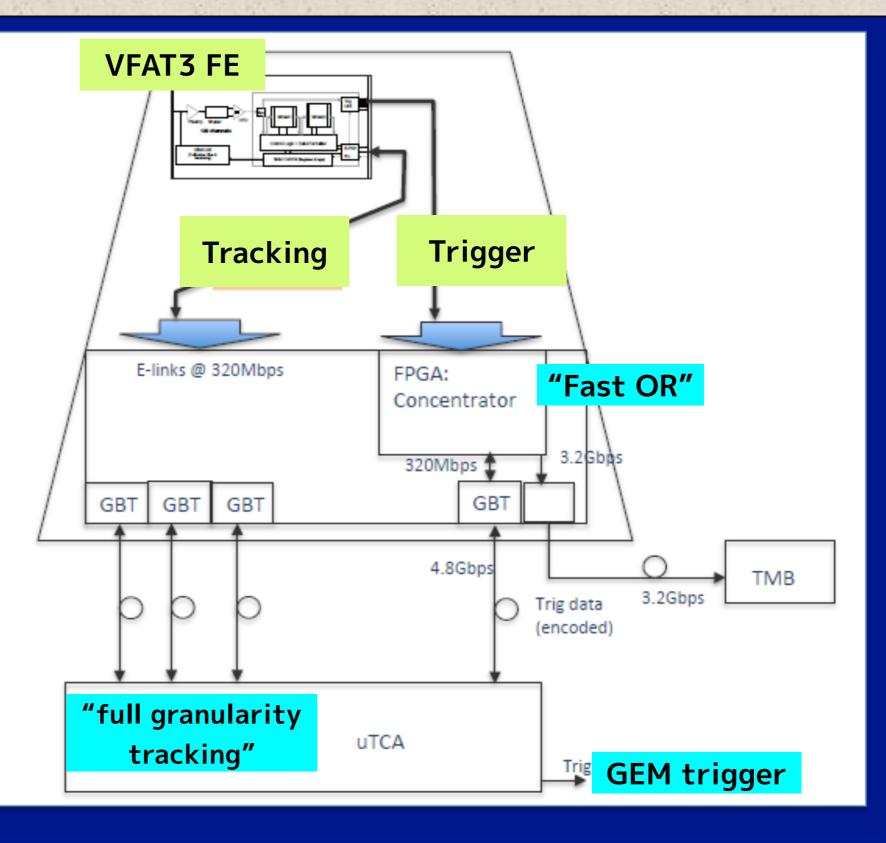

## The CMS GEM Electronics System

VFAT3 chosen as baseline for GEM (phase-1)

**GdSP** may be ideal for a number of **Phase-2 upgrades**

15

ALCT ( Anode )

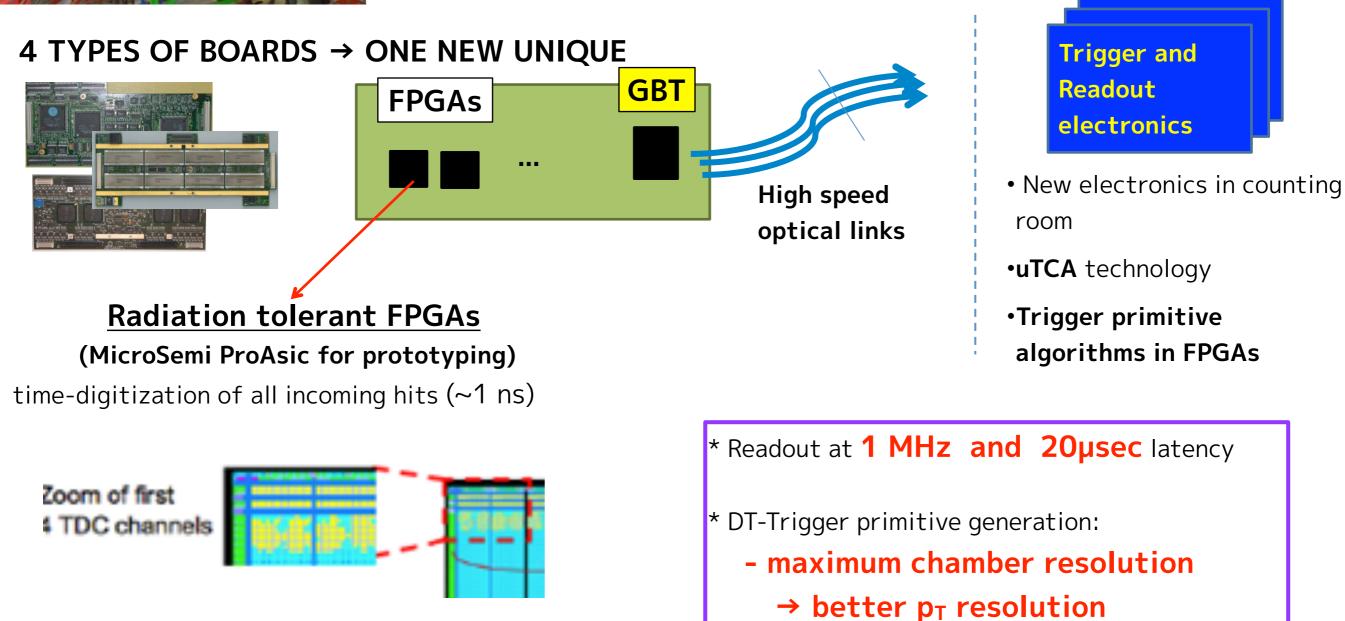

## Upgrade of DT on-chamber electronics

17

## Phase2 Mini-crates : DT

- more radiation tolerant / 1MHz readout / improve reliability / ...

- time digitization & Digital info. sent through high-speed optical link

R&D

started

Complexity is brought to the counting room

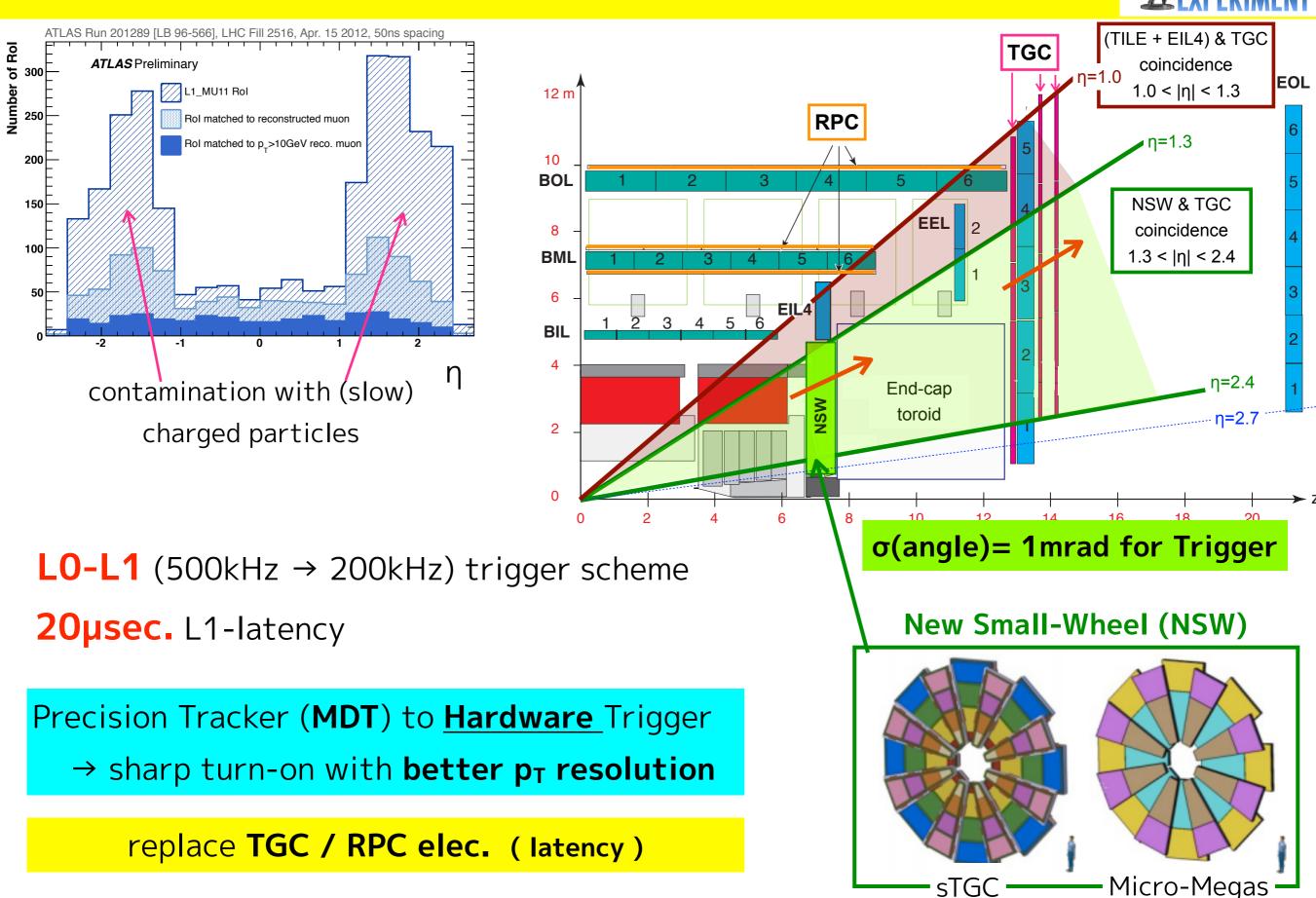

## ph.2 µ-upgrade - trigger & R/O

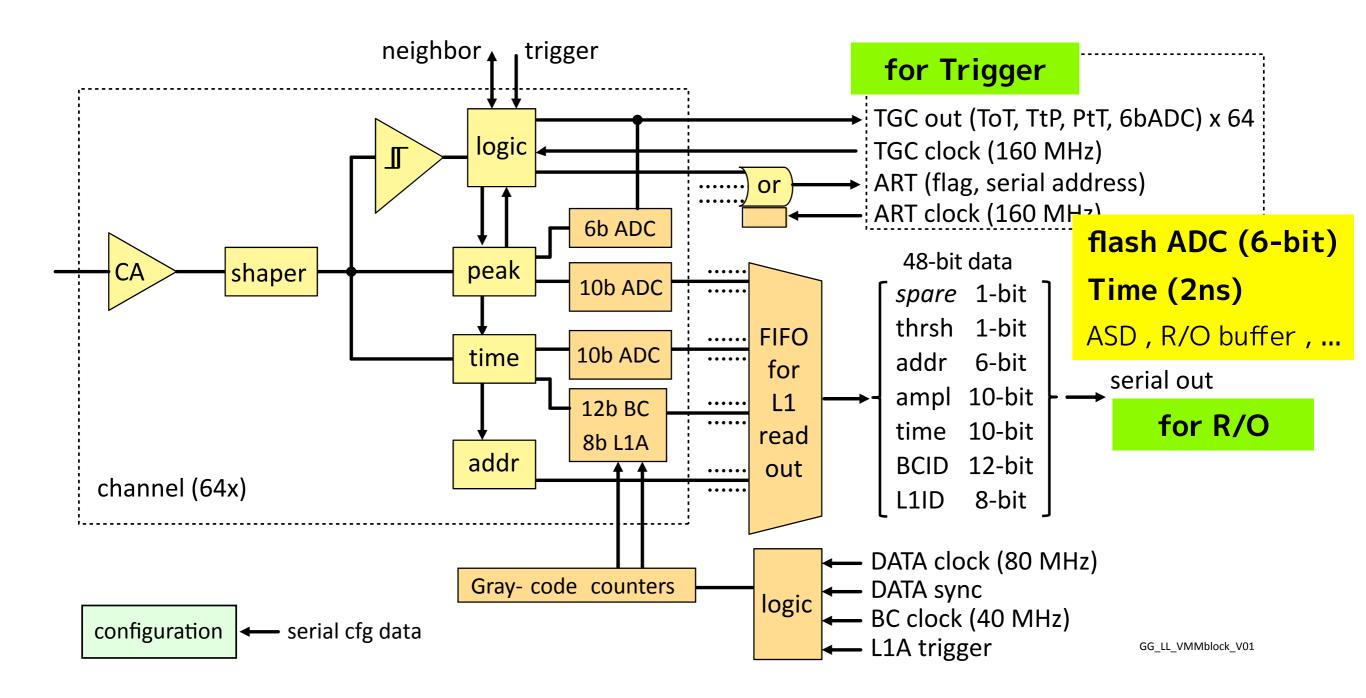

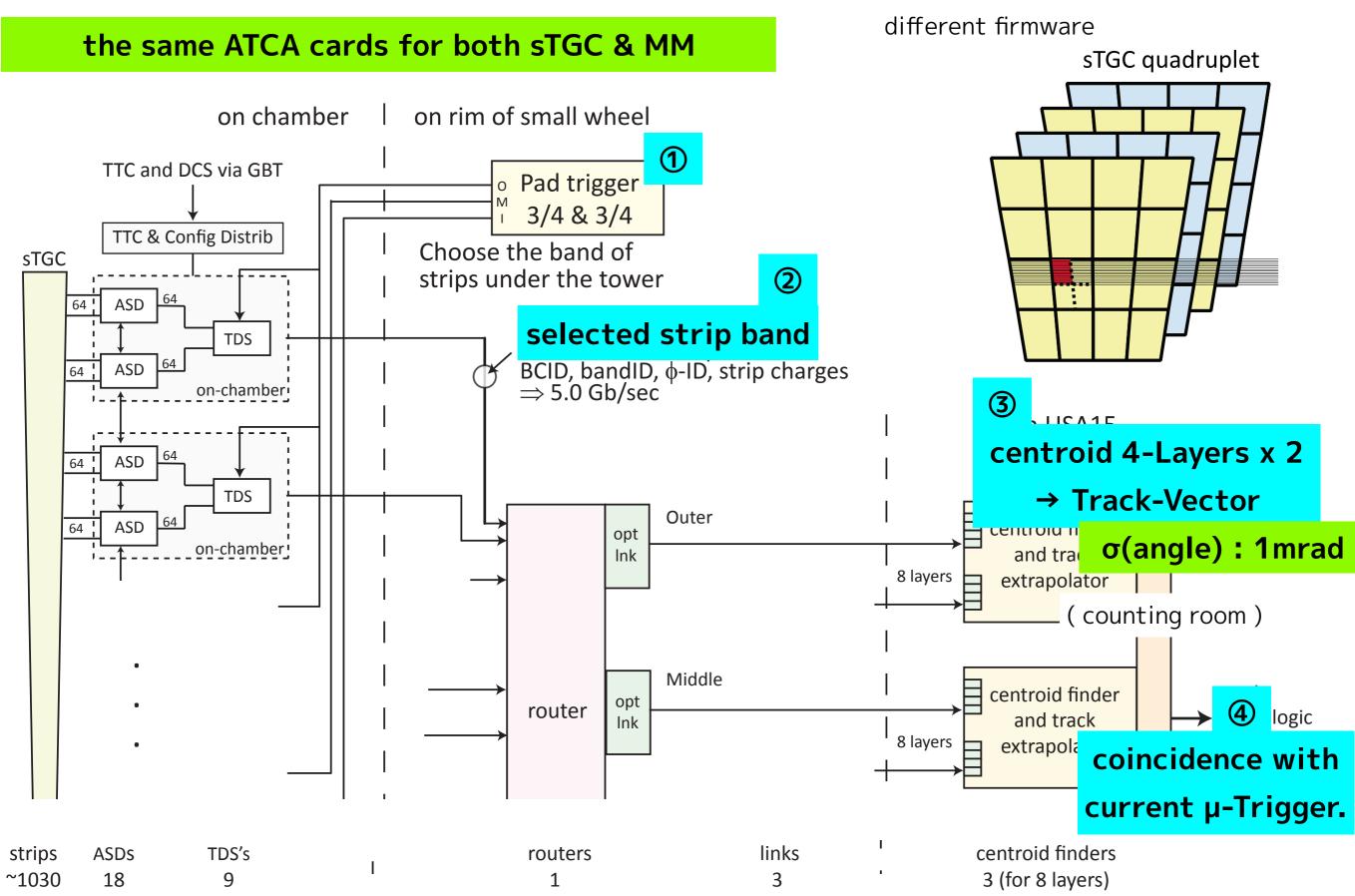

## New-SW : Front-End ASIC

#### **common ASIC** for sTGC & Micro-Megas : VMM2

64ch. per chip , 512mW/ch. , ~40k chips

### track-vector processor for trigger

21

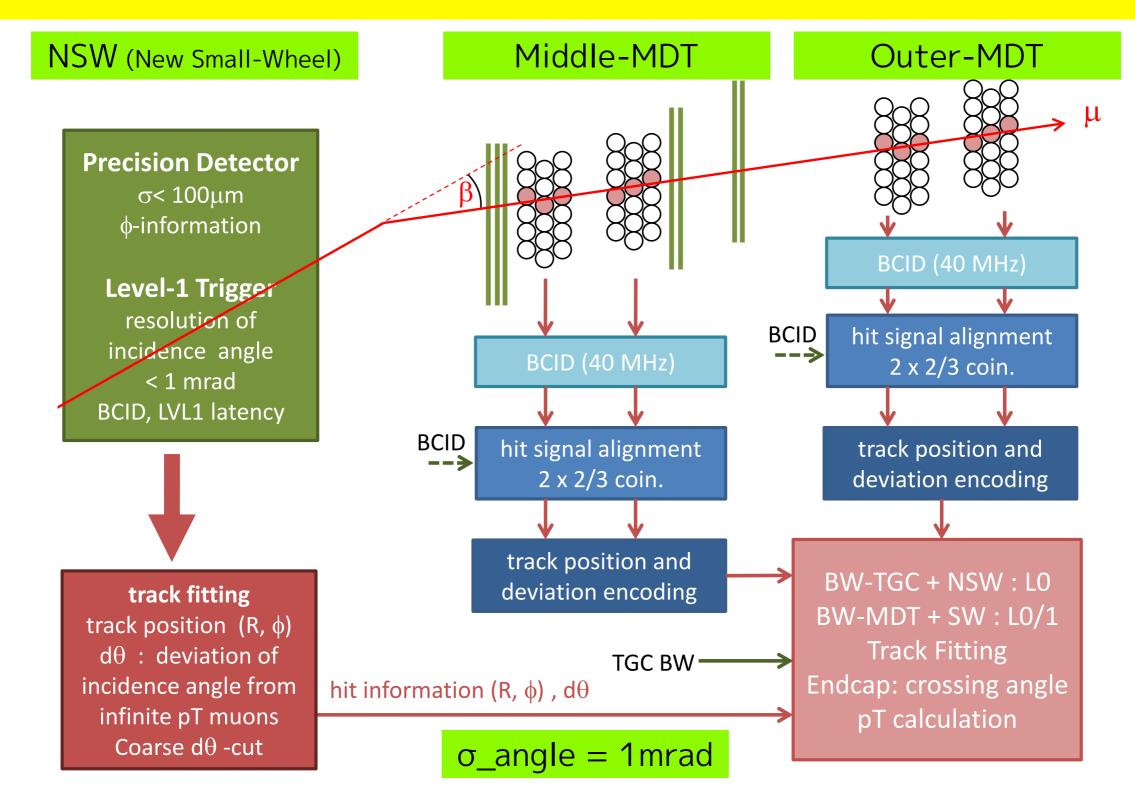

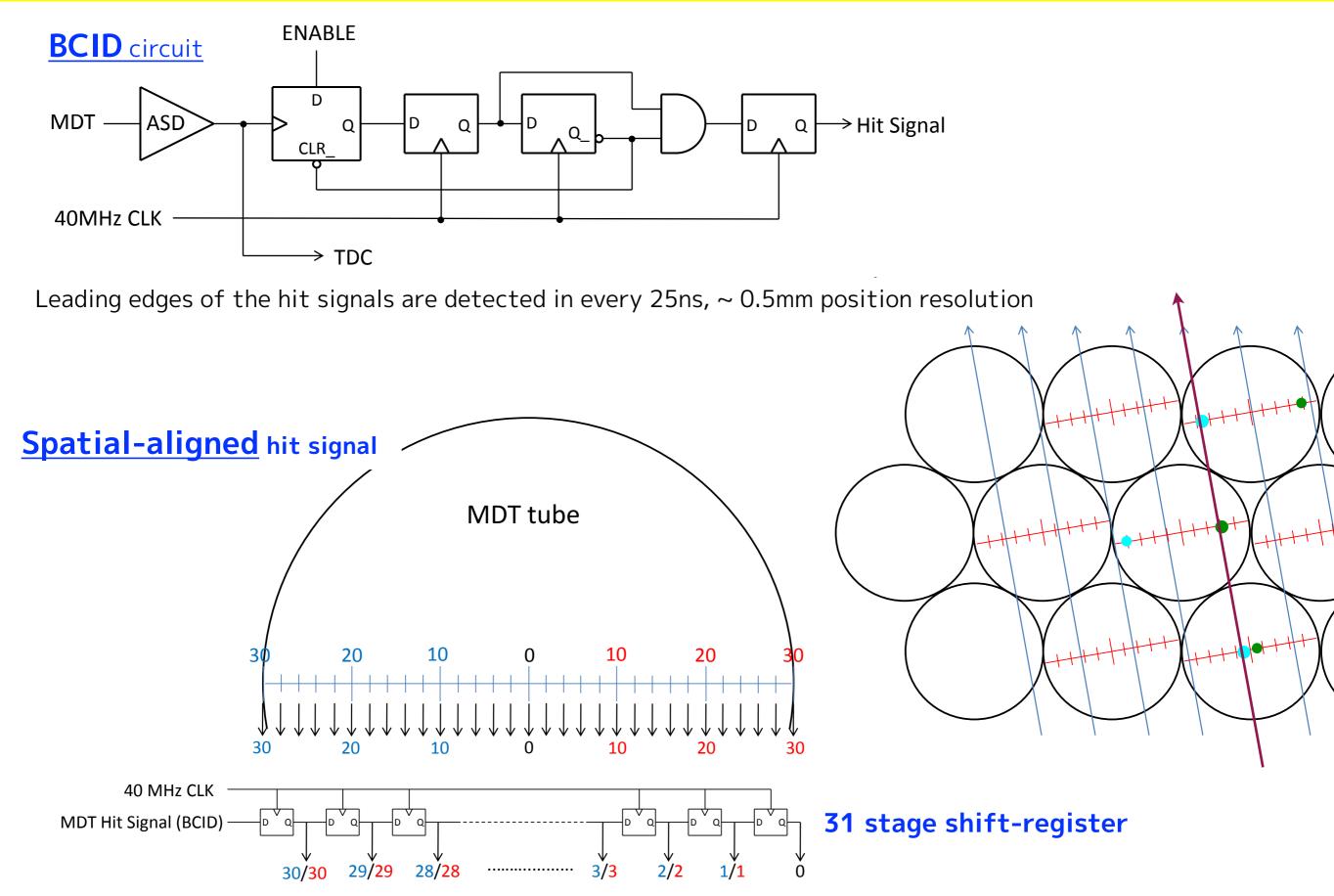

## ph.2 µ-trigger scheme : MDT as HW trig.

measure drift-time with a precision of LHC-clock (or 0.5 tick)

→ deduce angle at each 3-stations → p<sub>T</sub>

22

#### 23

## **Drift-Tube as Hardware-Trigger**

## **Summary**

#### <u>Concepts</u>

- common electronics across multi sub-systems

- as simple as possible in the pit, complexities brought to outside

#### <u>Technologies</u>

- high-speed optical links ( e.g. **GBT** )

- radiation hard Front-End ASICs

- FPGA with high-density serial links & performance

- ATCA ( or  $\mu\text{TCA}$  ) cards

#### high-rate readout

high-performance µ-trigger

# backup

#### [Detector systems]

#### (a) conceptual part

- High level motivation for upgrades: longevity

- Important performance requirements to achieve the HL-LHC physics program

#### (b) practical & technical part

- How to achieve to the expected performance

- Targeted R&D needs

- technology prospect (including cost considerations)

- ongoing activities & further actions

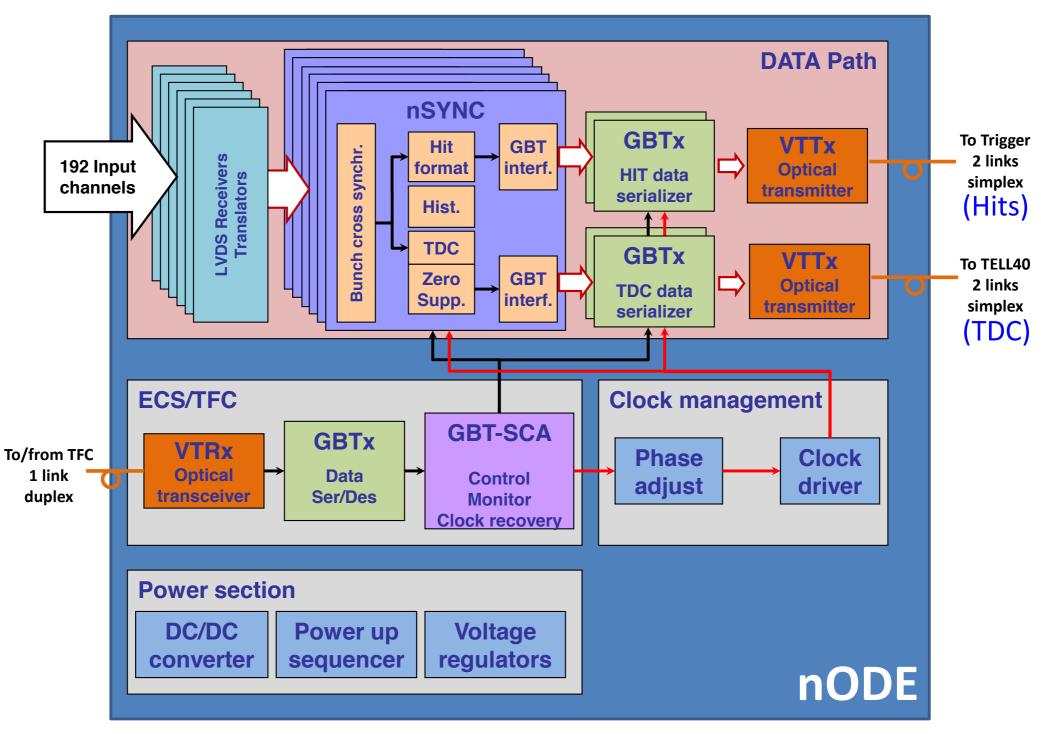

## <sup>27</sup> LHCb - nODE (new Off Detector Elec.)

I may skip this slide ... check with Alessandro

6 optical links required / nODE