#### Automatic inspection of SEE sensitivity in pixel microelectronics

<u>F. R. Palomo</u>, F. Márquez, F. Muñoz, M. A. Aguirre, L. Sanz(Universidad de Sevilla) M. Ullán (Instituto de Microelectrónica de Barcelona)

#### 23rd RD50 Workshop

13th-15th Nov 2013 CERN

#### Outline

- Introduction

- Motivation and goals

- SEE sensitivity analyzer

- Applied methodology and tool performance

- Case studies

- Conclusions and future work

Applied methodology

Tool performance

Case studies

Conclusions

#### Introduction

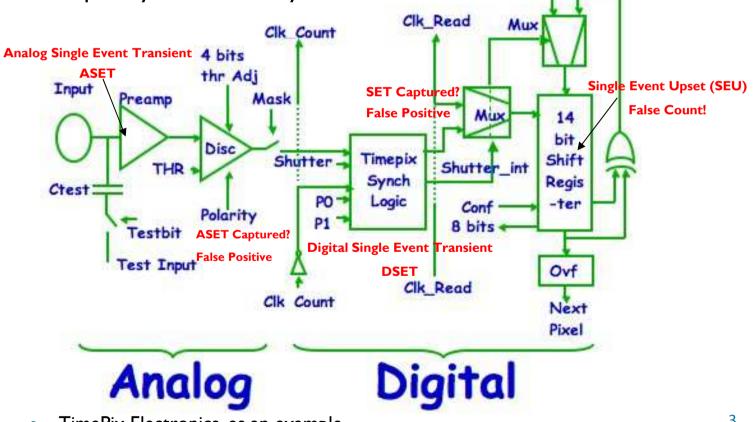

- Under the Silicon Detector we find the pixel electronics and it is sensitive to particle tracks too!

- As technologies shrinks, transient effects (SEE) can become critical

- Higher frequencies and lower dimensions  $\rightarrow$

- $\rightarrow$ Not only affects to digital, but also analog cells  $\rightarrow$

- $\rightarrow$  Complexity of error analysis increases

Previous

TimePix Electronics, as an example

- Applied methodology

- Tool performance Case studies Conclusions

#### Motivation

- Need for a rapid diagnose of vulnerabilities in previous stages of design → Radiation-hardened systems

- Dealing with SEE sensitivity analysis as the number of transistors increase is a challenging thread.

- Objective: an *automatic tool for SEE sensivity analysis*

- Provide a useful information about critical nodes of the circuit under test to the analog designer.

- Fast evaluation of complex analog circuits' vulnerabilities to radiation at transistor level.

- Elaborate a SEE sensitivity map of the circuits on test.

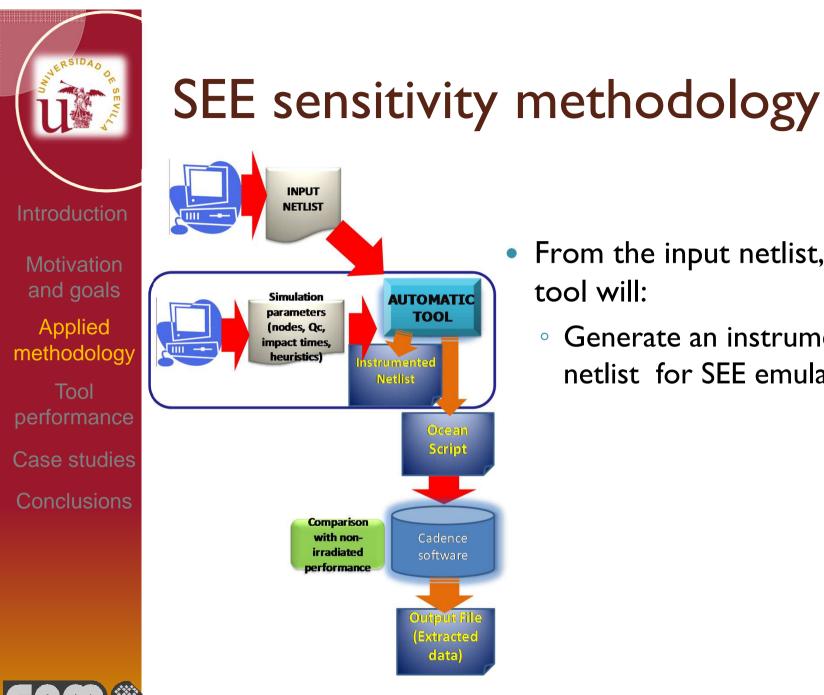

### SEE sensitivity methodology

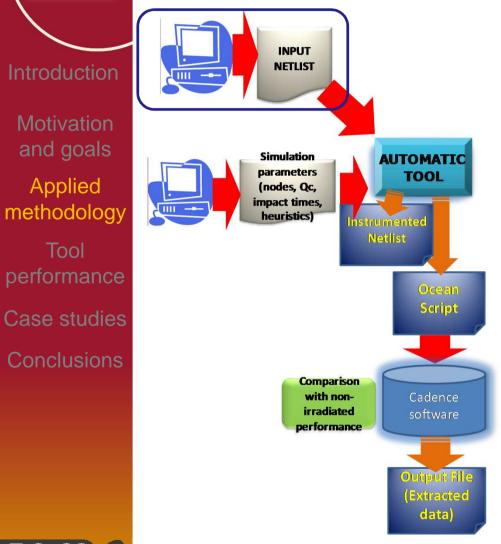

- Starting point: circuit definition by the designer.

- A Spectre netlist (extracted from simulation test-bench) is taken as an input.

CRSIDAD

- From the input netlist, the

- Generate an instrumented netlist for SEE emulation.

## SEE sensitivity methodology

- From the input netlist, the tool will:

- Generate an instrumented netlist for SEE emulation.

- Create a simulation script that automatically:

- Analyzes the SEE sensitivity of the analog circuit .

- Provides an output file with critical information.

Applied methodology

Tool performance Case studies

Conclusions

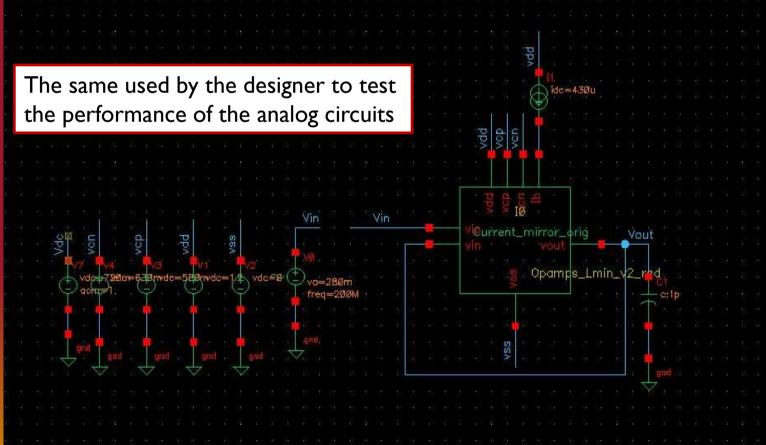

Starting point

- Input netlist

- extracted from the designer's test bench

## Starting point

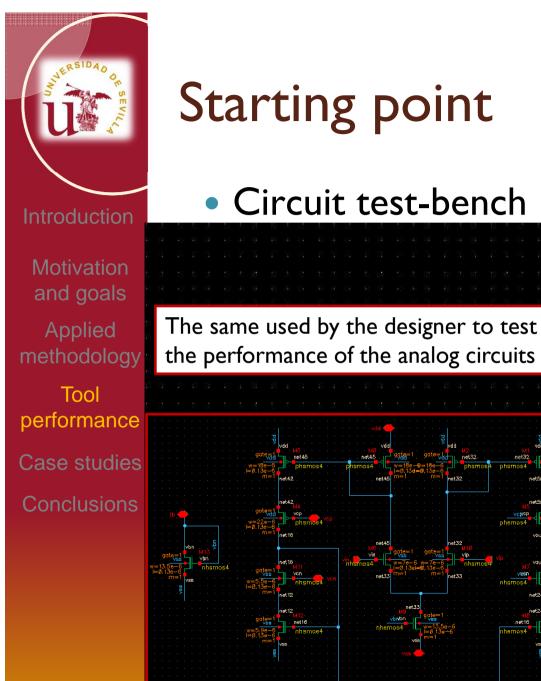

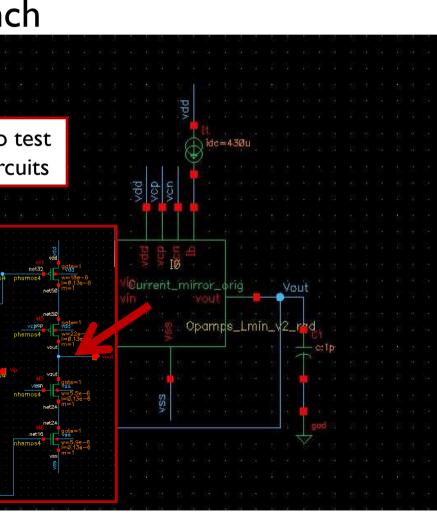

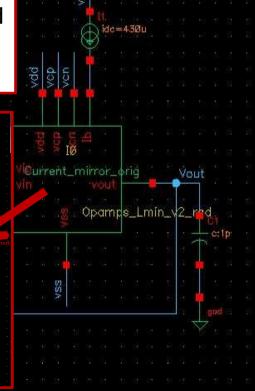

#### Circuit test-bench

## Starting point

Circuit test-bench

The only extra effort required is to place the SEE models (provided to the user)

Applied methodology

Tool performance Case studies Conclusions

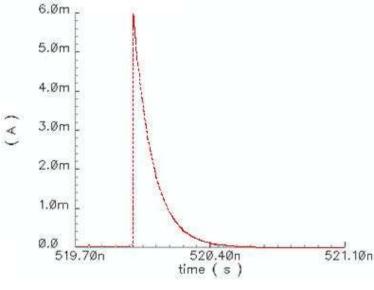

## Single Event Effects modeling

- SEE emulation based on charge injection models:

- Current sources with double exponential dynamics\*

- Use of configurable parameters (AHDL implementation)

$$T_{rad} = \frac{Q_c}{\tau_d - \tau_r} \left( e^{-\frac{\tau}{\tau_d}} - e^{-\frac{\tau}{\tau_r}} \right)$$

$$Q_c = \frac{\rho \cdot LET \cdot d}{3.6}$$

\***REF: G. Messenger,** "Collection of Charge on junction nodes from ion tracks", *IEEE Transactions on nuclear science*, vol.29, n° 6, Dec. 1982

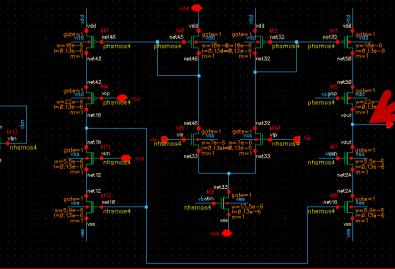

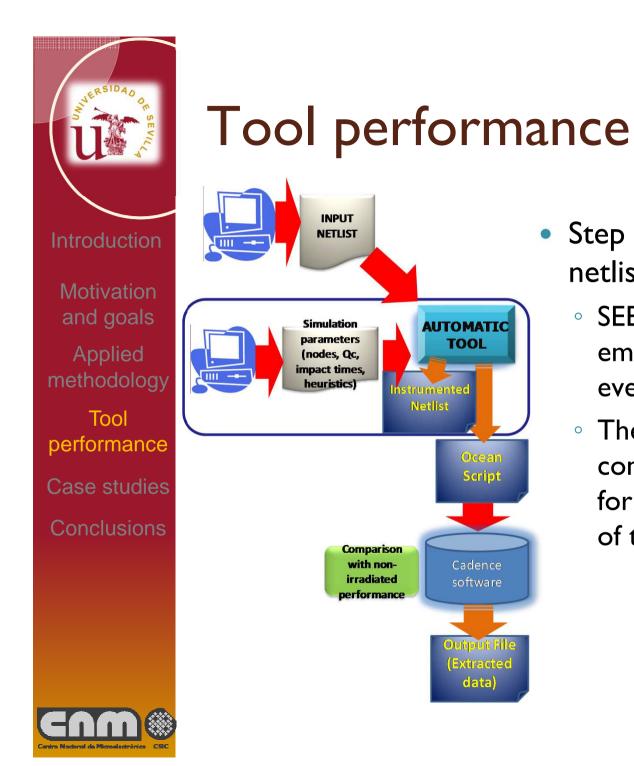

- Step I: a new instrumented netlist is generated.

- SEE models for impacts emulation are added to every possible target.

AUTOMATIC

TOOL

Script

Cadence

(Extracted data

instrumented

The user has to provide 0 configuration parameters for simulation and analysis of the circuits (step 2).

Applied methodology

Tool performance Case studies

Conclusions

### 2. Script generation

- Configuration parameters should be defined for automatic script generation:

- Impact nodes.

Applied methodology

Tool performance

Case studies

Conclusions

#### 2. Script generation

- Configuration parameters should be defined for automatic script generation:

- Impact nodes.

- SEE model parameters:

- -Injected charge

- -Impact times

- Outputs selected

Applied methodology

Tool performance Case studies

Conclusions

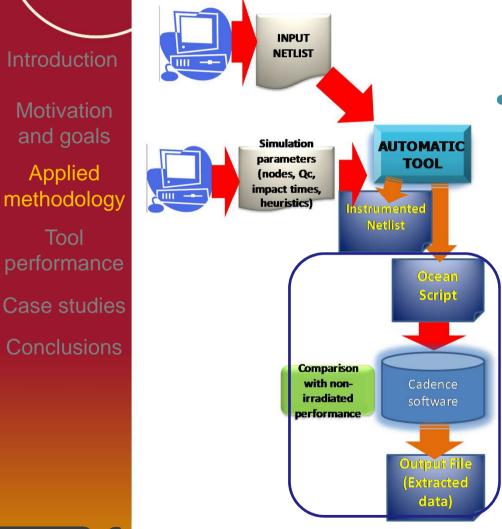

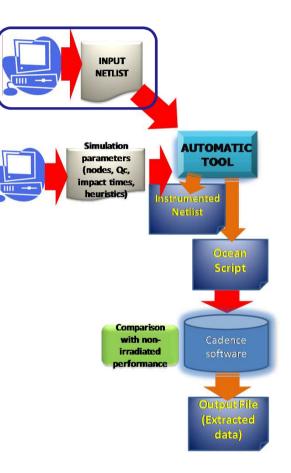

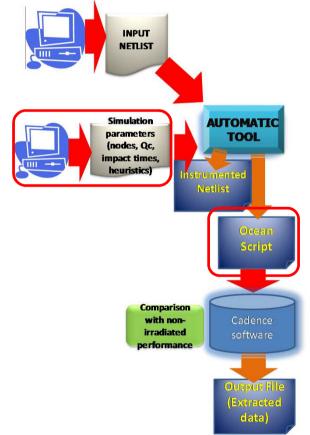

- INPUT NETLIST Simulation AUTOMATIC parameters TOOL (nodes, Qc, impact times, heuristics) Instrumented Script Comparison with non-Cadence irradiated performance Extracted data

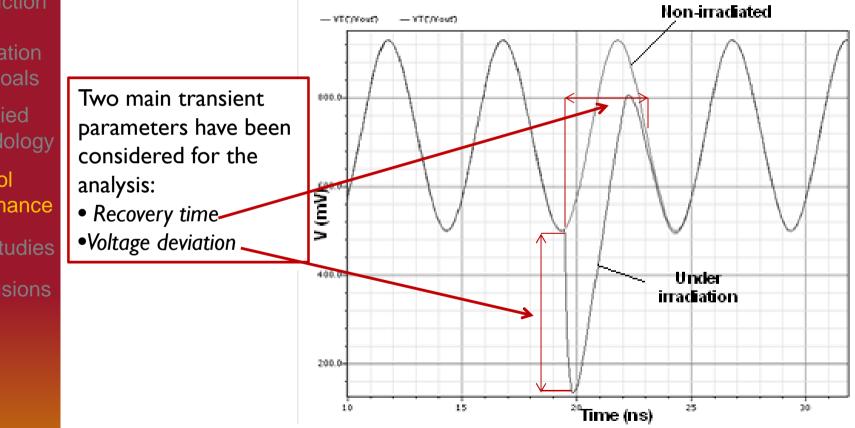

- A simulation script is automatically created.

- Compares an ideal (nonirradiated) output and the signal affected by injected SEEs.

- Results of the analysis of circuit's vulnerabilities are automatically analyzed and extracted into an output file.

Applied methodology

Tool performance

Case studies

Conclusions

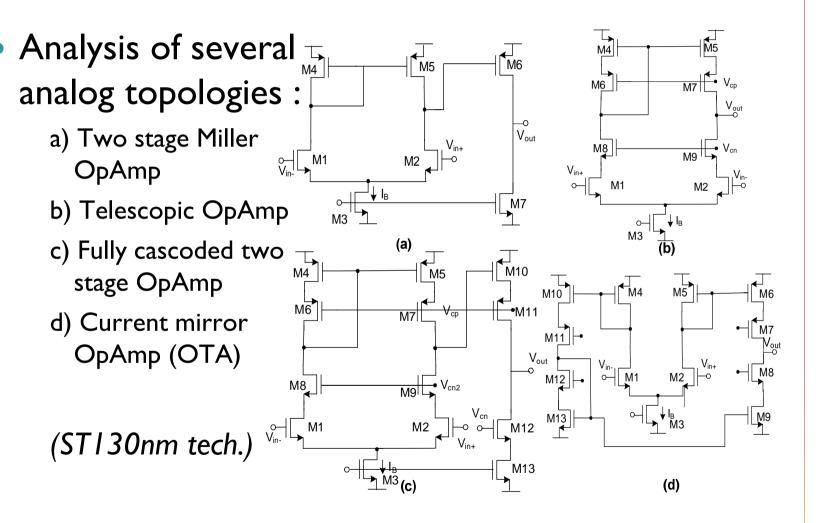

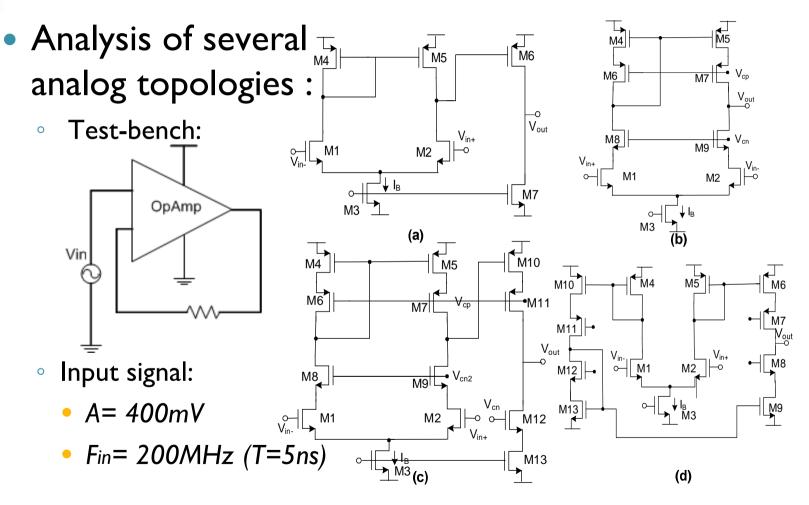

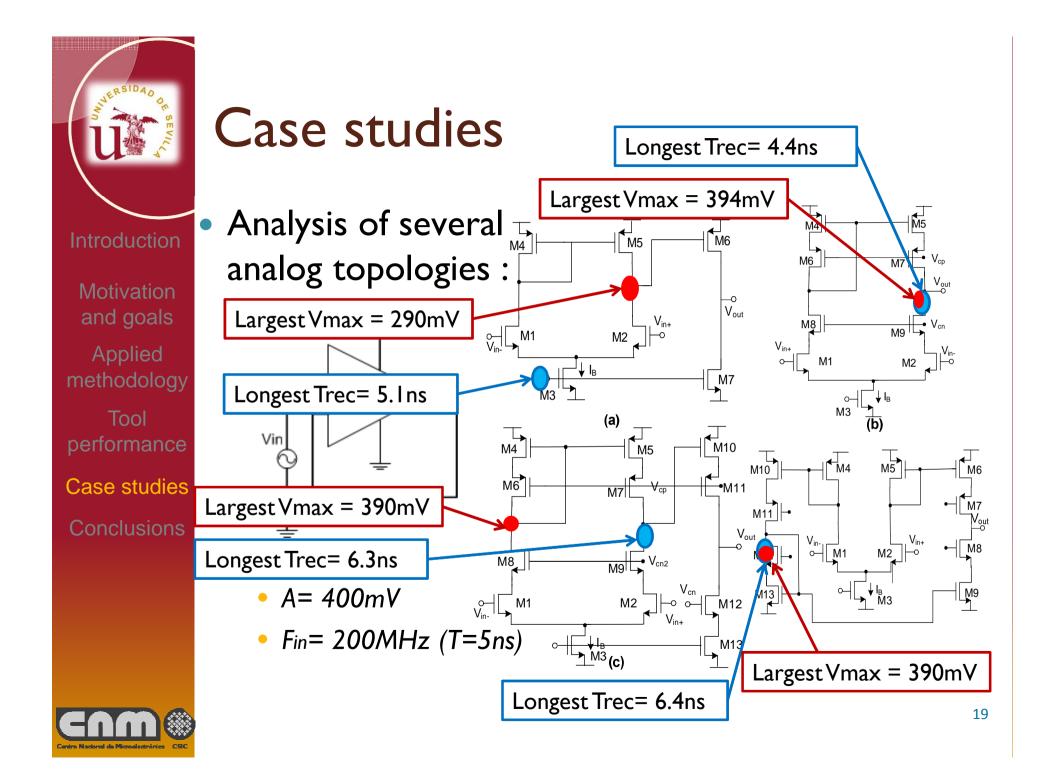

#### **Case studies**

Applied methodology

Tool performance Case studies

Conclusions

#### Case studies

Applied methodology

Tool performance Case studies

Conclusions

#### Heuristic analysis

Applied methodology

Tool performance Case studies Conclusions

#### = [= |×] Graph Window [43] File Edit Graph Axis Trace Marker Zoom Tools Help ⊜⊠#≣⊡⊞ø₽₽₽ Label Transient Analysis 'tran': time = $(0 \text{ s} \rightarrow 60 \text{ ns})$ -v("/I0/net32" ?result 'tran) -v("/Vout" ?result 'tran) - v("/10/net32" ?result 'tran) - v("/Vout" ?result 'tran) v("/I0/net32" ?result 'tran) - v("/Vout" ?result 'tran) v("/I0/net32" ?result 'tran) -v("/Vout" ?result 'tran) v("/I0/net32" ?result 'tran) - v("/Vout" ?result 'tran) v("/I0/net32" ?result 'tran) -v("/Vout" ?result 'tran) 1.1-1.0-.8 ŝ .7. .6-.5 .4 .3-10 20 40 50 30 60 0 time (ns) cadence

Transient simulations

#### Generated output database

Out /10/ /νοι Motivation /10/ and goals /νοι Applied /10/1 methodology /νοι Tool /10/ performance /νοι /10/ Case studies /νοι Conclusions /10/ /νοι

| tput   | Impact | Qc       | Timp     | Trec      | Vmax     |

|--------|--------|----------|----------|-----------|----------|

| /net32 | 10_M5  | 5,00E-13 | 1,00E-08 | 5.100.000 | 0.109233 |

| out    | 10_M5  | 5,00E-13 | 1,00E-08 | 6.400.000 | 0.225535 |

| /net32 | 10_M5  | 5,00E-13 | 2,00E-08 | 5.100.000 | 0.109186 |

| out    | 10_M5  | 5,00E-13 | 2,00E-08 | 6.400.000 | 0.225493 |

| /net32 | 10_M7  | 5,00E-13 | 1,3e-08  | 2.300.000 | 0.426629 |

| out    | 10_M7  | 5,00E-13 | 1,3e-08  | 3.600.000 | 0.183520 |

| /net32 | I0_M7  | 5,00E-13 | 2,6e-08  | 2.300.000 | 0.370461 |

| out    | 10_M7  | 5,00E-13 | 2,6e-08  | 3.000.000 | 0.147083 |

| /net32 | I0_M10 | 2,50E-13 | 1,00E-08 | 2.800.000 | 0.205726 |

| out    | I0_M10 | 2,50E-13 | 1,00E-08 | 3.900.000 | 0.186725 |

| /net32 | I0_M10 | 2,50E-13 | 2.0e-08  | 3.300.000 | 0.143872 |

| out    | I0_M10 | 2,50E-13 | 2.0e-08  | 4.600.000 | 0.231184 |

|        | •      |          |          |           |          |

Tool

#### Generated output database

Output /I0/net3 /Vout Motivation /I0/net3 and goals /Vout Applied /I0/net3 methodology /Vout /I0/net3 performance /Vout /I0/net3 Case studies /Vout Conclusions /I0/net3 /Vout

|    | Impact | Qc       |

|----|--------|----------|

| 32 | I0_M5  | 5,00E-13 |

|    | I0_M5  | 5,00E-13 |

| 32 | I0_M5  | 5,00E-13 |

|    | I0_M5  | 5,00E-13 |

| 32 | I0_M7  | 5,00E-13 |

|    | I0_M7  | 5,00E-13 |

| 32 | I0_M7  | 5,00E-13 |

|    | I0_M7  | 5,00E-13 |

| 32 | I0_M10 | 2,50E-13 |

|    | I0_M10 | 2,50E-13 |

| 32 | I0_M10 | 2,50E-13 |

|    | I0_M10 | 2,50E-13 |

|    |        |          |

| Timp     |

|----------|

| 1,00E-08 |

| 1,00E-08 |

| 2,00E-08 |

| 2,00E-08 |

| 1,3e-08  |

| 1,3e-08  |

| 2,6e-08  |

| 2,6e-08  |

| 1,00E-08 |

| 1,00E-08 |

| 2.0e-08  |

| 2.0e-08  |

Trec

Vmax 5.100.000 0.109233 6.400.000 0.225535 5.100.000 0.109186 6.400.000 0.225493 2.300.000 0.426629 3.600.000 0.183520 2.300.000 0.370461 3.000.000 0.147083 0.205726 2.800.000 3.900.000 0.186725 0.143872 3.300.000 4.600.000 0.231184

Applied methodology

Tool performance

Case studies

Conclusions

Applied methodology

Tool performance

Case studies

area

Conclusions

#### Future work

• Objective : create a SEE sensitivity map

Applied methodology Tool performance

. Case studies

Conclusions

# Future work

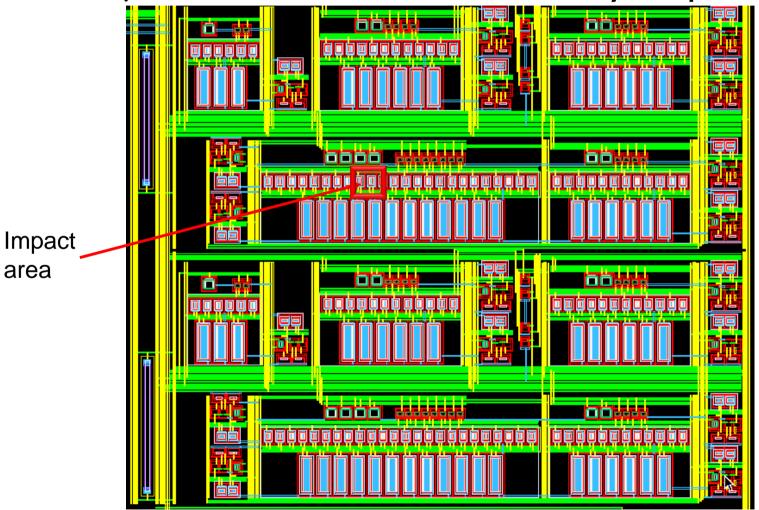

• Objective : create a SEE sensitivity map

Future work

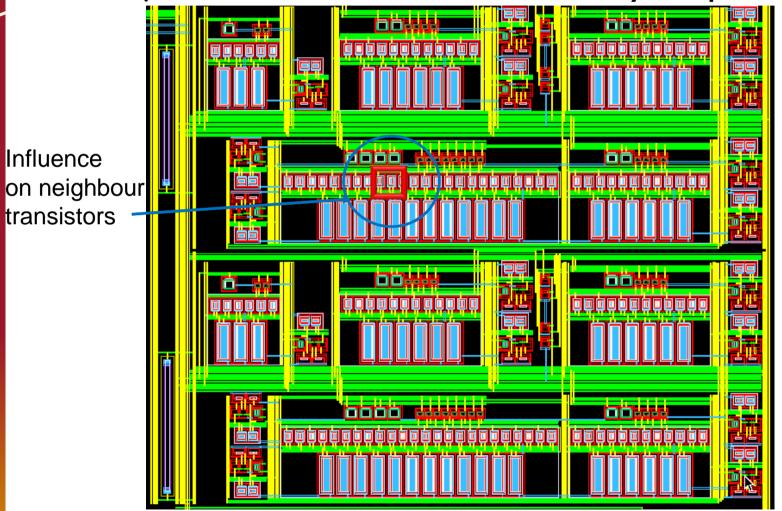

• Objective : create a SEE sensitivity map

Motivation and goals

Applied methodology

Tool performance

Case studies

Conclusions

Transistors inside an influence area should be taken into consideration for SEE emulation

Applied methodology

Tool performance

Case studies

Conclusions

## Conclusions and future work

- A preliminary tool for automatic inspection of SEE in analog schemes has been developed.

- Allows a rapid analysis of critical nodes at schematic level.

- Technology independent.

- Future work

- Experimental verification of results.

- Implementation of alternative SEE models.

- Extension of the analysis to layout level.

Applied methodology

Tool performance Case studies

Conclusions

Future work

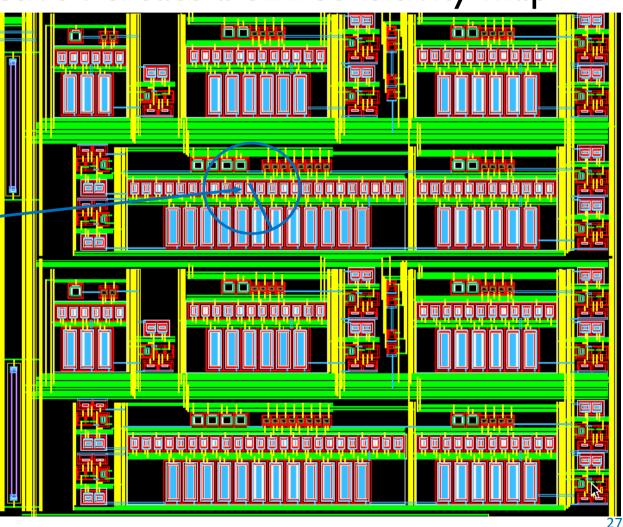

- Objective : create a SEE sensitivity map

- Several transistors can be affected by an impact

- Need of incorporing layout information to simulations

- $^{\circ}$  Use of geometrical criteria to define the test benchs ightarrow

- $\rightarrow$ Emulation of impacts influence on neighbour transistors

## Thanks for your attention

Contact: F. Rogelio Palomo (*rogelio@gte.esi.us.es*<sup>1</sup>)

Team:

Fernando Muñoz<sup>1</sup> Fernando J. Márquez<sup>1</sup> Miguel A. Aguirre<sup>1</sup> Luis Sanz<sup>1</sup> Miguel Ullán<sup>2</sup>

<sup>1</sup> Universidad de Sevilla <sup>2</sup> Instituto de Microelectrónica de Barcelona