## Pulsed power for a CLIC vertex detector

Cristian Alejandro Fuentes Rojas, PH-ESE-FE, CERN

#### Outline

CLIC, CLIC detector and Vertex barrel Restrictions for powering Power consumption @ Vertex Barrel Power pulsing and proposed power scheme Lab prototype Measurements and results Conclusions

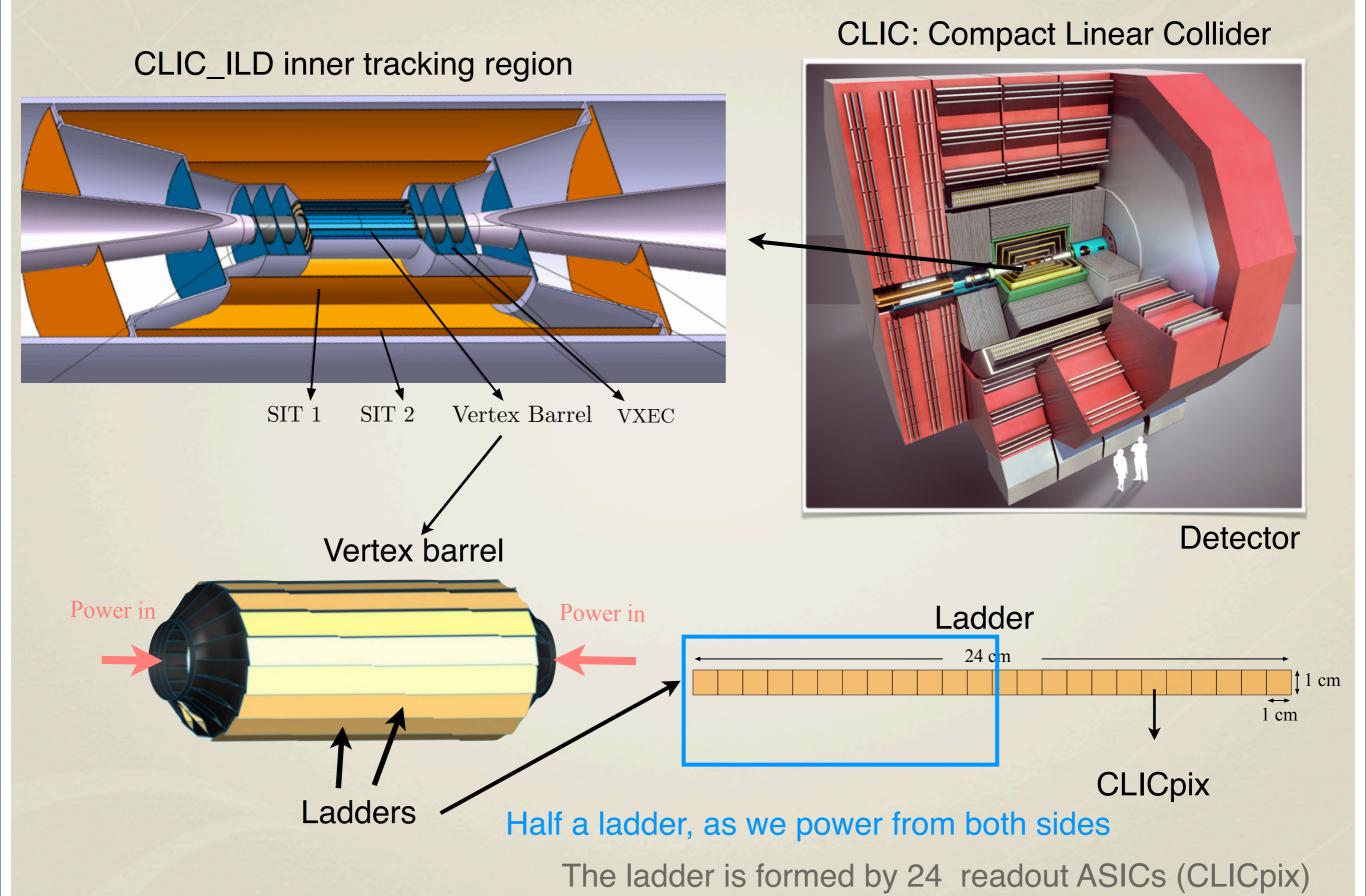

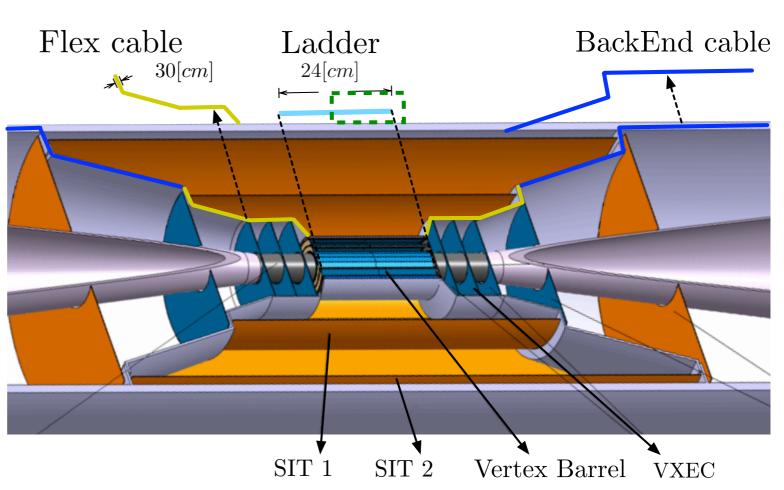

## CLIC detector, Vertex barrel, ladder & CLICpix

## Restrictions for powering

- 1) Material Budget:  $< 0.2\% X_0$  for a detection layer, from which 0.1  $\% X_0$  is already taken by the silicon sensor + readout chip. (100  $\mu$ m of silicon). This leaves, therefore, less than 0.1 $\% X_0$  for cooling, powering and mechanical structures.

- 2) Low power consumption: < 50 mW/cm<sup>2</sup> in the sensor area, as the heat-removal solution is based on air-cooling to reduce mass.

- 3) High magnetic Field: 4 to 5 [Tesla] restricting the use of ferromagnetic material.

#### extra challenge for analog electronics

4) Regulation: within 5% (60 mV) on the ASIC during the acquisition time in order to have a correct ToT measurement. (CLICPIX specifications).

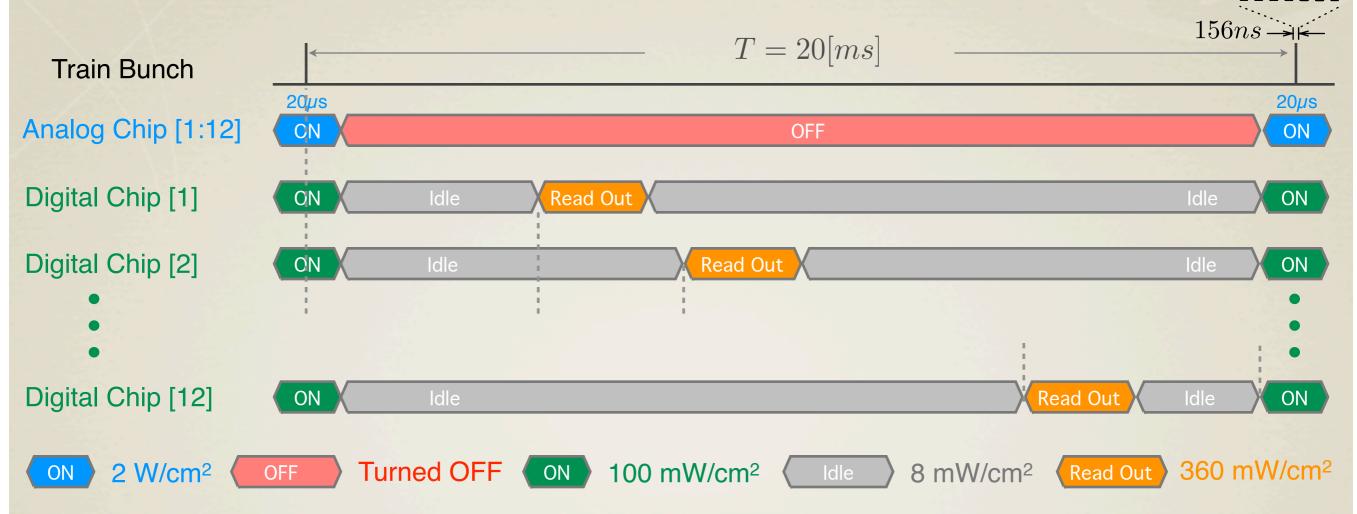

## Power consumption of Half a Ladder 312 × 500ps

- → Analog electronics can be turned OFF (power pulsing) to reduce the average power consumption (2m W/cm² instead of 2 W/cm² if it was ON all the time)

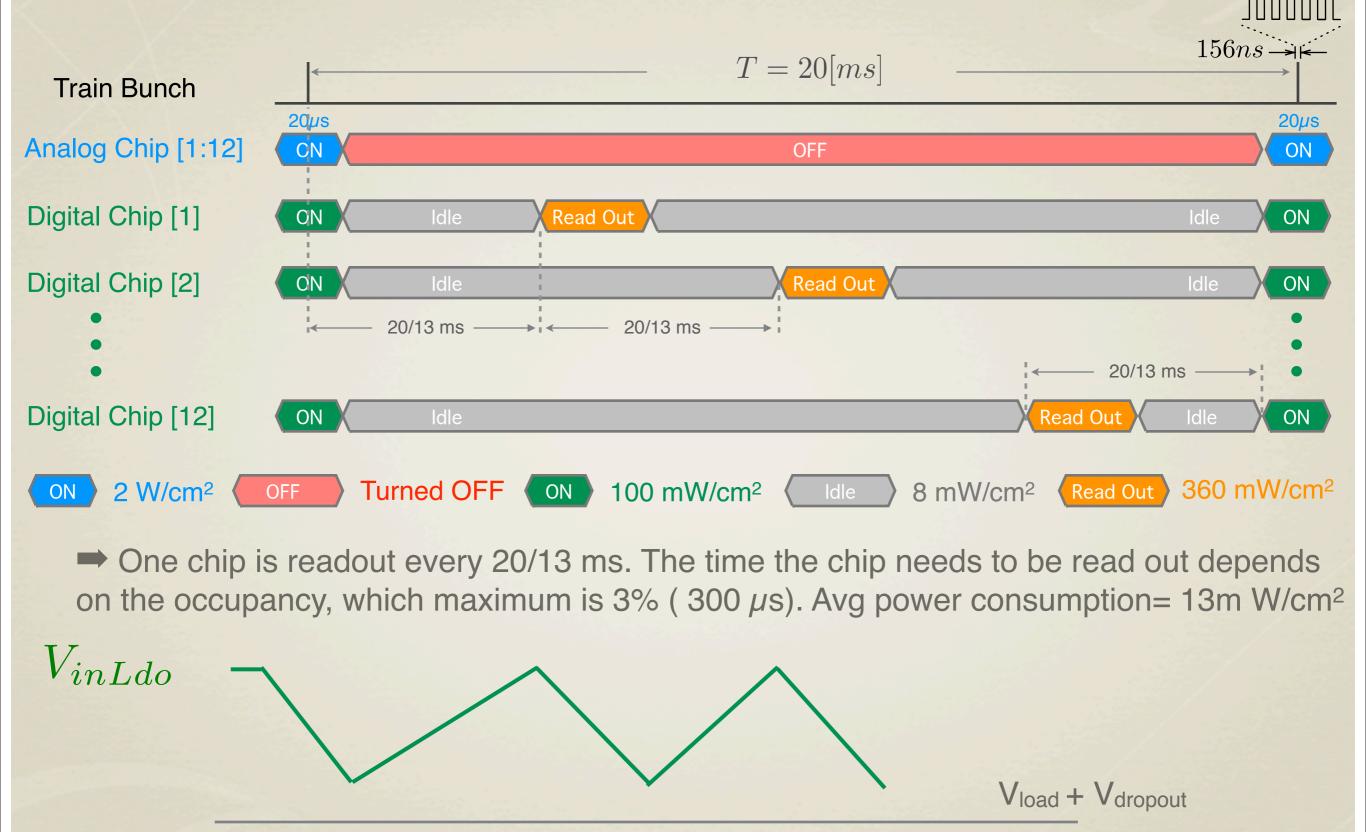

- $\rightarrow$  One chip is readout at a time. The time the chip needs to be read out depends on the occupancy, which maximum is 3% ( 300  $\mu$ s). Avg power consumption= 13m W/cm<sup>2</sup>

- → Analog voltage is 1.2V while the digital is expected to be 1V.

Analog and Digital will be powered separately. In that way, their powering schemes could be optimized independently to achieve the requirements from previous slide.

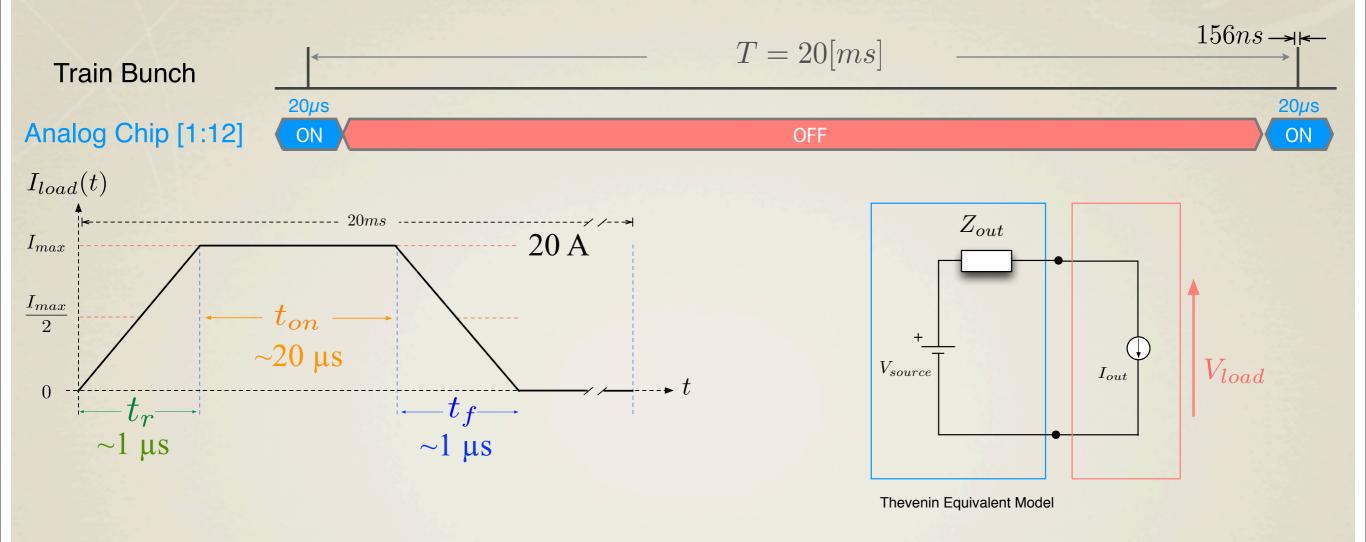

# Powering half a ladder (analog) (1)

If Zout has inductance (which it will)

$$V_{load} = \dots + L \frac{di(t)}{dt}$$

So we would like to have a gentle rise and fall times to have a good regulation.

We have defined that as 1  $\mu$ s

This will be achieved by turning on the ASIC by parts.

## Powering half a ladder (analog) (2)

#### Capacitors close to each ASIC at the FE:

✓ The current loop is very small.

$$\Delta V = I \frac{\Delta t}{C}$$

A 0805 SMD ceramic capacitor per ASIC has a  $%X_0 = 0,17!!$

- **\times** Capacitors must be small: material restriction. (but they should reach at least  $10\mu$ F).

- \* Additional regulation is still needed, as the capacitors discharge when the load is active.

#### Low dropout (LDO) voltage regulators added per ASIC:

The regulation in the ASIC is achieved, but the input capacitor still discharges..

How do we charge it back to its level to be ready for the next cycle?

DCDC converter option: (Reported last TWEPP 2012)

- ✓ Its feedback loop charges up the capacitors to the required level.(easy implementation)

- \* Introduces not negligible amount of mass, too high for this particular application.

- **Current peaks** while charging the capacitor. (and it doesn't use the whole idle time)

## Powering half a ladder (analog) (3)

How do we charge it back to its level to be ready for the next cycle?

...second approach.

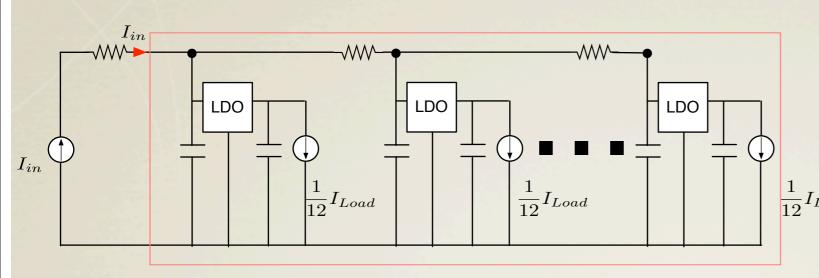

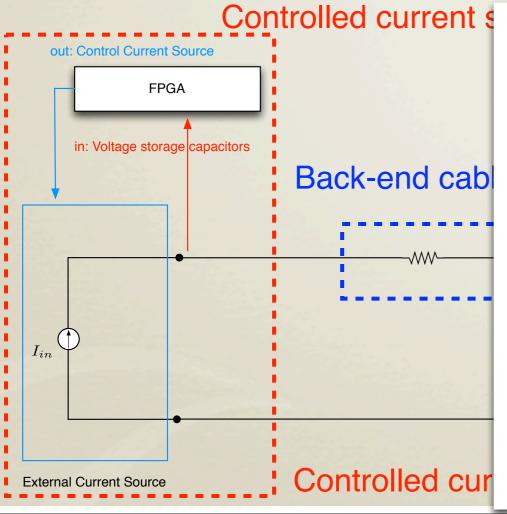

Controlled current source at the back-end: (Presented last TWEPP 2013)

Simpler idea behind, but more difficult to implement.

An estimation of the current at the BE, using the whole period to charge the capacitor, is:

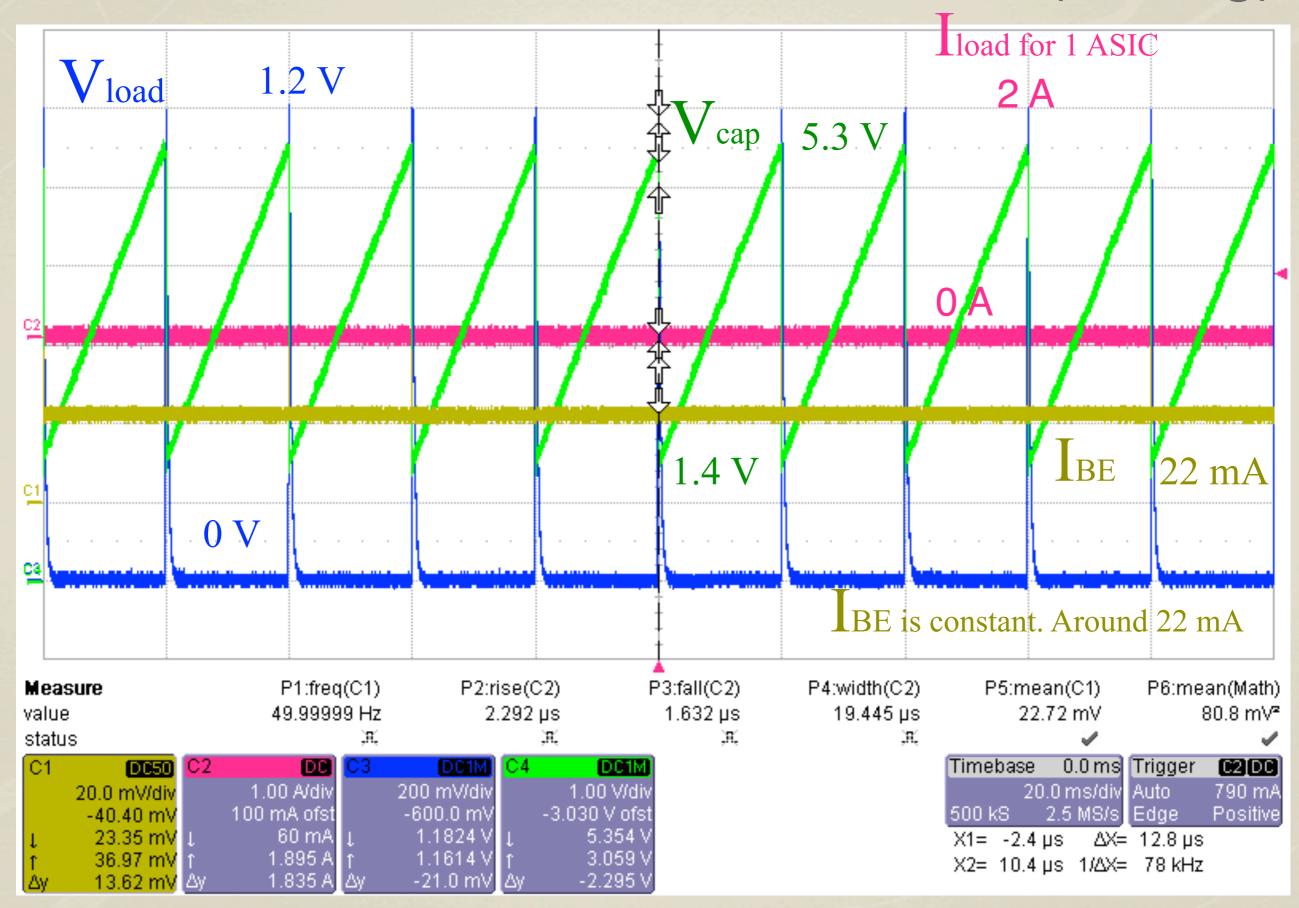

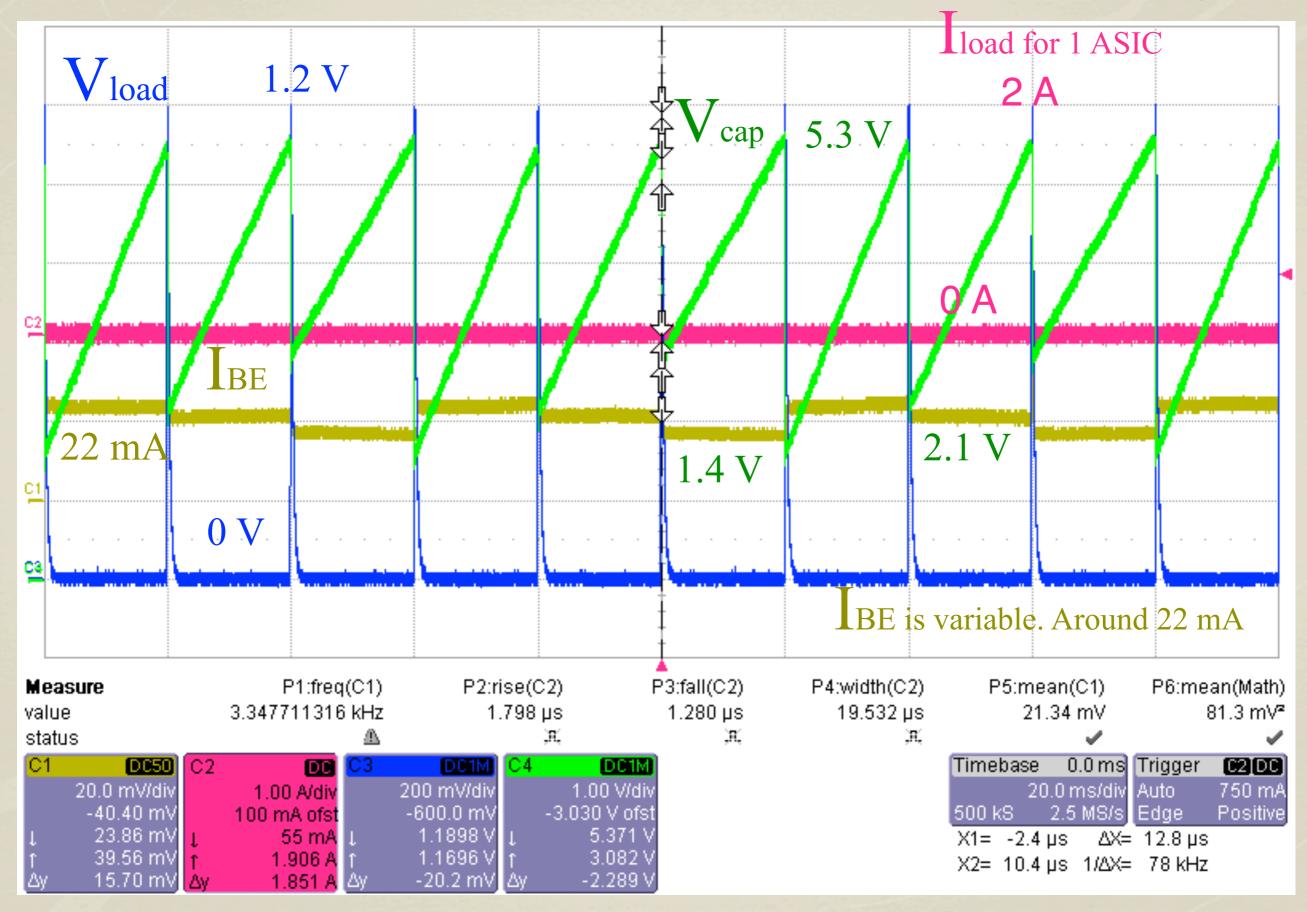

$$I_{in} = I_{load} \frac{t_{on}}{T} \approx I_{load} \frac{20\mu s}{20ms} \approx \frac{I_{load}}{1000} \approx 20mA$$

✓ Cables from the back-end to the capacitors @ FE can be really light in terms of mass.

From now on, this presentation will refer to this approach.

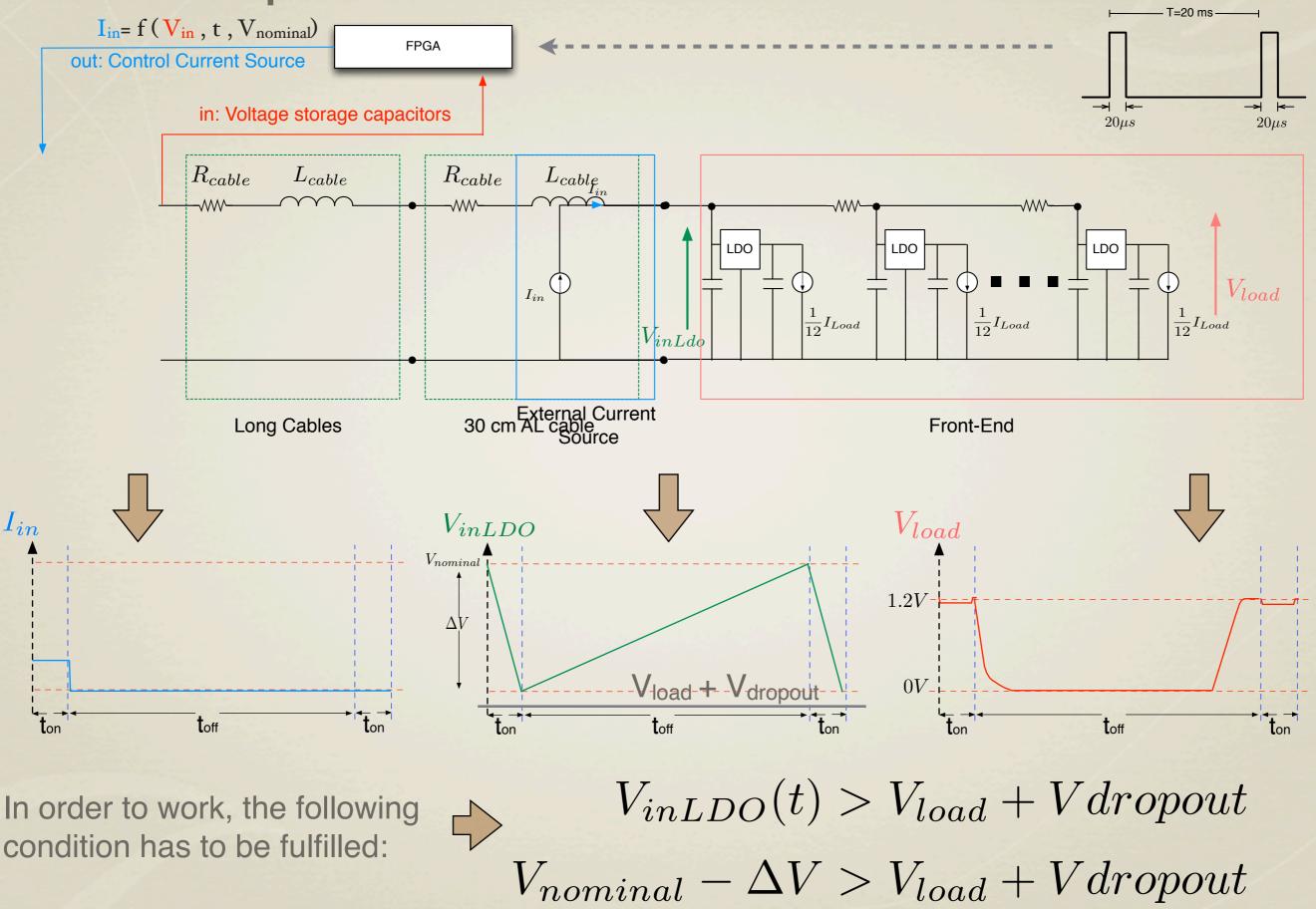

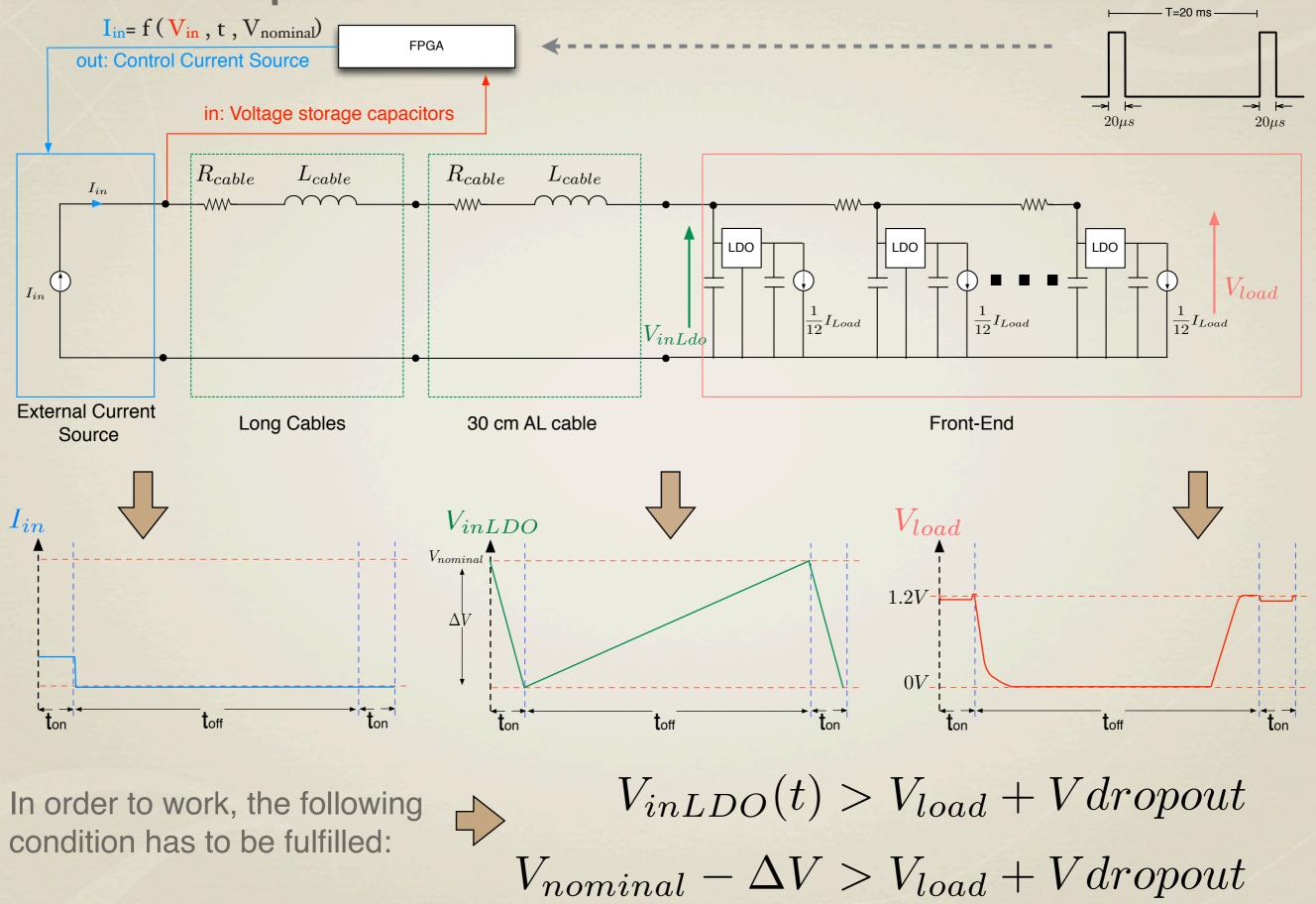

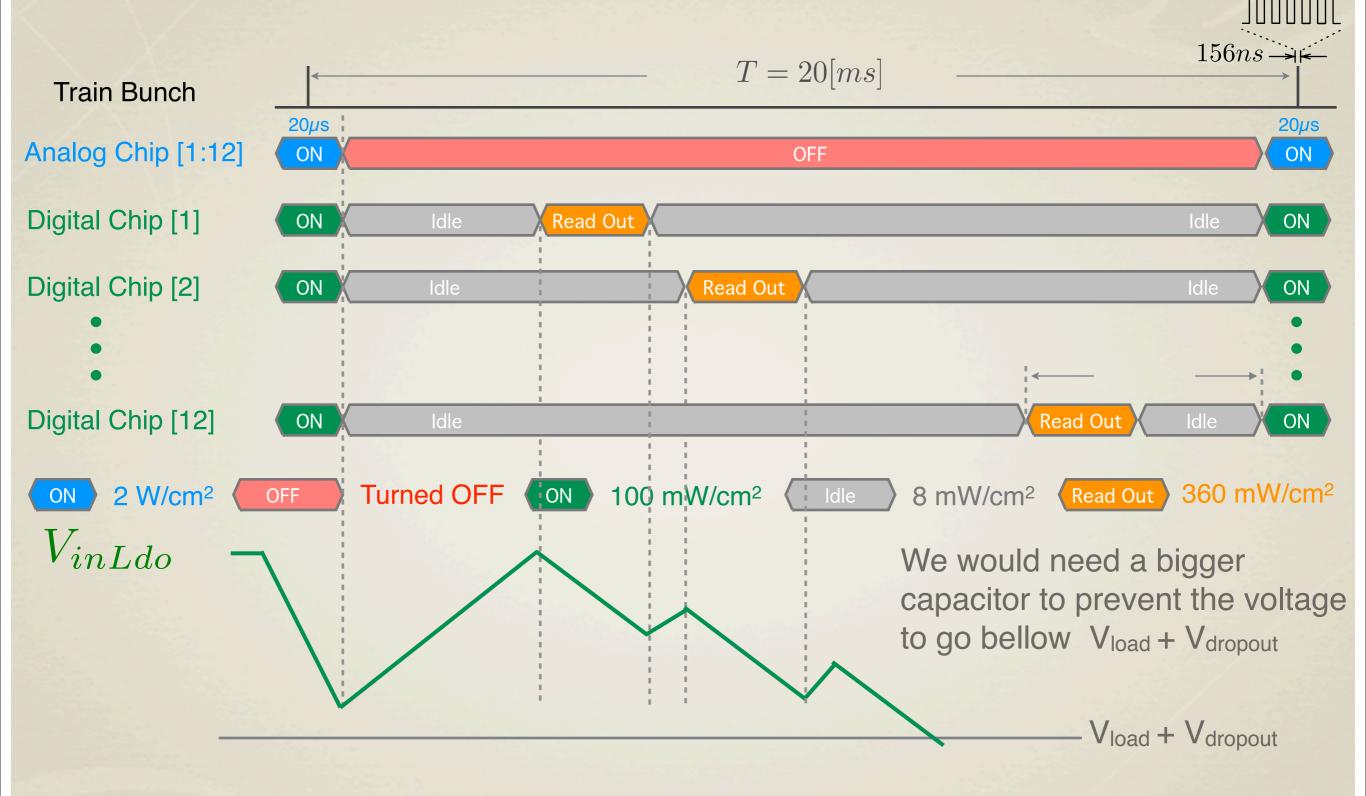

### Principle and waveforms of the scheme

### Principle and waveforms of the scheme

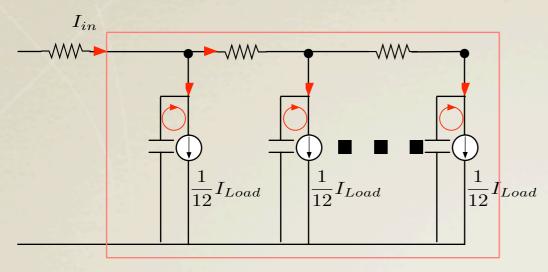

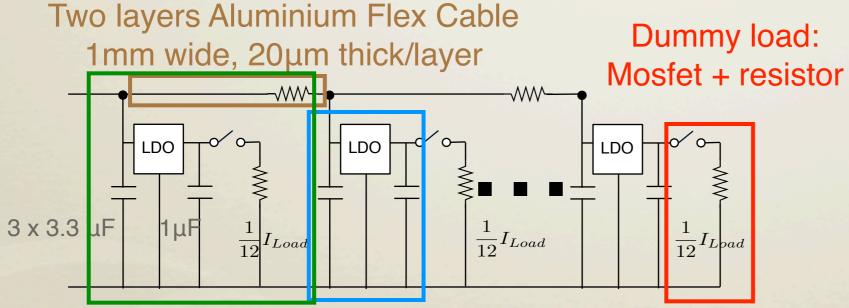

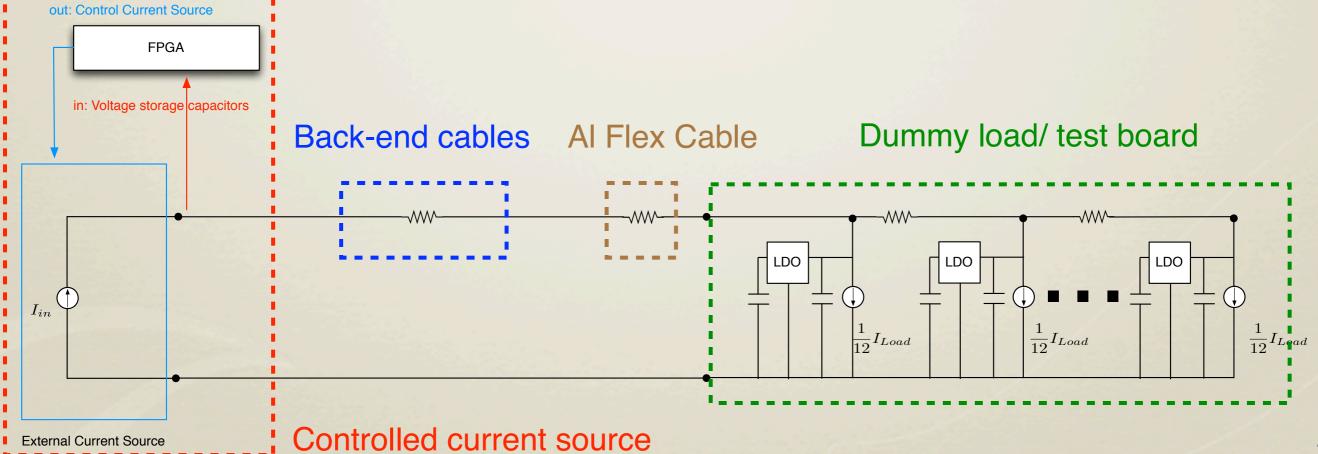

Implementation - T=20 ms - $I_{in} = f(V_{in}, t, V_{nominal})$ FPGA out: Control Current Source in: Voltage storage capacitors  $20\mu s$  $R_{cable}$  $R_{cable}$  $L_{cable}$  $L_{cable}$  $I_{in}$ -WW-LDO LDO LDO  $I_{in}$  $\frac{1}{12}I_{Load}$  $\frac{1}{12}I_{Load}$  $\frac{1}{12}I_{Load}$  $V_{inIdo}$ **External Current** Long Cables 30 cm AL cable Front-End Source Power components Power components FE ASICs or back-end in the ladder **Dummy Loads FPGA**

We will address this first in next slide.

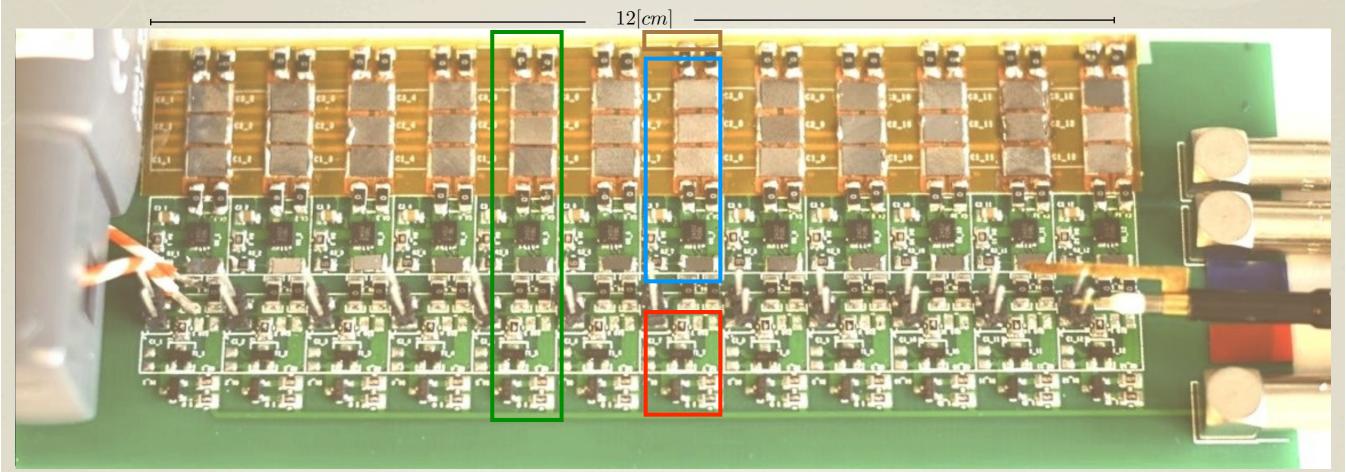

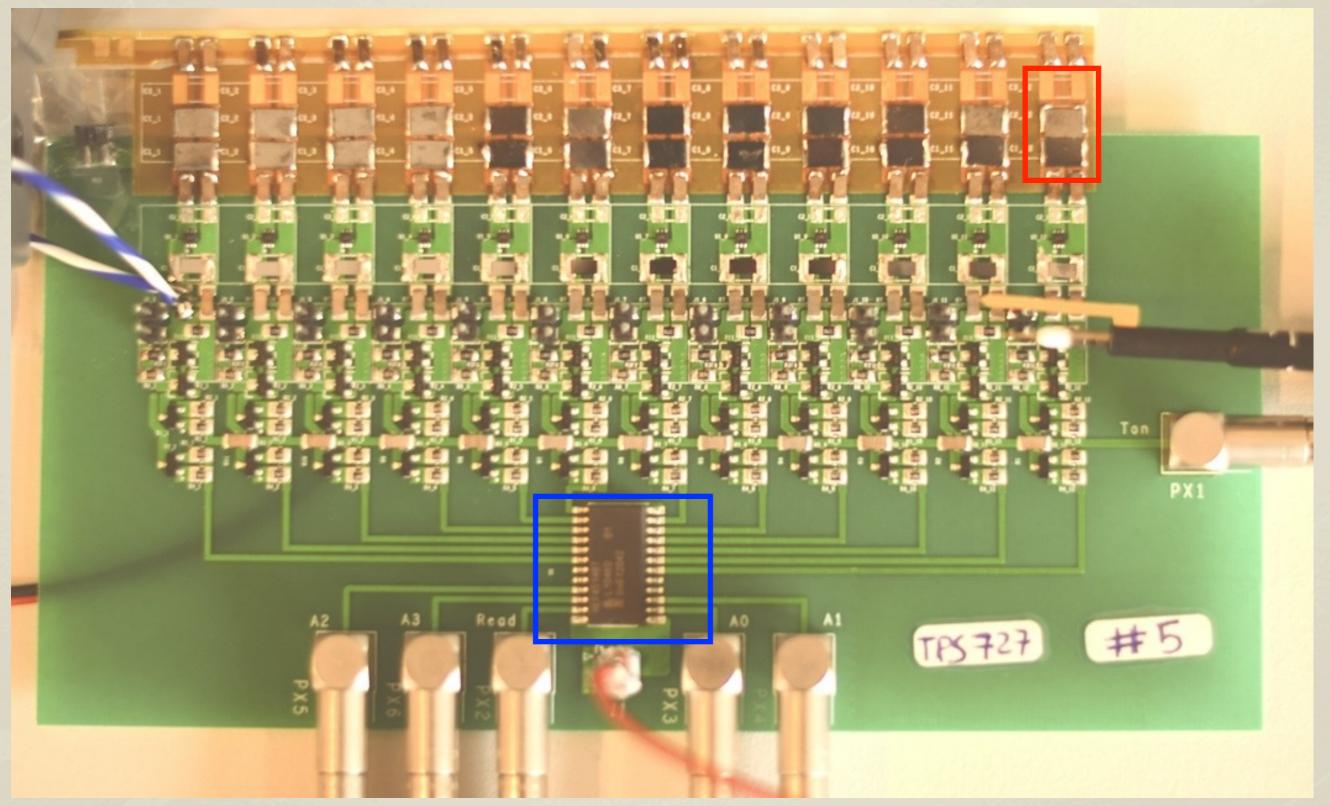

## Evaluation using Analog Dummy Load

The CLICpix is being developed, so in order to test the scheme we need a dummy load.

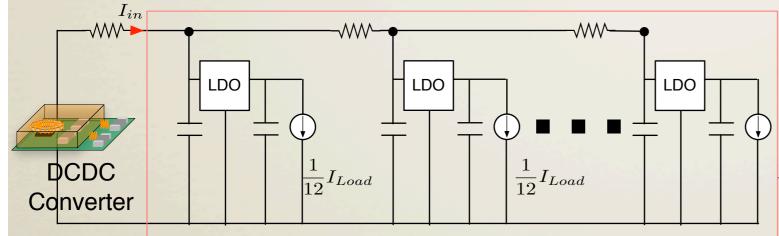

This duplicates 12 times, representing the 12 ASICs, the power storage, regulation and cabling.

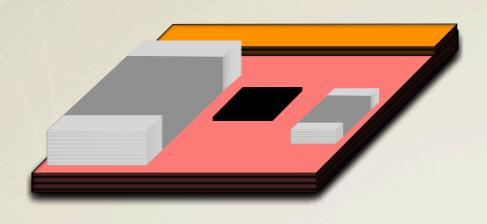

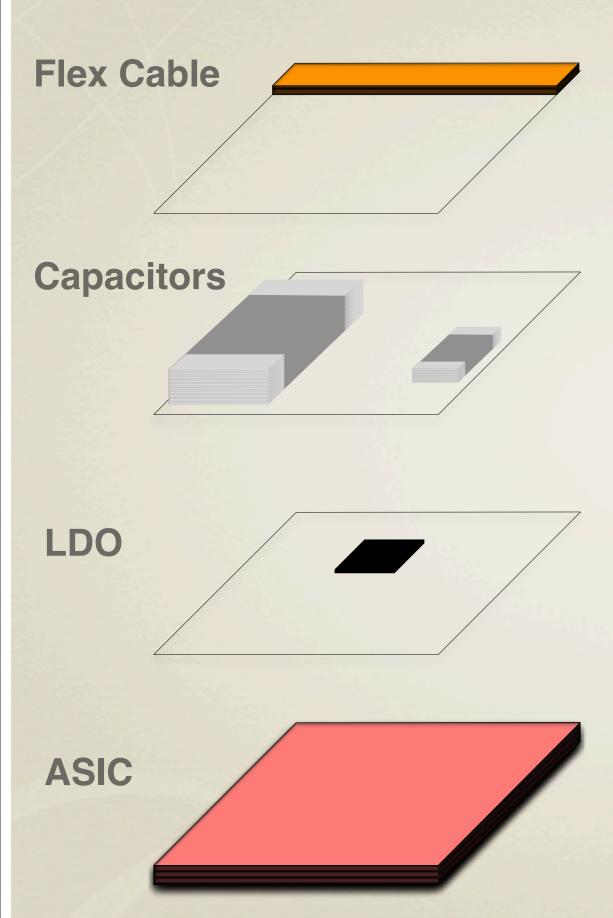

Power storage and regulation:

input Si cap (3 x 3.3  $\mu$ F) + LDO (out: 1.2V) + output Si cap (1 $\mu$ F)

## Why aluminium cables?

For the same resistance than a copper cable, aluminium cables have around 4 times lower material contribution. The aluminium flex cables were made at the CERN PCB shop.

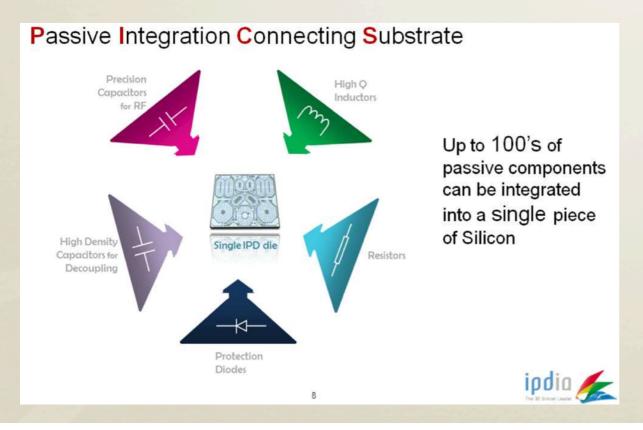

## Why silicon capacitors?

Low mass and flat. They can have a thickness down to 80 µm.

Ceramic capacitor of small smd package (0402 or 0201) can have comparable material. Nevertheless, their capacitance change dramatically (more than 80% of their value for some conditions) with the voltage applied (V<sub>bias</sub>), making them impractical for our application.

IPDiA company can integrate all the necessary passive components into a single die

Which can be afterwards connected to the CLICpix chip using TSVs (Through Silicon Vias).

This is just a preliminary idea.

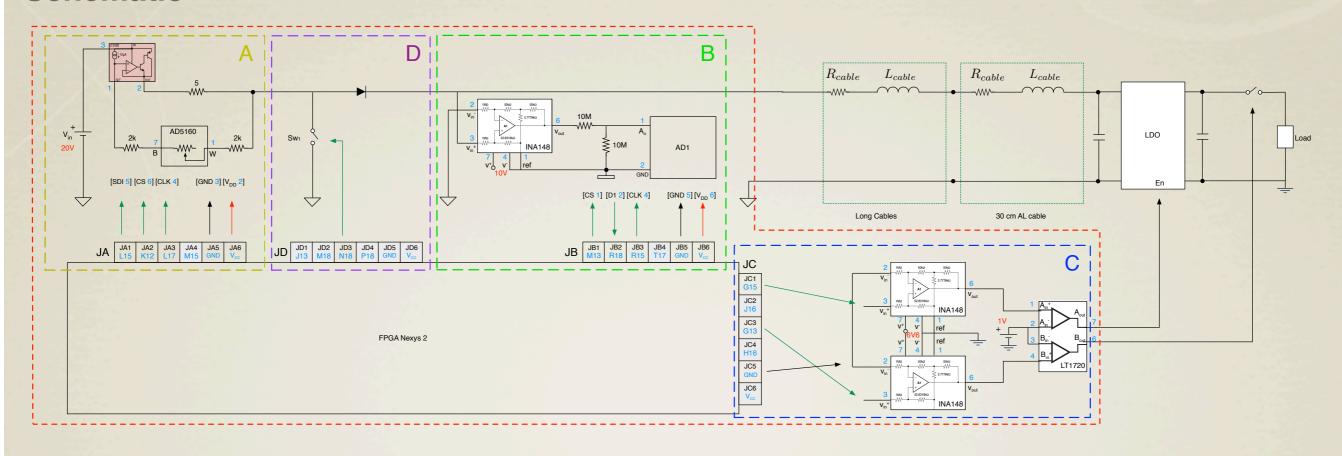

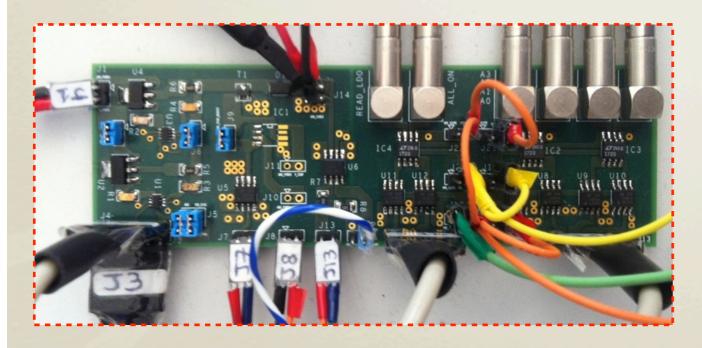

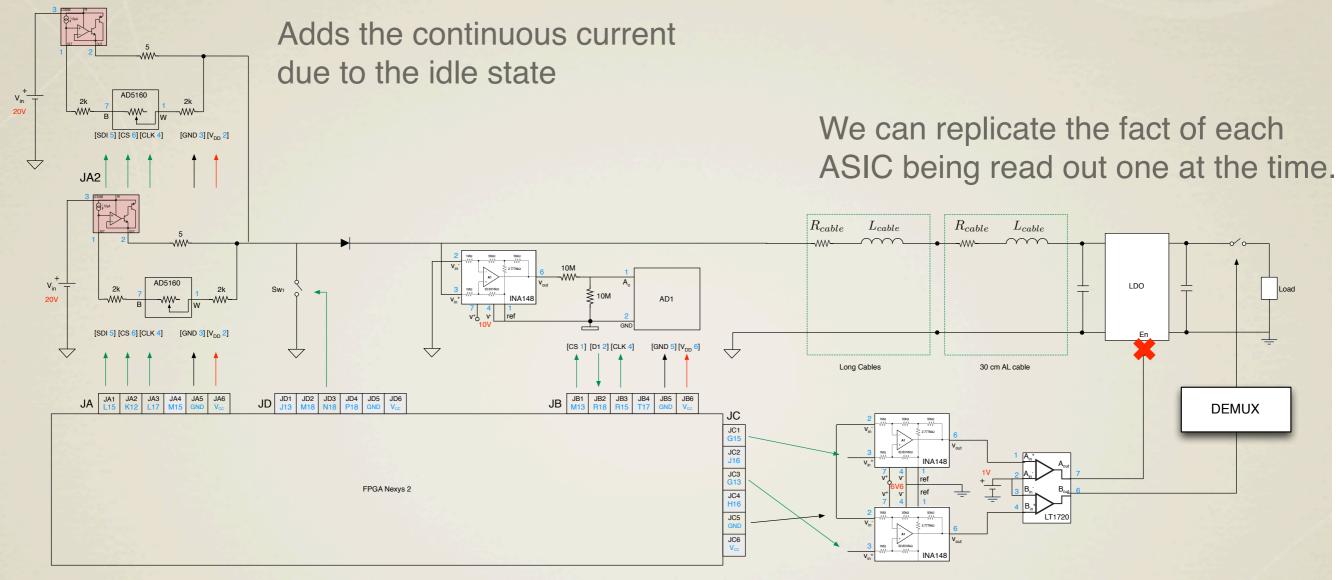

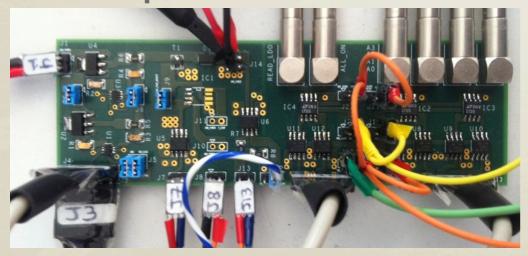

## Power components BE and FPGA (Analog)

#### **Schematic**

#### **PCB** implementation

#### **FPGA**

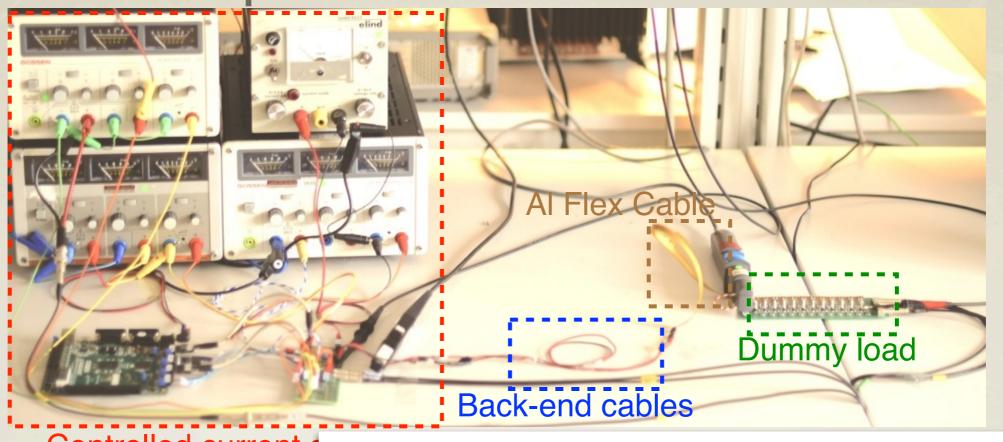

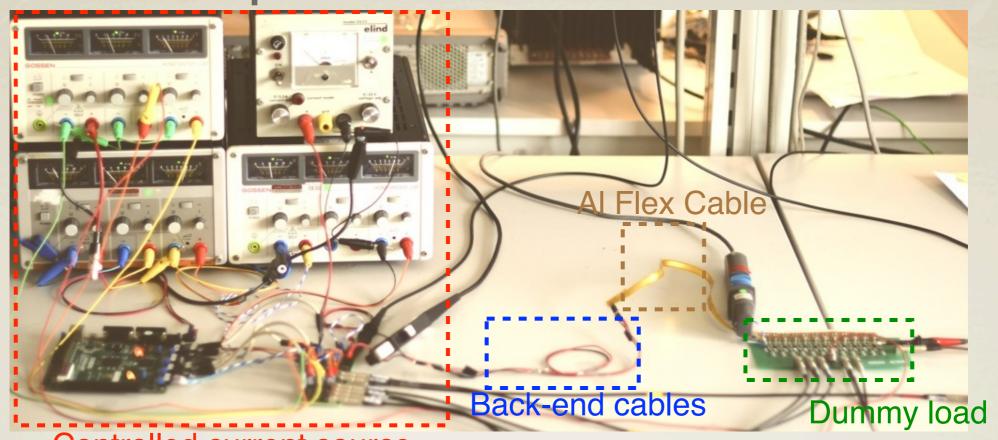

### Implementation @ Lab

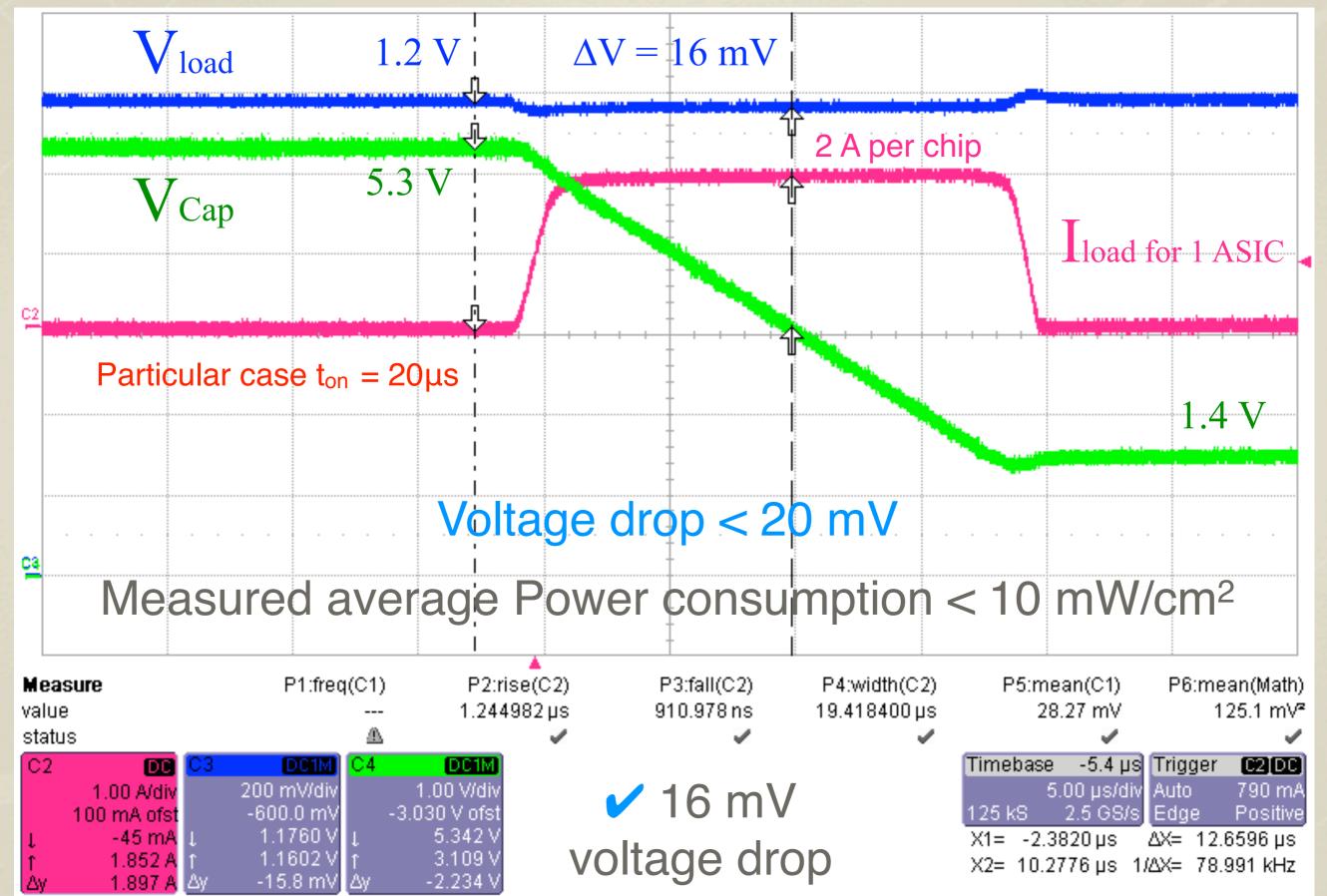

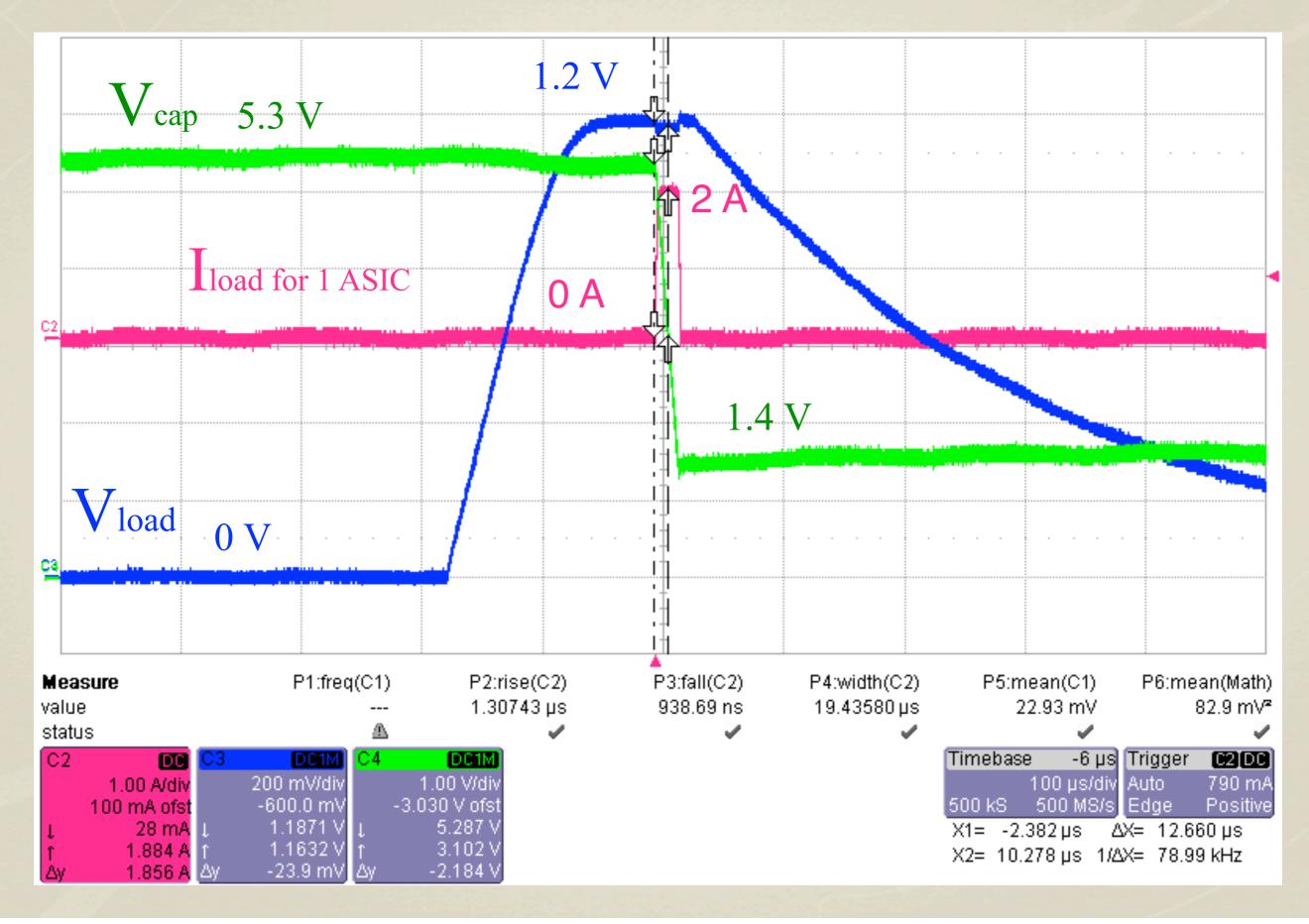

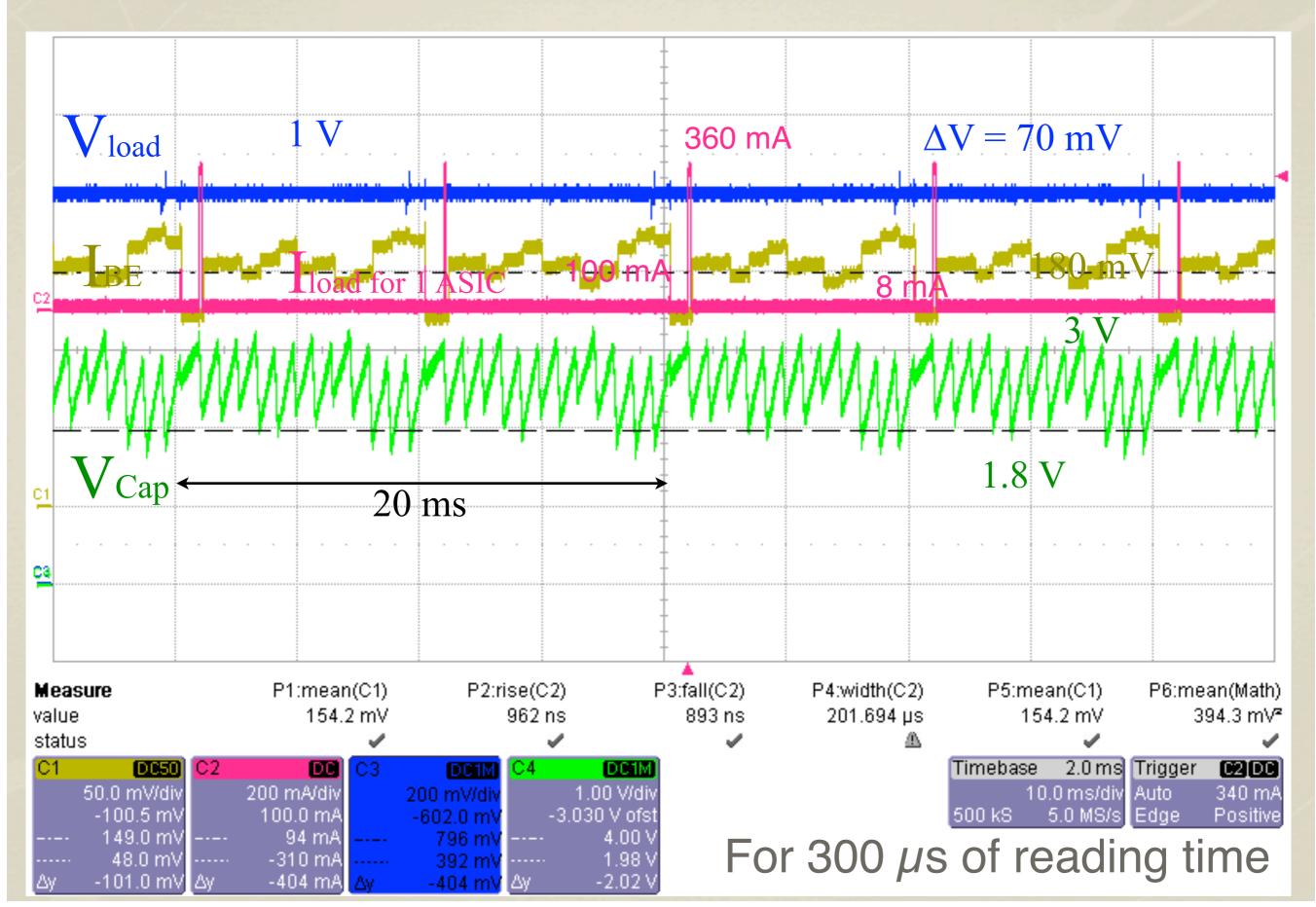

## Regulation during ton < 20 mV (analog)

# En/Dis voltage regulator (analog)

## Measurements for same load value (analog)

## Change in the load consumption (analog)

## Power consumption of Half a Ladder 312 × 500ps

# Power consumption of Half a Ladder 312 × 500ps

Now it can be solved similarly than for the analog part, with the difference that the time to charge the capacitor is smaller but the power consumption is lower too.

## Digital Dummy Load / test board

We reduced the capacitors from 10  $\mu$ F to 6.6  $\mu$ F

We added the possibility to switch individual MOSFETs to represent the read out of the ASICs

# Power components BE and FPGA (Digital)

#### **Schematic**

#### **PCB** implementation

## Implementation @ Lab

Controlled current source

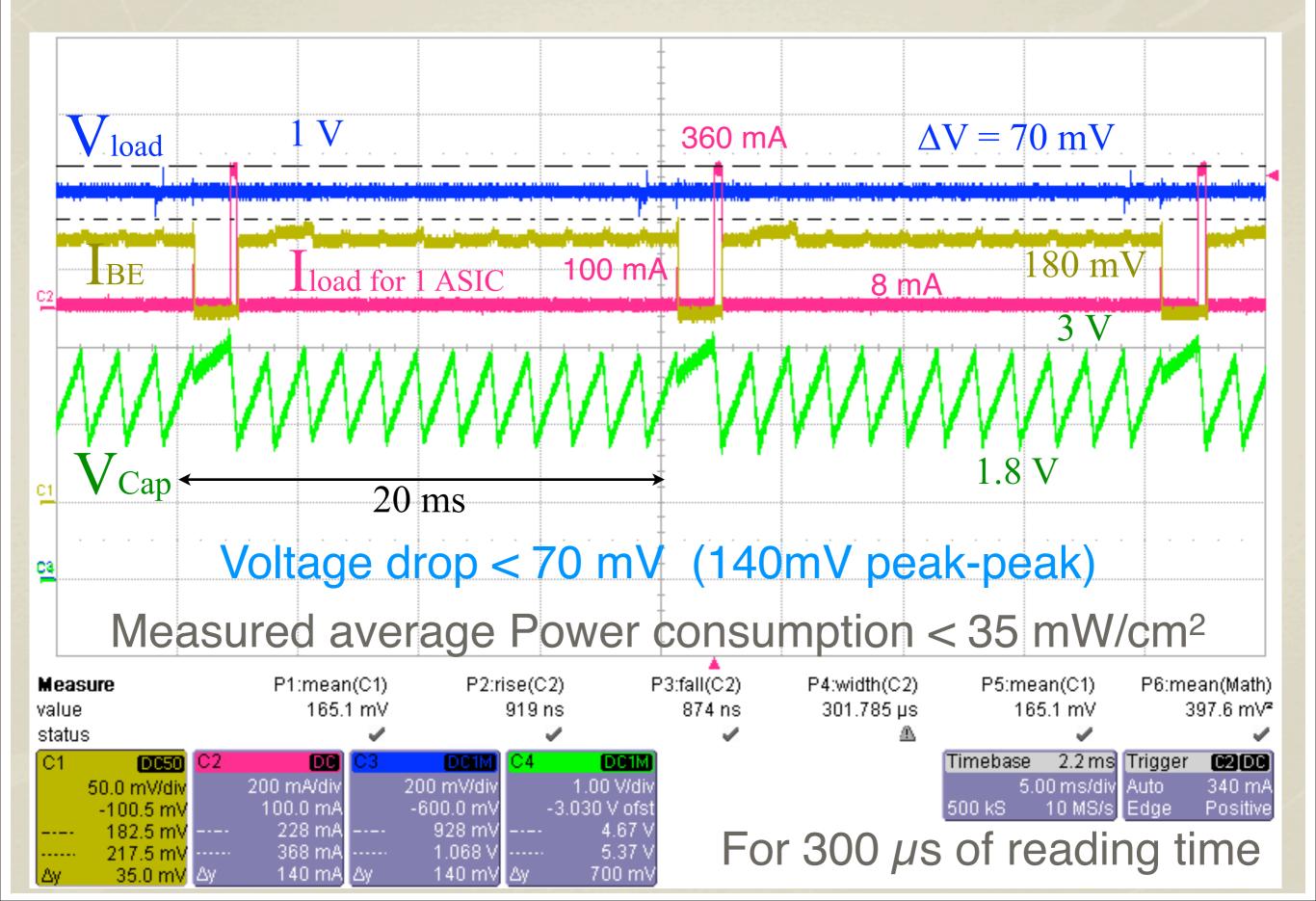

## Digital results

## Digital results

# Material Budget:

# Material Budget:

## Material Budget:

$h_{eq(FLEX)}$

$V_i$  = Volume of material i

A =Area of the ASIC

$$h_{eq(i)} = \frac{V_i}{A} \quad (mm)$$

Capacitors

Knowing the radiation length  $X_{0(i)}$  of the material in mm, we obtain the fraction of the radiation length  $\%X_0$  by:

$$\%X_0 = \sum_{i} \frac{h_{eq(i)}}{X_{0(i)}} \cdot 100$$

$$\%X_{0,ASIC} = \frac{0.1mm}{93.6mm} \cdot 100 = 0.1068$$

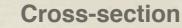

## Material Budget Today

#### Silicon capacitors (today 25 µF/cm²):

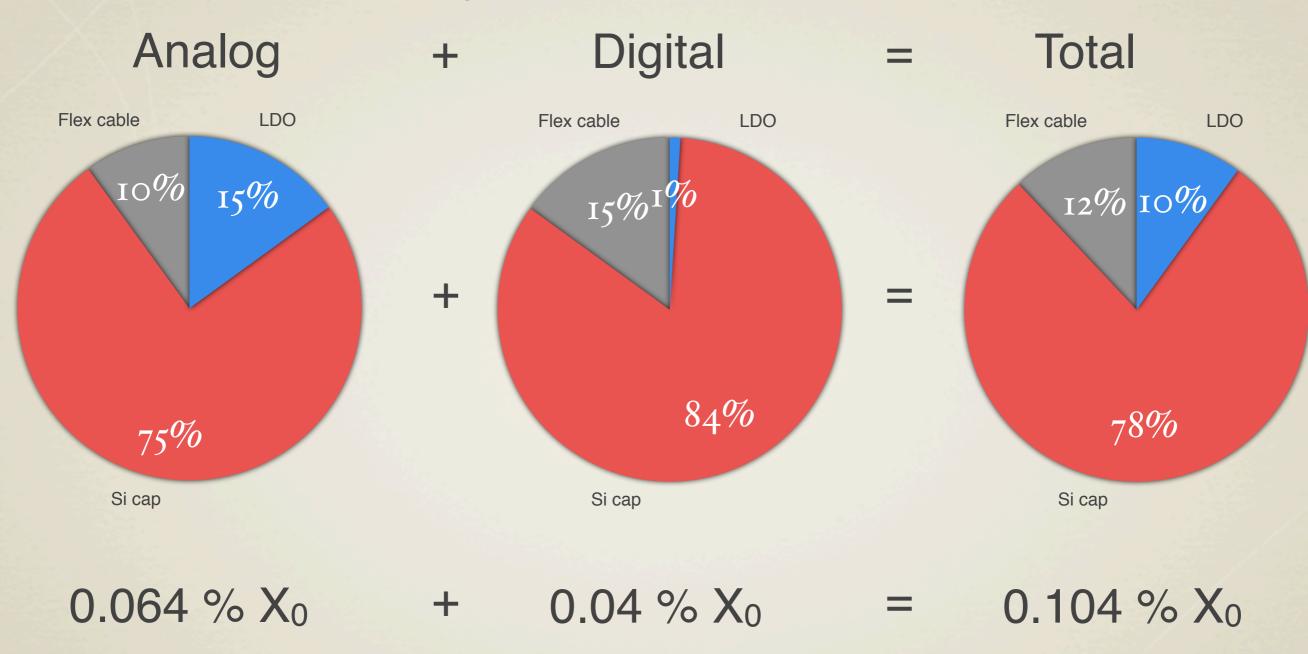

## Material Budget Toway Tomorrow\*

Silicon capacitors (today 25 100 µF/cm²):

#### Flex cable & LDO contribution now is half of the total.

- LDOs will be tried to be included in CLICPix

- → Flex cable material can easily be decreased. (We will produce a new al Flex)

#### Conclusions

During this talk we presented a power-pulsing scheme to power the analog and digital electronics of the future vertex barrel read-out ASIC CLICpix.

The presented scheme counted with regulation and silicon capacitors in the front-end, which were charged up using a back-end current supply of less than 50 mA for the analog part and less than 200mA for the digital one.

Some of the achieved results were:

- •Good regulation as required:

Analog voltage drop < 20 mV and Digital voltage drop < 70 mV

- Total Power losses/dissipation < 50mW/cm² as required.</li>

Analog < 10mW/cm² and Digital < 35mW/cm²</li>

- •Small current (20mA to 60mA for Analog and 100mA to 200mA for Digital) through the whole cable depending on the load consumption. => Low material cables.

- Today's Material Budget of 0.104 % X0, which is expected to be less than 0.043

X0. (after improvements of silicon capacitors technology).

We expect to decrease this contribution furthermore by redesigning the aluminum flex cable and by integrating the LDOs in the CLICPix ASIC.

## Thanks for your attention:)