## **NSREC 2013 Summary**

Radiation 2 Electronics (R2E) LHC Activities

Rubén García Alía, Giovanni Spiezia, Slawosz Uznanski

- Online **brochure** NSREC 2013:

- http://www.nsrec.com/brochure2013.pdf

- **Pre-print** collection (not exhaustive and with non-uniform naming):

- <u>\\cern.ch\dfs\Departments\AB\Groups\ATB\LP\Equipment</u> <u>Controls\Radmon and Radiation test</u> <u>facility\Conference\_WS\_scg\NSREC-13\pre-prints</u>

- <u>http://radwg.web.cern.ch/RadWG/Pages/Literature.htm</u>

- Online preprint request:

- <u>http://www.nsrec.com/preprints2013.htm</u>

- Online **data workshop** record:

- <u>http://nsrec.com/redw/</u>

- Dosimetry (optical fibers)

- Destructive SEE events (Schottky diodes)

- Test approach (high-speed SRAMs)

- Component scaling (sensitivity to secondary protons + electrons)

- Laser testing (transistor analysis for deep sub-micron)

- Moore's law (FinFETs)

- Performance of **Ge-doped optical fiber** as a thermoluminescent dosimeter (E1): **universal response** for gamma, 63 MeV protons and 0.8 and 14 MeV neutrons (resolution not clear, to be followed up in final paper)

- Optical fibers: parts of radiation tolerant data links (in power reactors) as well as dosimeters/sensors (spatial resolution below 1m over km distances)

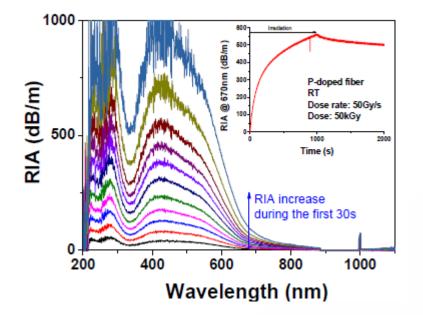

- Radiation-Induced Attenuation (RIA) is linked to the generation of point defects in the silica-based matrix. It can decrease or increase with temperature

- Irradiation using 10 keV X-ray machines at 50 Gy(SiO<sub>2</sub>)/s and different temperatures up to 300°C.

- Fiber optics analyzed:

- <u>**P-doped**</u> (radiation sensitive)  $\rightarrow$  RIA decreases with temperature

- <u>Ge-doped</u> (radiation tolerant) → saturation at doses exceeding 10 kGy.

RIA decreases with temperature

- <u>F-doped</u> and <u>Pure-Silica</u> (radiation hardened) → increases until 200°C, then decreases

## **Dosimetry using optical fibers (E1, F2)**

700 P-doped fiber 450nm (1 kGy) 600 650nm (1 kGy) RIA (dB/m) 650nm (10 kGv) 500 400 <u>~</u>C 300 200 100 0 50 100 150 200 250 300 Λ Irradiation Temperature (°C)

Dosimetry with **P-doped fibers**: linear response for space and medical, and possible calibration for larger doses

Spectra domains where RIA is only very slightly affected by temperature can be exploited for dosimetry applications

S. Girard et al. "Combined High Dose and Temperature Radiation Effects on Multimode Silica-based Optical Fibers", NSREC 2013 preprint

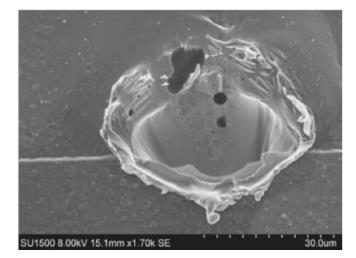

- Diodes used in hybrid DC-DC converters

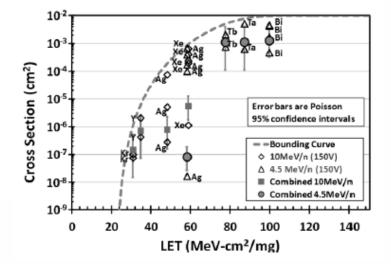

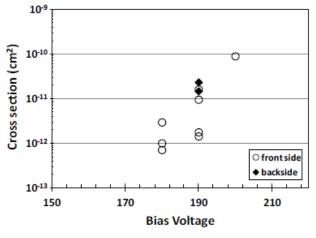

- Test performed on commercial parts SD090SC200A (Sensitron) and MBRC20200CT (On Semiconductors) for heavy ions (both) and protons (the second)

- Failures occur in reverse voltage and cross sections are strongly dependent on **voltage bias**

- LET threshold at ~ 10-20 MeVcm<sup>2</sup>/mg for both devices, and proton cross section of 10<sup>-12</sup> – 10<sup>-10</sup> cm<sup>2</sup>/device depending on bias voltage (180-200V)

- Direct ionization from a charged particle is thought to be insufficient to cause a failure. **Nuclear interactions** are needed to trigger the event

- **Tungsten** used as contact metal. Cross section similar from back side than front side, therefore fragments from tungsten are ruled out as the cause (note: fission products are isotropic)

## Destructive events in Schottky diodes (W-35, I-1)

Single Event Burnout

Heavy lon cross section

200 MeV proton cross section

J. George et al. "Single Event Burnout Observed in Schottky Diodes", NSREC 2013 preprint

- Advanced process technologies (sub-100 nm process) can operate at frequencies from several hundred MHz until greater than one GHz

- High performance SRAMs have low critical charge and often use **EDAC codes** that can reduce the number of events by 4 orders of magnitude

- Uncorrectable events (**MBUs**) can dominate the corrected error rate

- Testing modes: W/RUF (Write/Read Until Failure) yields equivalent results to Static, while W/R (Write/Read) provides a cross section ~1/2 that of Static (half the error are over-written)

- The nearly uninterrupted at-speed operation during the test can only be achieved with the data analyzed **on-chip**

- This test procedure allows for MCU and MBU detection, as well as transient (frequency dependent) and persistent error identification

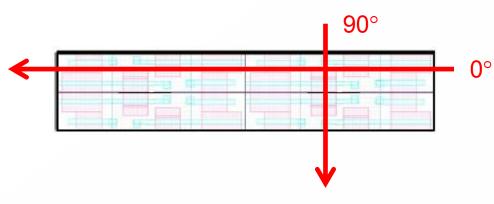

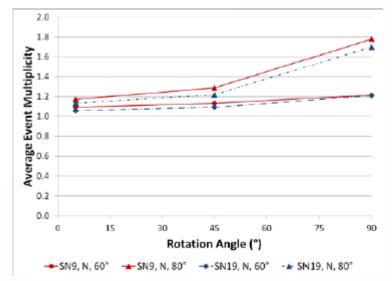

- Dependence of the event multiplicity with the **rotation angle** (and large tilt angle) as more cells are

## **At-Speed SEE SRAM testing (D-6)**

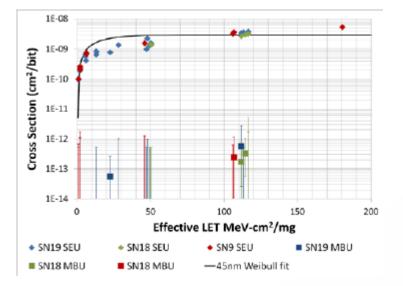

SEU and MBU cross section for 32 nm tech.

2x2 cell array for 90 nm SRAM

MBU dependence with rotation angle

*E. Cannon et al. "At-Speed SEE Testing of RHBD Embedded SRAMs", NSREC 2013 preprint*

- Tests performed on a 90 nm Fujitsu technology down to a supply voltage of 0.2V (nominal is 1.1V)

- Increase of a *factor* ~500 in the SER, however only a factor ~4 is expected from simulations shown in the work

- No pre-print of the paper available, but similar work can be found:

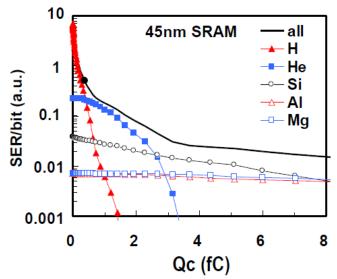

The sharp rise below 0.6fC (13.5keV) is due to the direct ionization of protons

Kobayashi, H. et al. "Alpha particle and neutron-induced soft error rates and scaling trends in SRAM", Reliability Physics Symposium, 2009 IEEE International, vol., no., pp.206,211, 26-30 April 2009

> In an accelerator environment, the impact could be even stronger (direct ionization from environment particles, higher proton and alpha production due to larger energies...)

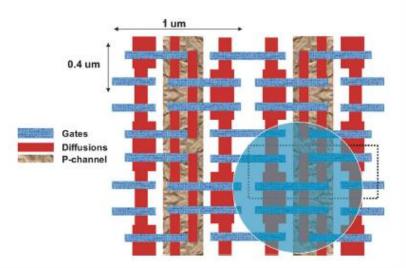

- Laser spot-size of **0.3 um** (FWHM) for the analysis of **single transistors** in **deep sub-micron technologies**

- 90 nm SRAM studied, with a cell surface of 0.7 x 1.6 um<sup>2</sup> and a transistor size in the order of 0.2 um

- Analysis of individual transistor sensitivity yields a very large intra-cell spread with a regular pattern, and is therefore attributed to the masking used to produce the chip

Schwank, J. et al. "Estimation of Heavy-Ion LET Threshold in Advanced SOI IC Technologies From Two-Photon Absorption Laser Measurements" Nuclear Science, IEEE Transactions on , vol.57, no.4, pp.1827,1834, Aug. 2010

45 nm memory cell covered by a 1 um spot-size

- First experimental evidence of SEU induction by a single electron

- 45 nm technology used: Q<sub>crit</sub> is estimated to be 0.38 fC for 1.1V (nominal) operation and 0.19 fC for 0.55V (corresponding to 8.6 and 4.3 keV respectively)

- Upsets only measured in the V<sub>supply</sub>=V<sub>nominal</sub>/2, consistent with simulations

- *Physical process:*

- X-ray beam (10 keV photons) which can undergo photoabsorption, transmitting almost all their kinetic energy to electrons

- Auger decay chain (internal absorption) can also deposit enough energy to cause an SEU

- Cell size simulated as 0.16 um<sup>2</sup> x 300 nm

- Note: the SEU cannot in principle be induced through direct ionization as the range in silicon of a 10 keV electron is 1.5 um (too large in relation to the deep sub-micron transistor size)

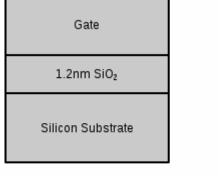

- **FinFETs** are the trend solution for component scaling below 28 nm thanks to their low leakage characteristics (Samsung, IBM, Global Foundries, Intel...)

- **High-K gate oxide** materials (HfO<sub>2</sub>) needed as leakage currents increase dramatically for SiO<sub>2</sub> with thicknesses below 2 nm

- Gate breakdown in SRAM memory transistors

- operation voltages could go down to 0.4-0.6V (for power efficiency, exascale computing being the driving application)

- Two main FinFET types:

- **bulk** (SEU prone, minor TID effects but still there due to the oxides in the STI)

- **SOI** (no charge sharing, less prone to SEU, TID effects in buried oxide)

Existing 90nm Process Capacitance = 1x Leakage Current = 1x

| Gate                             |  |

|----------------------------------|--|

| 3.0 nm high- dielectric <i>k</i> |  |

| Silicon Substrate                |  |

A potential high- processk Capacitance = 1.6x Leakage Current = 0.01x