#### MICE Tracker Readout Update, Preparation for Cosmic Ray Tests

- Cosmic Ray Tests at RAL

- AFE-IIt Firmware Development

- VLSB Firmware Development

- Summary and Plans

## Cosmic Ray Tests

- From Nov. 12 19, a cosmic ray test stand was set up at RAL including the following systems

- Scintillating Fiber Tracker

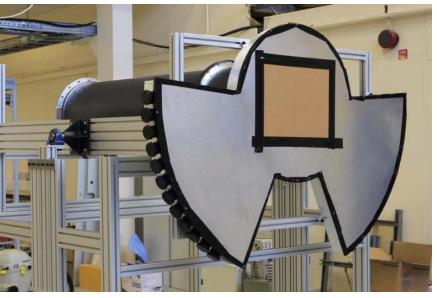

- Cherenkov Detector

- Data Acquisition

- Time of Flight counters not ready for tests

- Ultimately, problems with the two VLPC cryostats for the trackers prevented data taking

- One didn't cool down all the way to necessary operating temperature.

- The other developed leaks, possibly during overseas transit.

- Both cryostats shipped to FNAL for inspection and repair.

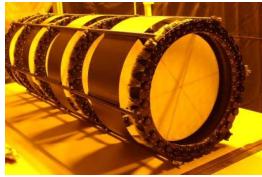

## Cosmic Ray Tests, Tracker

- The first tracker has been assembled.

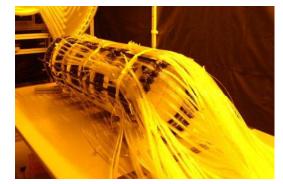

- The fiber-waveguide connections have been tested showing only one dead channel.

- The tracker firmware has been exercised with selfinjection data.

- Data to VLSB boards looked fine.

- Strange values written to control registers suggested problems with data taking with multiple boards.

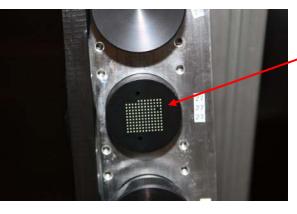

#### **Tracker Photographs**

5 tracker stations

Connecting waveguide fibers

Tracker, waveguide fibers, and patch panel all assembled

All waveguide fibers organized and bundled

Only one dead channel

## Work at Fermilab (FNAL)

- Cryostats shipped back to FNAL.

- First cryostat compressor jumpers weren't set properly (cryostat was o.k.)

- Second cryostat had a leak in one cassette (other cassette now has leak!).

- Power supplies had oscillating voltages.

- Problem traced to faulty ground

- Another power supply will be needed (one per cryostat)

- Possible problems with 10 meter long LVDS cables for VLSBs; current work using 3 meter long cables.

- Tracker firmware being tested at FNAL. (more later)

- Try for cosmic ray tests at RAL in March.

#### MICE Tracker Acronyms

- AFE-IIt Analog Front End, Version II, with time

- VLSB VME LVDS Serdes Buffer

- Versa Module Eurocard

- Low Voltage Differential Signalling

- Serializing/Deserializing

- FPGA Field Programmable Gate Array

- AFPGA controls analog data

- DFPGA controls digital bitmap of which channels are on.

#### Future Tasks for AFE-IIt Firmware

- Integrating Senerath's DFPGA code

- Senerath has released his (possibly) last version

- When tracker readout system is tested and working, we will determine what roles the current and Senerath's DFPGA codes will have.

- Implementing and debugging AFPGA 4-level buffer

- Bulk of code in place

- Need to work out potential timing conflict between incoming triggers and data transfers between AFPGA/DFPGA

- Testing that PLL locks on to variable ISIS signal

- Hardware and firmware all set

- Need to put everything together to test and work out kinks

#### Goal: Finish these in a couple months.

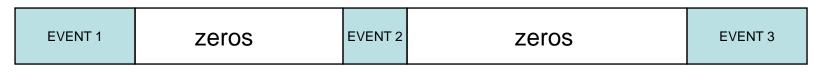

## **VLSB** Firmware Modifications

- Data storage in memory banks

- Before modifications

After modifications

EVENT 1 EVENT 2 EVENT 3

- Newly utilized registers: used by MICE DAQ

- Registers 0 3: Memory bank addresses of last data word

- Register 15: Number of events in spill

#### **VLSB** Firmware Modifications

- Enable trigger word operation for all four memory banks, not just first bank.

- Fast clear of memory banks

- Simulated data written to VLSB

- When fast clear bit set by MICE DAQ

- All memory addresses set to zero.

- Fast clear done bit properly set after last address cleared.

## **VLSB** Testing

- We're using a test stand at FNAL which sends repeating data patterns to the 4 memory banks of VLSB boards.

- A two-board set-up is being used.

- Preparing each board to receive data takes about a  $\mu s$  per board which is too long.

- To get this to work, we're sending a data trigger enable signal from a master board to a slave board via a LEMO cable connection. This takes only about 20 ns.

- For MICE beam, this won't be necessary, but it's useful for self-injected data and cosmic ray data taking modes.

- This has uncovered some code bugs which have been corrected.

# **VLSB** Testing

- What works

- Suppression of zero words

- Triggering on control register specified trigger word

- Data trigger enable signal sent from master board to slave board in about 20 ns.

- Control registers correctly indicate

- Final address of memory bank with data

- Number of events in a spill

- What doesn't work

- Getting both boards to start recording data at the start of first trigger word.

## Preparation for Cosmic Ray Test

- Connect power supply to two cryostats (done)

- Cryostat temperature tests (*done*)

- Get new AFE-IIt and VLSB firmware working together

- Characterize 4 cassettes

- Simulate cosmic ray test with LED

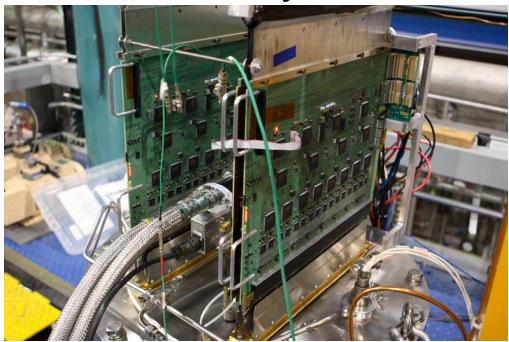

## AFE-IIt and VLSB Boards

- 8 boards for 2 cryostats fully tested and characterized.

- 4 boards assigned to 3<sup>rd</sup> cryostat, not yet tested and characterized

- 11 spare boards available, 4 of which will be assigned to 4<sup>th</sup> cryostat.

- 23 AFE-IIt boards available for MICE

- 19 VLSB boards available for MICE.

#### Summary

- Preliminary firmware package being set up for data readout tests at FNAL

- Only one level of 4-level buffer

- Using modified D0 DFPGA instead of Senerath's DFPGA.

- Aiming for

- Reshipping tracker readout system to RAL in March

- Unpacking tracker readout system at RAL in March for cosmic ray tests

- End in sight for full firmware for MICE (~ 600 triggers/ms)