# Pixel Detectors – on the brink to a new era

Norbert Wermes University of Bonn

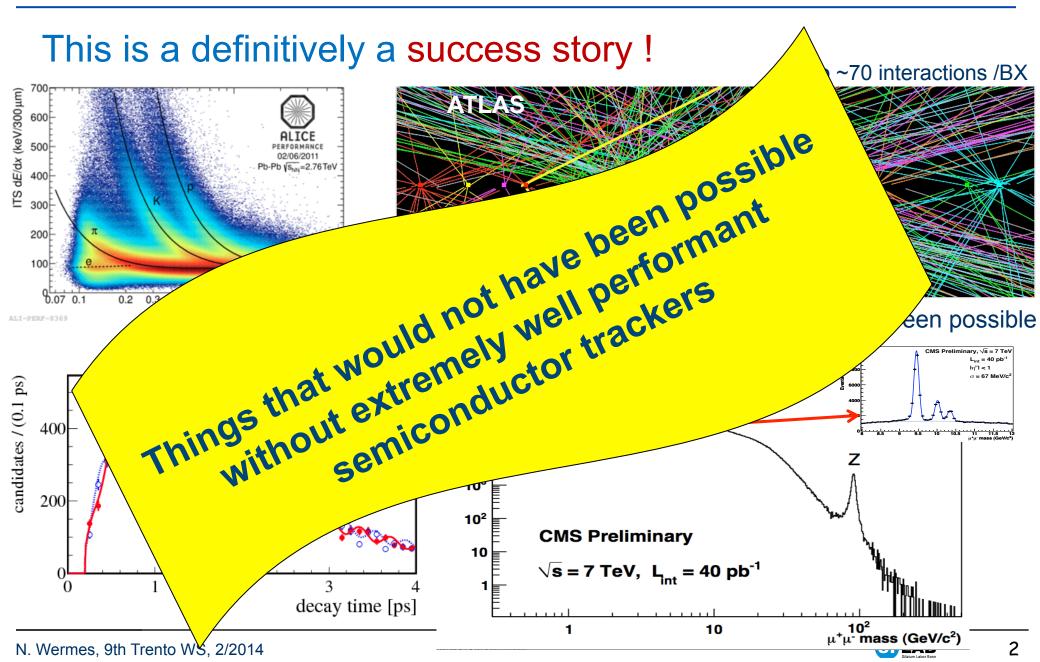

#### Looking back on 3 years of LHC running (25 /fb) ...

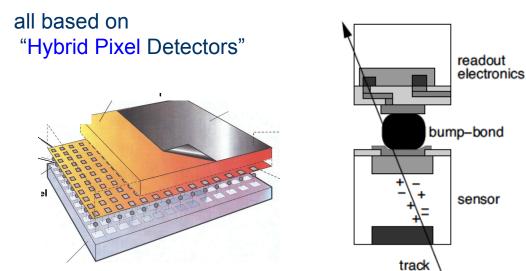

### A classification ... from HYBRID pixels to new challenges

- standard HYBRID pixels

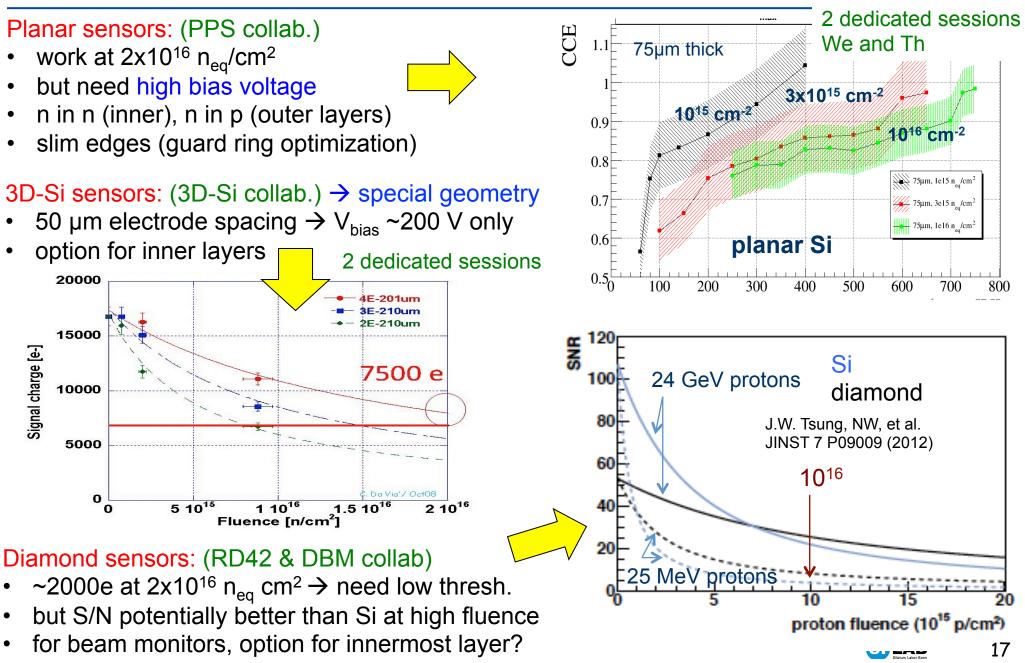

- various sensors: planar-Si, 3D-Si, diamond

- mixed signal R/O chip (FE-I3, FE-I4, ROC ...)

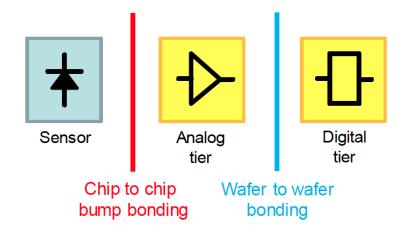

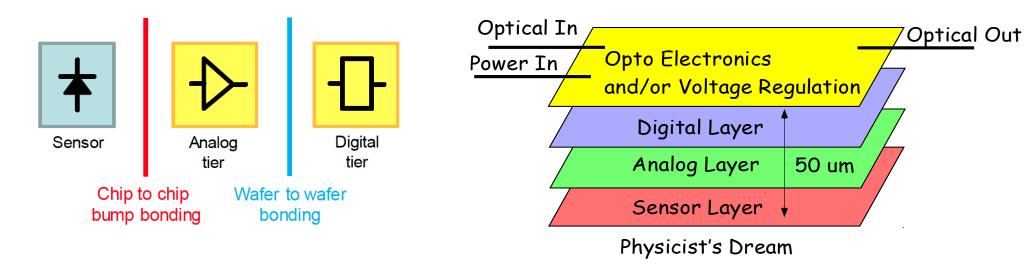

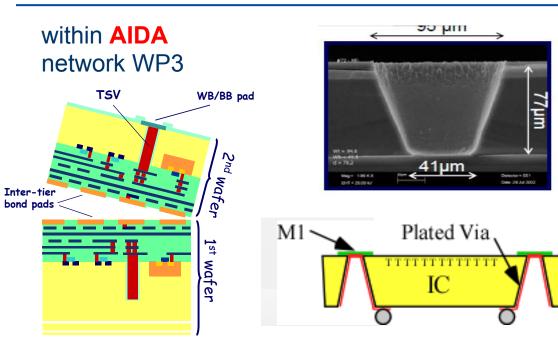

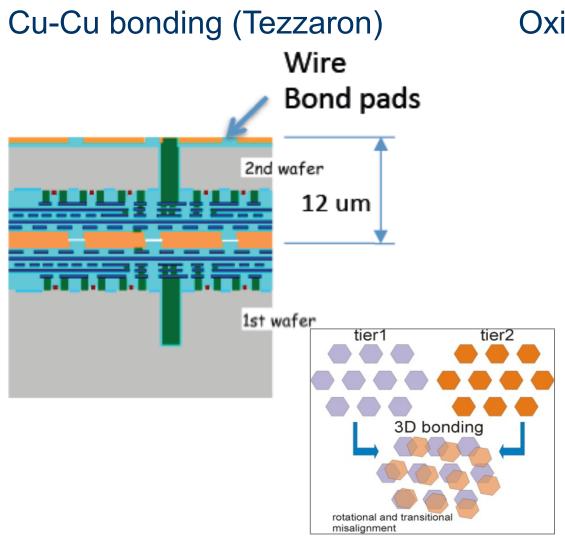

- 3D integration of CMOS Tiers

- separate analog / digital / opto

- FE-TC4 (Tezzaron/Chartered)

### A classification ... from HYBRID pixels to new challenges

- standard HYBRID pixels

- various sensors: planar-Si, 3D-Si, diamond

- mixed signal R/O chip (FE-I3, FE-I4, ROC ...)

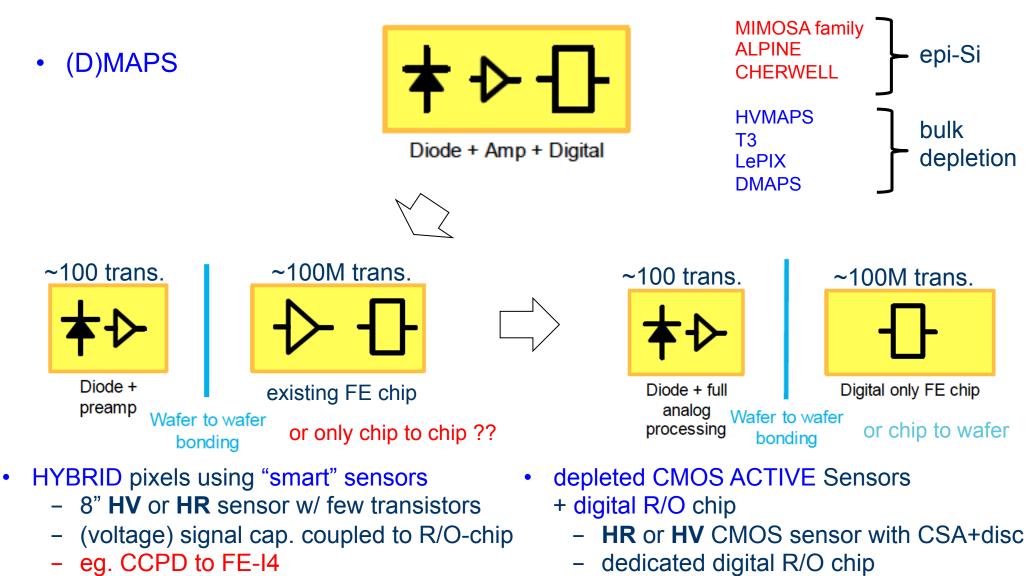

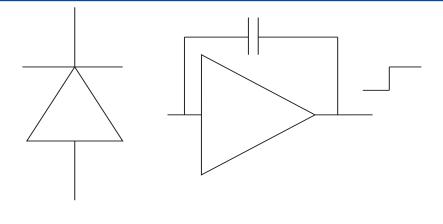

- Monolithic Active Pixel Sensors

- MAPS using CMOS with Q-collection in epilayer (usually by <u>diffusion</u> → recent advances)

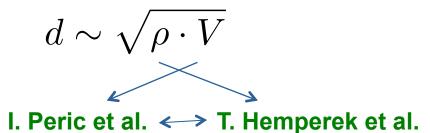

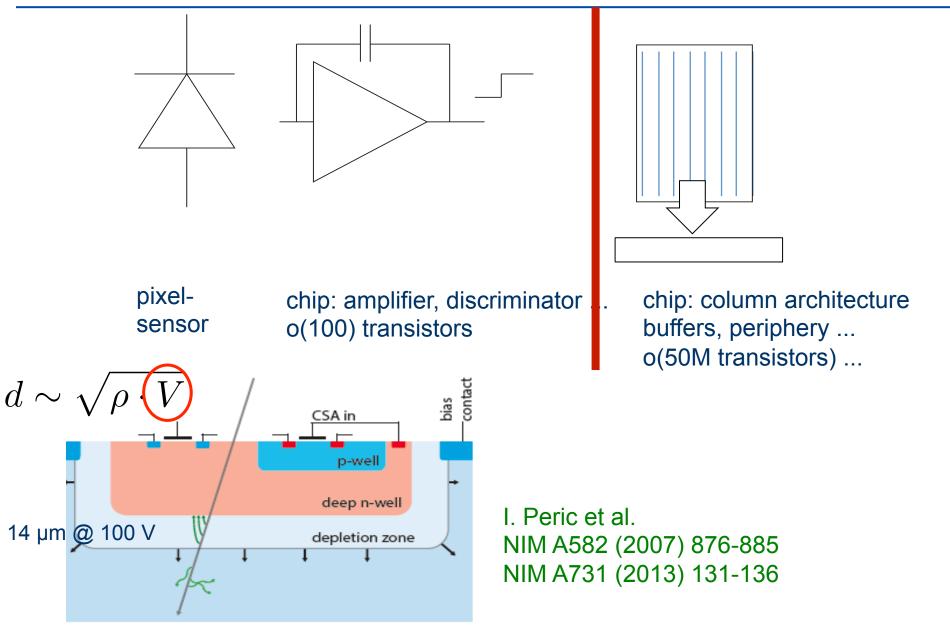

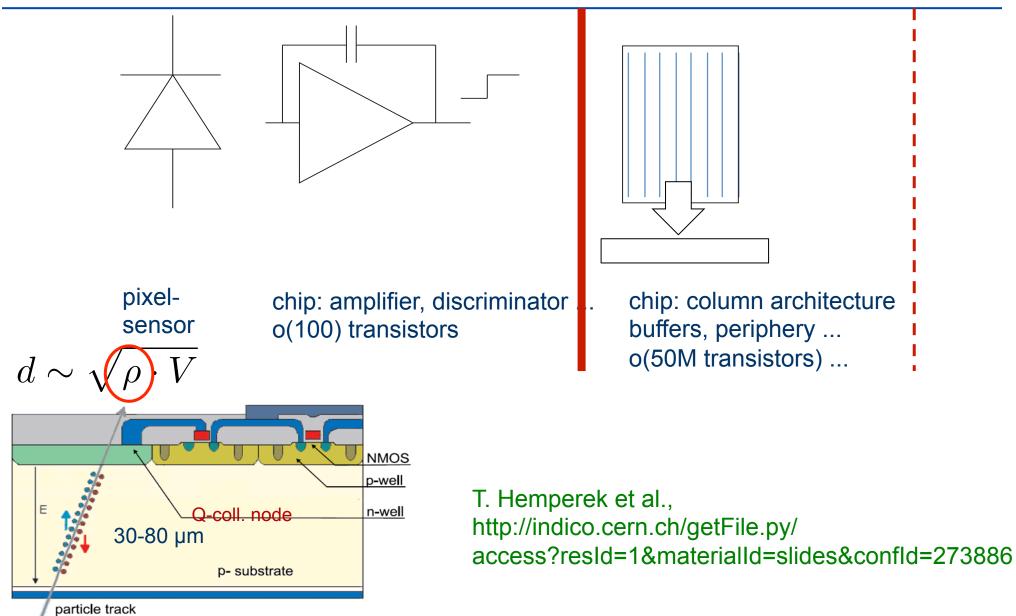

- depleted DMAPS using HR substrate and/or HV process to create depletion region:  $d \sim \sqrt{\rho \cdot V}$

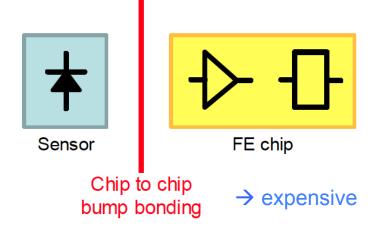

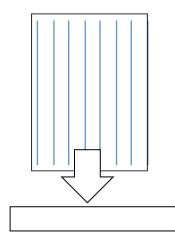

FE chip

$\rightarrow$  expensive

Sensor

Chip to chip

bump bonding

### A classification ... from HYBRID pixels to new challenges

DEPFET pixels (one in-pixel transistor)

CCPD -> DMAPS -> goal wafer to wafer

#### Rate and radiation challenges at the innermost pixel layers

#### **Hybrid Pixels**

|                                                                                                                                                                               | BX time  | Particle Rate | Fluence                               | lon. Dose             |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|---------------------------------------|-----------------------|--|--|--|--|

|                                                                                                                                                                               | ns       | kHz/mm²       | n <sub>eq</sub> /cm² per<br>I fetime* | Mrad per<br>lifetime* |  |  |  |  |

|                                                                                                                                                                               |          | K             | ·                                     |                       |  |  |  |  |

| LHC (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                                      | 25       | 1000          | 2×10 <sup>15</sup>                    | 79                    |  |  |  |  |

| HL-LHC (10 <sup>35</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                                   | 25       | 10000         | 2×10 <sup>16</sup>                    | > 500                 |  |  |  |  |

| HC Heavy lons (6×10 <sup>27</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                          | 20.000   | 10            | >1013                                 | 0.7                   |  |  |  |  |

| RHIC (8×10 <sup>27</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                                   | 110      | 3,8           | few 10 <sup>12</sup>                  | 0.2                   |  |  |  |  |

| <b>SuperKEKB</b> (10 <sup>35</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                         | 2        | 400           | ~3 x 10 <sup>12</sup>                 | 10                    |  |  |  |  |

| ILC (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> )                                                                                                                      | 350      | 250           | 10 <sup>12</sup>                      | 0.4                   |  |  |  |  |

| Iower rates<br>lower radiation       DEPFET: Belle II<br>MAPS: STAR@RHIC<br>and future<br>ALICE ITS       assumed lifetin<br>LHC, HL-LHC:<br>ILC: 10 years<br>others: 5 years |          |               |                                       |                       |  |  |  |  |

| N. Wermes, 9th Trento WS, 2/2014                                                                                                                                              | SI LAB 6 |               |                                       |                       |  |  |  |  |

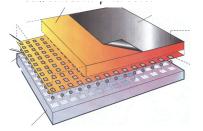

## Hybrid Pixels

- good S/N

- µm space resolution

- ~ns time resolution

- > 10 MHz / mm<sup>2</sup> rate capability

- radiation hard to 1 Grad

- radiation length per layer < 0.2%  $X_0$

- all in one monolithic pixel "chip"

- good S/N

- µm space resolution

- ~ns time resolution

- > 10 MHz / mm<sup>2</sup> rate capability

- radiation hard to 1 Grad

- radiation length per layer < 0.2% x/X<sub>0</sub>

- all in one monolithic pixel "chip"

hybrid pixels

- ✓ (fully) depleted

- ≻ ~10 µm

- ✓ obtained at LHC

- ✓ tbd for HL-LHC

- ✓ tbd for HL-LHC

- > 3.5% → 1.7%

no, hybrid

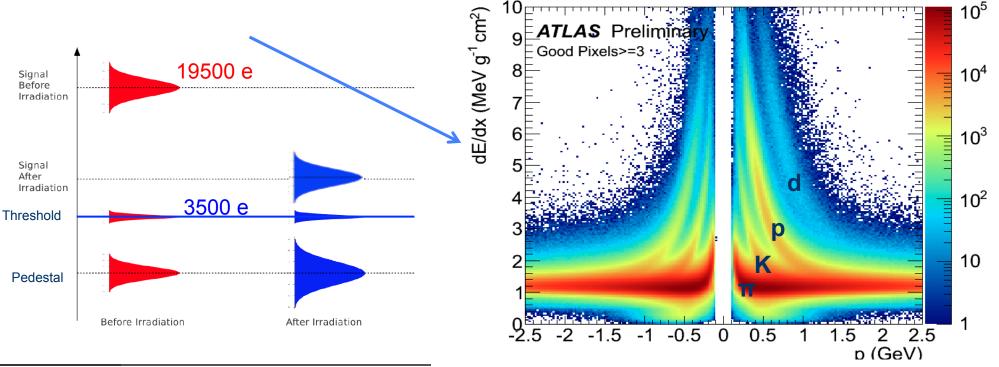

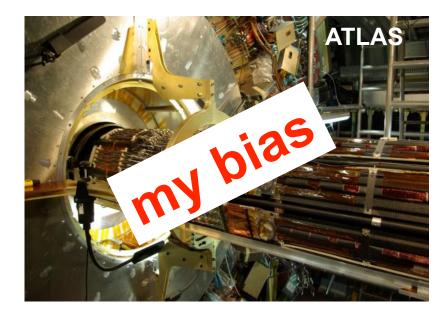

#### Performance (typical ... here ATLAS)

#### Signal of a high energy particle = 19500 e<sup>-</sup> $\rightarrow$ <10000 e<sup>-</sup> after irrad.

- □ Discriminator thresholds = 3500 e, ~40 e spread, ~170 e noise

- 99.8% data taking efficiency

- □ 95.9% of detector operational

- a ca. 10 μm x 100 μm resolution (track angle dependent)

- 12% dE/dx resolution

ATLAS: C. Gemme et al., Physics Letters B 720 (2013)

10

N. Wermes, 9th Trento WS, 2/2014

#### ... and abolutely convincing measured efficiencies

|                     | ATLAS<br>Pixels | ATLAS<br>Strips | CMS<br>Pixels   | CMS<br>Strips | LHCb   | ALICE<br>Pix | ALICE<br>SDD | ALICE<br>Strips |

|---------------------|-----------------|-----------------|-----------------|---------------|--------|--------------|--------------|-----------------|

| good<br>modules     | 95%<br>(→99%)*  | 99%             | 96.3%<br>(→99%) | 97.5%         | 99%    | 92%          | 86%          | 91%             |

| hit eff.<br>of good | >99%            | >99.5%          | >99%            | >99%          | >99.3% | >99%         | >99%         | >99%            |

| track eff.          | 99%             | >99%            | 99% ?           | 99% ?         | 98%    |              |              |                 |

| Data<br>taking      | 99.9%           | >99.1%          | 93º<br>(overall |               | 93%    |              |              |                 |

who would have thought in 2007 that one can operate such huge detectors w/o any access for more than 4 years with these efficiencies ?

after 2013/14 shut down

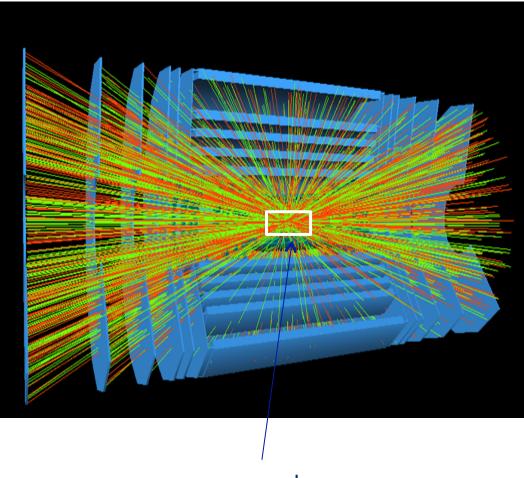

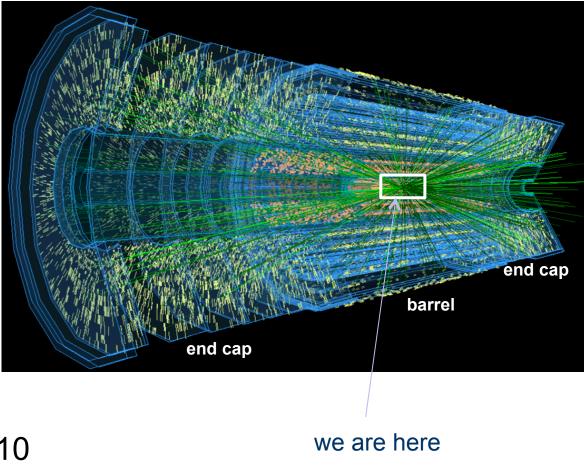

### Challenges for the LHC upgrades

### Increased luminosity requires

- higher hit-rate capability

- increased granularity

- higher radiation tolerance

- lighter detectors

Radiation hardness and rate increase compared to now

- phase 0 (2015) ≈ × 5

- phase 1 (2018) ≈ ×

- phase 2 (2022)

- ≈ × 5-10 ≈ × 10-30

we are here

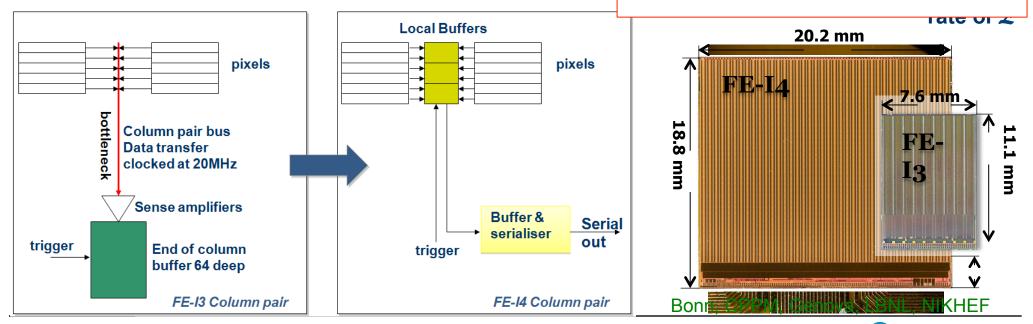

#### HL-LHC data rates

Hit inefficiency rises steeply with the hit rate

**Bottleneck:** congestion in (double) column readout

⇒more local in-pixel storage (130 nm !)

>99% of hits are not triggered

⇒ don't move them → no blocking

IBM (130 nm)

٠

0.05

0.04

0.03

0.02

0.01

**1-**ε

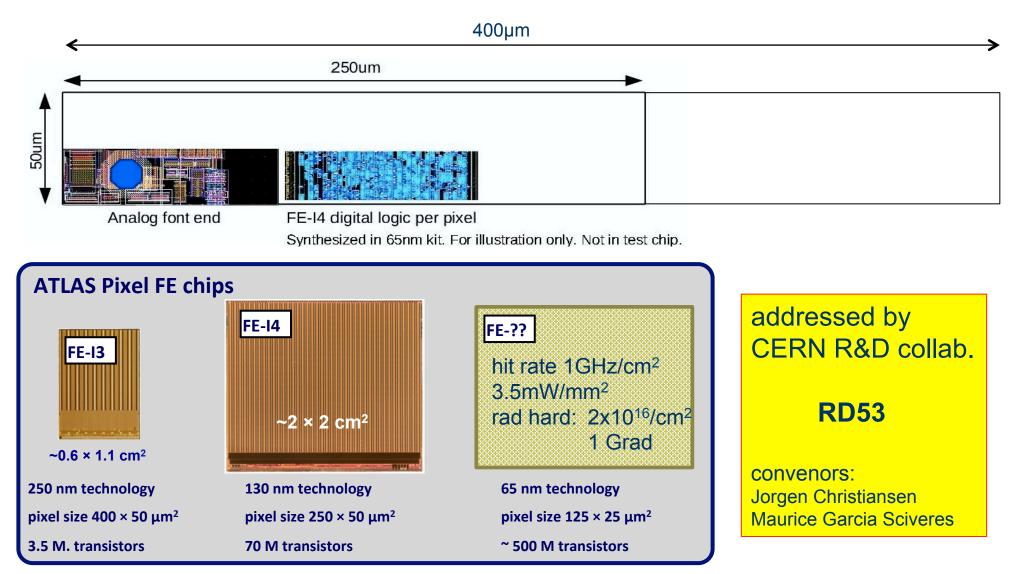

- 70 Million transistors

- 26880 pixels (50 x 250 µm<sup>2</sup>)

- lower noise than FE-I3

- lower threshold operation poss.

- higher rate compatibility

- radiation hard to >250Mrad

- 3+ years of design work w/ 8 designers

- working horse for current and future pixel R&D

13

N. Wermes, 9th Trento WS, 2/2014

M. Garcia-Sciveres et al, Nucl.Instrum.Meth. A636 (2011)

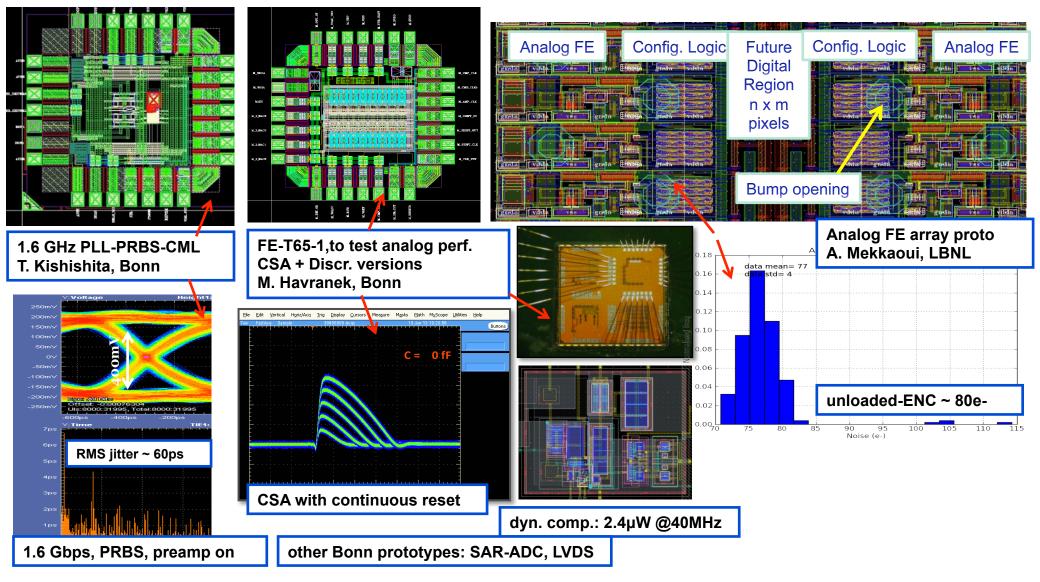

#### next generation based on 65 nm technology ...

65 nm prototypes of analog and digital circuits submitted and successfully tested

#### First ATLAS prototype IC blocks in 65nm

a problem still to solve: pMOS transistors don't stand more than 400 Mrad (CPPM)

N. Wermes, 9th Trento WS, 2/2014

15

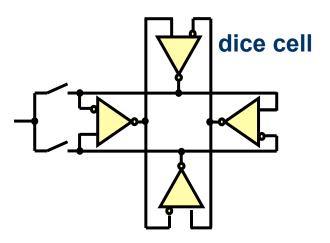

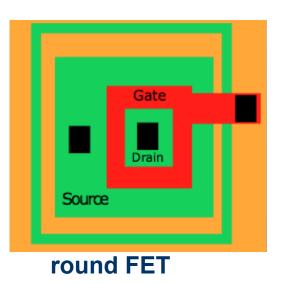

Radiation hardness to HL-LHC fluences  $\gg 10^{15}$  cm<sup>-2</sup>

□ chips are radhard ... provided that ...

- □ deep submicron technology used (130 nm  $\rightarrow$  65 nm)

- □ "round" transistors used at critical nodes

- □ SEU tolerant digital logic where needed

#### Hybrid Pixel: radhard sensor (passive) development

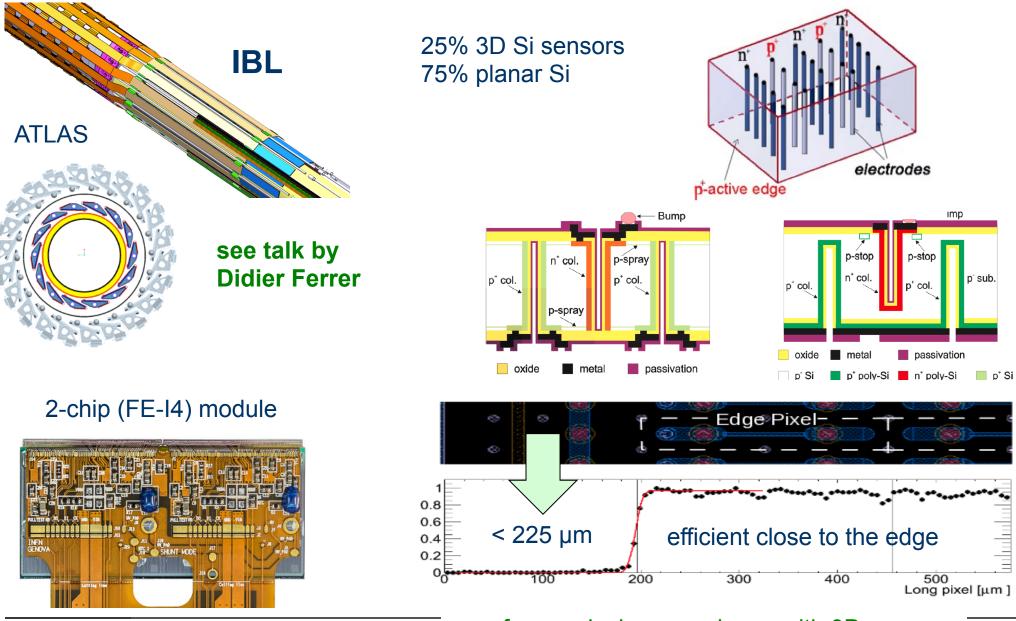

#### LHC upgrades .... ATLAS IBL (to be installed May 2014)

N. Wermes, 9th Trento WS, 2/2014

#### a so far convincing experience with 3D sensors

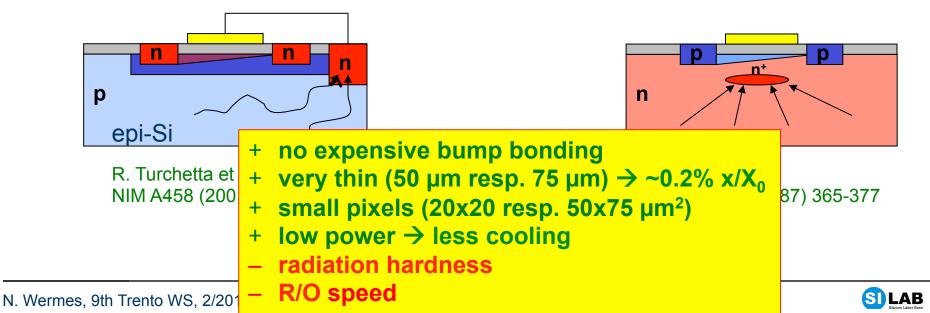

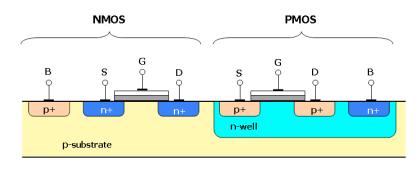

## (semi) Monolithic Pixels

#### (Semi)- Monolithic Detectors

- + really low mass

- + fewer interconnections

- slow (frame readout, rolling shutter)

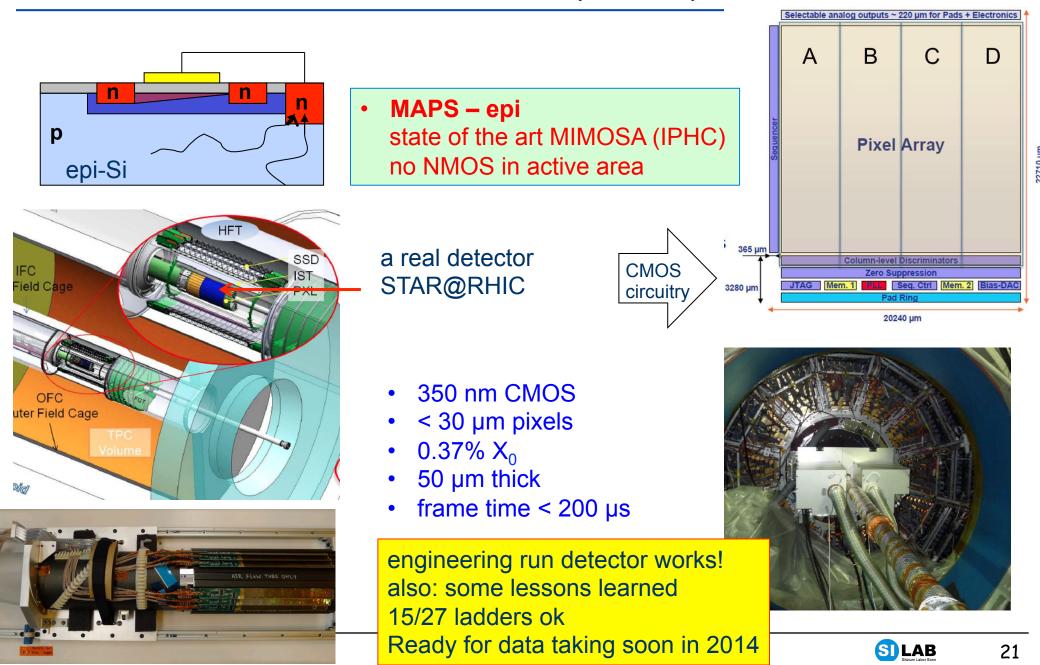

CMOS Sensors (MAPS)  $\rightarrow$  STAR CMOS with epi-layer as sensor

- + 'standard CMOS' process

- + CMOS circuitry, but limited to NMOS

- small signal, slow charge collection

- area limited by chip size

DEPFET → Belle II FET on fully depleted bulk

non standard double-sided process

20

- simple, one stage amplifier

- + large signal, fast collection

- + wafer size sensors possible

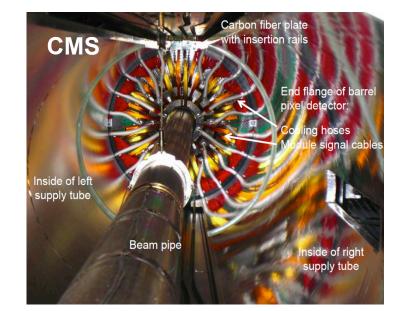

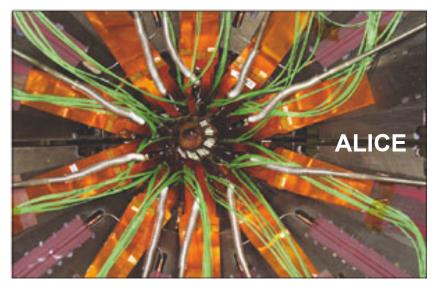

#### Monolithic Active Pixel Sensors (MAPS)

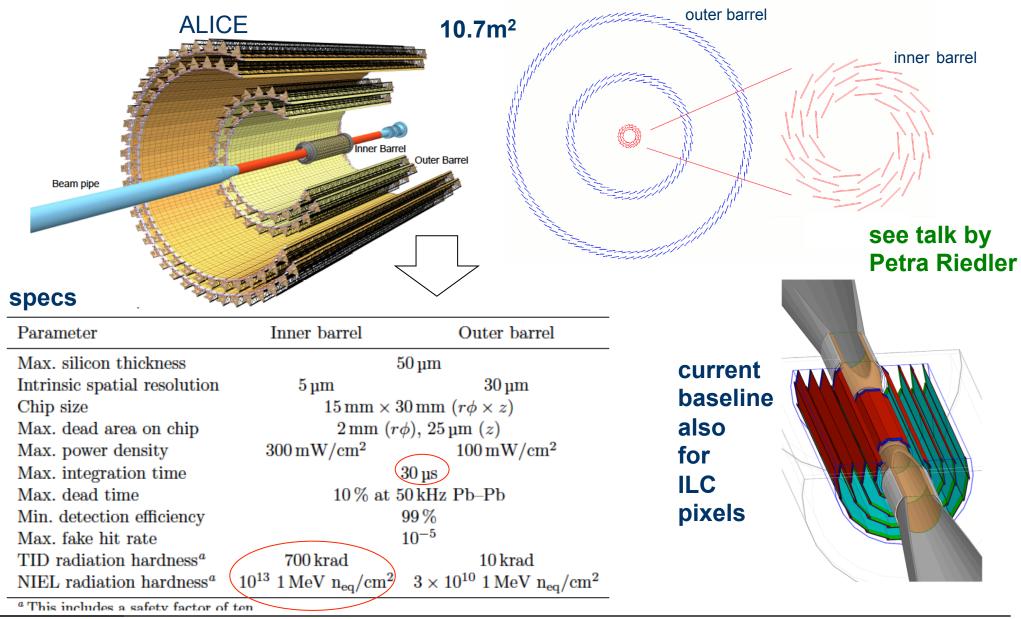

#### MAPS for ALICE (2018) and for the ILC (20xx?)

N. Wermes, 9th Trento WS, 2/2014

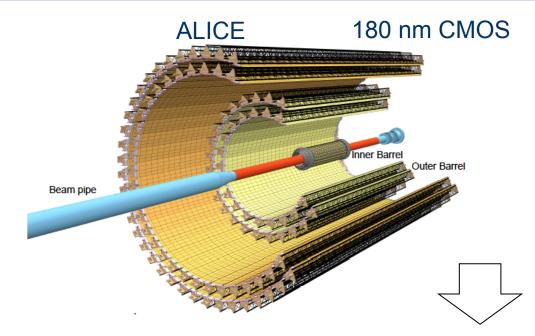

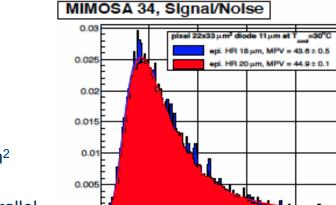

### MAPS for ALICE (2022) and for the ILC (20xx?)

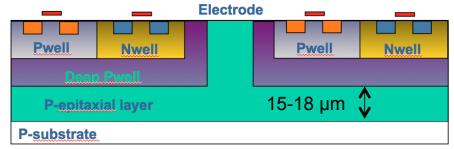

- 6 metal layers

- epi layer between  $\gtrsim$  1 k $\Omega$ cm, 15-18  $\mu$ m

- Deep Pwell shielding

TowerJazz 180 nm HR-epi (1 k $\Omega$ cm), epi layer up to 40  $\mu$ m thick

#### MISTRAL/ASTRAL (IPHC Strasbourg)

- MIMOSA type, rolling shutter archit. w/ column parallel readout

- pixel size 20x30µm, integration time ~30µs, ~250mW/cm<sup>2</sup>

- ASTRAL: in-pixel discr. & binary R/O, 10µs frame time, ~150 mW/cm<sup>2</sup>

#### CHERWELL (RAL)

- 128 pixels organized in strixels, each w/ discriminator, read out in parallel

- pixel size 20x20µm, integration time ~30µs, ~100mW/cm<sup>2</sup>

#### □ ALPIDE (CERN-INFN-Wuan)

- each pixel has its own amplifier and discriminator, data driven R/O

- pixel size 28x28 $\mu$ m, R/O time ~2-3 $\mu$ s, <100mW/cm<sup>2</sup>

## DEPFET Pixels ●

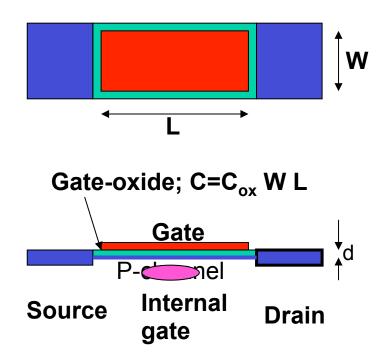

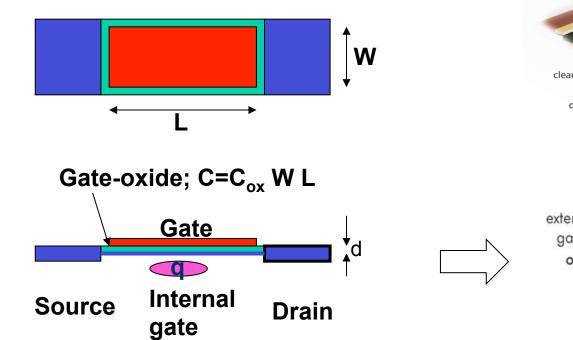

#### How does a DEPFET work?

A charge q in the internal gate induces a **mirror charge**  $\alpha$ q in the channel ( $\alpha$  <1 due to stray capacitance). This mirror charge is compensated by a change of the gate voltage:  $\Delta V = \alpha q / C = \alpha q / (C_{ox} W L)$  which in turn **changes the transistor current**  $I_d$ .

FET in saturation:

$$I_{d} = \frac{W}{2L} \mu C_{ox} \left( V_{G} + \frac{\alpha q_{s}}{C_{ox} WL} - V_{th} \right)^{2}$$

$\label{eq:lastic_ox} \begin{array}{l} I_d: source-drain current \\ C_{ox}: sheet capacitance of gate oxide \\ W,L: Gate width and length \\ \mu: mobility (p-channel: holes) \\ V_g: gate voltage \\ V_{th}: threshold voltage \end{array}$

#### **Conversion factor:**

q

$$g_{q} = \frac{dI_{d}}{dq_{s}} = \frac{\alpha\mu}{L^{2}} \left( V_{G} + \frac{\alpha q_{s}}{C_{ox}WL} - V_{th} \right) = \alpha \sqrt{2 \frac{I_{d}\mu}{L^{3}WC_{ox}}}$$

$$g_{m} = g_{q} = \alpha \frac{g_{m}}{WLC_{ox}} = \alpha \frac{g_{m}}{C}$$

#### How does a DEPFET work?

A charge q in the internal gate induces a **mirror charge**  $\alpha$ q in the channel ( $\alpha$  <1 due to stray capacitance). This mirror charge is compensated by a change of the gate voltage:  $\Delta V = \alpha q / C = \alpha q / (C_{ox} W L)$  which in turn **changes the transistor current**  $I_{d}$ .

- Internal amplification  $g_q \sim 500 \text{ pA/e}^-$

- Small intrinsic noise

- Sensitive off-state, no power consumption

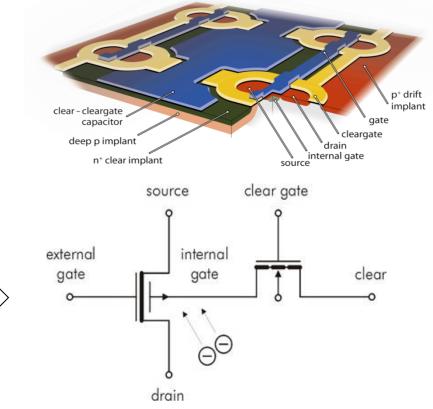

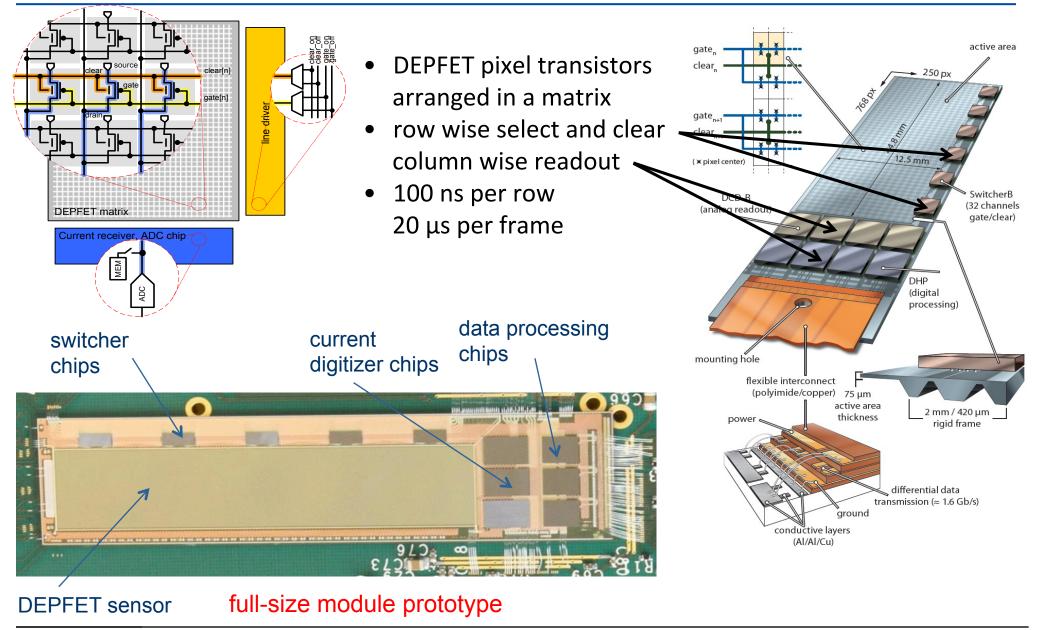

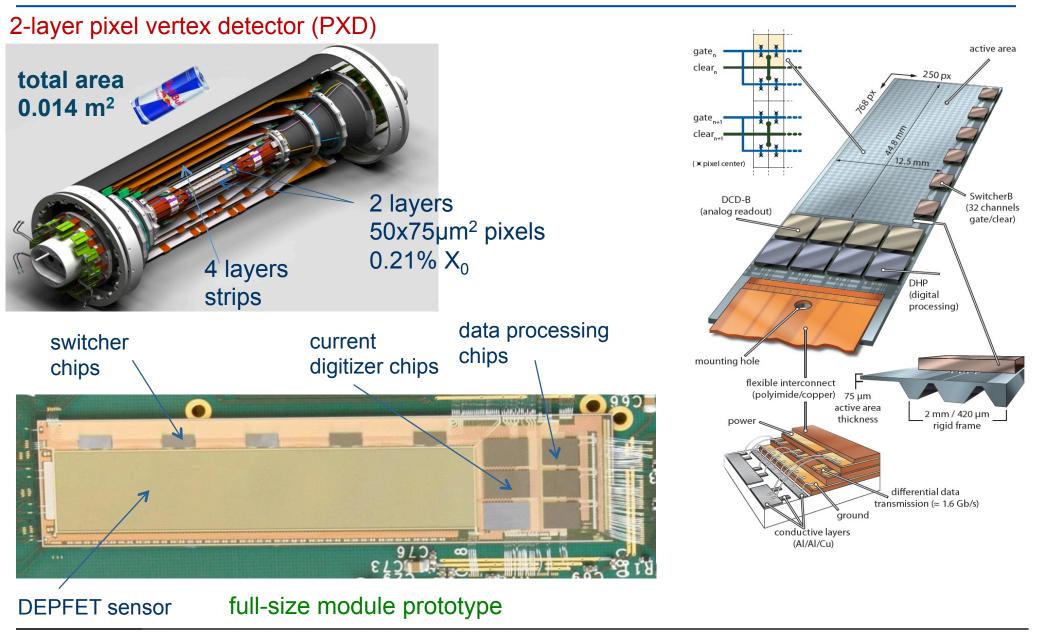

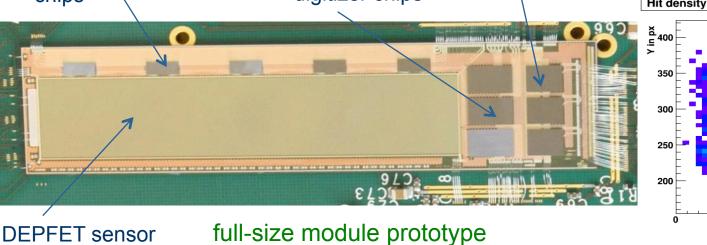

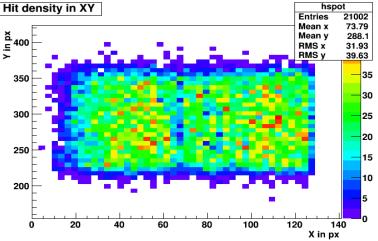

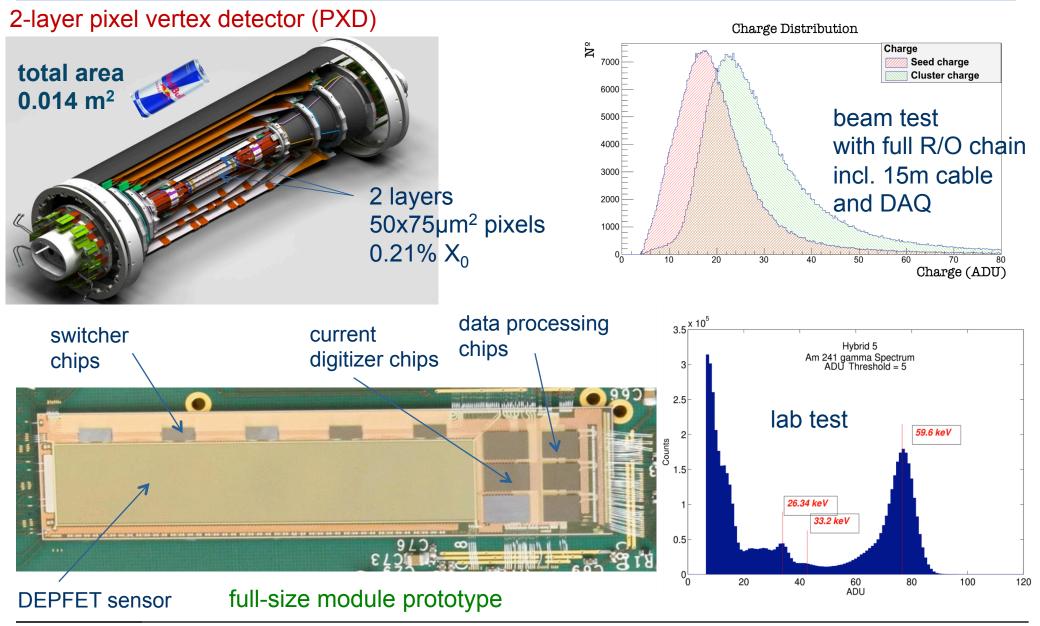

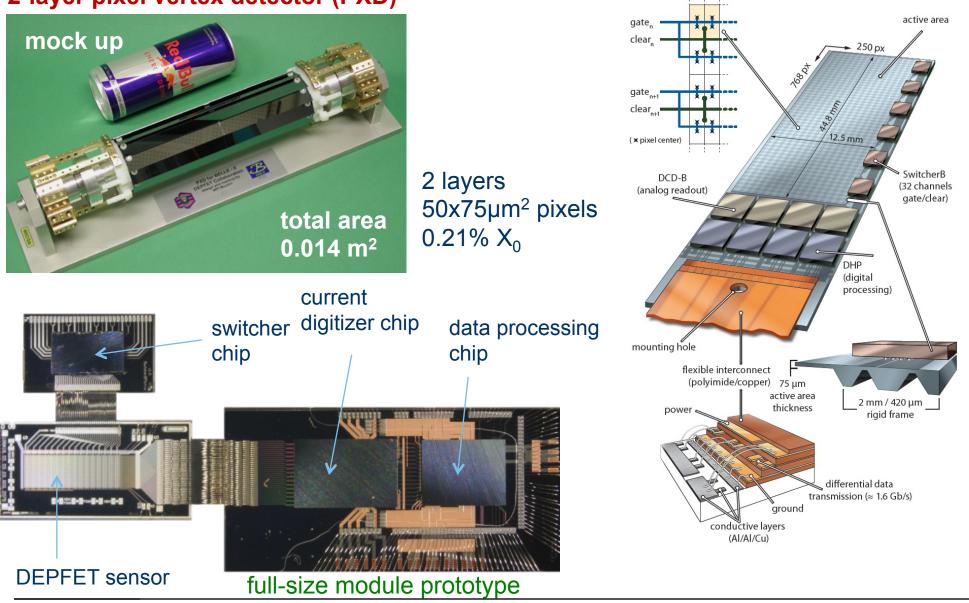

#### DEPFET PXD @ Belle II @ SuperKEKB

#### DEPFET PXD @ Belle II @ SuperKEKB

$50x75\mu m^2$  pixels 0.21% X<sub>0</sub>

switcher current data processing chips digitizer chips

#### from C. Marinas

#### DEPFET PXD @ Belle II @ SuperKEKB

N. Wermes, 9th Trento WS, 2/2014

- good S/N

- µm space resolution

- ~ns time resolution

- > 10 MHz / mm<sup>2</sup> rate capability

- radiation hard to 1 Grad

- radiation length per layer <  $0.2\% \text{ x/X}_0$

- all in one monolithic pixel "chip"

semi-monolithic MAPS/DEPFET

- > OK? / YES

- ✓ but ~1 µm is tough

- slow rolling shutter

- > < 1 MHz/mm<sup>2</sup>

- ➤ < 10 Mrad</p>

- ✓ but tough

31

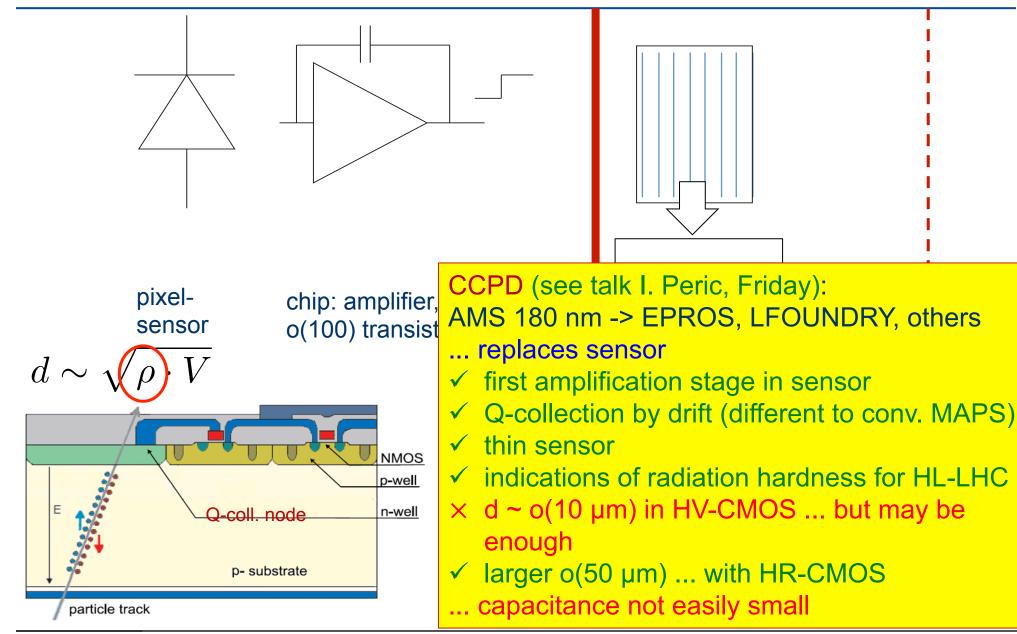

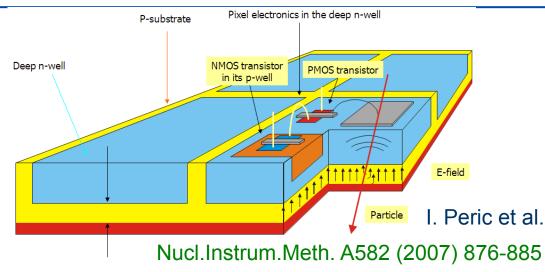

## HV and HR - Monolithic CMOS Pixels

... conventional MAPS (on epitaxial Si) not suited for pp @ LHC

... generate depletion layer under CMOS layer

... functionality wise MAPS with high resistivity epi material have the same target: full CMOS on a (thin) depleted layer

growing dollaboration: Bonn, CERN, CPPM, Geneva, Glasgow, Göttingen, Heidelberg, Liverpool, LBNL, ...

pixel-<br/>sensorchip: pixel cell: amplifier,<br/>discriminator ...<br/>o(100) transistors

chip: column/region architecture buffers, periphery ... o(>100M) transistors ... requires full CMOS i.e. pMOS and nMOS in circuit

signal  $\propto$  depletion depth

#### HV-CVMOS ... approach to generate depletion depth

N. Wermes, 9th Trento WS, 2/2014

#### HR-CVMOS ... approach to generate depletion depth

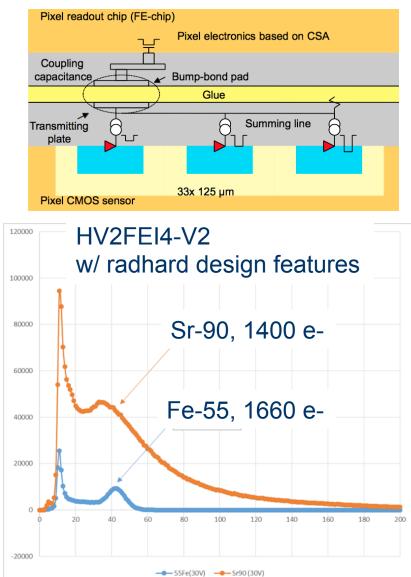

#### CCPD – approach (capacitively coupled pixel detector)

### CCPD – approach (capacitively coupled pixel detector)

- AMS 180 nm HV process (p-bulk) ... 60-100 V

- deep n-well to put pMOS and nMOS (in extra p-well)

- some CMOS circuitry possible (ampl. + discr.)

- > ~10-20 µm depletion depth → 1-2 ke signal

- various pixel sizes (~20x20 50x125 µm<sup>2</sup>)

- several prototypes

- > also strip like geometries possible

- replaces "sensor" (amplified signal) in a "hybrid pixel": any bonding (bump, glue, other...)

- big advantage: industrial CMOS process

- ☺ electrical contacts through wire bonds

- > indications of radiation hardness to ~10<sup>16</sup>  $n_{eq}$  / cm<sup>2</sup>

37

### **CCPD** with HV-CMOS

**DESY** testbeam

20

18

16

3006

7.201

179.8

2.853

11.05

Entries

Mean x

Mean y

RMS x

RMS \

38

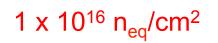

preliminary irradiation tests: using reactor neutrons 1x10<sup>15</sup> and 1x10<sup>16</sup> n<sub>eq</sub>/cm<sup>2</sup> also with protons and X-ray (862 Mrad !)

HV2FEI4 glue bonded to FEI4 and irradiated to 1 x  $10^{15} n_{eq}/cm^2$

- @RT after ~30 days / annealing

- source scan with ~25 V bias

- still alive, noise occ. ~10<sup>-10</sup>, not yet clear if this can be claimed as radiation resistant to this level

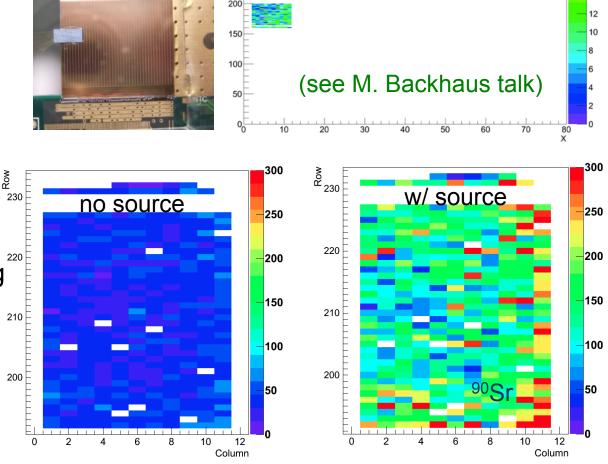

### HR-CMOS (not yet CCPDed)

#### needed

- high resistivity substrate material vendor or costumer supplied

- (several) **deep implants** for Q-collection and isolation (wells)

- backside processing for thinning and back contact

- (also strip-like geometries are possible)

#### addressed vendors

- Vendor A: 150nm,  $2k\Omega$ -cm n-bulk, **50\mum depl**.

- Vendor B: 180nm,  $1k\Omega$ -cm p-bulk + epi (various),

- Vendor C: 180nm, SOI HV proc.,100Ωcm p-bulk,

- Vendor D: 130nm, 3kΩ-cm p-bulk

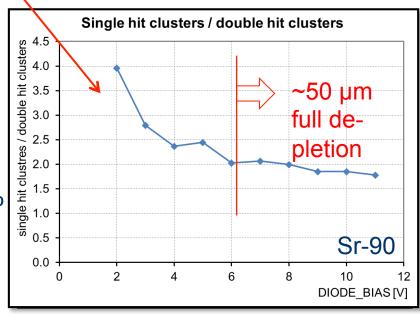

- Vendor E: 150nm, 2- 5 k $\Omega$ cm p-bulk, **>50 µm depl.**  $\rightarrow$

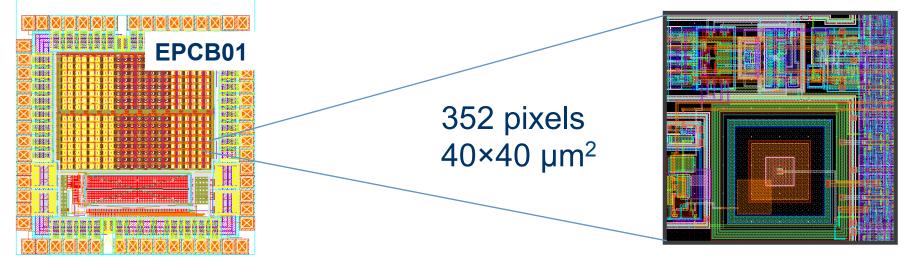

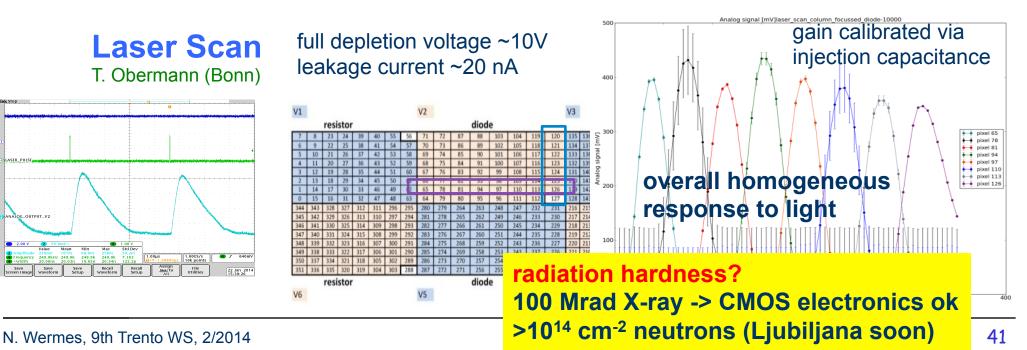

0V NMOS PMOS NWELL NWELL PWELL P-BURIED N-BURIED P-substrate - 40V (AS LOW AS POSSIBLE) standard with addn'l backside contact & high resistivity  $->>50 \mu m$  depletion depth and full CMOS logic Ö Deep Pw Deep Pwel P-substrate particle traci sideward drift to small collection diode  $\rightarrow$ MPW submitted Q4 2012 submitted Q1 2013  $\rightarrow$ MPW submitted Q1 2013  $\rightarrow$ MLM (full wafers) Q1 2014  $\rightarrow$ MLM to be subm. Q2 2014

T. Hemperek, H. Krüger (+ I. Peric, P. Pangaud et al. on Vendor D)

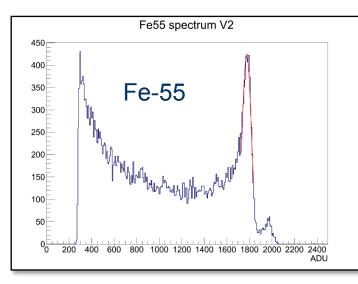

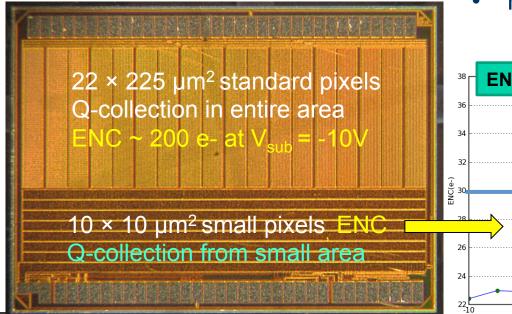

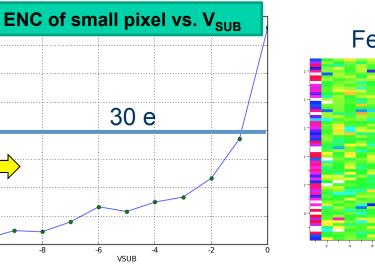

### **HR-CMOS**

~200 transistors in pixel real matrix operation

good

50µm, back side processed, full CMOS, fully depleted (>2kOhm-cm substrate)

noise (~30 e) and thres. disp. (~80 e) gain variation ~10% full depletion from cluster size saturation

### **HR-CMOS**

## ~200 transistors in pixel real matrix operation

50µm, back side processed, full CMOS, fully depleted (>2kOhm-cm substrate)

### T3MAPS: partial depletion, full CMOS (LBNL)

A. Mekhaoui, M. Garcia-Sciveres at al.

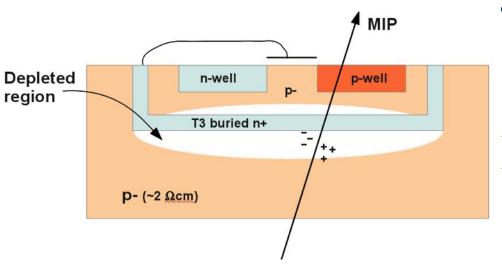

- use IBM 130 nm process (same as for FE-I4) offering also buried N-well in p-substrate to create depletion region and serve as Q-collecting electrode

- ✓ Q-collection by drift  $\rightarrow$  rad. hardness

- $\checkmark\,$  full use of CMOS and synthesized logic

- $\times$  rel. large capacitance

- × low res. bulk  $\rightarrow$  small depl. region (~5 µm)

- × perhaps more x-talk sensitive (n-well node)

- radiation program has started

N. Wermes, 9th Trento WS, 2/2014

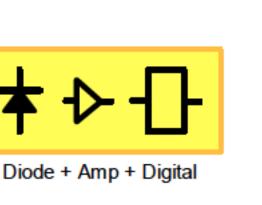

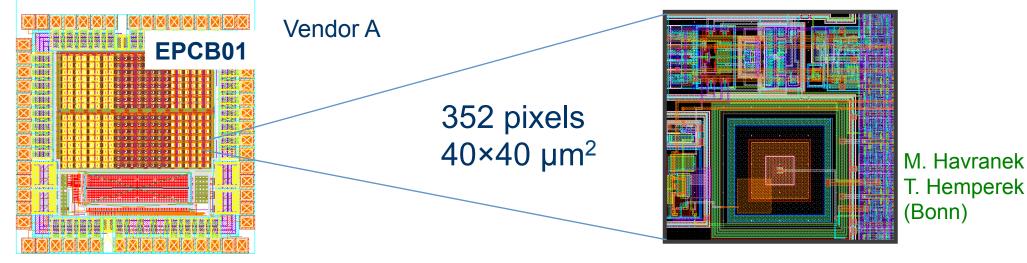

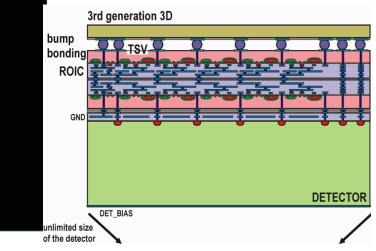

### 3D integration ...

#### ... various CMOS layers

#### **3D** integration promises

- higher granularity (smaller pixel size)

- lower power

- large active over total area ratio

- dedicated technology for each functional layer

- LAPIS Semic.

- MIT LL

- Tezzaron/ Chartered

### 3D integration ...

# FE-I3 operated through TSVs (<sup>241</sup>Am)

M. Barbero, T. Fritzsch, L. Gonella, F. Hügging et al., JINST 7 (2012) P08008

various approaches

- from (comparatively simple) post-processed TSVs with fairly large pitch, based on ATLAS FE-chips

- to via first/middle multi-Tier approaches (applied within the CMOS process plus post-processing) (CPPM/Bonn/ MPI)

- to first working 3D-integrated chip (R. Yarema et al, FNAL), VIPIC -> photon science

The "brink to a new era" currently looks like ...

□ for HL-LHC (pp collisions) at the innermost layers

- hybrid pixels possibly with some 3D integration will be able to cope with radiation and rate levels ... perhaps also DMAPS/CCPDs?

- with hybrid pixelsmaterial will not easily go below 1% X<sub>0</sub> per layer

- □ for (almost all) other applications in HEP or Heavy lons

- thin materials

- high integration

- costs (especially for large area applications) will dominate the issue.

- CMOS pixels in whatever variants

- "smart" sensor bonded to dedicated digital chip ... or ...

- fully monolithic ... or ...

open a new field which may even range into high radiation applications with lots of room for R&D in the coming years

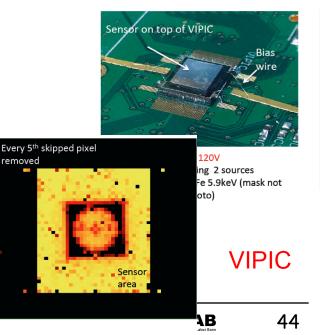

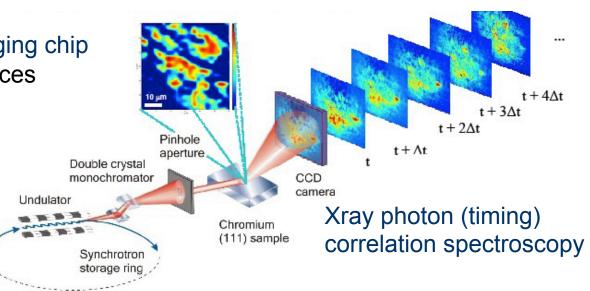

## VIPIC (Vertically Integrated Photon Imaging Chip)

- The VIPIC is designed to quickly count the number of hits in every pixel and read out the # of hits, and addresses in a dead timeless manner.

- To achieve the desired speed requires a sparsified digital readout, where only the pixels which have registered a hit are read out.

- To implement the sparsified readout requires a digital design which would not fit in the desired pixel size of 80 x 80 um along with the analog circuitry.

- Thus design was split into analog and digital design layers of equal area to meet the pixel size requirement.

- This required a large number (25) of signals to be passed between the analog and digital section of every pixel (over 100,000/chip)

- Chip operates in 2 modes

- Timed Readout of # of hits and addresses at low occupancy (~ 10 photons/cm<sup>2</sup>/10 usec)

- Imaging alternating 5 bit counters read out # of hits in each time slot without addresses (less data output without addresses)

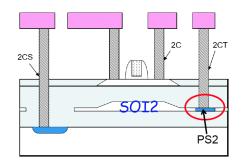

### CMOS on SOI ... Silicon on Insulator

#### the scheme

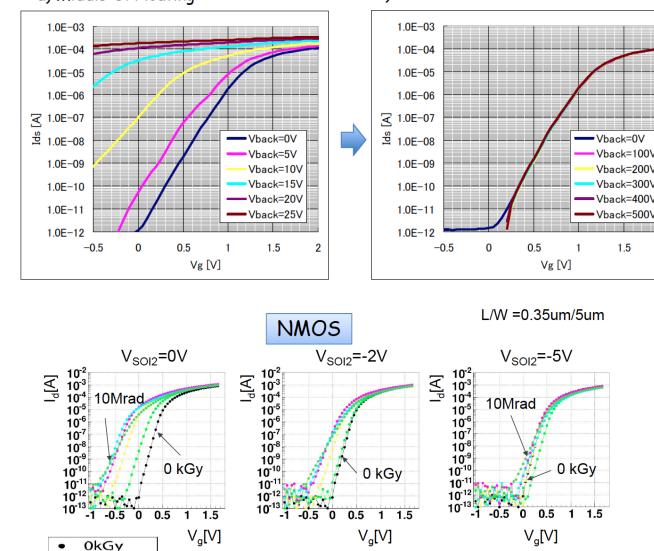

### **Double SOI**

#### Yasuo Arai (Vertex 2013)

**Back Gate Effect is** fully suppressed

0kGy

0.5kGy

1kGy

2kGy

5kGy

10kGy

20kGy

100kGy

rad. hardness ٠ still not easy

b) Middle-Si = GND

1.5

2

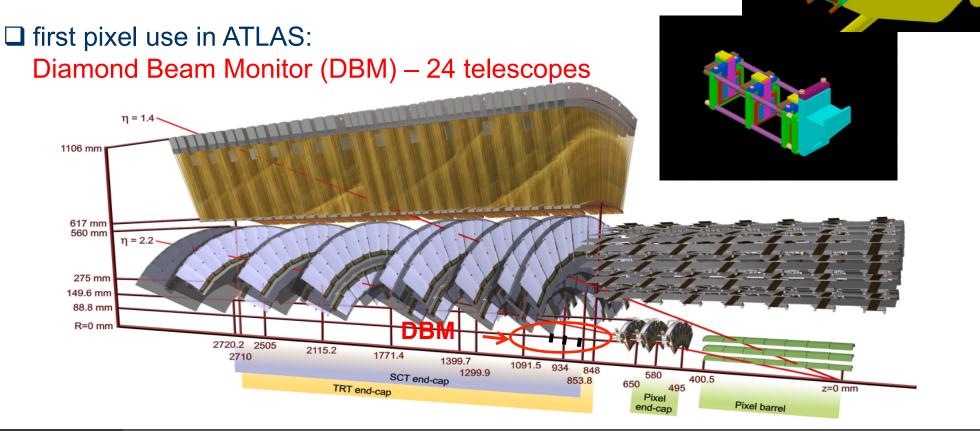

#### Today's "state of the art" of running detectors

### Challenges for the LHC upgrades

Increased luminosity requires

- higher hit-rate capability

- increased granularity

- higher radiation tolerance

- lighter detectors

Radiation hardness and rate increase compared to now

- phase 0 (2015) ≈ × 5

- phase 1 (2018) ≈ × 5-10

- phase 2 (2023) ≈ × 10-30

### **DBM** – Diamond Beam Monitor

#### □ radiation hard due to

- 5x larger band gap than Si  $\Rightarrow$  no leakage current

- strong lattice (x2 stronger than Si)  $\Rightarrow$  less NIEL damage

#### low Z

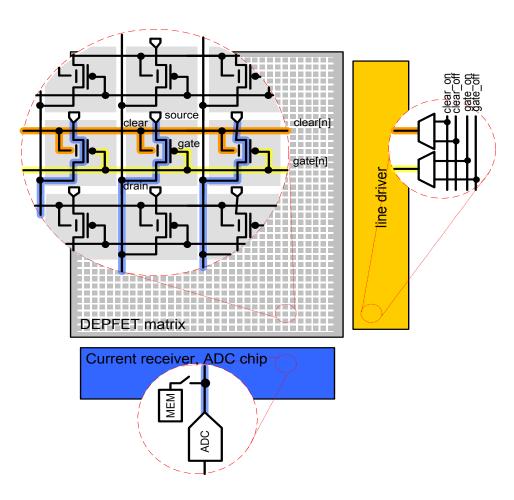

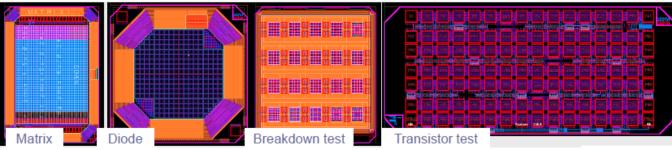

### DEPFET PXD @ Belle II @ SuperKEKB

#### 2-layer pixel vertex detector (PXD)

#### DEPFET pixel array

- DEPFET pixel transistors arranged in a matrix

- row wise select -> column wise readout of transistor (drain) currents

- Gate and clear lines need a steering chip

- Long drain readout lines to keep material out of the acceptance region

- 100 ns per row

20 µs per frame

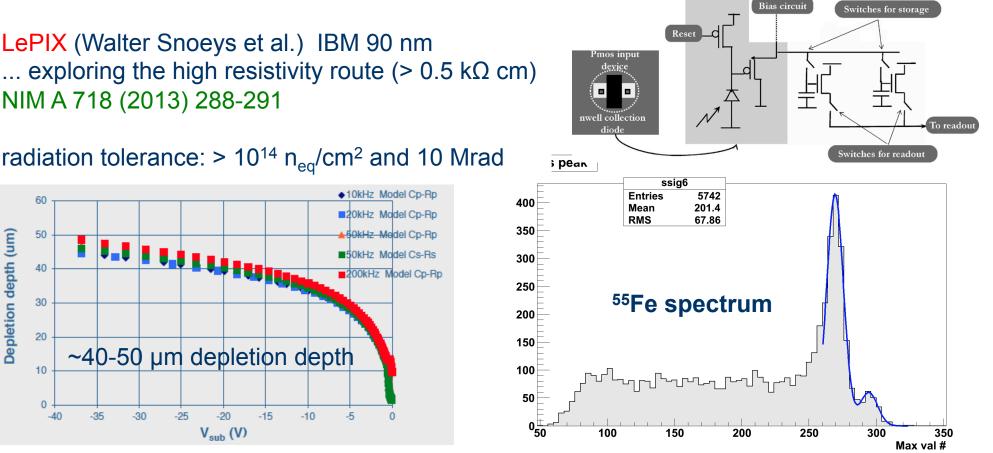

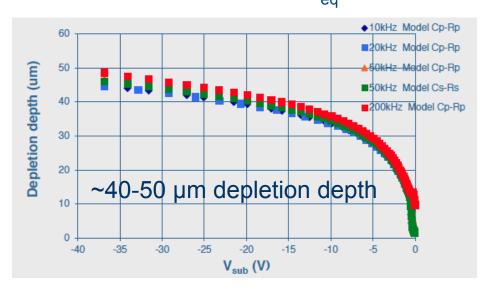

### **HR-CMOS** pixels

NIM A 718 (2013) 288-291

#### **2 transistors in pixel**

#### radiation tolerance: > $10^{14} n_{eq}/cm^2$ and 10 Mrad

LePIX (Walter Snoeys et al.) IBM 90 nm

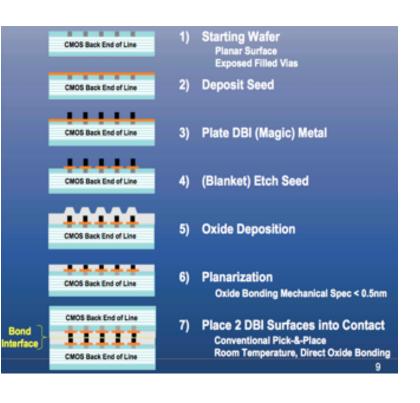

### **3D Integration**

#### Oxide-Oxide bonding (Ziptronix)

wafer level stacking and bonding has been a painful (4 year) experience (Ray Yarema, Vertex2013) ... but ... finally

N. Wermes, 9th Trento WS, 2/2014

56

#### 3D integration: A FIRST working chip with 3D integration for imaging

Every 5<sup>th</sup> skipped pixel

Sensor area

removed

a working 3D integrated chip ...

- VIPIC vertically integrated photon imaging chip

- goal: buffer and readout image time slices w/ dead time less readout

- output time stamped information

- circuitry needed would else not fit in cell area

- Detector biased at 120V

- Detector tested using 2 sources <sup>109</sup>Cd 22keV and <sup>55</sup>Fe 5.9keV (mask not shown in above photo)

#### R. Yarema et al. FNAL

57