#### UVM Test Environment for the Common Modular Architecture Static Limitations of the UVM Class Library

#### Marcel Alsdorf

14. November 2013 Beams Department, CERN

Virtual Interfaces Sequence Items Components Sequences Configuration

#### Static Limitations of UVM

UVM Environment for CMA Modules

Static Limitations of UVM

Overview of CMA Modules

# Overview of CMA Modules

UVM Environment for CMA Modules

Overview of CMA Modules

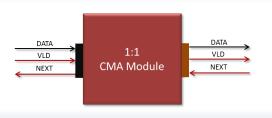

### 1:1 CMA Module

#### CMA Interface (CMI)

- DATA the actual information

- VLD/NEXT handshake between modules

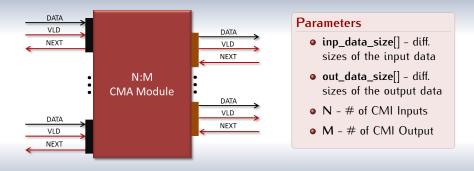

#### Parameters

- inp\_data\_size size of the input data

- out\_data\_size size of the output data

UVM Environment for CMA Modules

Overview of CMA Modules

### N:M CMA Module

(UVM Environment for CMA Modules)

Static Limitations of UVM

UVM Environment for CMA Modules

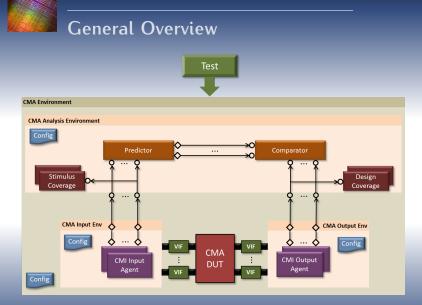

# UVM Environment for CMA Modules

UVM Environment for CMA Modules

- Able to verify any CMA module independent of internal functionality using the same Test Environment

- Include the degrees of freedom of CMA modules (parameters) as part of the Test Environment

- Decrease the necessary changes/adaptations in extended classes with every module test to a mimimum

Static Limitations of UVM

UVM Environment for CMA Modules

(UVM Environment for CMA Modules)

Static Limitations of UVM

Chapter 2.1

# Virtual Interfaces

Static Limitations of UVM

### CMI Input Virtual IF

#### interface cmi\_input\_if #(int data\_size = 32) (input clk);

logic[data\_size-1:0] rx\_data; logic rx\_vld; logic rx\_next;

// Unknown Signal Value Checks

property SIGNAL\_VALID(signal);

@ (posedge clk)

!\$isunknown(signal);

endproperty: SIGNAL VALID

VLD\_KNOWN: assert property(SIGNAL\_VALID(rx\_vld)) else `UVM\_ERROR("VLD\_KNOWN", "Signal rx\_vld unknown");

NEXT\_KNOWN: assert property (SIGNAL\_VALID(rx\_next)) else

`UVM\_ERROR("NEXT\_KNOWN", "Signal rx\_next unknown");

#### General

- connects the class world with the module world

- is an actual SV interface

#### **Protocol Assertions**

- Unknown Signal Values Checks

- Invalid States Checks

- Timing Relationship Checks

(UVM Environment for CMA Modules)

UVM Environment for CMA Modules - Sequence Items

Static Limitations of UVM

Chapter 2.2

# Sequence Items

Static Limitations of UVM

UVM Environment for CMA Modules - Sequence Items

### CMA Input Item

### **Specifics**

- used by the input agent's sequencer and driver

- is a parameterized class (factory registration different)

- defines the typical sequence item methods

| <pre>class cmi_input_item #(int unsigned data_size) extends uvm_sequence_item;<br/>`uvm_object_param_utils(cmi_input_item #(data_size))</pre> |                               |                                                                                                                                                                                                               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| //<br>// Data Fields<br>//<br>rand logic<br>rand logic [data                                                                                  |                               | vid;                                                                                                                                                                                                          |  |

| //<br>// Methods<br>//                                                                                                                        |                               |                                                                                                                                                                                                               |  |

| extern function<br>extern function<br>extern function<br>extern function<br>extern function<br>extern function                                | void<br>bit<br>string<br>void | <pre>new(string name = "cmi_input_item");<br/>do_copy (uvm_object Tha);<br/>do_compare (uvm_object Tha);<br/>convert2string();<br/>do_print(uvm_printer printer);<br/>do_record(uvm_recorder recorder);</pre> |  |

| endclass: cmi_inpu                                                                                                                            | it_item                       |                                                                                                                                                                                                               |  |

UVM Environment for CMA Modules – Sequence Items

Static Limitations of UVM

### CMA Output Item

#### lass cmi\_output\_item extends uvm\_sequence\_item; 'uvm\_object\_utils(cmi\_output\_item)

/ Data Fields

rand logic next;

#### / Method

extern function new (string name = extern function void do copy (uvm\_objec extern function bit do compare (uvm\_objec extern function string extern function void do print (uvm\_prin do record (uvm\_rec

nev(string hase = "emi\_output\_item"); do\_copy(uw\_object th); do\_compare(uwm\_object th), uvm\_comparer comparer); convert2string(); do\_print(uvm\_printerprinter); do\_record(uvm\_printerprinter);

#### ndclass: cmi\_output\_item

#### **Specifics**

- used by the output agent's sequencer and driver

- is actually not a parameterized class (no control over data lines)

- defines the typical sequence item methods

Static Limitations of UVM

UVM Environment for CMA Modules - Sequence Items

## CMA Analysis Item

### Specifics

- used by the input/output agent monitors and by the Analysis Environment

- is a parameterized class

- defines the typical sequence item methods

ass cmi\_ana\_item # (int unsigned data\_size) extends uvm\_sequence\_item; `uvm\_object\_param\_utils(cmi\_ana\_item #(data\_size))

| //<br>// Data Fields<br>//      |                                                                |

|---------------------------------|----------------------------------------------------------------|

| logic                           | vld;                                                           |

| <pre>logic[data_size-1:0]</pre> | data;                                                          |

| logic                           | next;                                                          |

| int                             | timestamp;                                                     |

| //<br>// Methods<br>//          |                                                                |

| extern function                 | <pre>new(string name = "cmi_input_item");</pre>                |

| extern function void            | do_copy (uvm_object rhs);                                      |

| extern function bit             | <pre>do_compare (uvm_object rhs, uvm_comparer comparer);</pre> |

| extern function string          | convert2string();                                              |

| extern function void            | do_print(uvm_printer printer);                                 |

| extern function void            | do_record(uvm_recorder recorder);                              |

| endolass: omi ana item          |                                                                |

(UVM Environment for CMA Modules)

Static Limitations of UVM

UVM Environment for CMA Modules - Components

Chapter 2.3

# Components

UVM Environment for CMA Modules - Components

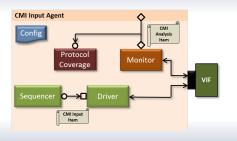

### CMI Input Agent

### Subclass Tasks

- Sequencer runs sequences based on CMI Input Items

- Driver communicates appropriately with the VIF

- Monitor monitors the VIF and forwards a CMI Analysis Item

- **Protocol Coverage** covers all State Transitions etc.

- Config configuration object of the agent

(UVM Environment for CMA Modules)

Static Limitations of UVM

UVM Environment for CMA Modules - Components

### CMI Input Agent

:lass cmi\_input\_sequencer # (int data\_size) extends uvm\_sequencer # (cmi\_input\_item#(data\_size)); `uvm\_component\_param\_utils(cmi\_input\_sequencer #(data\_size))

class cmi\_input\_driver #(int data\_size) extends uvm\_driver #(cmi\_input\_item#(data\_size)); `uvm\_component\_param\_utils(cmi\_input\_driver #(data\_size))

class cmi\_input\_monitor # (int data\_size) extends uvm\_component # (cmi\_ana\_item# (data\_size)); `uvm component param utils(cmi input monitor # (data size))

class cmi\_input\_protocol\_cov # (int data\_size) extends uvm\_subscriber # (cmi\_ana\_item # (data\_size) ; `uvm\_component\_param\_utils (cmi\_input\_protocol\_cov # (data\_size)

UVM Environment for CMA Modules - Components

### CMI Input Agent

| <pre>class cmi_input_agent extends uvm_agent;</pre> |                       |

|-----------------------------------------------------|-----------------------|

| `uvm_component_utils(cmi_input_agent)               |                       |

|                                                     |                       |

| //                                                  |                       |

| // Component Members                                |                       |

| //                                                  |                       |

| cmi_input_agent_config                              | m_cfg;                |

| cmi_input_monitor                                   | m_monitor;            |

| <pre>cmi_input_driver # (32)</pre>                  | m_driver;             |

| cmi_input_protocol_cov                              | <pre>m_protcov;</pre> |

| <pre>cmi_input_sequencer #(32)</pre>                | m_seqr;               |

| <pre>uvm_analysis_port # (cmi_ana_item)</pre>       | ap;                   |

#### **Agent Tasks**

- receives parameters through the config object

- factory-creates sub-components (<name>::create ...)

- connects sub-components with each other

- creates ports and connects them with sub-components

Static Limitations of UVM

UVM Environment for CMA Modules - Components

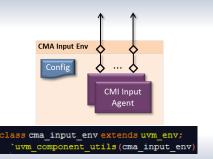

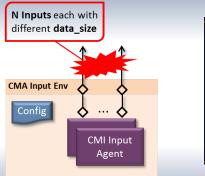

### CMA Input Environment

#### Tasks

- gets the parameters from its config object

- creates config objects for the sub-components (agents)

- factory-creates the agents

- creates and connects ports with agents

UVM Environment for CMA Modules - Components

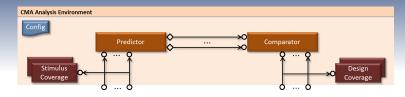

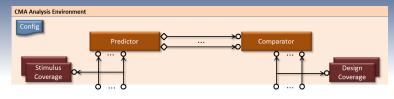

## CMA Analysis Environment

#### Input Subclass Tasks

- Stimulus Coverage module dependent coverage points concerning module stimulus

- **Predictor** user-defined model of the DUT behaviour

#### **Output Subclass Tasks**

- Design Coverage module dependent coverage points concerning module results

- Comparator compares projection with reality

## CMA Analysis Environment

UVM Environment for CMA Modules – Components

#### Input Subclass Tasks

- Stimulus Coverage module dependent coverage points concerning module stimulus

- **Predictor** user-defined model of the DUT behaviour

### **Output Subclass Tasks**

- Design Coverage module dependent coverage points concerning module results

- Comparator compares projection with reality

Each class has to be user-extended depending on Module functionality

Static Limitations of UVM

UVM Environment for CMA Modules – Components

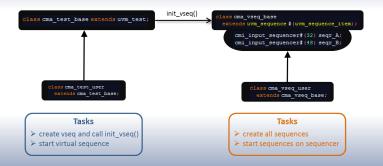

### CMA Environment

| lass cma_env extends uvm_component; |

|-------------------------------------|

| `uvm component utils(cma env)       |

|                                     |

|                                     |

| // Component Members                |

| · //                                |

cma\_env\_config

cma\_ana\_env

cma\_input\_env

cma\_output\_env

m\_cfg; m\_cma\_ana\_env; m\_cma\_input\_env; m\_cma\_output\_env;

#### Tasks

- highest-level environment

- receives parameter through config objects

- creates config objects for sub-enviroments

- builds sub-environments and connects them

(UVM Environment for CMA Modules)

Static Limitations of UVM

UVM Environment for CMA Modules - Sequences

Chapter 2.4

# Sequences

UVM Test Environment for the Common Modular Architecture 20

UVM Environment for CMA Modules – Sequences

### Overview

### **Standard Sequences**

- are objects and therefore they are not part of the initial phasing (build/connect)

- created and destroyed during runtime

- are running on a sequencer

- utilize sequence items as communication objects

- configuring sequences through the config\_db is limited and only possible through a sequencer

#### Virtual Sequences

- are objects as well

- distributes, creates and destroys other sequences

- can run on a virtual sequencer (not recommended)

- their interactions are defined in a body() method

- can not receive informations from the config\_db

Static Limitations of UVM

UVM Environment for CMA Modules - Sequences

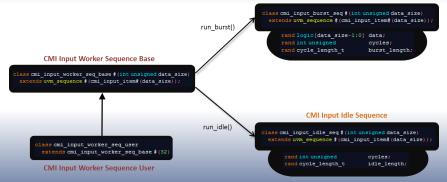

## CMI Input Sequence Hierarchy

Worker Sequences (part of the Sequence Package) **API Sequences**

(part of the Agent Package)

#### **CMI Input Burst Sequence**

UVM Environment for CMA Modules - Sequences

Static Limitations of UVM

## CMI Input Sequence Hierarchy

#### **Virtual Sequences**

(UVM Environment for CMA Modules)

Static Limitations of UVM

UVM Environment for CMA Modules – Configuration

Chapter 2.5

# Configuration

### Overview

- convenience layer on top of the resource\_db (adds hierarchical path as scope)

- using the resource\_db is not recommended

- should be used to transfer virtual interface pointers and configuration information to **components** during initial phasing

- this should be done mainly by using configuration objects

- can be used dynamically during the run\_phase (objects)

- but calling set() or get() at runtime is expensive and should be avoided

- therefore using the config\_db in objects is not recommended

Static Limitations of UVM

UVM Environment for CMA Modules - Configuration

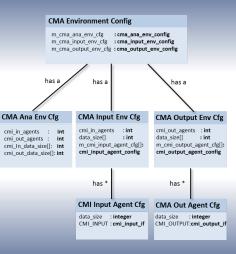

## CMA Component Configuration Tree

Static Limitations of UVM

UVM Environment for CMA Modules - Configuration

## **Configuring Sequences**

Should be avoided, but if necessary:

get\_full\_name()

uvm\_config\_db#(TYPE)::get(null, this.get\_full\_name(), field", field);

- sequences do not have hierarchy until they have been started on a sequencer

- once started, get\_full\_name() will return a hierarchy string for your sequence

- this string either includes the parent sequence's hierarchy or the hierarchy of the sequencer that the sequence was started on

UVM Environment for CMA Modules

(Static Limitations of UVM)

Static Limitations of UVM

# Static Limitations of UVM

(Static Limitations of UVM)

Static Limitations of UVM

### Analysis Items

// Declarations that are possible //

#### // Locked number of inputs/outputs analysis\_port # (my\_item# (32)) m\_ana\_port[0];

analysis\_port # (my\_item#(16)) m\_ana\_port[1]; analysis\_port # (my\_item#(42)) m\_ana\_port[2]; analysis\_port # (my\_item#(11)) m\_ana\_port[3];

/Locked data\_size \_analysis\_port # (my\_item# (32) ) m\_ana\_port[cmi\_in\_agents-1] ;

// Declarations that aren't possible //

//No <<for generate>>loop or a preprocessor <<for>> loop

GENERATE FOR (int : i < cmi\_in\_agents, i++)

analysis port #(data\_size\_vec[i]) m\_ana\_port[i]

END GENERATE</pre>

....

ndclass:my env

UVM Environment for CMA Modules

(Static Limitations of UVM)

Static Limitations of UVM

### Analysis Items

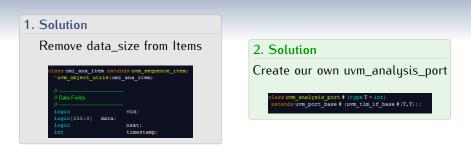

#### 1. Solution

Remove data\_size from Items

| <pre>class cmi_ana_item extends uvm_sequence_item;<br/>`uvm_object_utils(cmi_ana_item)</pre> |       |                     |  |

|----------------------------------------------------------------------------------------------|-------|---------------------|--|

| //<br>// Data Fields<br>//                                                                   |       |                     |  |

| logic<br>logic[255:0]                                                                        | data; | vld;                |  |

| logic<br>int                                                                                 |       | next;<br>timestamp; |  |

UVM Environment for CMA Modules

(Static Limitations of UVM)

Static Limitations of UVM

### Analysis Items

| 1. Solution |

|-------------|

|-------------|

| Remove | data_ | _size | from | Items |

|--------|-------|-------|------|-------|

|--------|-------|-------|------|-------|

| <pre>class cmi_ana_item extends uvm_sequence_item;<br/>`uvm_object_utils(cmi_ana_item)</pre> |       |                     |  |

|----------------------------------------------------------------------------------------------|-------|---------------------|--|

| //<br>// Data Fields<br>//                                                                   |       |                     |  |

| logic<br>logic[255:0]                                                                        | data; | vld;                |  |

| logic<br>int                                                                                 |       | next;<br>timestamp; |  |

#### 2. Solution

Create our own uvm\_analysis\_port

lass uvm\_analysis\_port # (type T = int)

extends uvm\_port\_base # (uvm\_tlm\_if\_base # (T,T));

UVM Environment for CMA Modules

(Static Limitations of UVM)

Static Limitations of UVM

### Analysis Items

### Both Solution are reasonably unclean and cumbersome

Static Limitations of UVM

### Virtual Sequencer

int cmi in agents;

// Seqeuncer

// Declarations that are possible //

#### //Locked number of sequencer

cmi\_input\_sequencer#(32) m\_inp\_seqr[0]; cmi\_input\_sequencer#(48) m\_inp\_seqr[1]; cmi\_input\_sequencer#(54) m\_inp\_seqr[2];

```

// Locked data_size

```

cmi\_input\_sequencer#(32) m\_inp\_seqr[cmi\_in\_agents-1];

// Declarations that aren't possible //

#### **Declaring Sequencers**

- leads to same static declaration problem as seen before

- virtual sequence cannot receive informations from the config\_db

#### Solution

Rewrite the complete virtual sequence by hand for every test (no base class)

Static Limitations of UVM

### **General Solution**

### Factory ?

- Idea: extend a non-parameterized base class with a parameterezied version

- but an instance of a class can only be overwritten when it is being factory-created somewhere

- uvm\_analysis\_port can not be factory created (not part of the hierarchy)

- sequences are also actually not part of the hierarchy, but there are ways to bypass this limitations

- still cumbersome and unclean

Static Limitations of UVM

### **General Solution**

### Factory ?

- Idea: extend a non-parameterized base class with a parameterezied version

- but an instance of a class can only be overwritten when it is being factory-created somewhere

- uvm\_analysis\_port can not be factory created (not part of the hierarchy)

- sequences are also actually not part of the hierarchy, but there are ways to bypass this limitations

- still cumbersome and unclean

- 2 Code Generator

- Result: cleaner classes in the test environment

- bypasses those static limitations of SV

- possibilities to generate main structures of the user-extended classes

Static Limitations of UVM

### **General Solution**

#### • Factory ?

- Idea: extend a non-parameterized base class with a parameterezied version

- but an instance of a class can only be overwritten when it is being factory-created somewhere

- uvm\_analysis\_port can not be factory created (not part of the hierarchy)

- sequences are also actually not part of the hierarchy, but there are ways to bypass this limitations

- still cumbersome and unclean

- Ode Generator

- Result: cleaner classes in the test environment

- bypasses those static limitations of SV

- possibilities to generate main structures of the user-extended classes

#### Thank you for your attention!

30 / 3<sup>.</sup>