# SystemVerilog and UVM for the ABC system verification

Francis Anghinolfi

#### OUTLINE

- + The ABC verification environments

- SystemVerilog and UVM

- + UVM techniques for the ABC system

- + Development plans

- + SystemVerilog for ABC system?

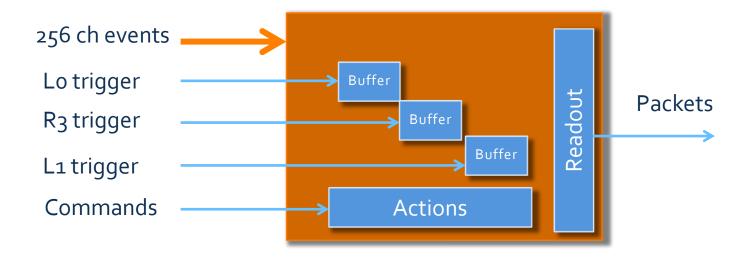

+ What is ABC function (in short)

Verification does (in short):

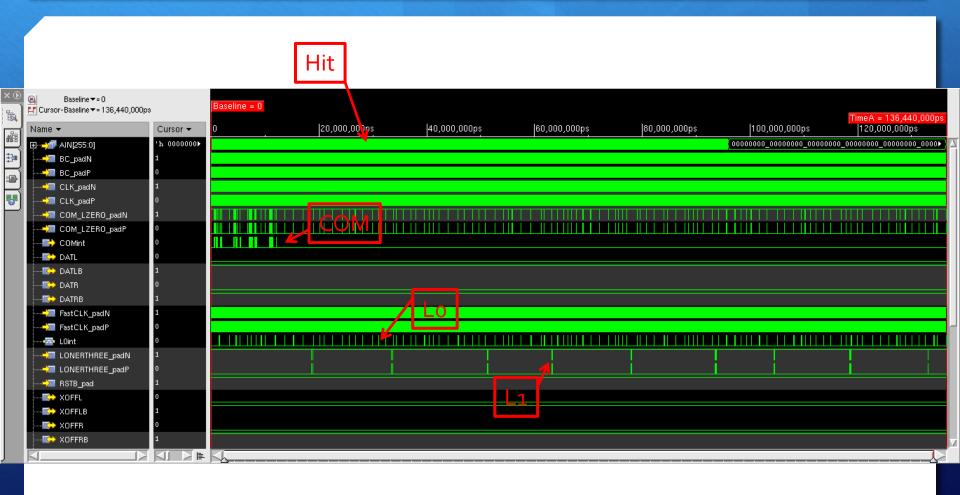

Stimulation of hits, triggers, commands

Analysis of packets (in relation to Stimulations)

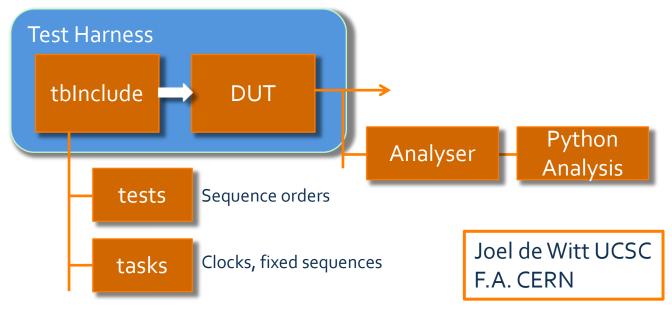

+ One of the verification setup (verilog only based)

Verification does (in short):

Stimulation of hits, triggers, commands, precoded time relations Analysis of packets (in relation to Stimulations)

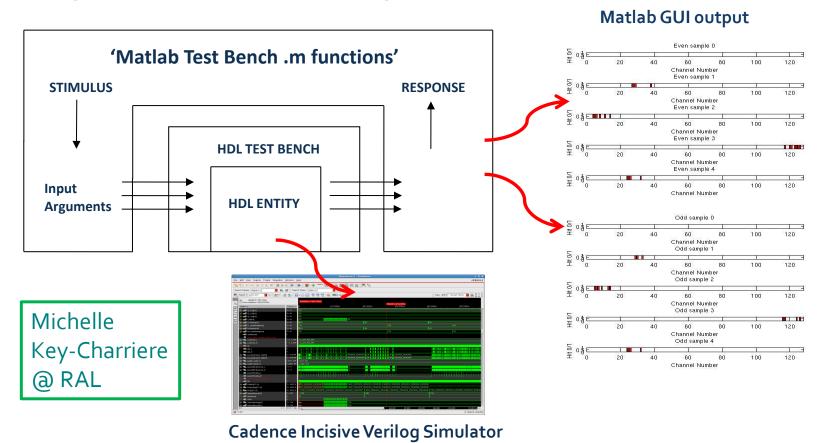

+ Algorithm Development Using Matlab and Cadence Incisive

#### + Object Oriented Software Trace

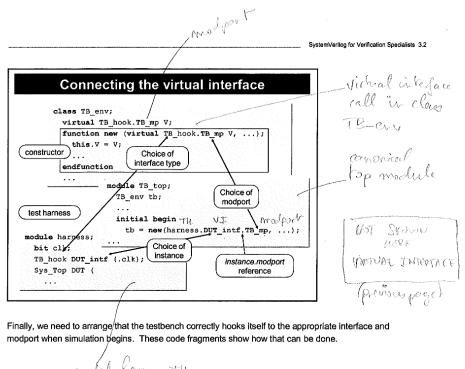

+ MY starting point : the SystemVerilog training course ....

(Sorry Mr. Fitch! It was a wonderful course!)

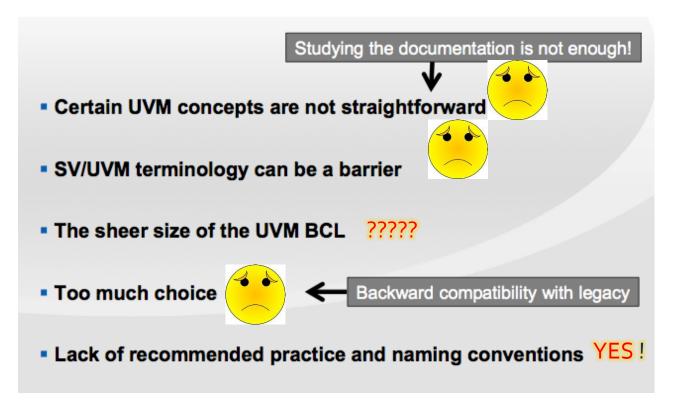

+ And later on about UVM .... (from an Accelera course slide)

+ At least I have seen the interest of THIS feature in SV/UVM:

- In the spirit of SV, this has to do with test & functionality coverage, through generation of random data and address sets.

- For exp. systems the feature becomes naturally useful as experiments have to deal with random (physics) data AND random triggers time distributions ((with constraints ©)...)

+ So generating random physics data set is an easy trick

```

rand int unsigned hit;

constraint Hits (hit dist {[o,255]};)

for (int i=o;i<256;i++)

begin

if (i == hit) hitbus[i] = 1;

else

hitbus[i] = o;

end

```

+ What about getting a fix pattern data?

rand bit [57:0] como;

constraint busyo {como[7:0] dist {[0:255]}; }

constraint busy1 {como[15:8] dist {[0:255]}; }

sequence

transaction

Data = { 4'h3, 4'ho, 4'ho, 4'ho, 4'h1, 4'hf, 3'ho,LEFT, 4'h1};

`uvm\_do\_with (req, {como[57:0] == {HEADER, HCCField, HCCID, ABCID, RegAdress, WRITE, Data}; start\_data < 100;})

Como is 58 bits word : 2^58 = 288230376151711744, seems beyond SV limits

14 Nov 2013

System Verilog MiniWorkshop

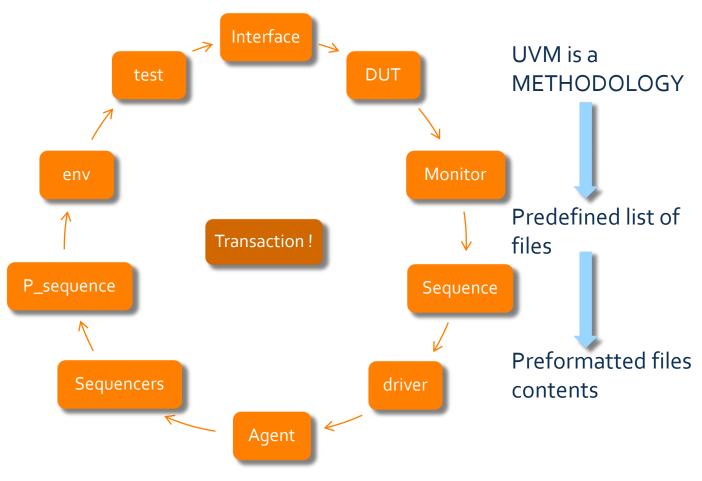

What appeared is that UVM is a sort of wrapper formalism for SystemVerilog

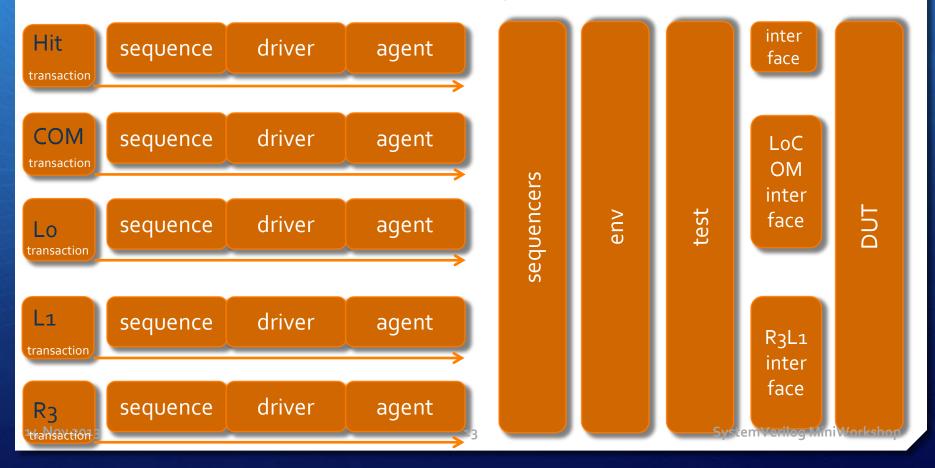

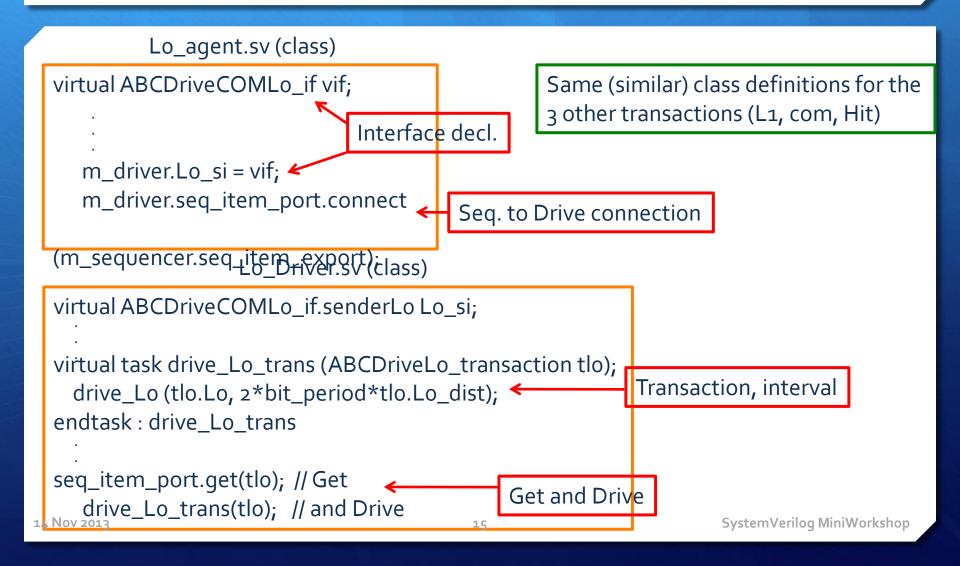

+ For ABC the interest is in running parallel transactions

```

HitBus_if si (clk);

ABCDriveCOMLo_if comLo_si (clk);

ABCDriveR<sub>3</sub>L<sub>1</sub>_if R<sub>3</sub>L<sub>1</sub>_si (clk);

ABC test1.sv (class)

task main_phase(uvm_phase phase);

phase.raise_objection(this);

begin

// create and start the virtual sequence

virtual_seq vseq;

vseq = virtual_seq::type_id::create();

vseq.start(m_env.m_virtual_seqr);

end

phase.drop_objection(this);

endtask: main_phase

```

ABC\_top.sv (module)

```

ABC_env.sv (class)

```

L1\_sequence.sv (class)

11bits sequence, 3 bits Header, 8 bits binary count number, Interval btw. sequences with exponential distribution

L1\_transaction.sv (class)

```

rand bit [10:0] L1C;

constraint busy9 {L1C dist {[0:2047]}; }

rand bit pick_L1; // Select First Level Trigger signal

constraint busy10 {pick_L1 dist {0 :/ 9, 1 :/ 1}; } // 10% at 1

rand int unsigned L1_dist;

constraint val1 {L1_dist dist {[200:400]}; }

```

Variables declarations with constraints

## Development plans

- + Develop the control & input sequences close to real case

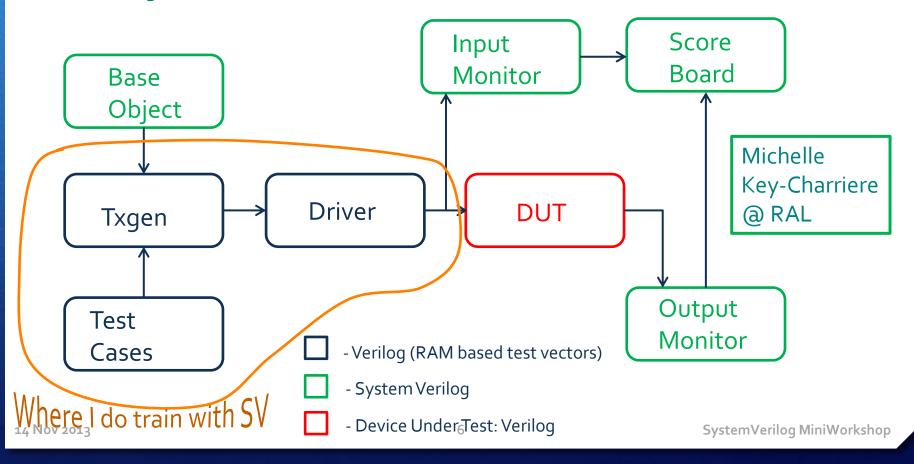

- + Join with the existing setup for ABC+HCC system, developed at RAL by M. Key-Charriere

- + Explore the random nature of stimuli to verify/validate the response of the ABC/HCC to false commands, bit errors, disordered triggers etc ...

## SV/UVM for ABC system?

- + Could I have described the same sequences with std. verilog?

- + My experience : a veeery looooong training process

- + UVM methodology saved me: I think I could not do the job with SystemVerilog without the UVM formalism

- + The monitor/checker options did not look so attractive, however I did not do much work there

- + Pay off for the effort ....?