# DAREI80X

### A 0.18UM MIXED-SIGNAL RADIATION-HARDENED LIBRARY FOR LOW-POWER APPLICATIONS

G. Franciscatto, imec E. Geukens, ICSense

### OUTLINE

- Background

- The DARE solution

- MicroElectronics Platform

- DAREI80X libraries

- DAREI80 vs. DAREI80X

- Summary

- Future work

## BACKGROUND

- Commercial IC technologies for radiation applications

- Low cost / high yield

- High speed

- Low power

- Thin-gate oxide => high TID tolerance

- Commercial libraries

- Standard design flow

- Designed for highest density

- Highly sensitive to SEL & SEE

- Solution tailored for radiation applications is needed

ThalesAlenia

## **THE DARE SOLUTION**

- Design Against Radiation Effects

- DAREI80 in UMC 0.18µm technology

- Silicon-proven radiation-hardened library

- General radiation applications (> IMrad)

- ELT devices => high power consumption

- No non-volatile memory

- No high-voltage (BCD) devices

AMICSA 2014 JUNE 29 - JULY I CERN GENEVA (CH)

## **MICROELECTRONICS PLATFORM**

- Libraries, back-end, manufacturing and test services for radiation applications

- DARE180X

- <u>New</u> radiation-hardened mixed-signal library package

- Low-power solution for space applications

- XFAB 0.18µm (XH018)

- Inherent TID tolerance >100 krad

- Triple-well devices

- High-Vt and low-Vt transistors

- High-voltage BCD devices

- Non-volatile memory

- European foundry

## **MICROELECTRONICS PLATFORM**

- Radiation-hardening by design

- TID tolerance > 100 krad

- No ELT needed

- SEL hardening > 70 MeV.cm<sup>2</sup>/mg

- Guard-rings

- SEU/SET hardening > 60 MeV.cm<sup>2</sup>/mg

- Redundant architectures (DICE)

- Hardening-by-drive-strength

**I**Csense

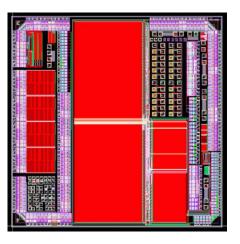

## DAREI80X LIBRARIES

- CORE standard cell library

- Standard combinational cells (variable LETth)

- SET-hardened combinational cells (LETth > 60 MeV.cm<sup>2</sup>/mg)

- Clock and set/reset trees

- Hardening-by-drive-strength

- SEU-hardened sequential cells (LETth > 60 MeV.cm<sup>2</sup>/mg)

- DICE architecture

- P&R cells

### Cesa

halesAlei

- Two compatible implementations

- Low-power core library (DARE180X)

- High-speed core library (DARE180XL)

**I**Csense

### DAREI80X LIBRARIES

- ► I/O library

- 3.3V and 5V-tolerant digital I/Os

- SET-hardened inputs

CERN

- 3.3V and high-voltage analog I/Os

- SRAM blocks

- 5 dual-port SRAM

- MBU insensitive

- SEU immune when used with an EDAC

Cesa

####

### DAREI80X LIBRARIES

SET-hardened analog blocks

CERN

- PLLs

- Bandgaps

- Oscillators

- ADC/DAC

- Linear regulators

- Other analog auxiliary blocks (comparators, PGAs, ...)

####

### DAREI80VS. DAREI80X

|                   | DARE180                           | DARE180X                  |  |

|-------------------|-----------------------------------|---------------------------|--|

| Technology        | UMC 0.18µm                        | XFAB 0.18µm (HV)          |  |

| Supply range      | 1.8V/3.3V ±10%                    | 1.8V/3.3V ±10%            |  |

| Temperature range | -55°C ~ 125°C                     | -55°C ~ 125°C             |  |

| TID tolerance     | >   Mrad                          | > 100 krad                |  |

| Raw gate density  | 25 kGates/mm <sup>2</sup>         | 59 kGates/mm <sup>2</sup> |  |

| Core cells        | 130                               | 86                        |  |

| I/O cells         | 83                                | 48                        |  |

| SRAM              | Single/dual-port<br>SRAM compiler | 5 dual-port blocks        |  |

Cesa

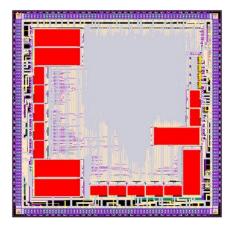

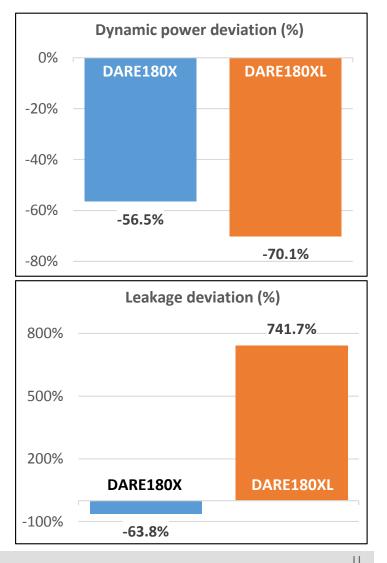

## DAREI80VS. DAREI80X

- Synthesis comparison

- Real design case

- Reference: DARE180

- Dynamic power

- Switching power optimized

- Smaller input capacitances

- Internal power reduced

- DICE flip-flops

### Cesa

- ThalesAlenia

AMICSA 2014

- Leakage power

- DICE flip-flops consume less

CERN

GENEVA (CH)

- Device dependent

JUNE 29 - JULY I

© IMEC 2014

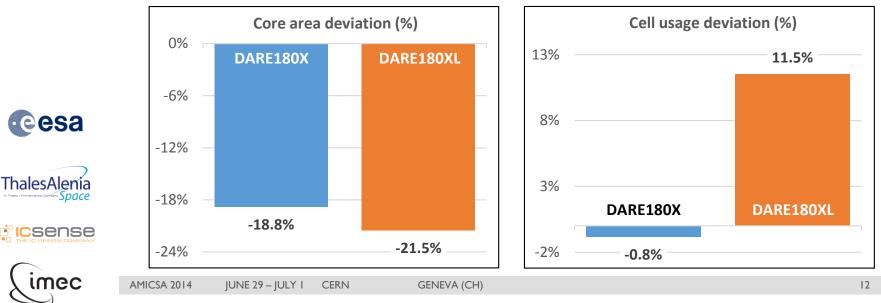

### DAREI80VS. DAREI80X

- Synthesis comparison

- Real design case

- Reference: DARE180

- Area reduction

- Smaller cell footprint

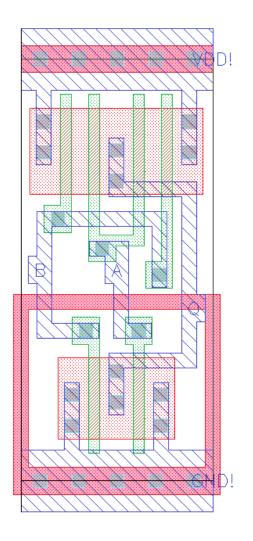

### DARE 80 VS. DARE 80X

|                     | DARE180<br>(reference)      | DARE180X   | DARE180XL    |

|---------------------|-----------------------------|------------|--------------|

| Cell                | NAND2                       | NA2JIX4    | NA2JILVTX4   |

| Rel. drive-strength | XI                          | <b>X</b> 4 | <b>X</b> 4   |

| LET threshold (SET) | 35 MeV/cm <sup>2</sup> .mg  | -50%       | 0%           |

| Sat. cross-section  | 3.45 cm <sup>2</sup>        | -75%       | <b>-62</b> % |

| Area                | <b>39.5</b> μm <sup>2</sup> | -25%       | -25%         |

| Rise FO4 delay      | 90 ps                       | +55%       | -10%         |

| Fall FO4 delay      | 66 ps                       | +43%       | -8%          |

| Avg. input cap.     | I5 fF                       | 0%         | -7%          |

- ThalesAlenia

- NAND2 = smallest/weakest NAND cell in DARE180

- **IC**sense

- - 4x stronger than NA2JIXI (the weakest NAND cell in DARE180X)

CERN

### SUMMARY

### MicroElectronics Platform

- Radiation-hardened mixed-signal libraries and IP

- Back-end, manufacturing and test services

- Commercial IC technologies

- New DARE180X library

- Low-power solution for space applications

- Straight transistors (no ELTs)

- Smaller area

- Cell sizing not lower-bound limited

- Better synthesis results => dynamic power optimized

### **FUTURE WORK**

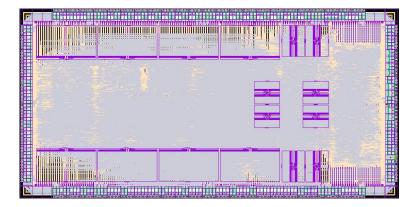

- DAREI80X available in 2014' Q3

- Test vehicle chip in 2014' Q4

- Radiation tests in 2015

### **REDANT@IMEC.BE**