#### THE DEVELOPMENT OF A RADIATION TOLERANT LOW POWER SRAM COMPILER IN 65NM TECHNOLOGY

**R. BROUNS, IMEC**

Introduction

Specifications

Strategies applied

Architecture and subblocks

Layout and compiler

Summary and references

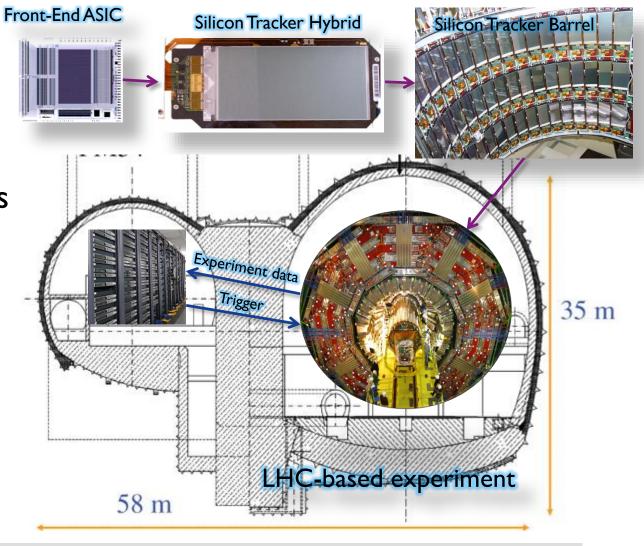

### **TRIGGER SYSTEM IN LHC EXPERIMENTS**

- Single event is ~IMB data

- Collision rate 40 MHz ~40 TB/s of data

- not all events are interesting for physics

- The trigger system selects only interesting events

- reduces data shipped out of the experiments

- Average trigger rate ~100 kHz

# MOTIVATION

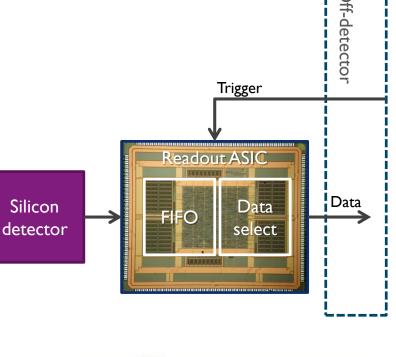

Trigger system evaluation time is order of  $\mu$ s

- During this time, data is stored in a FIFO

- FIFOs are normally embedded in front-end ASICs as SRAM blocks

- The LHC luminosity upgrade imposes stringent constraints to the front-end detector electronics

- Low-power, fast data rates, small pixels, radiation-hard ...

- 65nm CMOS is the chosen technology for many subdetector ASICs

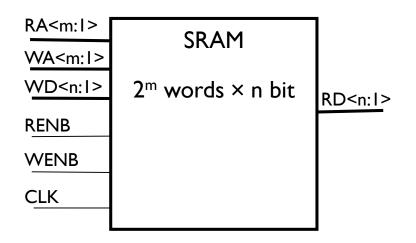

## **SPECIFICATIONS**

- Pseudo dual port behavior

- 65 nm technology with standard Vt devices

- 4 metal layers used

- Supply  $1.2V \pm 10\%$

- Power consumption 24uW/MHz

- ► Temperature range: -40 ... I 25°C

- Max frequency 80 MHz

- TID hardening > 200 Mrad

- LET threshold > 15 MeVcm<sup>2</sup>/mg

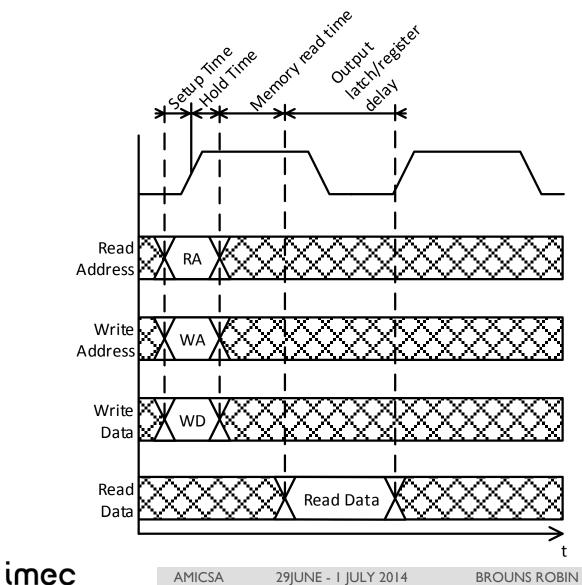

## **TIMING BEHAVIOR**

29JUNE - 1 JULY 2014

**BROUNS ROBIN**

AMICSA

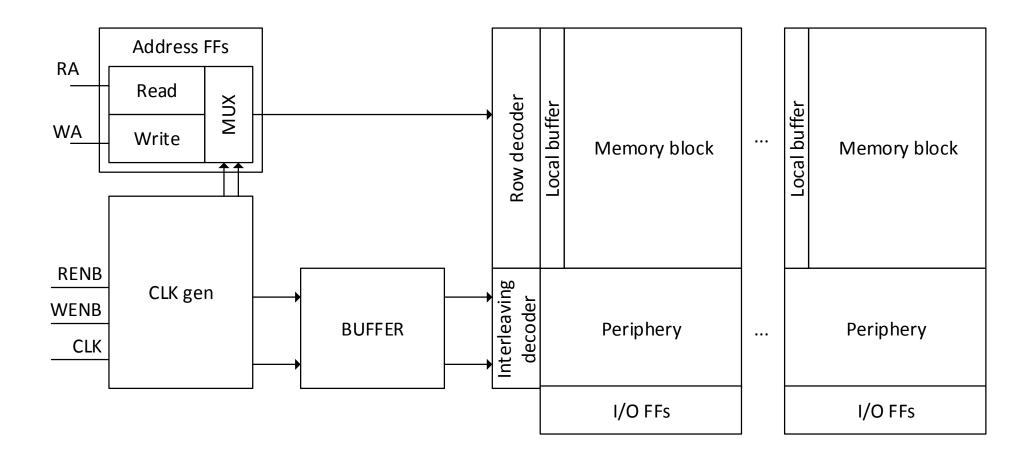

#### Pseudo dual port

- I master clock

- 2 address inputs (R/W)

- I data port (I/O)

© IMEC 2014

## LOW POWER

- Multiple techniques

- Split word lines

- Global word lines

- Local word lines with optimized buffer

- Discharge level of bit-lines reduced to 100mV

- Timing optimized by self-timing

- Dummy memory

# **RADIATION HARDENING**

### TID

- Minimum size MOS > DRC minimum

- p+ guard bands between n-type regions

### SEE

- Drive strength hardening

- DICE FF

## ARCHITECTURE

| # words    | 512w<br>8bit | 512w<br>8bit | <br>512w<br>8bit |

|------------|--------------|--------------|------------------|

| increasing | 512w<br>8bit | 512w<br>8bit | <br>512w<br>8bit |

Multi columns: increasing word size

#mosaic rows =

current aspect ratio target aspect ratio

### ARCHITECTURE

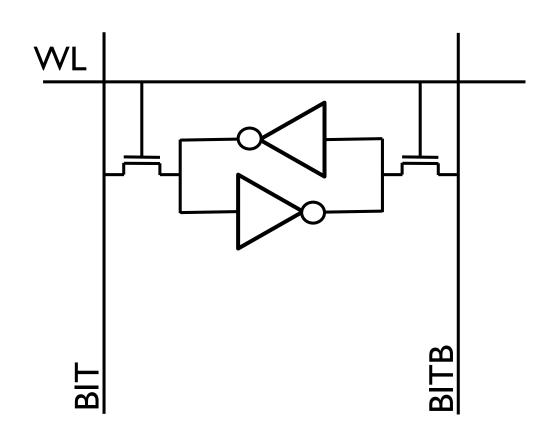

## **MEMORY CELL**

#### Standard 6T cell

TID hardening:

Not minimal width of MOS

P+ guard band

Verified PVT

SNM > 18% of Supply voltage

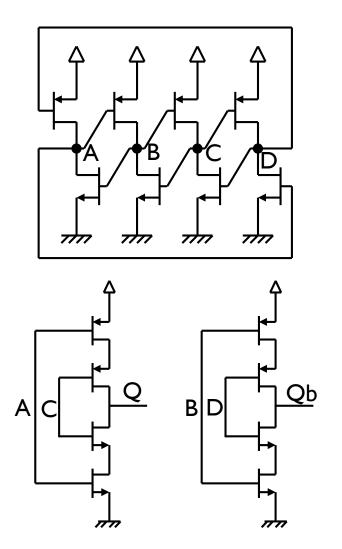

## **DICE FLIP-FLOP**

Corner stone of SEU hardening

Output redundancy

A=C and B=D

cCell

Absorbs SEU by going high impedance

Location in the design:

- Stores addresses

- Stores I/O data

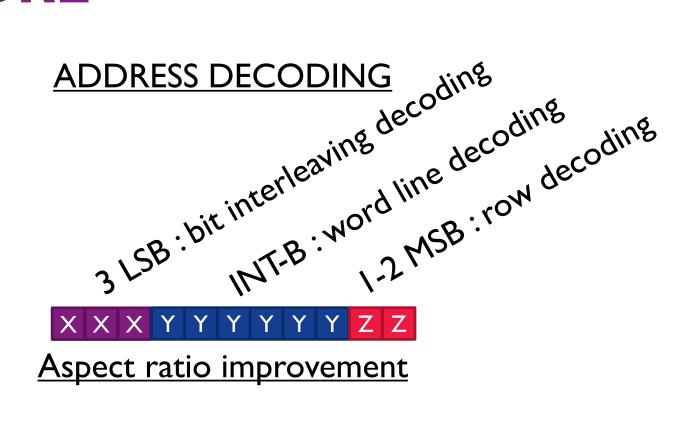

## PERIPHERY

- 8 bit interleaving A1B1C1D1...A2B2C2D2...

- Preventing Multi Bit Upset

- Aspect ratio improvement for small word sizes

- Multiplexer between BIT lines

Sense amplifier

Precharge Transistors

Write transistors

## **MEMORY BLOCK**

#### 2 flavors

- 512 words x 8 bits

- 64 word lines

- I 28 words x 8 bits

- 16 word lines

Split word line

Local optimized buffers

### Output multiplexing gates to increase # words

8 bit interleaving

# **CLOCK GENERATOR**

#### State machine

- Controlling all signals

- Precharge & discharge of BIT lines

- Select read/write address

- Output latch

- Write transistor

- Self-timing delays between states

- Dummy memory block

- Reset every clock cycle

imec

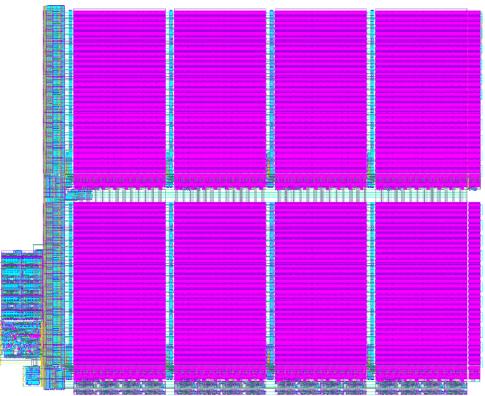

## LAYOUT

- 2 dedicated floorplans

- I 28 words memory block

- 512 words memory block

- 2 SRAMs on test chip

- I 024 words x 32 bits ≈ 450µm x 380µm

- I 28 words x 8 bits ≈ 245µm x 70µm

- Post layout verified in all PVT corners

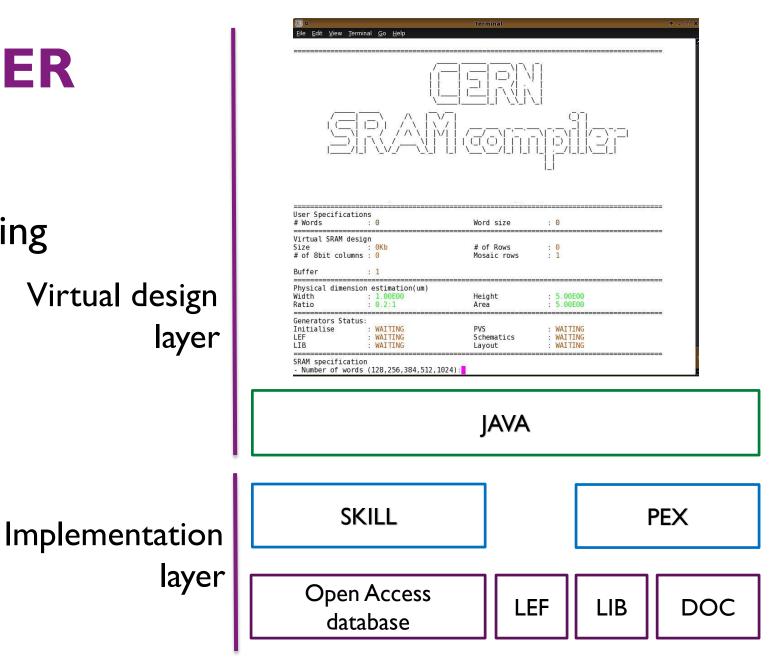

# COMPILER

- 2 layered system

- VDL for easy planning

- Dimensions

- Buffer size

- IL generates views

- Modular structure

### SUMMARY

Presented the design of a SRAM compiler

- 65nm CMOS technology

- Pseudo dual port

- Low power

- Radiation hardened against TID and SEE

- 2 flavors in memory blocks for optimal scalability

- 2 layered compiler

- Virtual design

- Modular implementation layer