# ACQUIMEA Passion for Technology

innovations for high performance microelectronics

# Use of IHP's 0.25 µm BiCMOS Process in the Development of European LVDS Devices\*

• COSO AMICSA 2014 - CERN - GENEVA - SWITZERLAND

\*EUROPEAN LVDS DRIVER DEVELOPMENT (ESA CONTRACT Nº. 4000105866)

## Outline

- ARQUIMEA / RAD HARD microelectronic products and services

- News!

- Introduction

- LVDS Octal Repeater

- Circuit Implementation

- Radiation Hardening

- Simulation Results

- Experimental Results

- Conclusions and Future Developments

- AOB

### **ARQUIMEA / RAD HARD MICROELECTRONIC** PRODUCTS AND SERVICES

### **MIXED-SIGNAL ASICs & IPs**

- Deep submicron digital, analogue and mixed-signal design and radiation hardening. SMART POWER.

- IP design, back-end and integration.

- ASICs Project Management (full supply chain).

### TECHNOLOGY CHARACTERISATION

Process or custom devices characterization (electrical and radiation test)

### **FPGAS**

Space FPGAs design and implementation as per ECSS-Q-ST-60-02

### STANDARD COMPONENTS

Development of rad hard standard components for space (LVDS, ANALOGUE MULTIPLEXORS, ADC's, DAC's, ...)

### **NEWS!** ARQUIMEA & IHP become partners in Space microelectronics

### Rad Hard Technologies available for MPW & Small Volume Production (under ESA & DLR evaluation)

| SGB25RH | A cost-effective technology<br>with a set of RF npn-HBTs up<br>to a breakdown voltage of 7 V                                                                    |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SG13RH  | A high-performance 0.13 $\mu$ m<br>BiCMOS with npn-HBTs up to<br>f <sub>T</sub> /f <sub>max</sub> = 250/300 GHz,<br>with 3.3 V I/O CMOS and 1.2 V<br>logic CMOS |  |

#### Rad-hard processes, libraries and IPs for digital, RF, analogue & mixedsignal design

|                                         |                                             | 000000           |

|-----------------------------------------|---------------------------------------------|------------------|

| STEP                                    | OUTPUT                                      | CONTACT          |

| 1. Design Kit Access<br>Service         | PDK (basic/enhanced)                        | IHP/<br>ARQUIMEA |

| 2. Support to Design                    | VHDL/NETLIST +<br>SCHEMATIC                 | ARQUIMEA         |

| 3. Support to Analogue<br>Layout        | VHDL/NETLIST +<br>SCHEMATIC + LAYOUT        | ARQUIMEA         |

| 4. Support to A/D<br>Integration        | GDSII FILES                                 | ARQUIMEA         |

| 5. Automatic Test Pattern<br>Generation | TEST PATTERNS                               | ARQUIMEA         |

| 6. Netlist                              | NETLIST                                     | ARQUIMEA         |

| 7. Place & Route                        | GDSII FILES                                 | ARQUIMEA         |

| 8. Analogue Layout                      | ANALOGUE LAYOUT                             | ARQUIMEA         |

| 9. Analogue + Digital<br>Integration    | GDSII FILES                                 | ARQUIMEA         |

| 10. DRC + LVS Checks                    | GDSII FILES VERIFIED                        | ARQUIMEA         |

| 11. Manufacturing                       | CHIPS                                       | IHP              |

| 12. Assembly & Test                     | TESTED PARTS                                | ARQUIMEA         |

| 13. Delivery                            | PARTS &<br>DOCUMENTATION<br>(including CoC) | ARQUIMEA         |

|                                         |                                             |                  |

### VLOILLEV

or high performance

## **ARQUIMEA Projects**

### **MIXED-SIGNAL ASICs & IPs**

- **ELSA**: Mixed signal housekeeping and conditioning device for **Hispasat AG1** REDSAT active antenna to be launched in 2015.

- DETECTA: High Speed Acquisition chain and ADC (>1 Gs, 10bit) based on IHP 0.13um (2010).

- Cosmic Vision HF & MF: Configurable mixed-signal ASIC for Cosmic Vision Instrumentation Payload, for the following applications: CCD signal, processor, Radiation detector, Radiation spectrometer, ADC, DAC, Filter, Low noise amplifier, Power amplifier. Two devices at high frequency and medium frequency are under development (2010).

- European LVDS devices: Development of European Rad Hard LVDS device family (2012).

- RadHARQ: Development of rad hard digital library and radiation detectors based on IT380 technology (2013).

- SWIPE: Development of a radiation detector (TID, SEU) for moon lander application (2013).

- **CARTU**: Development of a medium frequency 13-bit ADC (2013).

## Introduction

- Video, photo, high speed links, telemetries, ... space systems use very high data rates.

- Data links have to be:

- Fast

- Reliable

- Low Power

- Low EMI

- Low Cost

### LVDS (Low Voltage Differential Signal) is used for intra-spacecraft high speed communications.

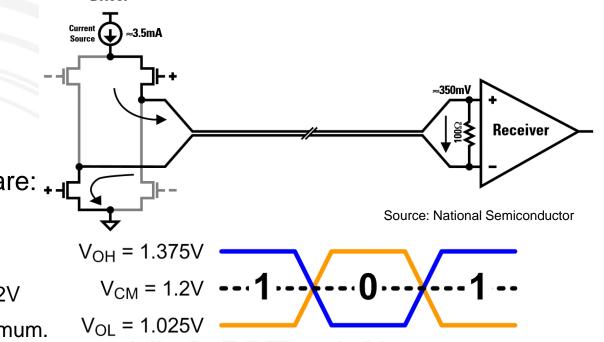

## LVDS (Low Voltage Differential Signaling)

Low Voltage Differential Signaling comprises the following advantages:

Driver

- **High Data Rate**

- Low Power

- Low EMI emissions

- **High Noise Rejection**

- Low Cost

- Its main characteristics are: + Its

- Differential

- Low voltage: ±350mV

- Common Mode Voltage: 1.2V

- Rise/Fall times: 260ps minimum.

- High Data Rate (655 Mbps max. ANSI/TIA/EIA-644 standard).

for high performance microelectronic

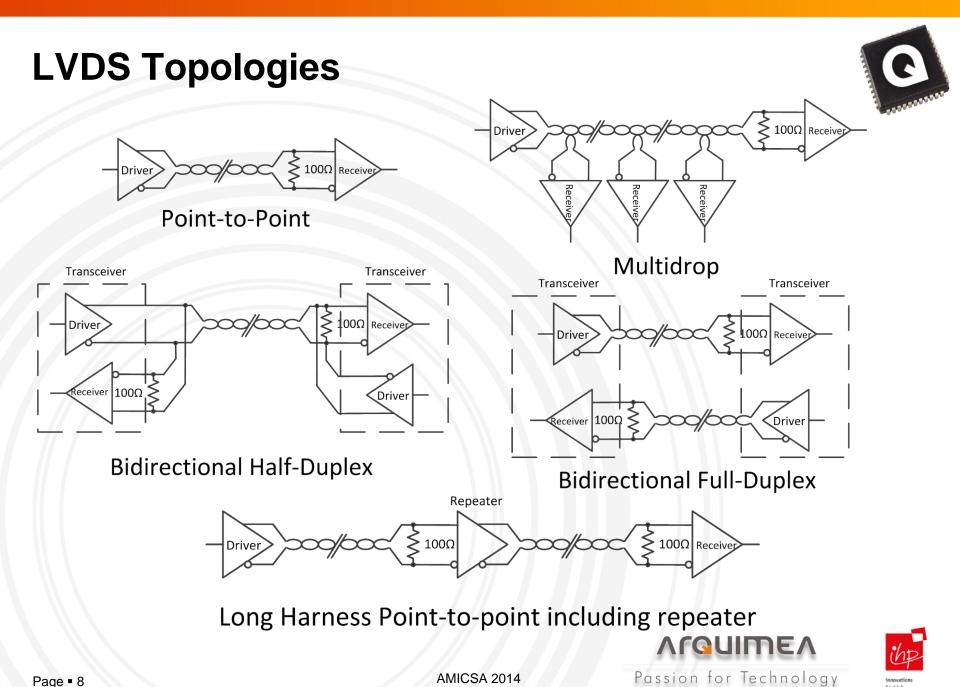

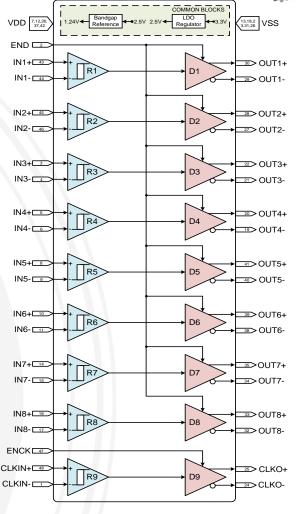

## **LVDS Octal Repeater**

- Full ANSI EIA/TIA 644A compliance.

- Eight Data channels.

- One clock channel.

- Data channels enable pin.

- Clock channel enable pin.

- Tri-state driver capability.

- >500 Mbps data rate (250 MHz).

- Single 3.3 V Supply.

- Extended temperature range (-55°C, +125°C).

- Integrated voltage reference.

- Extended input common mode for LVDS inputs (-4V, +5V).

- Extended maximum absolute rating for LVDS inputs (-5V, +6V).

- TTL compatible digital inputs.

- Small channel delay, <2.7 ns typical, <3.5 ns over full temperature range.

- Low peak-to-peak jitter <236 ps (±3σ).</li>

- Low channel to channel skew <150 ps typical, <250 ps over full temperature range.</li>

- 8 kV HBM ESD enhanced protection.

- Fail-Safe functionality included.

- Cold Spare functionality.

- Radiation Hardness higher than 300 kRad (Si) TID with ELDRS and SEL immune up to 60 MeV cm2/mg LET.

- CQFP48 package.

AMICSA 2014

#### Page 10

## **Circuit Implementation**

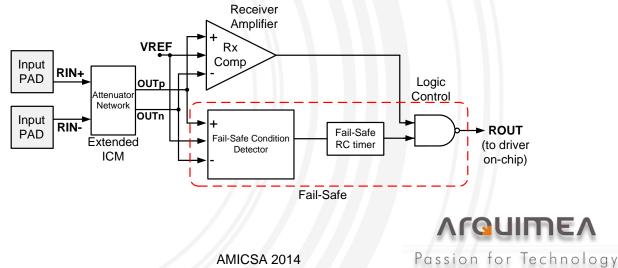

### Receiver

- Frequency compensated Attenuation network

- Rail-to-rail high speed Comparator

- Fail-Safe Detector

- Fail-Safe 500ns RC timer

- Allows extended input common mode range from -4V to +5V

- Cold Spare inputs

#### Page • 11

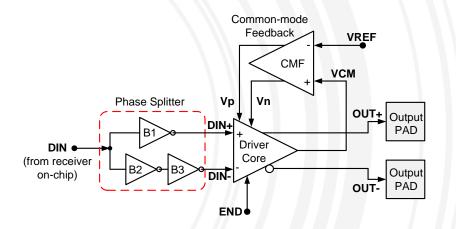

## **Circuit Implementation**

### Driver

- Phase Splitter

- Driver Core

- Common Mode feedback amplifier

- Designed to achieve minimum <u>at least 500Mbps</u> data rate

- Cold Spare outputs

performance

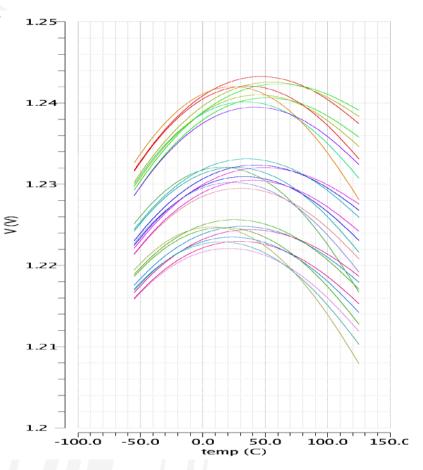

## **Circuit Implementation**

- 1.25V internal bandgap reference

- First order compensation

- Voltage Reference

- LDO regulator

- 3.3V input voltage

- 2.5V output voltage (core voltage)

- 8 kV HBM ESD pads

- Custom made ESD protections and pads for 8kV ESD and 250V MM.

Bandgap output voltage across corner variations

### **Radiation Hardening**

- Expected radiation performance of IHP SGB25RH (from previous radiation data):

- Expected SEL immune > 60 MeV cm2/mg

- Immunity up to 300 kRad for high and low dose rates

- Several techniques were used to improve radiation hardness (in addition to Rad Hard DRC design kit rules) including its application to custom digital cells.

- High W/L or ELT layout for NMOS devices.

- Systematic guard ring isolations or triple-well isolation.

- Differential design.

- SET sensitivity has been evaluated using specific software tools (developed by Grupo de Ingeniería Electrónica, from Universidad de Sevilla).

AMICSA 2014

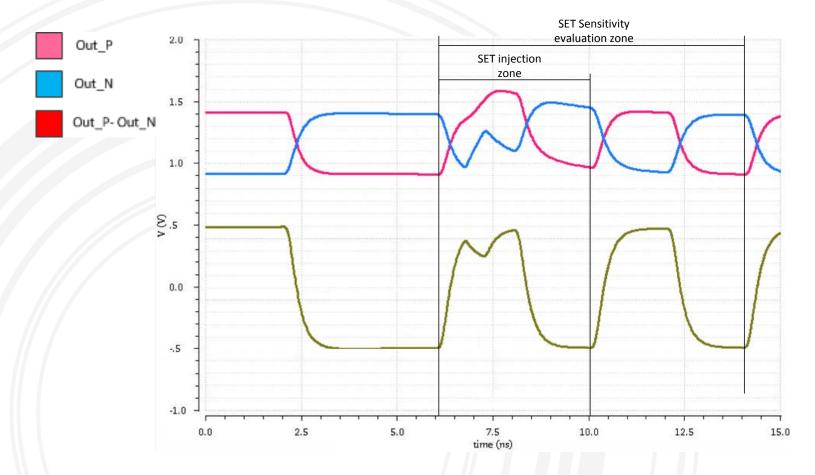

## **Radiation Hardening – SET simulation**

Example of SET injection in the driver core circuitry

VLOUIMEV

for high performance microelectronic

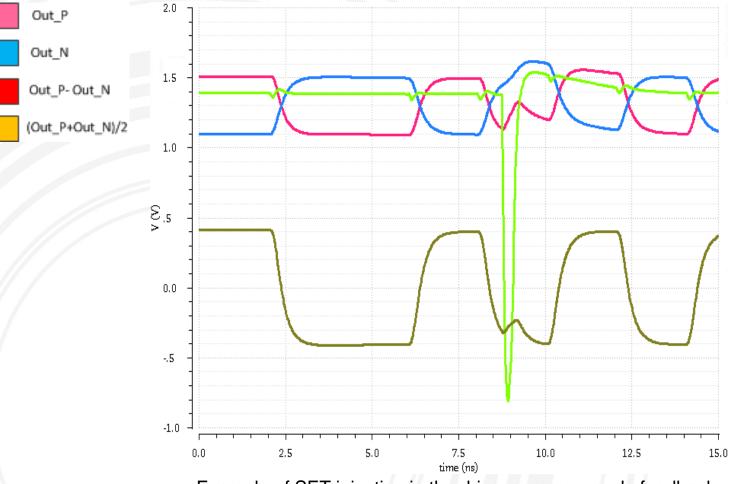

### **Radiation Hardening – SET simulation**

Example of SET injection in the driver common mode feedback. Driver CMRR avoids bit flip at the LVDS output.

for high performance microelectronic

### **Simulation Results**

- Extensive extracted view simulations have been performed over:

- Full temperature range,

- Process corners,

- Supply variations.

- Results:

- Full ANSI EIA/TIA 644A compliance.

- Minimum Data Rate: 500 Mbps (can go up to 728Mpbs), with extended common mode (-4V to +5V).

- Small Channel delay: 2.7ns

- Low channel to channel skew: 150 ps

- Cold Spare, tri-state and fail-safe functionality verified.

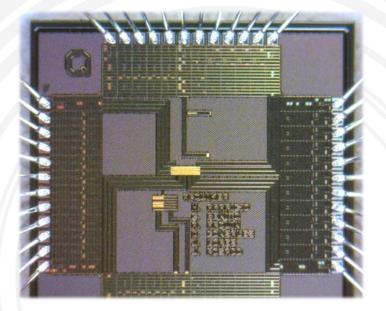

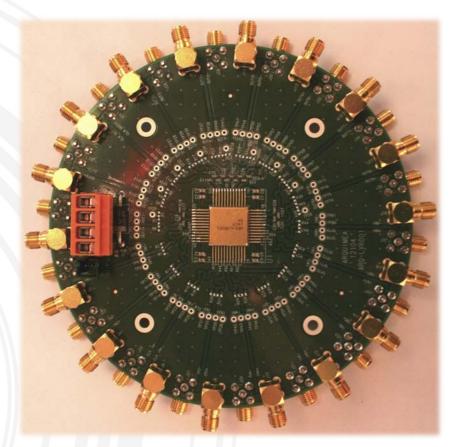

## **Chip implementation**

- IHP SGB25RH (MPW)

- Die size: 2x2 mm<sup>2</sup>.

Package: CQFP48 (by MICROSS)

for high performance microelectronic

**VLOUILDEV**

### **Test activities**

- ESD testing has been performed by IHP achieving more than 7.3kV for all pads (limited by the test equipment capability).

- Full electrical characterization in July 2014

- Radiation tests expected in September 2014 (for TID and heavy ions) by ALTER Technology.

#### LVDS Octal Repeater Test Board

**LIDEN**

### Conclusions

- A radiation hard, Octal LVDS repeater has been designed and manufactured.

- Full ANSI EIA/TIA 644A compliance.

- Minimum Data Rate of 500 Mbps (can go up to 728Mpbs), with extended common mode (-4V to +5V).

- Small Channel delay of 2.7ns

- Low channel to channel skew of 150 ps

- Cold Spare, tri-state and fail-safe functionality verified.

- Full electrical characterization and radiation testing ongoing.

- A full evaluation/qualification of the device it is expected to be performed in the next project phase.

### **Future Developments**

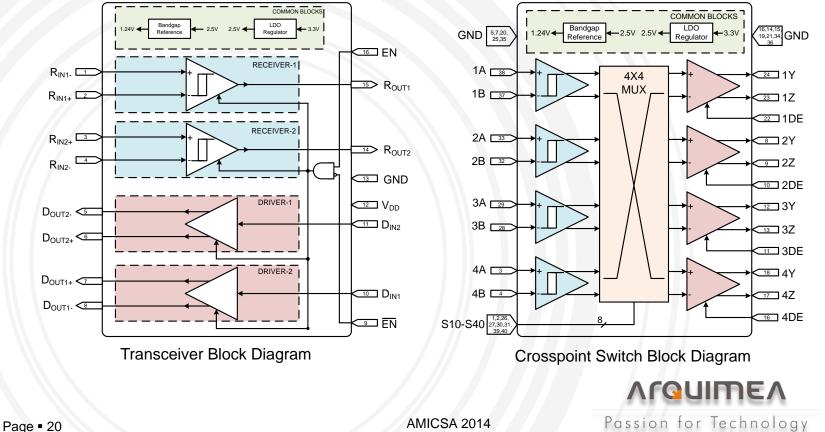

A complete family of LVDS devices: driver, receiver, transceiver and crosspoint switch, with equivalent performances to the octal repeater, are under development by Arguimea as a continuation of this work.

AMICSA 2014

for high performanc nicroelectron

### for your attention...

jlopez@arquimea.com

arquimea\_026

AMICSA 2014

# νιωεν

#### Microelectronics; Actuators; Space Electronics

#### ARQUIMEA INGENIERÍA, S.L.U.

Margarita Salas 16 Bajo A, 28919 Leganés (Madrid) – ES Phone: +34 91 689 8094 Email: info@arquimea.com Website: www.arquimea.com

#### Microelectronics: Digital Design, Back-End & Test Services

#### ARQUIMEA DEUTSCHLAND GmbH

Im Technologiepark 1, 15236 Frankfurt (Oder) – DE Phone: +49 (0) 335 557 1717 Email: deutschland@arquimea.de Website: www.arquimea.de

AMICSA 2014