# Fermilab Electronics Development Plans

David Christian Fermilab November 20, 2013

# Primary Activities 2013-2014

- Radiation tolerance studies (RD53)

- 130 and 65nm ICs (mostly transistors) designed at FNAL, fabricated by Global Foundries & TSMC

- 130nm results will validate our methods

- 65nm results will extend comprehensive tests to ~1 Grad

- Gamma irradiation Sandia National Lab

- Coordinated by Steve Wagner (Colorado)

- Major contribution from Michael Krohn (Colorado graduate student)

- 1<sup>st</sup> irradiations will be of room temperature devices, but we plan to irradiate cold devices (-20C?) if possible

- Readout chip for array of 30µx100µ pixels

- 130nm CMOS (GF)

- Goals:

- Explore how small a pixel is possible.

- Demonstrate low threshold ( $\leq 1000 e^{-}$ ) operation.

- Provide a device for sensor R&D.

# Sandia Gamma Irradiation Facility

- <u>http://www.sandia.gov/research/facilities/gam</u> <u>ma\_irradiation\_facility.html</u>

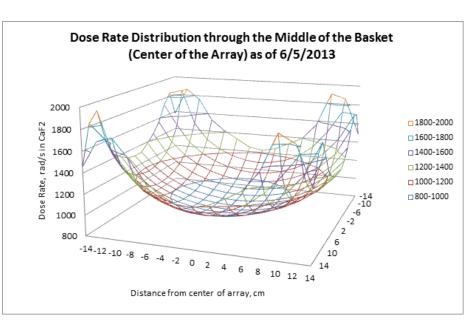

- Three test cells with arrays of <sup>60</sup>Co sources (1 MeV gammas)

- Sources shielded in pool of water; raised above water for irradiation

- Sample held in basket above pool.

- High dose rate possible

- 1krad/sec typical (3.6Mrad/hr)

- Large area with approx equal dose rate.

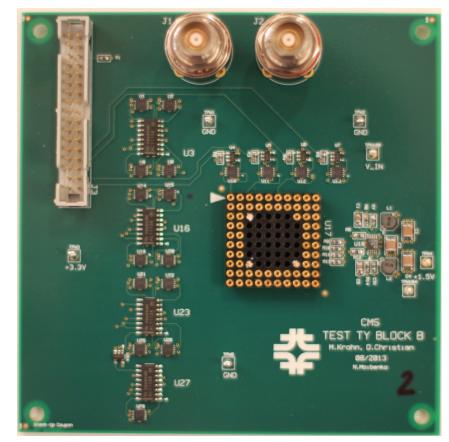

### Measurement PCBs

- Test ICs bonded in pin grid arrays.

- ~20 transistors bonded per package

- PCB provides power for protection diodes and connects SMUs to one transistor at a time

- Labview program selects which current switches are active – connects one SMU to transistor source/drain & the other to transistor gate.

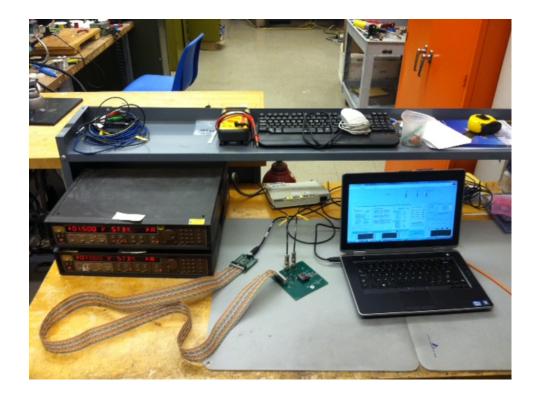

### Simple "Portable" Measurement Apparatus

- For each transistor:

- Set  $|V_{ds}| = V_{dd}$

- Sweep Vg  $(0 V_{dd})$

- Measure  $I_{ds} \& I_{g}$

- Extract

- Leakage current (off state)

- Transconductance g<sub>m</sub>(max)

- Threshold voltage  $V_T$

## Small-Pixel Readout Chip

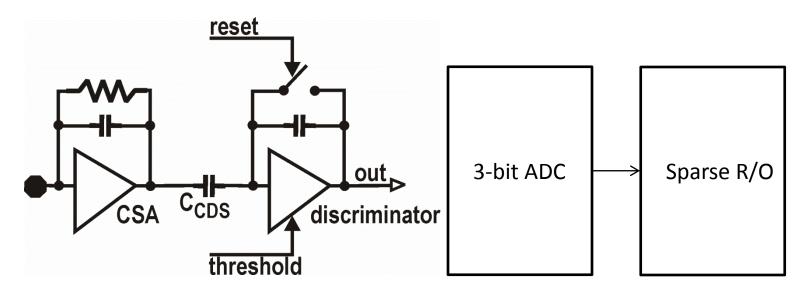

### Pixel Unit Cell

- Both FE cells use a synchronous front end, reset @40MHz:

- Correlated double sampling with  $\Delta t$ =25ns removes low frequency noise.

- Greatly reduces sensitivity to pile-up.

- Designed so that current draw does not change during reset.

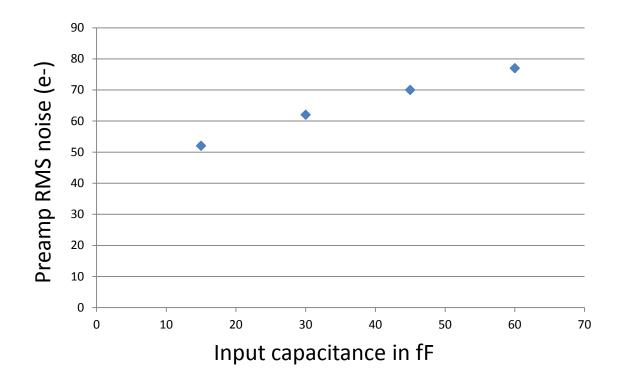

#### Simulation of Preamp#1 Yields Noise < 100 e<sup>-</sup>

- Correlated double sampling adds a small amount of noise (total noise = 62 e- at C<sub>in</sub> = 30 fF)

- Power Consumption: 5μA (preamp) + 8μA (all comparators)

- $433 \text{ mA/cm}^2 = .65 \text{W/cm}^2 (1.5 \text{V})$

## Test ROC timeline

- Fabricate test ROC in Global Foundries 130nm CMOS

- Submission expected in January 2014

- Test bare dice

- March April 2014

- If OK

- Bond to sensors included on Phase-1 prototype sensor wafer

- Bond to diamond sensors (Colorado)

- Bench test with sources

- Beam test

- Translate (at least analog circuits) to 65nm (as part of RD53)

- Fabricate either small blocks or ROC

- Compare circuit performance w/130nm version