#### Status of the 3DIC project

R. Brenner - Uppsala University P. Seller - STFC(RAL)

Richard Brenner – Uppsala University

1/(8)

#### AIDA WP3 March 26 2014

۵

## Background

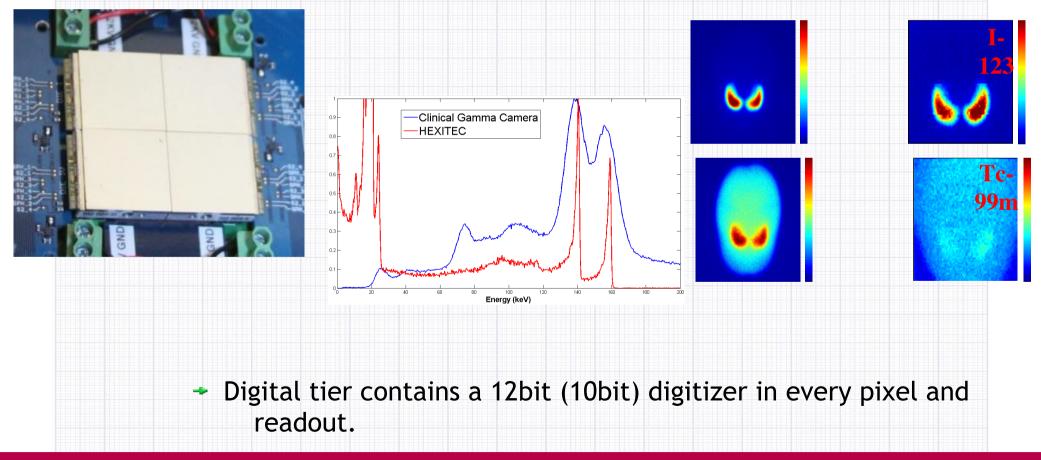

Demonstrate that 2-tier 3D pixeldetector readout ASIC with vias in every pixels can be done "via last"

Analogue tier based on proven Hexitec platform

## Specifications

- Technology ASIC: AMS 0.35 μm

- 40x40 pixels

- Effective pixel pitch 250x250 μm

- 4-side buttability

- Digitization modes 12 and 10 bits

- Output of "hit-pixel"

- Each pixel should be able to handle 2 hits/readout (~deadtimeless operation)

### Progress

- 12 wafers containing both tiers produced, tested and shown to be well functioning. (pre-AIDA)

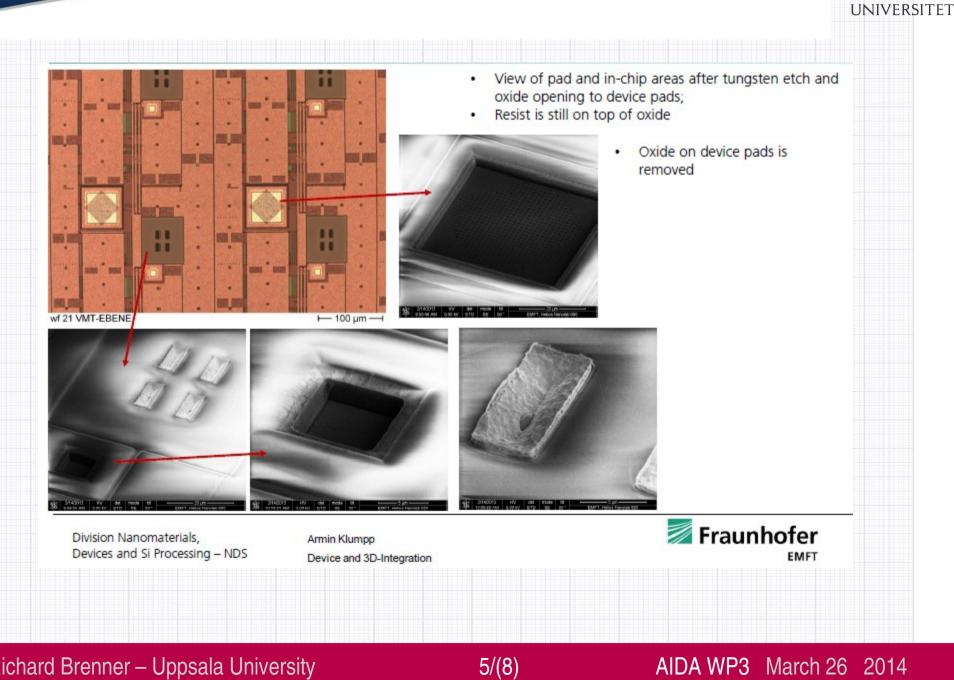

- In 2011 EMFT were contracted to thin the "Analogue" wafers

- In 2012 EMFT were contracted to finish the SLID bonding (there was an unfortunate long delay between these two steps because of contract issues)

- The first SLID parts were delivered in Mid 2013 (rather than end 2012)

- The first full wafer of SLID parts were delivered in Oct 2013

UPPSALA

#### Richard Brenner – Uppsala University

## Deliverables (& lessons learned)

- TSV processing and contact metalization went generally OK

- Excessive stress induced in the thinning process (to 50  $\mu m$ ) and this had to be modified to stop the wafers cracking

- Back side metalization critical and is one of the main worries.

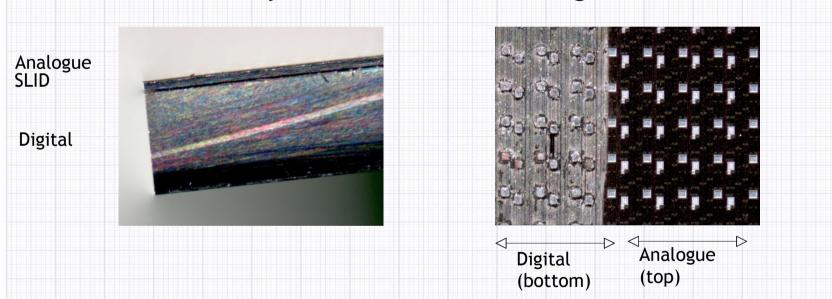

- EMFT have now delivered a wafer of SLID bonded ASICs and some non-bonded parts

- 9 proper devices (thin top analogue to thick digital) on the wafer that are properly SLID bonded together

Analogue (top)

- 10 thin top digital bonded to thick analogue. The SLID bonds are not functionally and the devices have a non-functional checker-board Al pattern on top surface. These do have good wire bond pads so can be connected to test boards.

- 5 thin analogue and 5 thin digital ASICs. One analogue AISC went for stress imaging at ANKA.

Digital (bottom)

## Cont.

The full SLID wafer is visibly very poorly bonded (Fig 2) and we do not expect any good devices but there could be valuable indications by using the new system. We have used some ASICs from the wafer but there were only 6 devices worth taking from the wafer.

EMFT agree, that the device SLID looks very poor and there will be very poor yield. 3DIC is still strategically important for them and they have committed to continue the development. They agreed to reprocess devices Free Of Charge if we can provide more wafers.

Richard Brenner – Uppsala University

AIDA WP3 March 26 2014

# Plans (AIDA year 4)

- Testing of already delivered devices started and will continue with a PhD student who begin testing at RAL and continue in Uppsala.

- 12 new wafer purchased and delivered to EMFT for processing

- EMFT processing plans (intend to split your 12 wafers into 4 bottom wafers and 8 top wafers):

- M1: Top wafers thinned on handling substrate by 30.05.14

- M2: Electroplated copper structures on thinned-Top back side by 13.06.14

- M3: Electroplated copper/tin structures on bottom wafer by 05.05.14

- M4: Assembled Top on Bottom by 27.06.14