#### New FEC V6

A long story..

## Design periods 2013

**Schematics:**

3D component layout

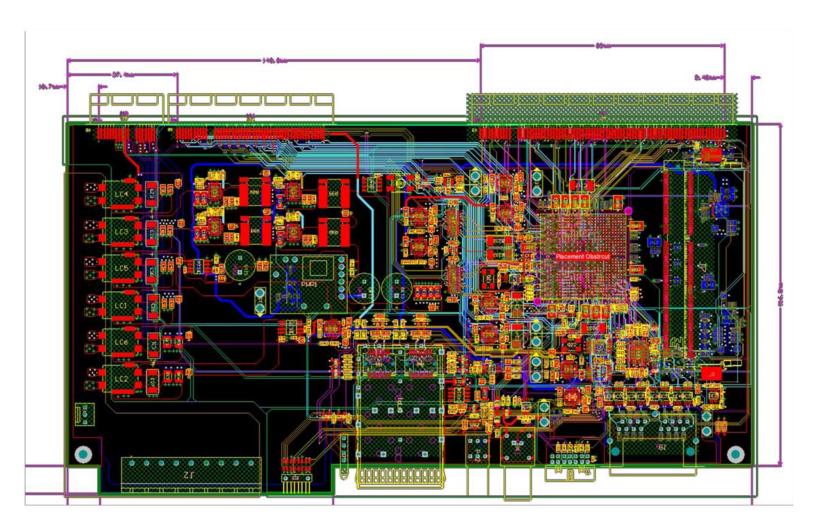

12 layer PCB routing:

**UPV Valencia** RD51/CERN

**AES Madrid**

Component procurement

Front panel

PCB mounting:

Testing 4 protos:

RD51/CERN

RD51/CERN

**TELSA Sion**

**UPV Valencia**

## Main motivation for FEC upgrade

- Need more FPGA resources (Zero-supression etc)

- Need 2<sup>nd</sup> SFP for more flexible architectures

- DDR memory plug in

- Jitter cleaner for precise clock Xmission to SRU

- Additional I/O connector on front panel

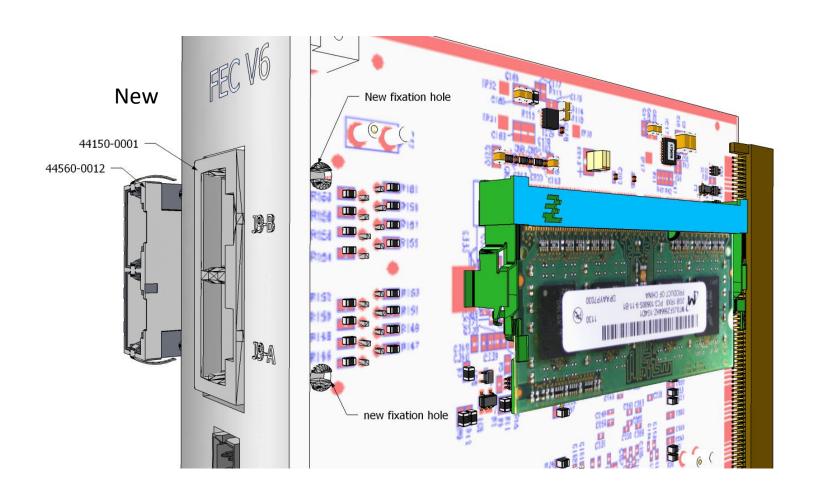

#### Common FEC V6 card

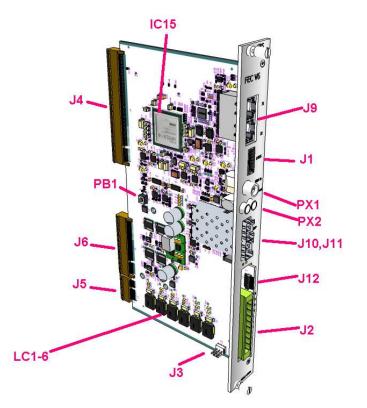

SRS backside connectors Virtex-6 FPGA: XC6VLX130T-1FFG784C Jitter cleaner: Clock phase alignment NIM Trigger LVDS in 2x RJ45: remote I2C, DTCC link SRSU Power connector Dual SFP, I/O connector JTAG on Front panel Ethernet (2 x 1 Gb)

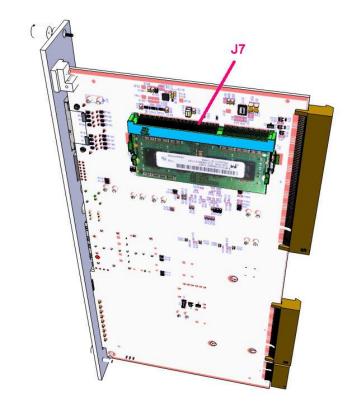

DDR3 plugin RAM on backside

# Photo FEC V6 Jan 2014

Dual RJ45 Virtex 6 JTAG **Dual SFP+** aux I/O Hans.Muller@cern.

DDR3 plugin

# AES 14 layer routing

#### Several hickups 2013

Bari routing 1Q 2013 was not successful until June 2013, complexity too high June-July 2013: 3 calls for commercial FEC V6 routing 1st AES layout Aug 2013: DDR3 would hit the crate

This required complete re-routing of critical DDR3 lines, pin swapping ect by UPV First PCBs and final component list ~ End Nov 2013...

Component procurement and call for PCB layout December 2013

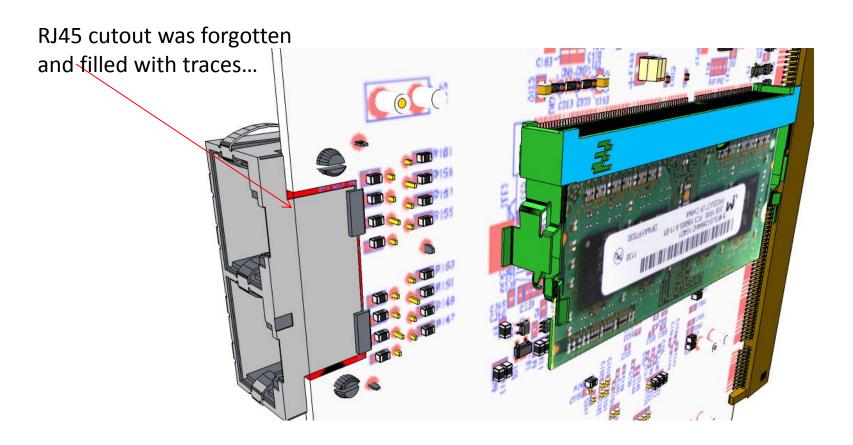

# Small hickup 2

Waiting now for test results....

# Fix: change of Rj45 connector modification of frontpanel

#### Status 2014

- All components and PCBs for 12 FECs @ TELSA

- 4 FEC-V6 prototypes produced

- 8 FEC –V6 still on hold @ TELSA

- 4 cards new at UPV for test, awaiting result

- BOM components revision procurement

- Expect 3-4 weeks after test result

#### Proto cost

| • | PCB layout/AES                                | 5 kFs   |

|---|-----------------------------------------------|---------|

| • | PCB's 12 layer NELCO/Lab Circuits             | 3.6 kFs |

| • | PCB mounting /TELSA                           | 6 kFs   |

| • | FPGA's /Silica                                | 5 kFs   |

| • | Components / Mouser / Farnell / Digikey 3 kFs |         |

| • | Front panels                                  | 0.2 kFs |

- Total prototype cost 12 cards

22.8 kFs

- → Proto cost 1.9 kFs/ FEC V6

- 10kFs contributed from common fund

- 12 x first user cost 1.1 kFs

#### General FEC V6 availability

- After proto phase, FEC 6 to replace FEC V3

- PRISMA /CERN store production change

- Expect higher cost than FEC V3 (increased FPGA cost)