### General comments

The Fe board will have a firmware general architecture close the actual design

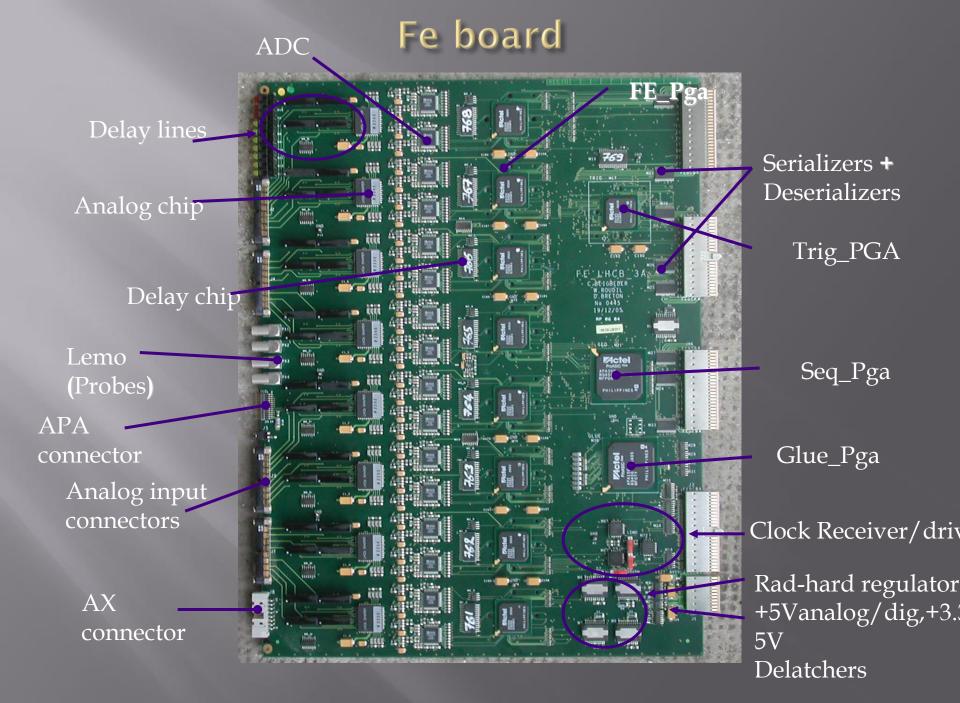

- The FE board was designed with 2 different kinds of FPGA and 4 different references :

- 9 non-reprogrammable Actel AX500 and AX 250

- 2 reprogrammable : Actel APA 150 and APA300

- The new version will be fully equiped with reprogrammable device APA3E Actel family devices.

- The whole crate will be reprogrammable without external components which is a drawback of the actual design.

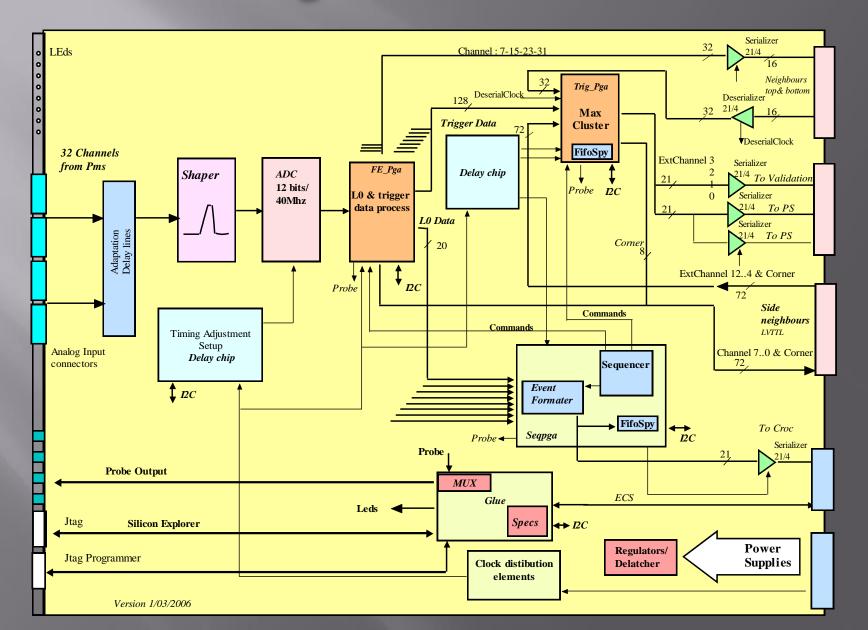

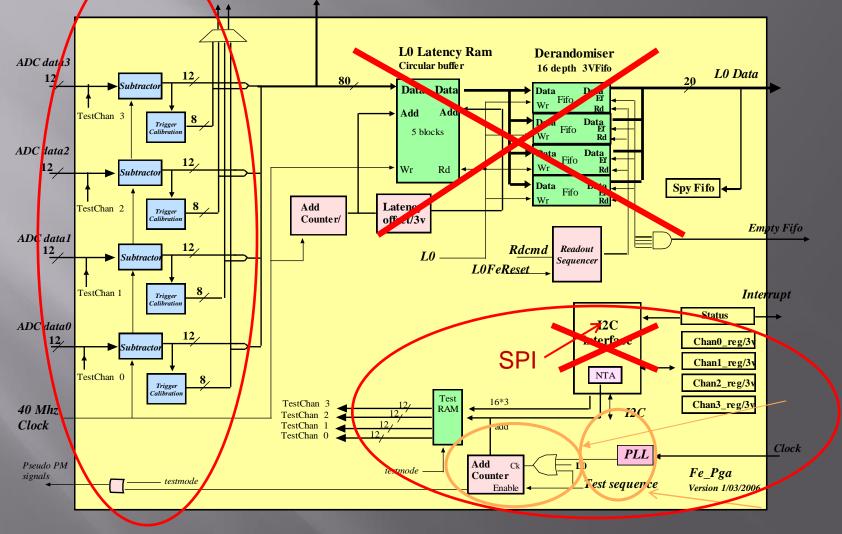

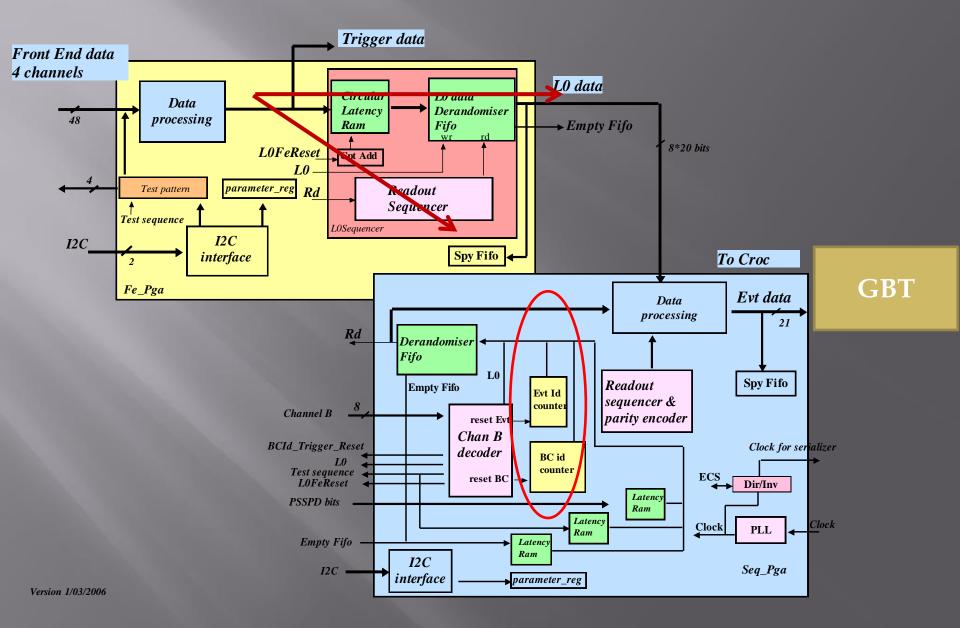

# Block diagram of the FE board.

### data processing part

Trigger data (16 bits @ 80 Mhz ) Neighbours data (up to 32 bits@ 40 Mhz)

e PGA ->

### Fe PGA -> Data processing part

FE\_Pga

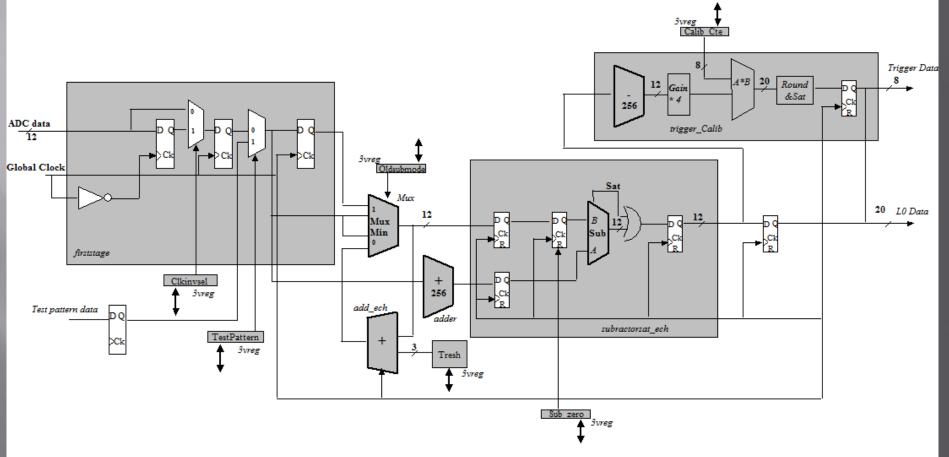

L0 and trigger data processing part : Module Subtract

5 Clock cycles Input to Output

# **Front-end PGAs**

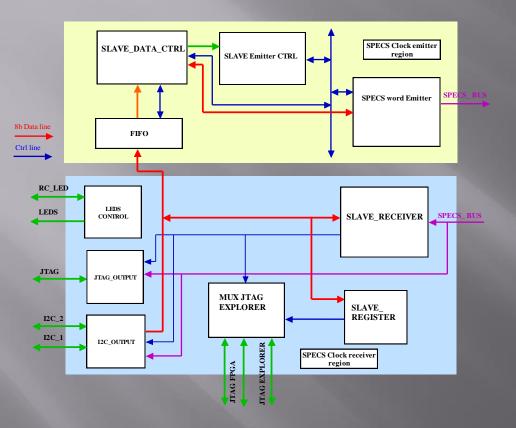

### Glue PGA -> GBT SCA or GBT decoder and USB 2 and glue logic

FTDI USB decoder cannot be implemented on the board. Use the UM 232 H with the Glue PGA to generate parallel bus , JTAG and I2C for test purpose.

Can we decode the GBT protocole to the SCA inside the GLUE and generate the JATAG and SPI

## LLT data

The TrigFPGA on the FEB computes a local address (cell id between 0 and 31) A more detailed address is needed :

To match HCAL and ECAL related cells to be able to sum their ET (was done in TVB before) Absolute « official » address needs to be build for each address sent to « L0DU » and to the DAQ, in the format [Detector, Area, Row, Col] (was done in Selection Boards before, using Local Address + Crate ID + FEB ID)

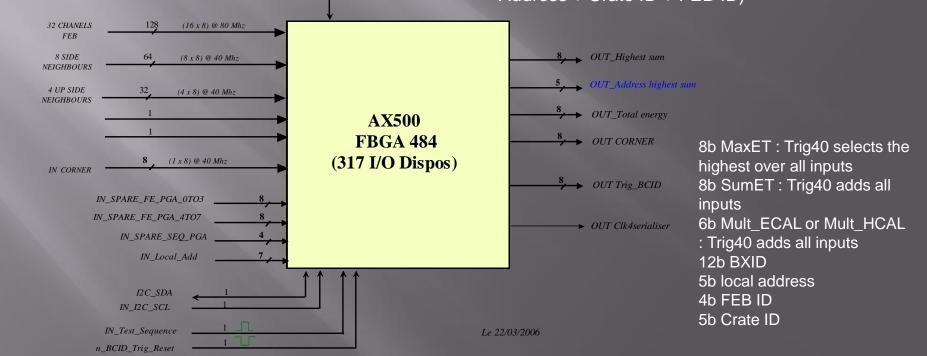

#### /O UPegember 1, 2018al : 317 Whose 266 inputs, 39 outputs, 1 bidirectional.

#### Trig\_PGA : AX500 - FBGA 484 (317 I/O Dispos)

IN CLK Global

**Recensement des I/O**

### Fonctionalities kept

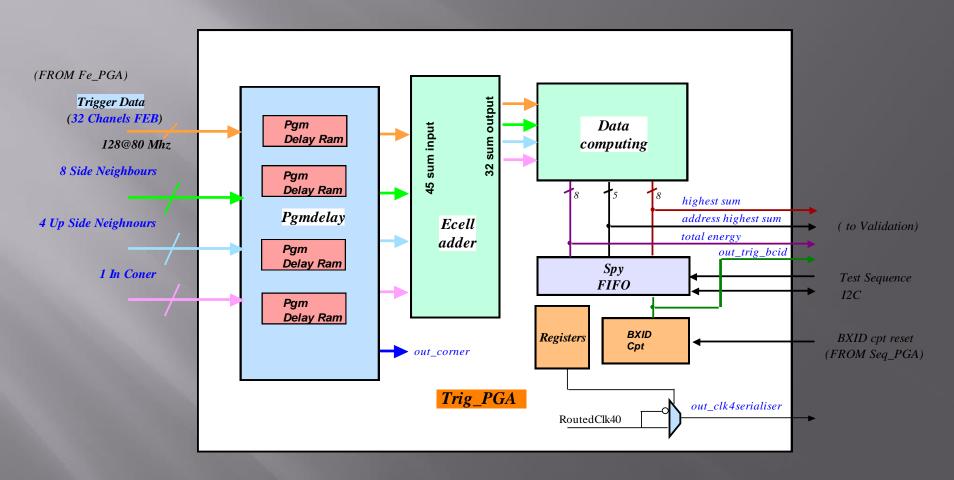

- Since channels come from different locations, they have to be *time-aligned* before the computation:

- Each different source (card cells, up, side and corner neighbours) can be *delayed independently* by 25 ns steps in the range 0 – 15x25 ns.

- Neighbours via backplane arrive first, then channels on the same board (because they are multiplexed at 80 MHz), then neighbour via cables and the corner.

- A BxId counter is incremented and sent with trigger candidates. The reset of the BxId is *delayed* by a delay coded on 12 bits (0<delay<4096) and loaded by ECS.

- All input channels can be *individually masked* in order to remove them from the trigger computation. By default, at start-up, all channels are masked. They are then un-masked loading registers by ECS.

- The calibration command (activating the writing of 256 consecutive events in the Spy RAM) can be *delayed* by: 0<=delay<4096.</p>

# Global View of Trig\_pga

Global View, Trig\_PGA Version 22/03/2006

### Detail View

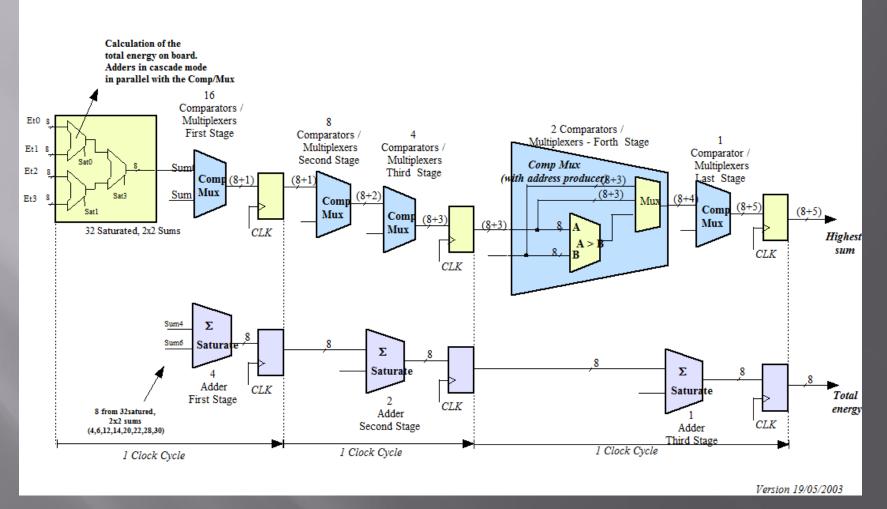

#### Trig\_PGA : Highest sum and Total energy compute

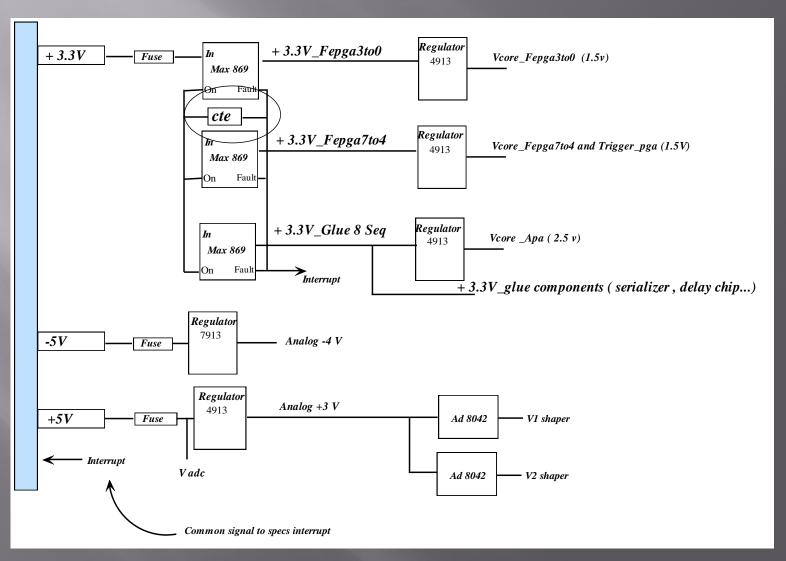

### Power distribution

#### Board Consumption : +5 V = 4A +3.3V = 2 A-5V = 1 A