# EVAPORATIVE CO2 COOLING IN SILICON MICRO-CHANNELS FOR THE

Paweł Jałocha University of Oxford on behalf of the LHCb VELO and PH/DT/Cooling group

# Motivation

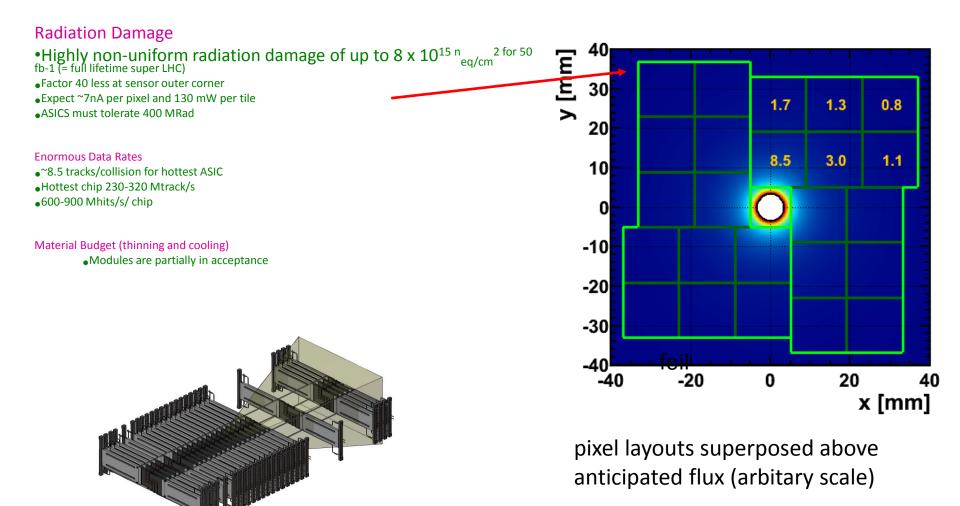

- LHCb VELO 2018 upgrade asks for high-speed hybrid pixel detectors to allow DAQ and data analysis to cope with increased LHC luminosity

- Sensors and ASIC's need efficient, low mass and direct cooling system

- VELO cooling is already based on liquid CO<sub>2</sub>

Silicon plate with embedded micro-channels meets the requirements

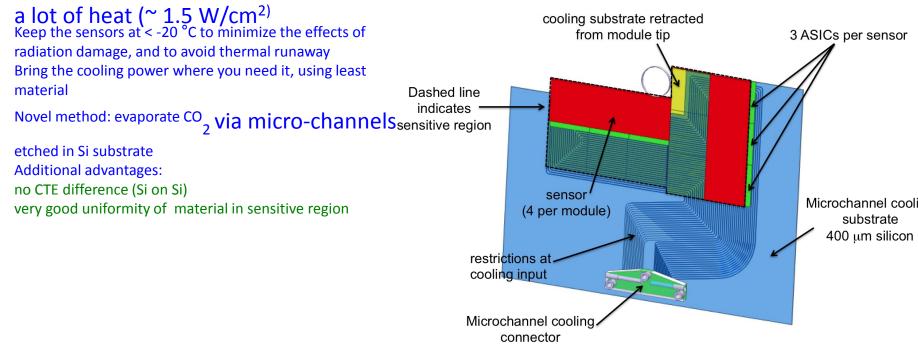

# Cooling requirements for VELO

- Keep sensor temperature below -20°C to minimize the effect of radiation damage and to avoid thermal runaway.

- Bring cooling power directly where it is needed using least amount of material (detector tip is the hotest spot)

- The total power per module is ~26W (2W per ASIC and ~2W on the innermost sensors)

- Cooling active area (24cm<sup>2</sup>)

- Power area density: 1.1W/cm<sup>2</sup>

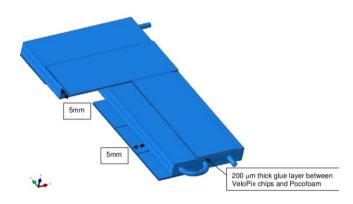

- 5mm of uncooled ASIC/sensor (overhang) close to the beam to reduce the amount of material

# Mechanical requirements

- Leak tight (secondary LHC vacuum !)

- The saturation CO<sub>2</sub> pressure is 65 bars @ 25°C

- Minimum pressure of 170 bars (factor 3 safety margin)

- Long term reliability

- Cyclic pressure and temperature cycles

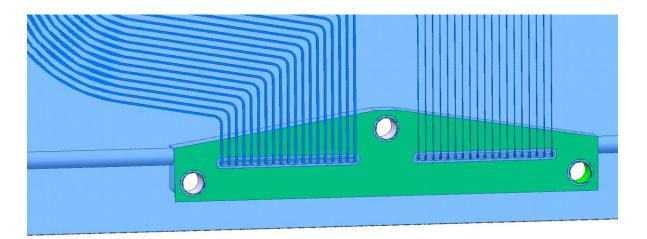

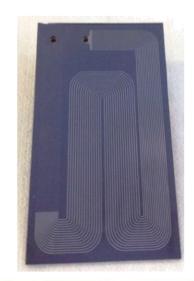

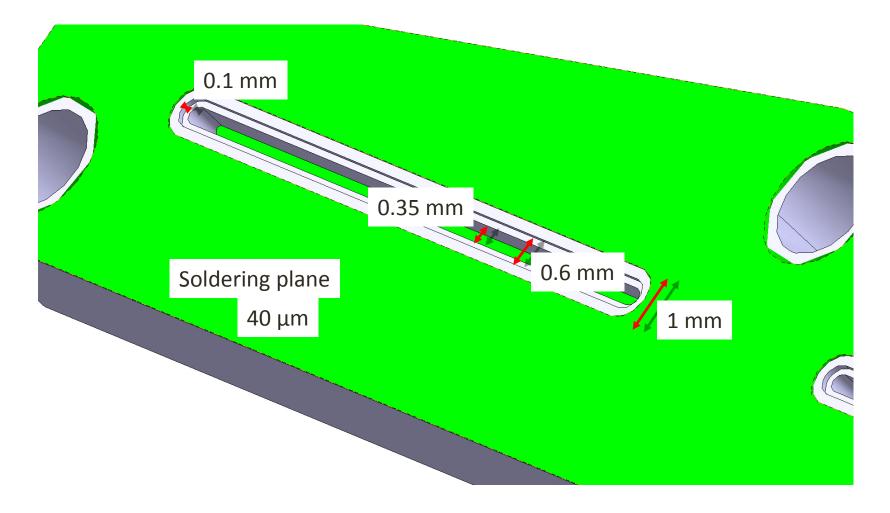

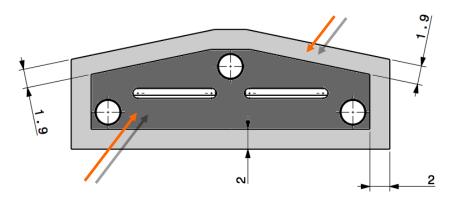

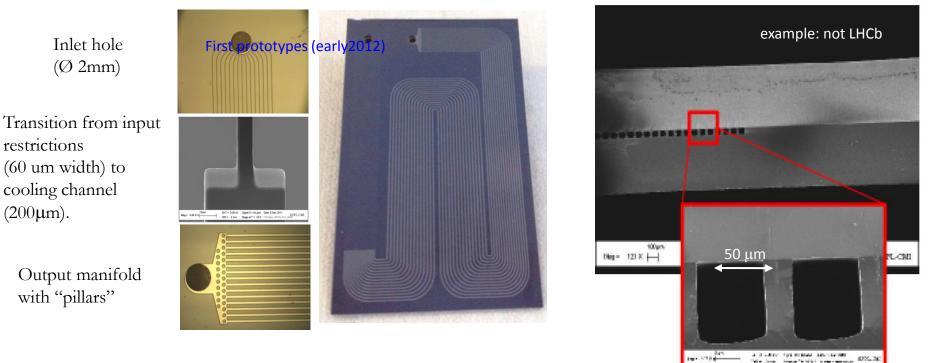

### Micro-channel wafer layout

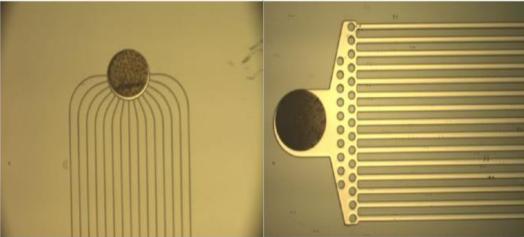

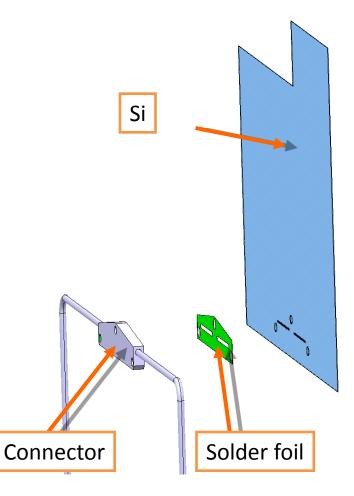

# Micro-channel wafer layout: connector, inlets and outlets

23/07/13

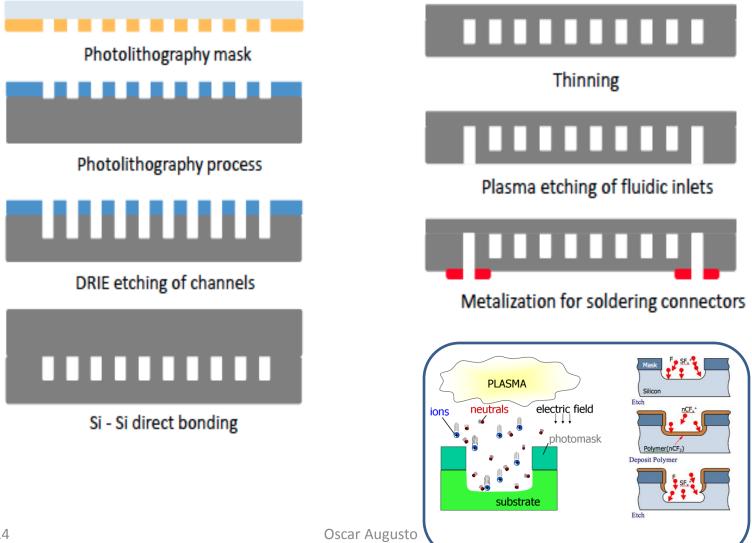

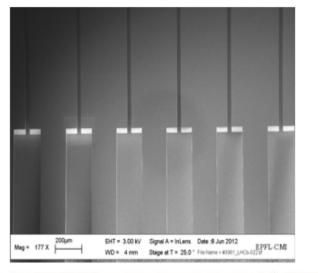

## Micro-channels fabrication

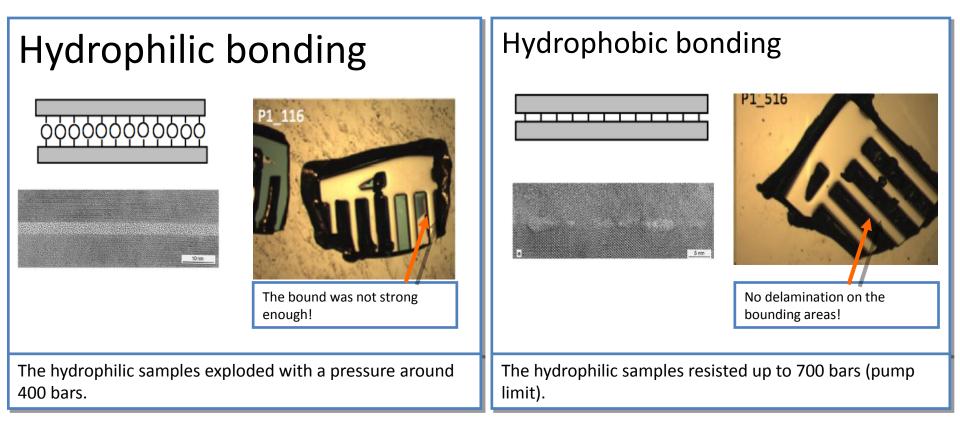

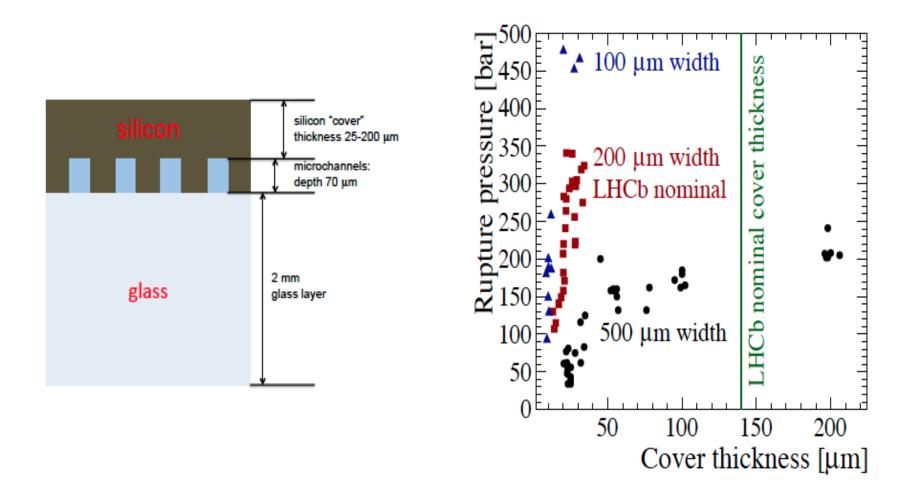

## Pressure resistance

#### for two types of direct (fusion) bonding

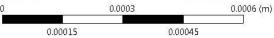

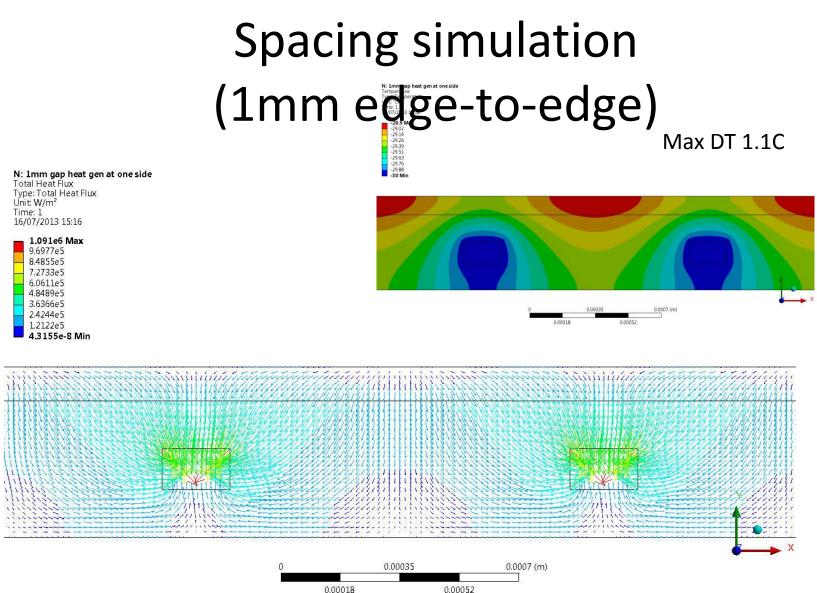

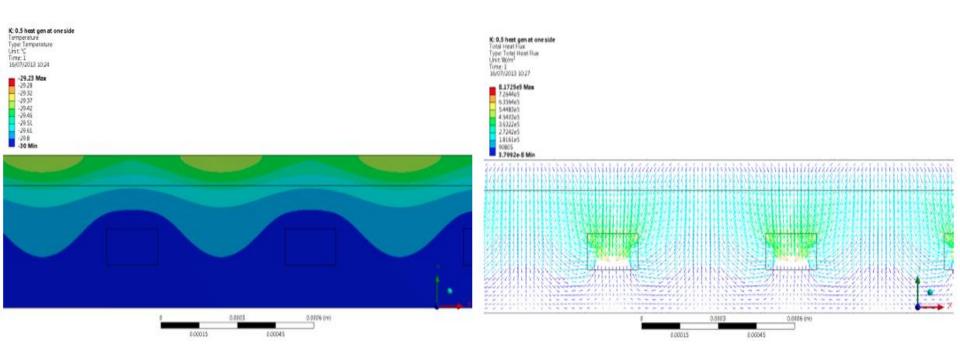

# Thermal simulation

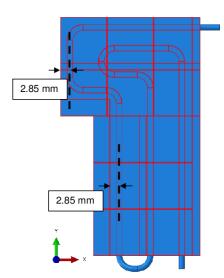

- Optimize the spacing distance between the channels for the new layout

- balance cooling efficiency against pressure resistance

- Simulation with a 3D model is done using ANSYS

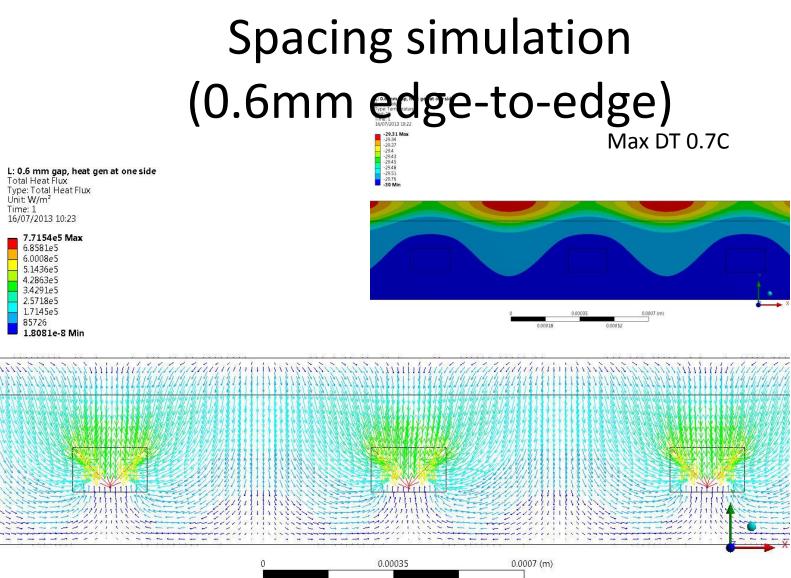

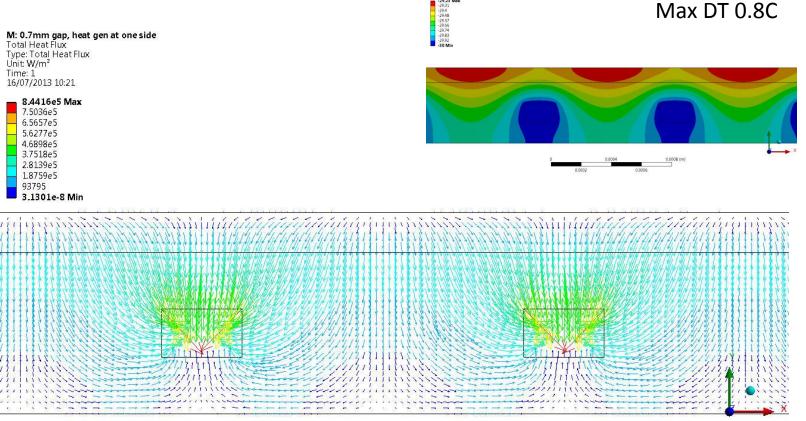

- Spacings of 500  $\mu m$  , 600  $\mu m$  , 700  $\mu m$  and 1000  $\mu m$

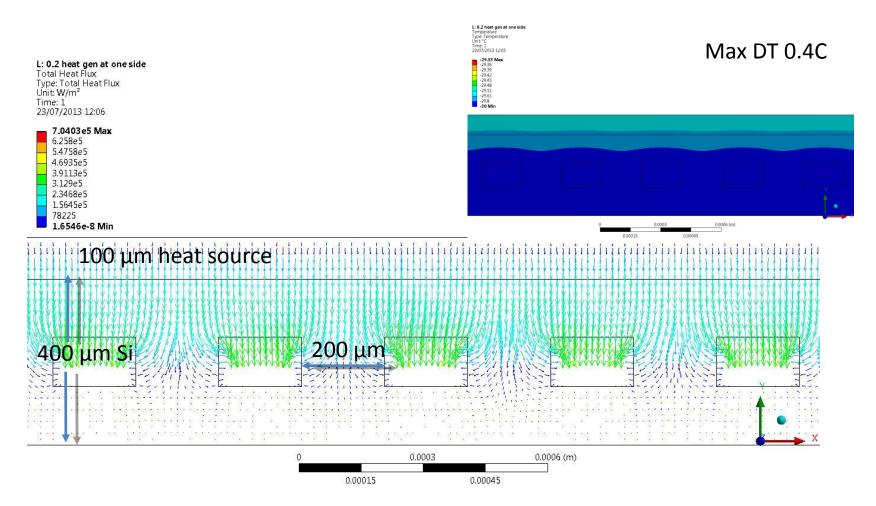

# Spacing simulation (0.2mm edge-toedge – current design)

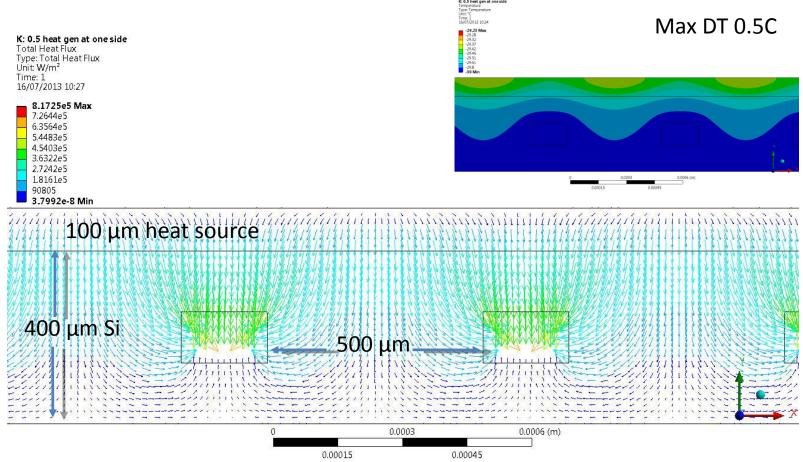

# Spacing simulation (0.5mm edge-to-edge)

This is taken for the new layout

0.00018

0.00052

# Spacing simulation (0.7mm edge-to-edge)

0.00018

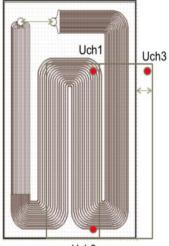

# Micro-channels prototype: Snake I

- "Snake I" prototype: 4 x 6 cm<sup>2</sup>

- 380µm silicon bounded to 2 mm Pyrex

- Dimensions\*

- Restrictions: 70µm x 30µm

- Micro-channels: 70μm x 200 μm

- The restrictions are designed to trigger the boiling

- It is critical to control the area on the output manifold

\*The diameter of the human hair is between  $17\mu m$  and  $181\mu m$ .

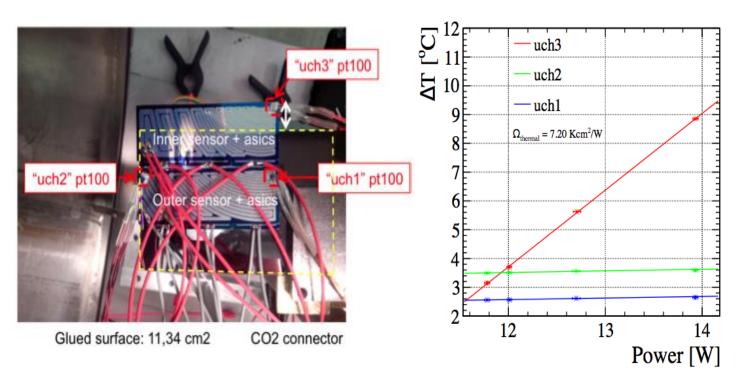

Uch2

# **Cooling performance**

The end of lifetime expectations corresponds to ~13W and on this conditions the maximum  $\Delta T$  across the module is less than 7°C (apart from the sensor tip the difference is only 1°C)

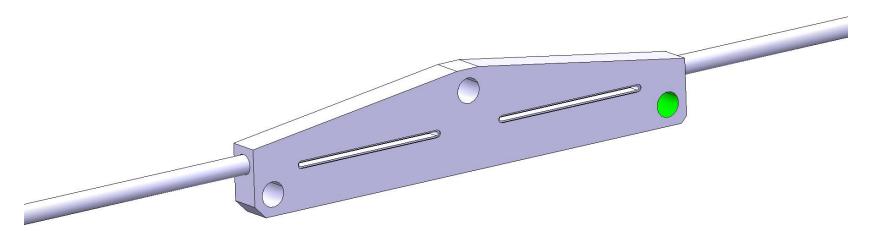

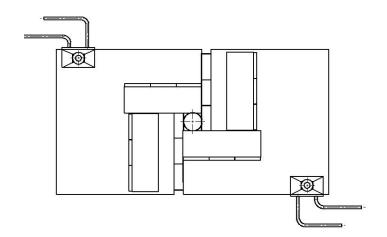

# Supplying the micro-channel wafer with CO<sub>2</sub>

- How to reliably join metal cooling pipes to a silicon wafer ?

- Metallize the silicon surface and solder

- Need to resist the pressure > 200 Bar

- Must not degrade with time (creep, corrosion)

- Must withstand numerous thermal cycles

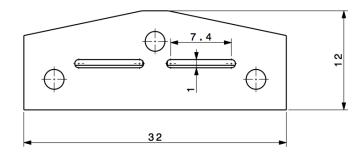

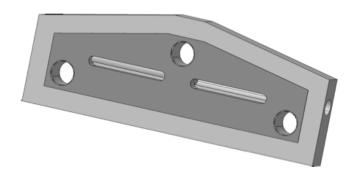

# **Connector soldering**

- Attachment of the fluidic connector on the silicon substrate

- Requirements:

- No interconnections between the voids

- Maximum dimensions of the void should not be bigger than 1 mm

- It should corresponds to less than 5 % of the total soldering area

- No flux (prevent corrosive effects on long term)

- Preform foil soldering technique with frame on vacuum

### **Connector soldering**

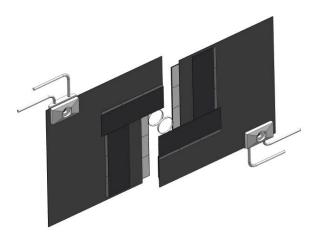

# Preform foil soldering technique with frame (with slids)

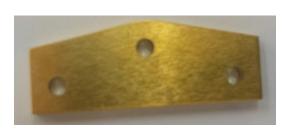

# Preform foil soldering technique with frame: components

Solder foil 50µm (made in our lab)

Small aluminium "washers" (D=2.46 mm) 20/05/14

Connector without the slits

Module0 Meeting

Silicon with the slits pattern on the metallization

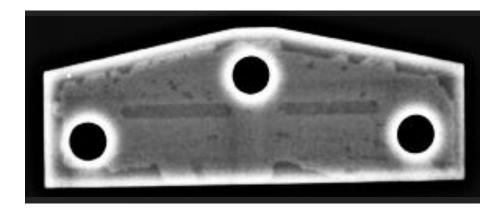

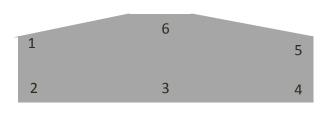

# Sample 66

#### Total thickness measurement

$1-3104\ \mu m$

- **2 3105 μm**

- 3 3099 µm

- 4 3109 μm

- 5 3108 µm

- $6-3111\,\mu\text{m}$

$\Delta h = 12 e \mu meting$

+5 $\mu m$  of Ni on the Si metallization

$T_{MAX} = 195^{\circ}C$ TAL = 46.5 s P = 1.8x10<sup>-3</sup> mbar

•Solder

- The solder moved out of the non metallized area (slits).

- The excess is constrained inside the frame

- No escape through the holes ("washers")

- •Voids

- Few voids

- Small (≤ 1 mm)

- Not interconnected

23

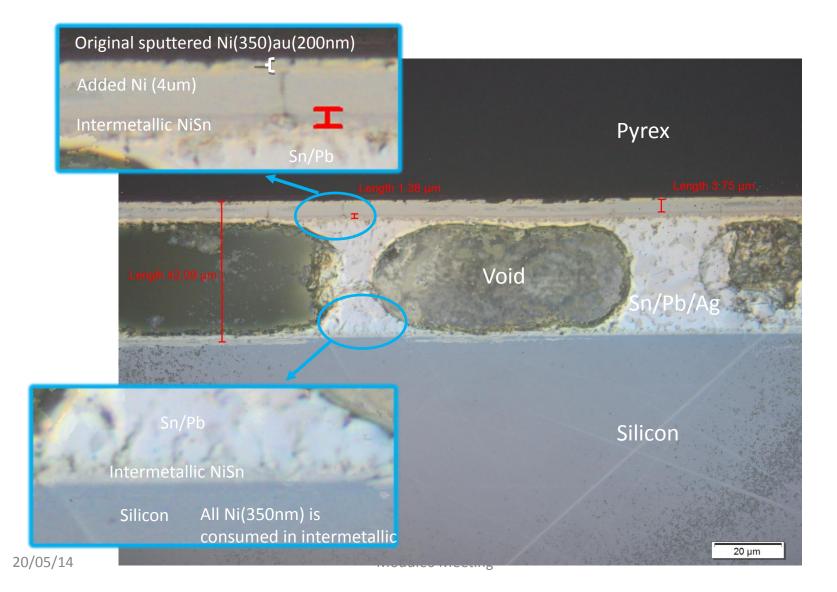

## Optical zoom 1000x on void in solder layer

# Solder leak test

- Leak test performed using water

- All samples resisted more than 70 bars

- Exploded with pressures around 80-145 (2 samples)

- The explosions happened exactly on the slits

- Is it too wide? New design for the slits?

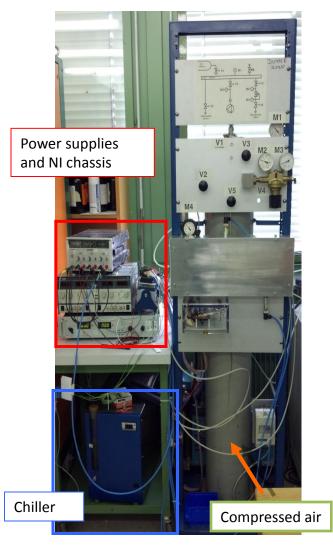

## Stress tests

- Perform temperature and pressure cycles:

- Pressure: 1-200 bars

- Temperature: -40°C up to + 40°C

- Ensure long system life

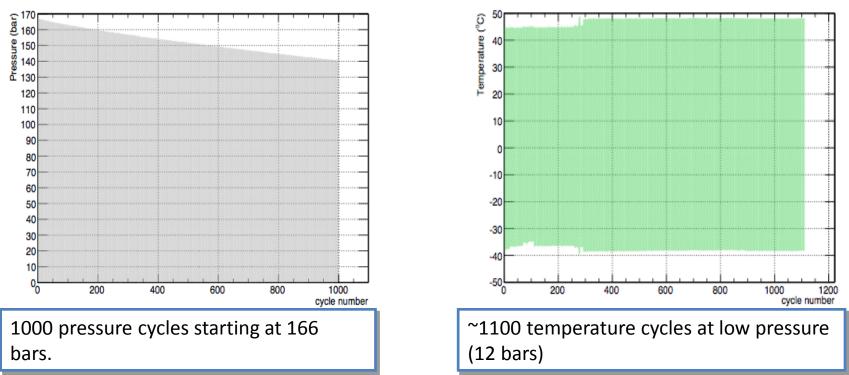

## Stress tests

Max and Min Temperature Pressure on the C2\_422\_222

Max and Min Pressure on the C3\_312

Thousands temperature and pressure cycles were performed on micro-channels samples without any sign of long term effect

## Summary

- LHCb VELO Detector will be built with microchannel cooled pixel modules

- Requirements for VELO are satisfied: material, power density, sensor tip temperature

- Reliability under pressure and temperature cycles

- Current intensive research around the soldering technique to join metal to silicon.

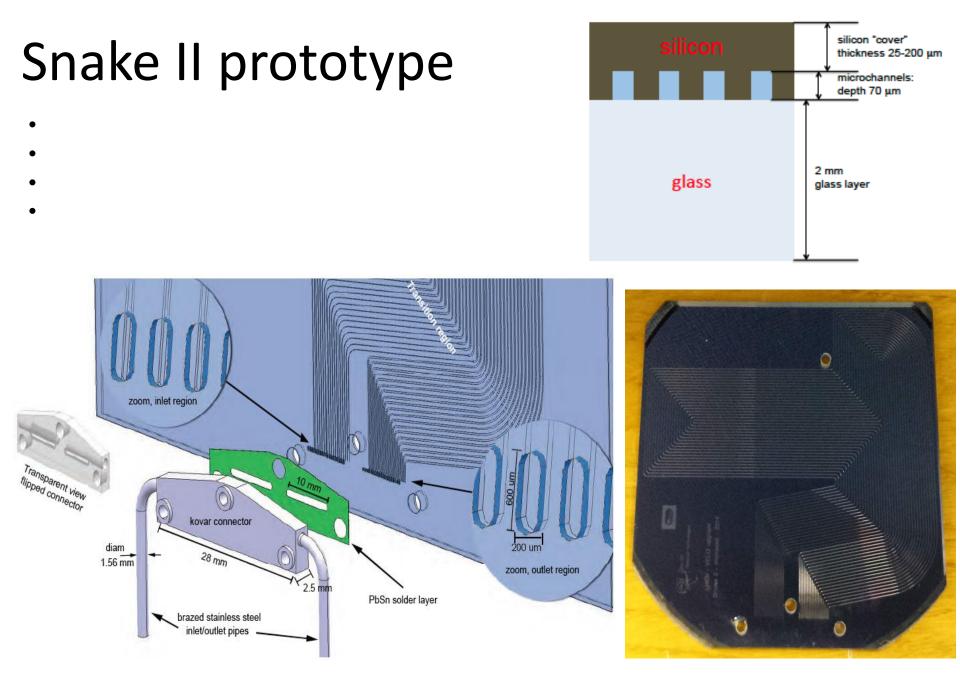

- New Snake II prototype from Lausanne

- More test samples from Southampton around September to be tested in Oxford

## Backup slides

## Snake II – Si Thickness

## Snake II – channel spacing

#### Criteria: Maximum $\Delta T < 1^{\circ}C$ The heat flow should use most of the silicon substrate

The spacing of 0.5 mm was chosen.

Oscar Augusto

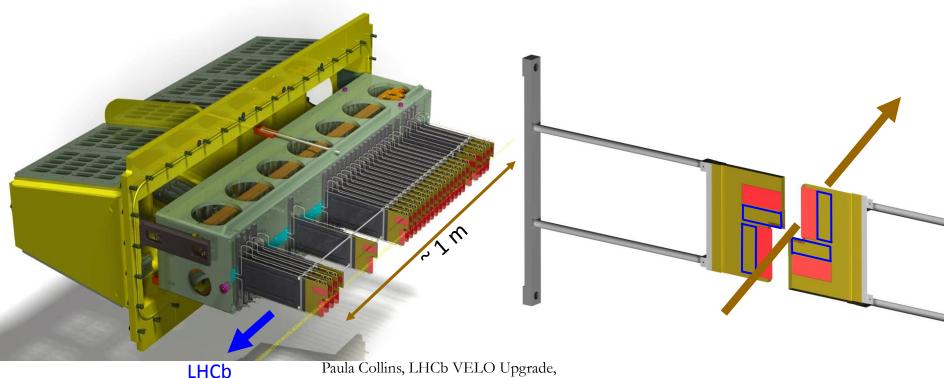

# Upgraded VELO (VErtex LOcator)

Function of VELO: provide precise tracking and trigger on displaced vertices

New Pixel detector approved by collaboration on 17<sup>th July 2013</sup> 26 stations arranged perpendicularly along the direction of the beam

varying spacing in beam direction, min. 24 mm between stations total active area 1237 cm2 (= size of A3 sheet of paper) Geometrical efficiency > 99 % for R < 10 mm

99 % of tracks from interaction region have 4 or more hits

15/05/14

Paula Collins, LHCb VELO Upgrade, IEEE/MIC 2013

# Challenges for upgraded VELO

Paula Collins, LHCb VELO Upgrade, IEEE/MIC 2013

## Two solutions proposed: Poco-foam and micro-channels

Figure 6. Structure 3, position of the cool pipes

# Micro-channel cooling

#### High speed pixel readout chips produce

36

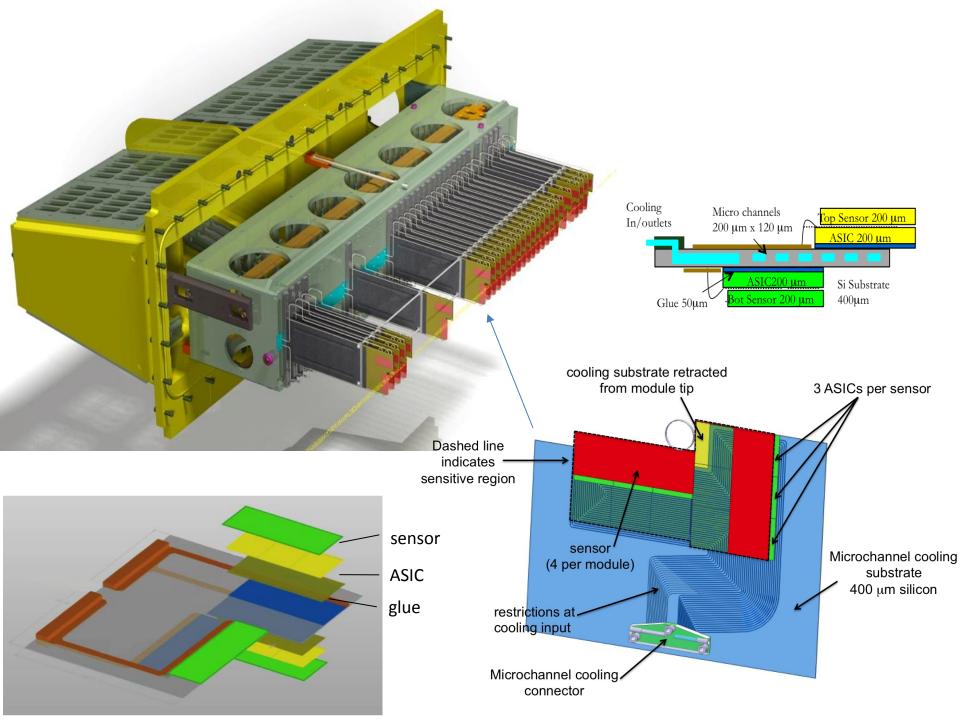

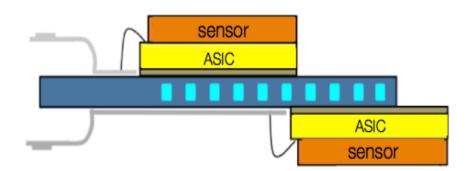

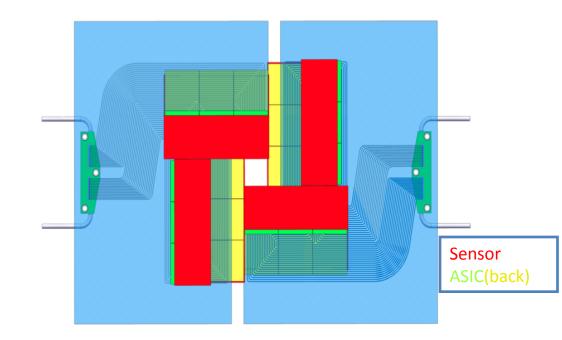

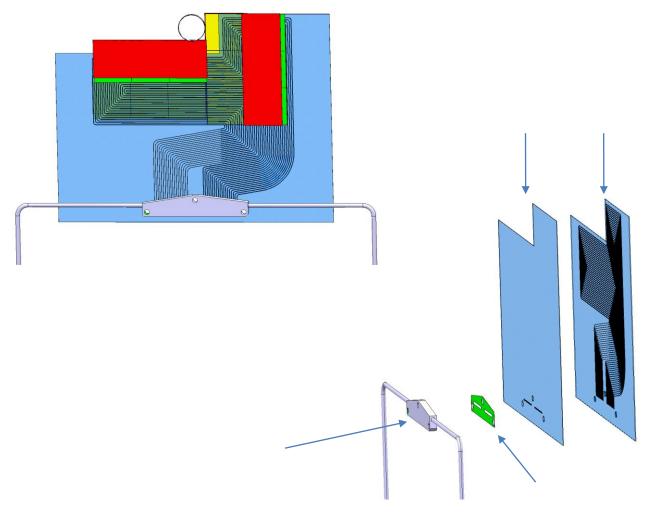

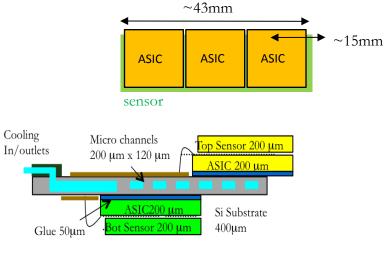

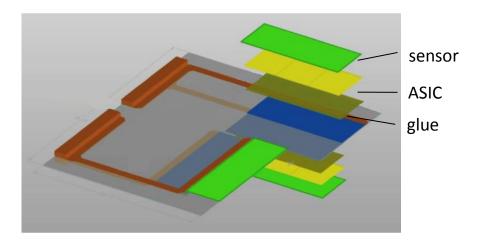

## VELO module

#### Sensor tiles: 3 readout VeloPix ASICs on a sensor:

55 x 55 μm<sup>2</sup> pixels elongated pixels between ASICs ~450 μm guard ring

4 sensor tiles, 2 on each side of substrate power and readout traces on kapton circuit board

Whole VELO ~41 Mpixels

Silicon substrate with integrated micro-channels for cooling

Material in active region ~ 0.8 % X

### Why CO<sub>2</sub> evaporative cooling in silicon microchannels?

- Silicon microchannels

- Cooling is under the heat source

- Low mass The substrate is also the cooling

- No mismatch of expansion coefficients

CO<sub>2</sub>

- High latent heat

- Low viscosity

- Not toxic

- Inert gas

- Cheap

- Radiation hard

### Micro channel cooling II

**Channel dimensions 200 x 120 µm<sup>2</sup>** Operational Pressure ~15 Bar at -30 °C, and ~60 Bar at room temp. Including safety limits it has to withstand > 150 Bar Samples with hydrophobic bonding withstand > 700 Bar Thermal and pressure cycling tests (-40 .. +40 °C, 0 .. 200 Bar) ongoing

Paula Collins, LHCb VELO Upgrade, IEEE/MIC 2013