### CMS Pixel-Strip Project

ACES 2014 - Fourth Common ATLAS CMS Electronics Workshop for LHC upgrades Wednesday, 19 March 2014

Kostas Kloukinas PH-ESE, CERN on behalf of the CMS Tracker PS module R&D team

### Motivation

The Pixel-Strip Module concept

- The Macro Pixel ASIC (MPA)

- The MPA-light prototype

### Conclusions & Future Plans

- CMS Tracker upgrades at High Luminosity LHC

- HL-LHC: sustained luminosity of 5x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- More than 100 pileup events per bunch crossing @ 40MHZ

- μ, e and jet rates exceed the 100 kHz rate

- Increasing thresholds would affect physics performance

- Performance of algorithms degrades with increasing pile-up

- Add tracking information at Level-1 selection

- Reconstruct "all" tracks above 2 GeV

- Identify the vertex origin along the beam axis with ~ 1 mm precision

### Modules with p<sub>T</sub> discrimination

Reject locally signals from low-p<sub>T</sub> particles

### The Pixel Strip (PS) module

Kostas.Kloukinas@cern.ch

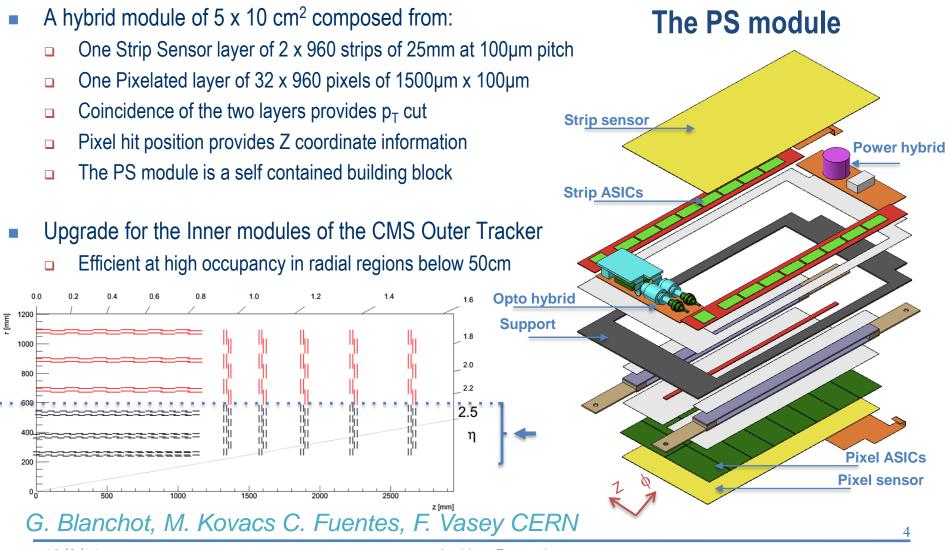

## PS module (baseline)

- Each PS module is composed from Pixel and Sensor layers.

- Strips are readout from <u>16 Short Strip ASICs (SSA)</u>

- Pixels are readout from <u>16 Macro Pixel ASICs (MPA)</u>

- Pixel/Strip hits are analysed to find stubs in the MPA periphery.

- A stub is a particle with a momentum > 2 GeV/c which crosses the two sensor layers.

- Found Stubs are sent out at each Bunch Crossing (25 ns) while the full event is stored locally and is sent out only if requested with a L1 Trigger signal.

- L1 Trigger Signal is generated outside from the Tracker.

1 mm

100 mm

2

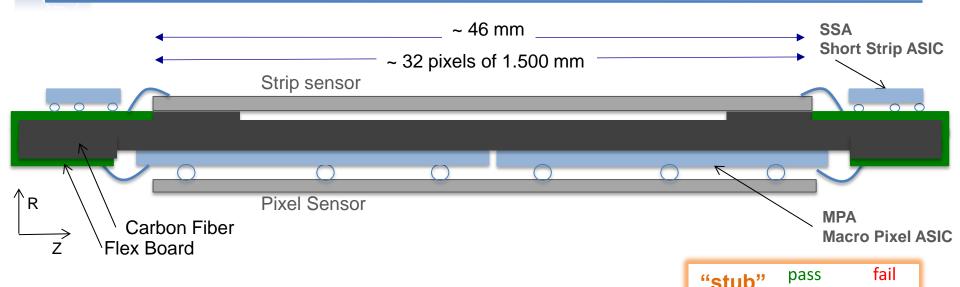

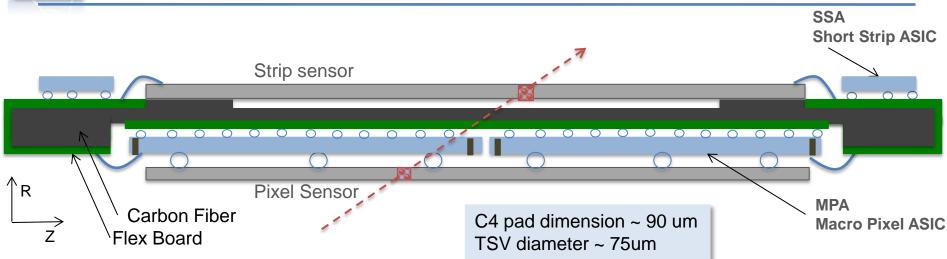

## PS module with TSVs

- Connectivity along Z-direction on modules can make possible the tracking of particles that cross the readout areas of two MPAs

- Increases the average readout efficiency by  $\sim 10\%$  (more important for tracks at high  $\eta$ )

- This interconnectivity necessitates the use of TSVs on the MPAs

- Possible implementations include the use of bumped flex board

- This solution can improve the power distribution on the MPAs

- The TSV option is being evaluated and preliminary contacts with industry are in place

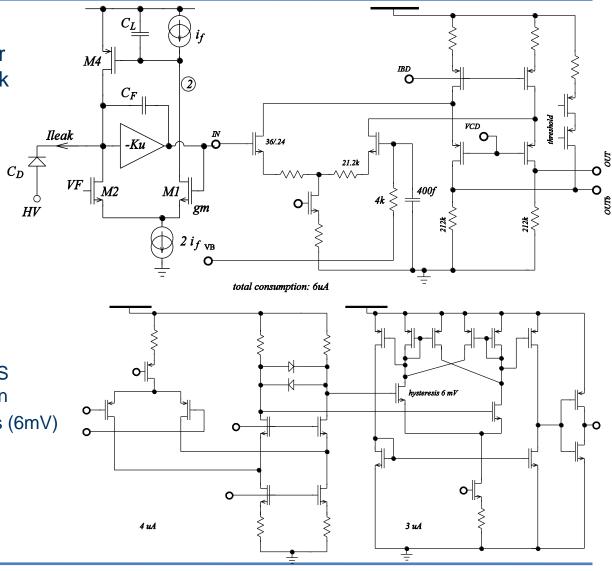

### MPA analog FE architecture

- Transimpedance Preamplifier with Krummenacher feedback leakage compensation for n<sup>+</sup> on p<sup>-</sup> detectors

- Single-ended to differential folded cascode stage with resistive load

- Discriminator with:

- PMOS folded cascode input

- Swing limiter based on PMOS working in diode configuration

- Second stage with hysteresis (6mV)

### J. Kaplon, CERN

19/3/14

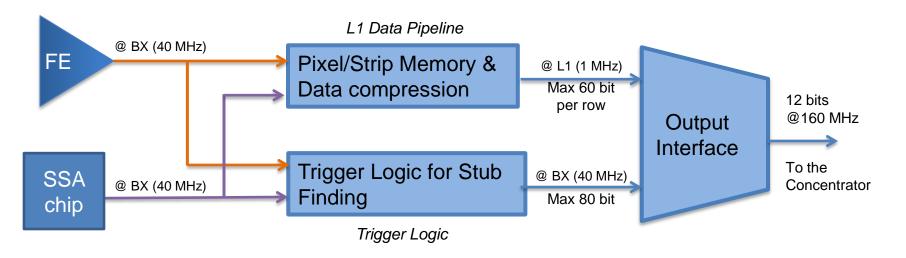

#### Input each 25 ns (40 MHz):

Pixel hits from Front- End: 120 columns x 16 rows = 1920 hits

Strip hits from SSA chip: 120 hits

L1 Data Pipeline stores data for the duration of the L1 latency (10 or 20 µsec). Upon arrival of L1, data are sent to the Data Compression block and then to concentrator.

*Trigger Logic* elaborates inputs synchronously with the bunch crossing and looks for the coincidences between pixel and strip hits in order to generate stubs.

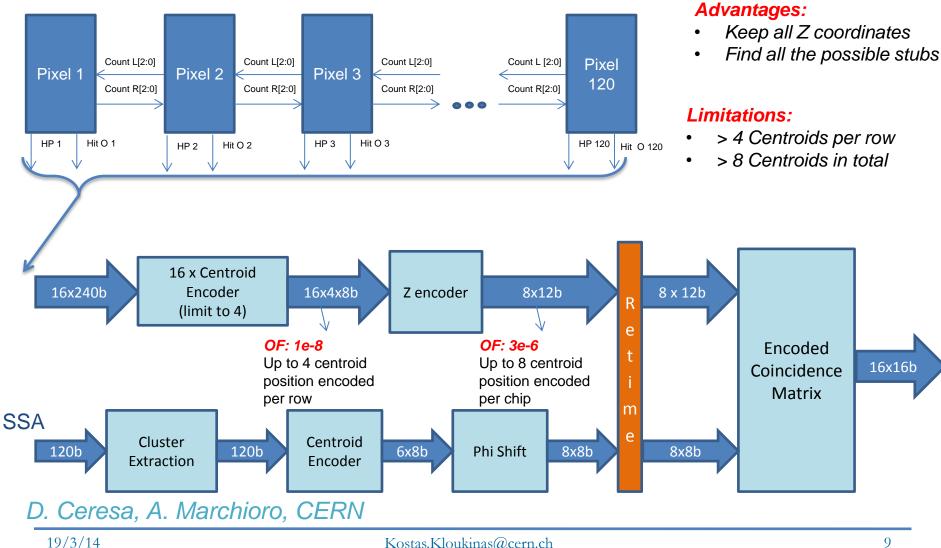

# MPA Trigger Logic for Stub finding

Wide Cluster Elimination + Centroid Extraction (6 wire x 100 um for each pixel)

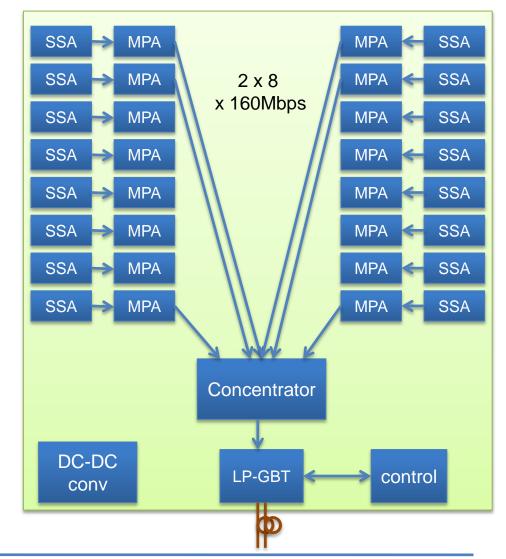

# Module Readout Architecture

- Star bus readout

- Low voltage differential signals

- @ 160MBps

- Data Concentrator ASIC

- Aggregates data from MPAs

- Construct data packets

- Transmit data via the LP-GBT

- Handle channel bandwidth for Trigger & Readout data

- Respecting a fixed trigger latency

- Minimize readout event losse

- 130nm or 65nm (low power) process

- LP-GBT

- Low Power GigaBit Transceiver

- 65nm (low power) process

- Power per module for readout ASICs: 4 W

- < 250 mW per MPA chip</p>

- $\sim$  < 1/3 into analog, i.e. 80 mW, or < 40  $\mu$ W/pixel

- 65nm LP (Low Power) process (LP also means "slower"!)

- Analog FE circuitry:

- 1.2V supply, < 30µA/channel (up to discriminator output, not including common biases overhead)

- 22 ns pulse shaping S/N: > 20

- Digital logic :

- 1.2V supply, possibly 0.85V for slow digital circuitry

- Low power design techniques in clock distribution network

- Development of special low leakage SRAM for readout FIFOs (outsourced IP block)

- Development of CMOS IO pads using thin gate devices (outsourced IP block)

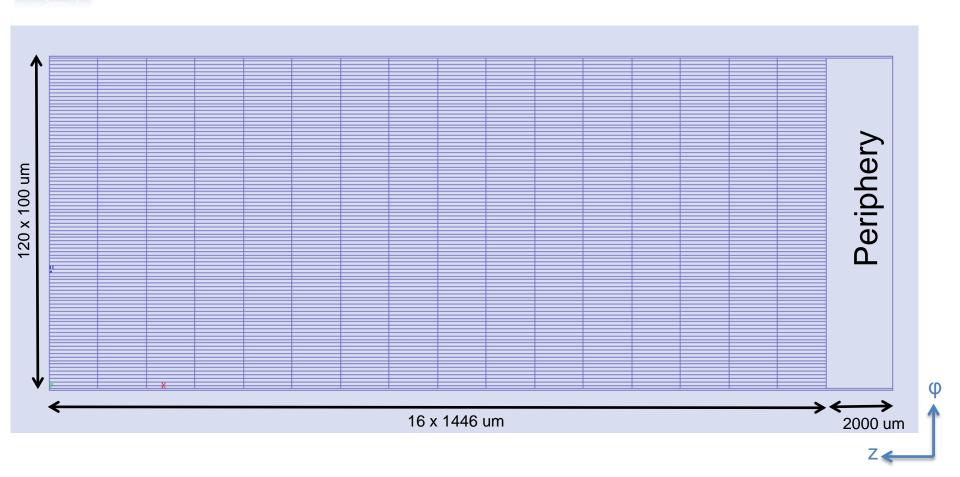

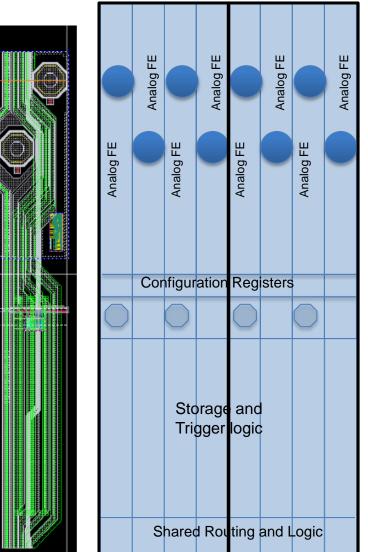

#### 120 columns x 16 rows = 1,920 pixels

#### Pixel Floorplan providing a framework for:

- detector shielding from electronic noise

- routing power of critical analog blocks

- routing long digital lines

- enable possible usage of TSVs

#### Decision for an 8 metal stack process

| M1 | m1  | local    | cell                      |  |

|----|-----|----------|---------------------------|--|

| M2 | х   | local    | cell                      |  |

| M3 | х   | local    | cell and block            |  |

| M4 | х   | local    | cell and block            |  |

| M5 | х   | regional | cell and group and shield |  |

| M6 | Z   | global   | clk and pwr               |  |

| M7 | u   | global   | clk, pwr and shield       |  |

| M8 | RDL | global   | pads and GND              |  |

Example layout of top layers

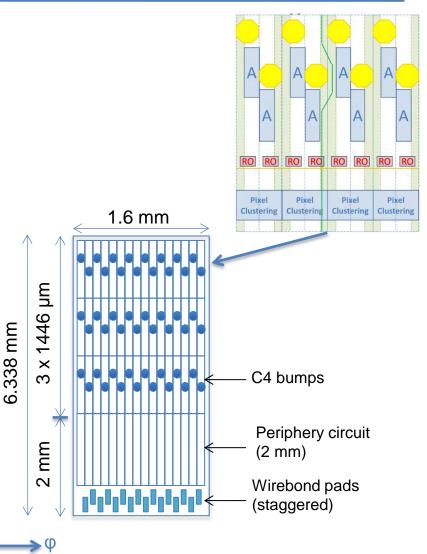

## The MPA-light demonstrator

- A reduced size MPA design

- 16 x 3 pixels (instead of 120 x 16)

- Size of single pixel (as final): 100 x 1446 um

- Bump-bond pad size: 90 mm

- Pitch 200 mm horizontal, 300 mm vertical

- Wirebond pads for hybrid connections

- Pixel floorplanning similar to the final MPA

- Scalable to the final design

#### Purpose

- Prototype & qualify the analog FE circuitry

- Facilitate the development of the sensor

- Understand and solve the numerous technical aspects of the Module Assembly

7

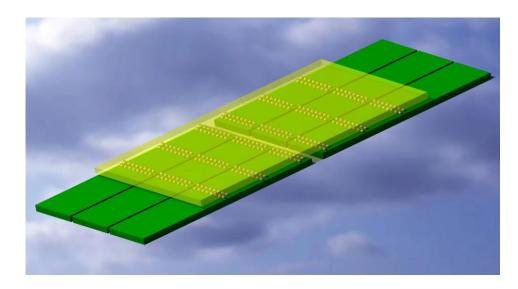

- MAcro Pixel Sub Assembly (MAPSA) light

- Objective is to assemble a module of 3 x 2 MPA-light chips for a total of 288 pixels z

- Bump-bondable to detector

- Wire-bondable to hybrid

- Floorplan allows for TSV experimentation

| 5.4 mm                                                                                                                                                |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| 0 <sup>0</sup> | 0 <sup>0</sup> | 0 <sup>0</sup> |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       | 12.676 |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

|                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

| <u>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup>0<sup>0</sup></u>             | 00000000000000000000000000000000000000                                                                                                                | 000000000000000000000000000000000000000                                                                                                               |        |  |  |  |

| <b>→</b> Φ                                                                                                                                            |                                                                                                                                                       |                                                                                                                                                       |        |  |  |  |

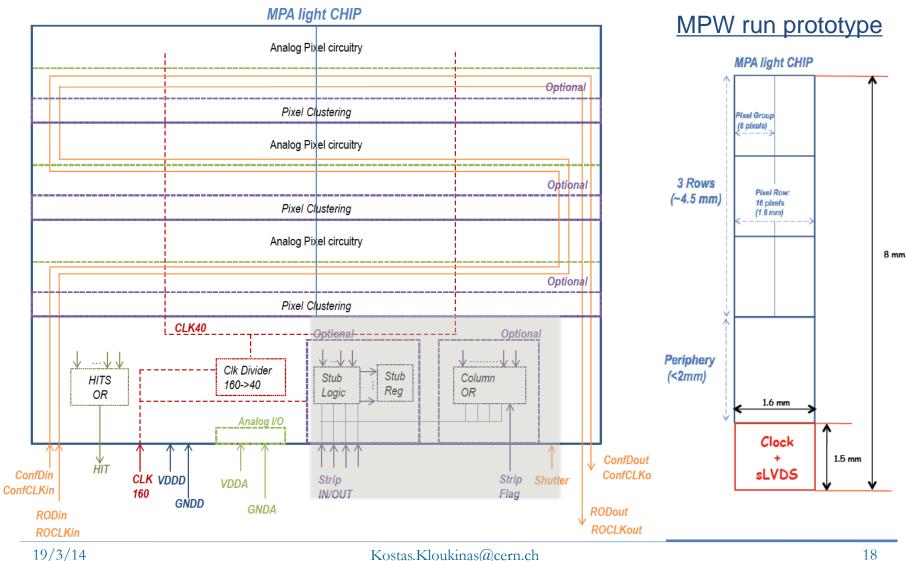

# MPA-Light functionalities (baseline)

#### Full analog chain as in final module

- Preamp-shaper

- Discriminator

- DAC for threshold adjustment

- DAC for global biasing

- Calibration circuit

- Read-Out via single serial shift register per chip

- Capability of single-hit or multiple-hit-counter mode (16-bit) per pixel

- Configuration with serial shift register (16-bit/pixel)

- Simple trigger (OR of channels)

- No L1 buffer, no concentrator interface

- Separate analog and digital power domains

- Analog 1.2 V

- Digital: explore capability of decreasing supply voltage to 0.85 V

- Power & Clock Routing scheme as close as possible to the final MPA

- 65nm process on 8 metals, as in the final MPA

## MPA-Light additional functionalities

- Additional functionalities focuses on the testing of the Stub Finding Logic (the logic needed to provide L1 trigger tracking information)

- Pixel Row and Strip Clustering

- Hits Encoder

- Phi-Shift logic

- Implement a "Strip-like" configuration mode for the pixels, thus emulating a strip sensor layer

- Implement interconnect bus between MPA-light chips transmitting hits at 160MHz from the "Strip-like" layer to the pixel layer electronics

- Implement Coincidence and Stub Sorting logic

- Drivers and receivers sLVDS-CMOS (320Mbps and 640Mbps, 0.8 and 1.2V bias voltage)

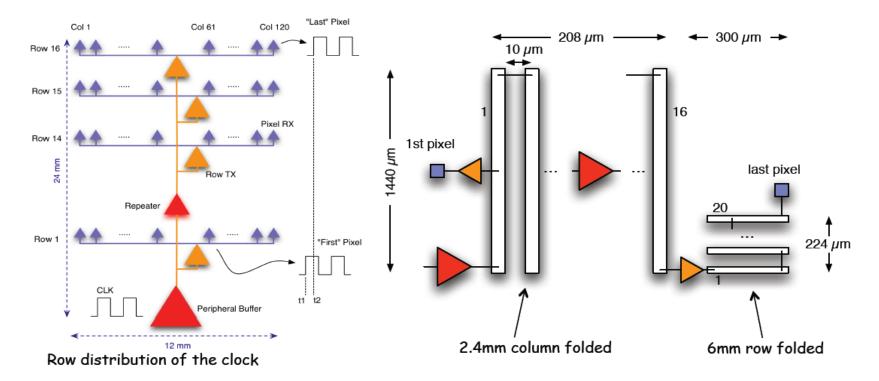

- 2. Test structure to simulate the propagation delay, skew and power consumption of the row distribution of the clock

V. Re, G. Traversi, L. Gaioni, F. De Canio – U. Pavia and INFN Bergamo

- Promising concept of Pixel-Strip module with local  $p_T$  discrimination

- Choice of technologies is driven by the optimization of the tracker performance

- Low Power ASIC technology combined with system level Low Power techniques

- Lightweight module assembly, avoiding the use of thick interposers

- Use of commercial technologies compatible with large volume production having the perspective of high yield at an affordable cost

- R&D on TSVs is an important element for the performance of the final design

- MPA-light prototyping scheduled for end of Q3 2014

- MAPSA-light prototyping targeted for the end of Q4 2014

- Results will pave the way towards the final PS module design (2016-17)

Acknowledgements: Most of the ideas and the work by A. Marchioro

19/3/14

sLVS Differential IO pads

- Development of scalable Low Voltage Signaling (sLVS) differential IO pads for PS module ASIC interconnections:

- SSA to MPA

- MPA to Concentrator

- Different loads:

- 300 fF (SSA outputs)

- I0 pF (MPA outputs)

- 2.5cm, 6cm, 10.5cm long transmission line on the thin hybrid toward the concentrator

- Low-power consumption design: 15mW

- 12 differential lines at 320 Mbps (1.25mW per link, i.e. TX/RX)

- 6 differential lines at 640 Mbps (2.5mW per link, i.e. TX/RX)

- Power supply: 1.2V (nominal)

- Work in progress targeting 0.85 V

V. Re, G. Traversi, L. Gaioni, F. De Canio – U. Pavia and INFN Bergamo