### ATLAS–CMS-LCD **RD53** collaboration:

Pixel readout integrated circuits for extreme rate and radiation

Jorgen Christiansen on behalf of RD53

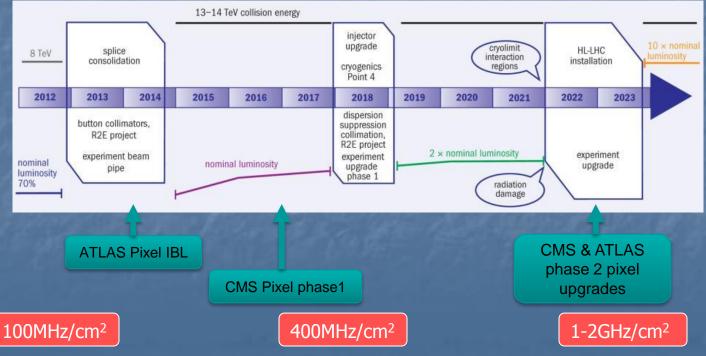

# LHC Pixel upgrades

- Current LHC pixel detectors have clearly demonstrated the feasibility and power of pixel detectors for tracking in high rate environments

- Phase0/1 upgrades: Additional pixel layer, ~4 x hit rates

- ATLAS: Addition of Inner B Layer (IBL) with new 130nm pixel ASIC (FEI4)

- CMS: New pixel detector with modified 250nm pixel ASIC (PSI46DIG)

- Phase2 upgrades: ~16 x hit rates, ~4 x better resolution, 10 x trigger rates, 16 x radiation tolerance, Increased forward coverage, less material, , ,

- Installation: ~ 2022

- Relies fully on significantly improved performance from next generation pixel chips.

# Phase 2 pixel challenges

#### ATLAS and CMS phase 2 pixel upgrades very challenging

- Very high particle rates: 500MHz/cm<sup>2</sup>

- Hit rates: 1-2 GHz/cm<sup>2</sup> (factor  $\sim$ 16 higher than current pixel detectors)

- Smaller pixels: ~¼ (~50x50um<sup>2</sup> or 25x100um<sup>2</sup>)

- Increased resolution

- Improved two track separation (jets)

- Outer layers can be larger pixels, using same pixel chip

- Participation in first/second level trigger ? (no)

- A. 40MHz extracted clusters (outer layers) ?

- B. Region of interest readout for second level trigger ?

- Increased readout rates: 100kHz -> ~1MHz

- Data rate: 10x trigger X >10x hit rate = >100x !

- Low mass -> Low power

Very similar requirements (and uncertainties) for ATLAS & CMS

- Unprecedented hostile radiation: ~1Grad, ~10<sup>16</sup> Neu/cm<sup>2</sup>

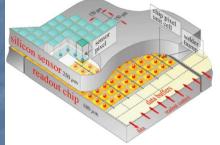

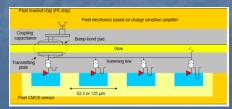

- Hybrid pixel detector with separate readout chip and sensor.

Monolithic seems unfeasible for this very high rate hostile radiation environment

- Phase2 pixel will get in 1 year what we now get in 10 years (10.000 x more radiation than space/mil !)

- Pixel sensor(s) not yet determined

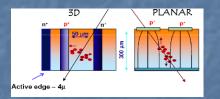

- Planar, 3D, Diamond, HV CMOS, ,,

- Possibility of using different sensors in different layers

- Final sensor decision may come relatively late.

- Complex, high rate and radiation hard pixel chips required

ATLAS HVCMOS program

### Pixel chip

#### Pixel readout chips critical to be ready for phase 2 upgrades

- Technology: Radiation qualification

- Building blocks: Design, prototyping and test

- Architecture definition/optimization/verification

- Chip prototyping, iterations, test, qualification and production

- System integration

- System integration tests and test-beams

- Production and final system integration, test and commissioning

#### Phase 2 pixel chip very challenging

- Radiation

- Reliability: Several storage nodes will have SEUs every second per chip.

- High rates

- Mixed signal with very tight integration of analog and digital

- Complex: ~256k channel DAQ system on a single chip

- Large chip: >2cm x 2cm,  $\frac{1}{2}$  1 Billion transistors.

- Very low power: Low power design and on chip power conversion

- ATLAS and CMS have evolved to similar pixel chip architectures and plans to use same technology (65nm) for its implementation.

- Experienced chip designers for complex mixed signal ICs in modern technologies that must work in a extremely harsh radiation environment is a scarce and distributed "resource" in HEP.

# Pixel chip generations

| Generation          | Current<br>FEI3, PSI46                                        | Phase 1<br>FEI4, PSI46DIG                                     | Phase 2: HL-LHC               |

|---------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|

| Pixel size          | 100x150um <sup>2</sup> (CMS)<br>50x400um <sup>2</sup> (ATLAS) | 100x150um <sup>2</sup> (CMS)<br>50x250um <sup>2</sup> (ATLAS) | ~ <b>50x50um</b> <sup>2</sup> |

| Sensor              | 2D, ~300um                                                    | 2D+3D (ATLAS)<br>2D (CMS)                                     | 2D, 3D, Diamond,<br>HVCMOS ?  |

| Chip size           | 7.5x10.5mm <sup>2</sup> (ATLAS)<br>8x10mm <sup>2</sup> (CMS)  | 20x20mm <sup>2</sup> (ATLAS)<br>8x10mm <sup>2</sup> (CMS)     | > 20 x 20 mm <sup>2</sup>     |

| Transistors         | 1.3M (CMS)<br>3.5M (ATLAS)                                    | 87M (ATLAS)                                                   | ~1G                           |

| Hit rate            | 100MHz/cm <sup>2</sup>                                        | 400MHz/cm <sup>2</sup>                                        | 1-2 GHz/cm <sup>2</sup>       |

| Trigger rate        | 100kHz                                                        | 100KHz                                                        | 200kHz - <b>1MHz</b>          |

| Trigger latency     | 2.5us (ATLAS)<br>3.2us (CMS)                                  | 2.5us (ATLAS)<br>3.2us (CMS)                                  | 6 - <b>20us</b>               |

| Hit memory per chip | 0.1Mb                                                         | 1Mb                                                           | ~16Mb <b>(160x)</b>           |

| Readout rate        | 40Mb/s                                                        | 320Mb/s                                                       | 1-4Gb/s (100x)                |

| Radiation           | 100Mrad                                                       | 200Mrad                                                       | 1Grad                         |

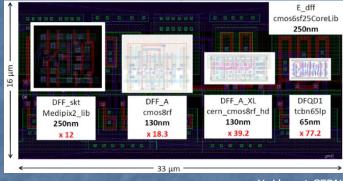

| Technology          | 250nm                                                         | 130nm (ATLAS)<br>250 nm (CMS)                                 | 65nm                          |

| Architecture        | Digital (ATLAS)<br>Analog (CMS)                               | Digital (ATLAS)<br>Analog (CMS)                               | Digital                       |

| Buffer location     | EOC                                                           | Pixel (ATLAS)<br>EOC (CMS)                                    | In Pixel buffering            |

| Power               | ~1/4 W/cm <sup>2</sup>                                        | ~1/4 W/cm <sup>2</sup>                                        | 1/2 - 1 W/cm <sup>2</sup>     |

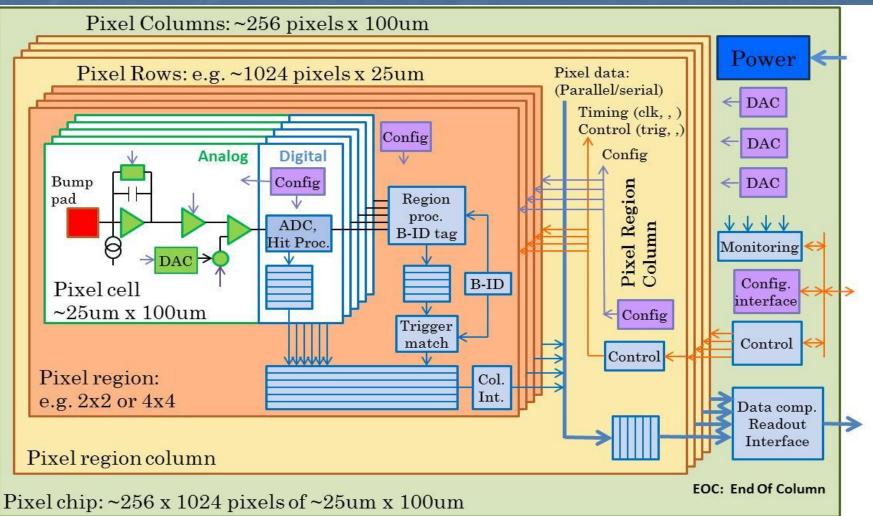

# 3<sup>rd</sup> generation pixel architecture

- 95% digital (as FEI4)

- Charge digitization (TOT or ADC)

- ~256k pixel channels per chip

- Pixel regions with buffering

- Data compression in End Of Column

- Chip size: >20 x 20 mm<sup>2</sup>

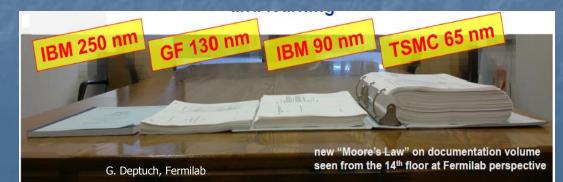

# Technology: Why 65

#### Mature technology:

Available since ~2007

#### High density and low power

- High density vital for smaller pixels and ~100x increased buffering during trigger latency

- Low power tech critical to maintain acceptable power for higher pixel density and much higher data rates

- Long term availability

- Strong technology node used extensively for industrial/automotive

- Access: CERN frame-contract with TSMC and IMEC

- Design tool set, Shared MPW runs, Libraries, Design exchange within HEP community

- Affordable (MPW from foundry and Europractice, ~1M NRE for final chips)

- Significantly increased density, speed, , , and complexity compared to 130nm !

#### Introducing 14XM (eXtreme Mobility)

X. Llopart CERN

7

# 65nm Technology

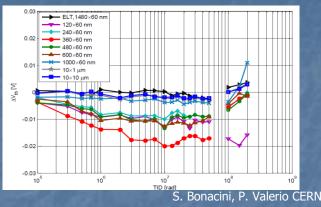

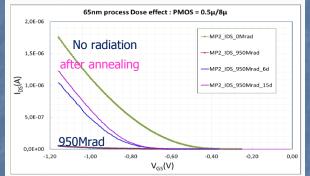

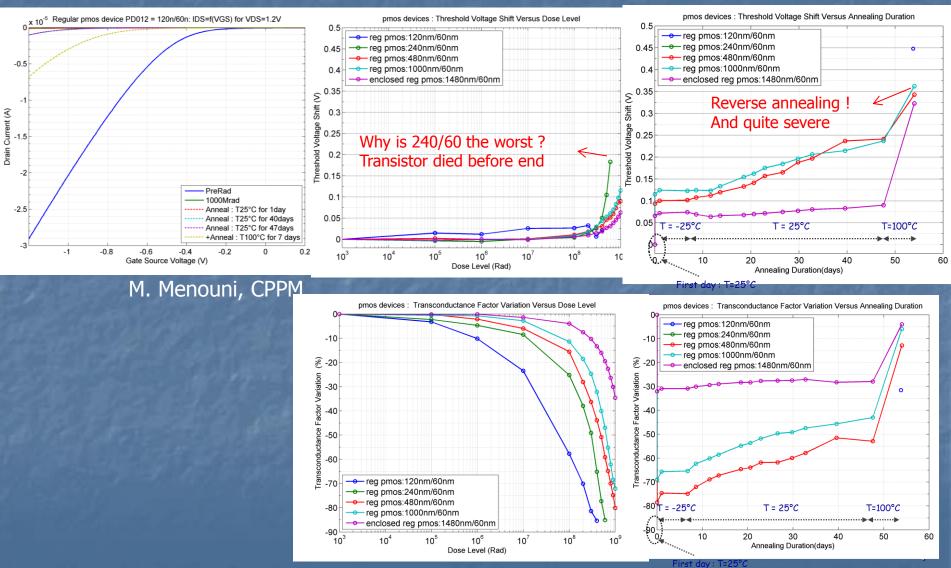

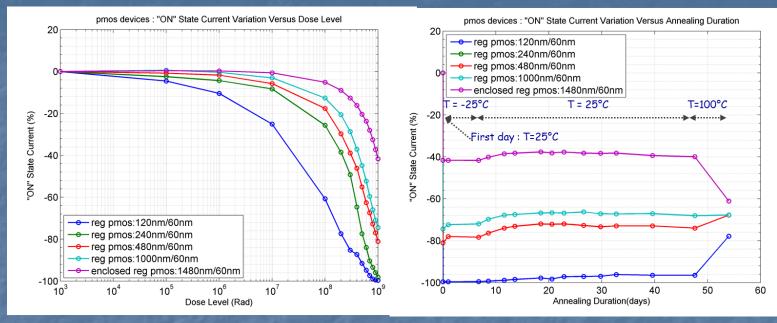

#### Radiation hardness

- Uses thin gate oxide

- Radiation induced trapped charges removed by tunneling

- More modern technologies use thick High K gate "oxide" with reduced tunneling/leakage ?.

- Verified for up to 200Mrad

- To be confirmed for 1Grad

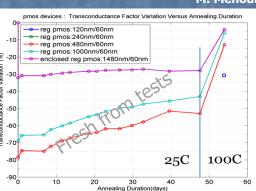

- PMOS transistor drive degradation, V<sub>t</sub> shift, Annealing ?

- CMOS normally not affect by NIEL

- To be confirmed for 10<sup>16</sup> Neu/cm<sup>2</sup>

- Certain circuits using "parasitic" bipolars to be redesigned ?

- SEU tolerance to be built in (as in 130 and 250nm)

- SEU cross-section reduced with size of storage element, but we will put a lot more per chip

- All circuits must be designed for radiation environment ( e.g. Modified SRAM)

- Annealing scenario critical

- Detectors will run cold (~-20°C)

- Yearly annealing periods ? (room temp or higher ?)

- If unacceptable degradation then other technologies (alternative foundries, 40nm, etc.) must be evaluated and/or a replacement strategy must be applied for inner pixel layers.

### ATLAS – CMS RD collaboration

- Similar/identical requirements, same technology choice and limited availability of rad hard IC design experts in HEP makes this ideal for a close CMS – ATLAS RD collaboration

- Even if we do not make a final common pixel chip

Forming a RD collaboration has attracted additional groups and collaborators

- Synergy with CLIC pixel (and others): Technology, Rad tol, Tools, etc.

- RD53 collaboration recommended by LHCC June 2013

- Institutes: 17 (+ 3 new applicants)

- ATLAS: CERN, Bonn, CPPM, LBNL, LPNHE Paris, NIKHEF, New Mexico, RAL, UC Santa Cruz.

- CMS: Bari, Bergamo-Pavia, CERN, Fermilab, Padova, Perugia, Pisa, PSI, RAL, Torino.

- Collaborators: ~100, ~50% chip designers

- Collaboration organized by Institute Board (IB) with technical work done in specialized Working Groups (WG)

- Initial work program covers ~3 years to make foundation for final pixel chips

- Co-spokes persons: ATLAS: M. Garcia-Sciveres, LBNL. CMS: J. Christiansen, CERN

RD53 web (new): <u>www.cern.ch/RD53/</u>

# Working groups

#### WG Domain

#### WG1 Radiation test/qualification: M. Barbero, CPPM

Coordinate test and qualification of 65nm for 1Grad TID and 10<sup>16</sup> neu/cm<sup>2</sup> Radiation tests and reports.

Transistor simulation models after radiation degradation Expertise on radiation effects in 65nm

#### WG2 Top level: (M. Garcia-sciveres, LBNL)

Design Methodology/tools for large complex pixel chip Integration of analog in large digital design Design and verification methodology for very large chips. Design methodology for low power design/synthesis. Clock distribution and optimization.

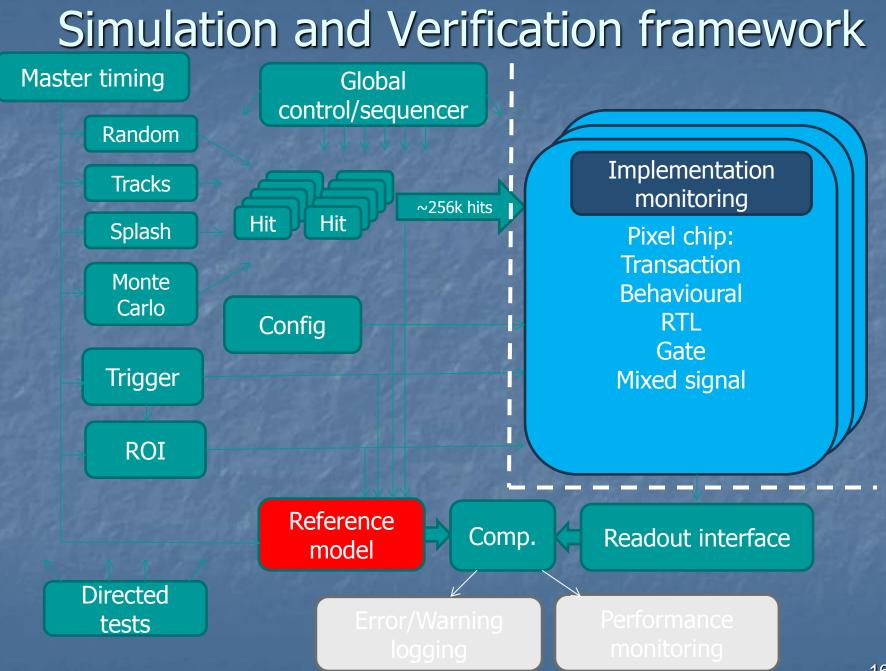

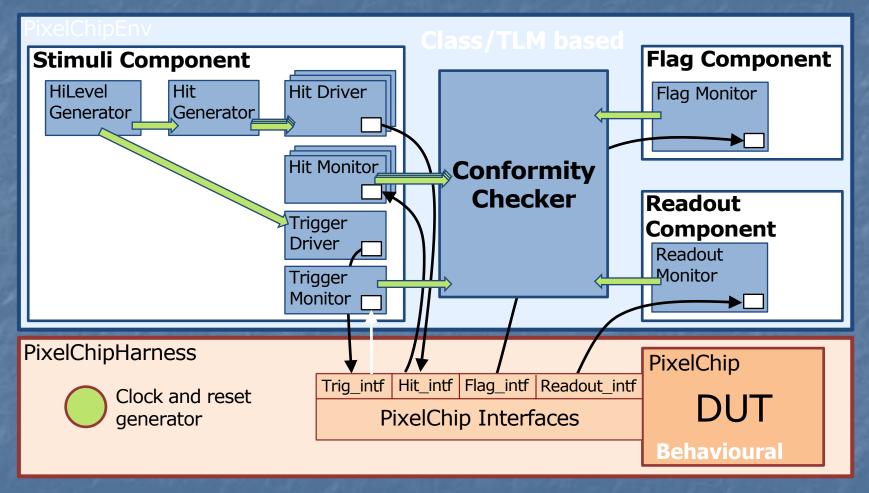

#### WG3 Simulation/verification framework: T. Hemperek, Bonn

System Verilog simulation and Verification framework Optimization of global architecture/pixel regions/pixel cells

#### WG4 I/O : To be started

Development of rad hard IO cells (and standard cells if required) Standardized interfaces: Control, Readout, etc.

#### WG5 Analog design / analog front-end: V. Re, Bergamo/Pavia

Define detailed requirements to analog front-end and digitization Evaluate different analog design approaches for very high radiation environment. Develop analog front-ends

WG6 IP blocks: ( J. Christiansen, CERN)

Definition of required building blocks: RAM, PLL, references , ADC, DAC, power conversion, LDO, , Distribute design work among institutes Implementation, test, verification, documentation

### Status and plans

#### General

- MOU in the pipeline

- Some institutes have obtained funding thanks to RD53 (justified by the fact that it is for ATLAS & CMS)

- WGs have regular meetings

- Next collaboration workshop: April 10-11 at CERN

- Define schedule for shared IC runs, Full pixel chip demonstrator: 2016

- Radiation: Urgent

- Verify that 65nm is OK, Evaluate alternatives (2014)

- Radiation test campaigns have started

- Simulation models after radiation (2015)

- Analog

- Defining requirements

- Defined alternative schemes to be evaluated: TOT, ADC, Auto-zero, Sync Async, etc.

- Design/test different implementations and choose (2015)

- IPs: ~30 IP block

- Defined who makes what.

- Define detailed specs, how to make/deliver IPs, start design (2014)

- IP library with layouts, simulation models, documentation, , , , (end 2015)

#### Simulation:

- Defining simulation tool (SV + UVM), bench mark, Framework definition

- Simulate different architectures and optimize

- SEU immunity verification

- Top: How to put such a chip together

- Global aspects: Metal stack, Mixed signal, Power dist, Global integration, Bump-bonding pattern, ,

- IO: To be started

### **RD53 Summary**

Highly focused ATLAS-CMS-LCD/CLIC RD collaboration to develop/qualify technology, tools, architecture and building blocks required to build next generation pixel chips for very high rates and radiation Synergy with other pixel projects when possible Centered on technical working groups Baseline technology: 65nm CERN frame contract/NDA/design kit . Will evaluate alternatives ("emergency" plan) 17 Institutes, 100 Collaborators Initial work program of 3 years Goal: Full pixel chip prototype 2016 Working groups have gotten a good start. Common or differentiated final chips to be defined at end of 3 year R&D period

# Backup slides

### **RD53** Outlook

#### 2014:

- Release of CERN 65nm design kit: Very soon !

- Detailed understanding of radiation effects in 65nm

- Radiation test of few alternative technologies.

- Spice models of transistors after radiation/annealing

- IP block responsibilities defined and appearance of first FE and IP designs/prototypes

- Simulation framework with realistic hit generation and auto-verification.

- Alternative architectures defined and efforts to simulate and compare these defined

- Common MPW submission 1: First versions of IP blocks and analog FEs

#### **2015:**

- Common MPW submission 2: Near final versions of IP blocks and FEs.

- Final versions of IP blocks and FEs: Tested prototypes, documentation, simulation, etc.

- IO interface of pixel chip defined in detail

- Global architecture defined and extensively simulated

- Common MPW submission 3: Final IPs and Fes, Small pixel array(s)

#### **2016:**

- **Common engineering run**: Full sized pixel array chip.

- Pixel chip tests, radiation tests, beam tests , ,

- 2017:

Separate or common ATLAS – CMS final pixel chip submissions.

### Participation matrix

| Institute     | WG1<br>Radiation | WG2<br>Top level | WG3<br>Sim./Ver | WG4<br>I/O | WG5<br>Analog | WG6<br>IPs       |

|---------------|------------------|------------------|-----------------|------------|---------------|------------------|

| Bari          | С                |                  | А               |            |               | А                |

| Bergamo-Pavia | А                |                  |                 | С          | А             | В                |

| Bonn          | С                | А                | А               | В          | В             | А                |

| CERN          | B(*)             | (*)              | А               | C(*)       | А             | B <sup>(*)</sup> |

| СРРМ          | А                | В                | С               | С          | В             | А                |

| Fermilab      | А                | В                |                 |            | А             |                  |

| LBNL          | В                | А                | В               | В          | А             | А                |

| LPNHE Paris   | А                | В                | А               |            |               | А                |

| NIKHEF        |                  | А                | А               |            |               | А                |

| New Mexico    | А                |                  |                 |            |               |                  |

| Padova        | А                |                  |                 |            |               | А                |

| Perugia       | В                |                  | А               |            |               | В                |

| Pisa          |                  | В                | А               | А          |               | А                |

| PSI           | В                | Α                |                 | С          | А             | А                |

| RAL           |                  | В                | В               |            | А             | С                |

| Torino        | С                | В                | С               | В          | А             | А                |

| UCSC          | С                | В                | С               |            |               | А                |

A: Core competency, B: High interest, C: Ability to help

(\*): General CERN support for 65nm

### SV+UVM framework

# IP blocks

| Country                                   | DE  | CFRN        | FR WddD | NL     | i ir     | av/<br>erg   | IT -  | INFN     | Pisa     | e<br>E   | US TINIT | FR HNAT | UK  | SU<br>SU      | CZ<br>(e) | Comments   |   |          |   |        |

|-------------------------------------------|-----|-------------|---------|--------|----------|--------------|-------|----------|----------|----------|----------|---------|-----|---------------|-----------|------------|---|----------|---|--------|

| Group                                     | Ä   | ۲<br>۲      | 9 8     | NIKHFF |          | Pav/<br>Berg | (Mila | Padova   |          | Torino   | Е        | LPN     | Ľ.  | Santa<br>Cruz | (Pro      |            |   |          |   |        |

| ANALOG: Coordination with analog WG       |     |             |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| Temperature sensor.                       |     |             | 0       |        |          | (P)          |       |          |          | (P)      |          |         |     |               | (P)       |            |   |          |   |        |

| Radiation sensor                          |     |             | (P)     |        |          | (P)          |       |          |          | 0?       |          |         |     |               | (P)       |            |   |          |   |        |

| HV leakage current sensor.                |     |             | 0       |        |          | (, )         |       |          |          | (P)      |          |         |     |               | (P)       |            |   |          |   |        |

| Band gap reference                        |     | 0           |         | (P)    |          | 0            |       |          |          | (F)      |          |         | (P) |               | (F)       | 3 Groups   |   |          |   |        |

| Self-biased Rail to Rail analog buffer    | (P) |             | (P)     |        |          |              |       |          |          |          |          |         | 0   |               | (P)       |            |   |          |   |        |

| MIXED                                     | (٢) |             | (P)     | (٢)    |          |              |       |          |          |          |          |         | 0   |               | (P)       |            |   |          |   |        |

| 8 – 12 bit biasing DAC                    |     | (D)         |         |        | 0        |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| 10 - 12 bit slow ADC for monitoring       |     | (P)<br>0    | 0       |        | 0        |              |       |          |          |          |          |         |     |               | (P)       | 3 Groups   |   |          |   |        |

| PLL for clock multiplication              | 0   | (P)         | Ŭ       | (P)    | Ŭ        |              |       | (P)      | (P)      | (P)      |          |         | (P) | (P)           |           |            |   |          |   |        |

| High speed serializer ( ~Gbit/s)          | 0   | (P)         |         | (P)    |          |              |       | . /      | (P)      |          |          |         | (P) |               |           | Together   |   |          |   |        |

| (Voltage controlled Oscillator)           |     |             |         | (P)    |          |              |       | 0        | (P)      | (P)      |          |         |     |               |           | Needed ?   |   |          |   |        |

| Clock recovery and jiter filter           | 0   | (P)         |         |        |          |              |       |          | (P)      |          |          |         | (P) |               |           |            |   |          |   |        |

| Programmable delay<br>DIGITAL             | 0   | (P)         |         |        |          |              |       |          | (P)      |          |          |         | (P) |               |           |            |   |          |   |        |

| SRAM for pixel region                     | (P) | (P)         |         |        |          |              | 0     |          |          |          |          |         |     | (P)           |           |            |   |          |   |        |

| SRAM/FIFO for EOC.                        |     | (P)         |         |        |          |              | (P)   |          | (P)      |          |          |         |     | 0             |           |            |   |          |   |        |

| EPROM/EFUSE                               | (P) | Ó           | (P)     |        |          |              | ( )   |          |          |          |          |         |     |               |           |            |   |          |   |        |

| DICE storage cell / config reg            | (P) |             | 0       |        |          |              | (P)   |          | (P)      |          |          |         |     | (P)           |           | Or TMR ?   |   |          |   |        |

| LP Clock driver/receiver                  | (P) | ( )         |         |        |          | 0            |       |          |          |          |          |         | (P) |               |           |            |   |          |   |        |

| (Dedicated rad hard digital library)      | (P) | (P)         | (P)     |        |          |              |       |          | 0        |          |          | (P)     | (P) |               |           | If needed  |   |          |   |        |

| (compact mini digital library for pixels) | (P) | (P)         | (P)     |        |          |              |       |          | 0        |          |          | (P)     | (P) |               |           | If needed  |   |          |   |        |

| IO: Coordination with IO WG               |     |             |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| Basic IO cells for radiation              | (P) | 0           |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| Low speed SLVS driver (<100MHz)           | (P) | (P)         |         |        |          | 0            |       |          | (P)      | (P)      |          |         |     |               | (P)       |            |   |          |   |        |

| High speed SLVS driver (~1Gbits/s)        | (P) | (P)         |         |        |          | 0            |       |          | (P)      | (P)      |          |         |     |               | (P)       | Together   |   |          |   |        |

| SLVS receiver                             | (P) | (P)         |         |        |          | 0            |       |          | (P)      |          |          |         |     |               | (P)       |            |   |          |   |        |

| 1Gbits/s drv/rec cable equalizer          |     |             |         |        |          |              |       |          |          |          |          |         |     |               | ( )       | New        |   |          |   |        |

| C4 and wire bond pads                     | (P) | 0           |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| (IO pad for TSV)                          | 0   |             | (P)     |        |          |              |       |          |          |          |          | (P)     |     | (P)           |           |            |   |          |   |        |

| Analog Rail to Rail output buffer         | 0   |             | (P)     |        |          |              |       |          |          |          |          | (P)     |     | (P)           |           |            |   |          |   |        |

| Analog input pad<br>POWER                 | 0   |             |         |        |          |              |       |          |          |          |          | (P)     |     |               |           |            |   |          |   |        |

| LDO(s)                                    |     | (P)         | (P)     | 0      |          |              |       |          | (P)      | (P)      |          |         | (P) |               |           |            |   |          |   |        |

| Switched capacitor DC/DC                  |     | (P)         | (•)     | 0      |          |              |       |          | (,)      |          | 0        |         | (•) |               | (D)       |            |   |          |   |        |

| Shunt regulator for serial powering       |     | (P)         |         | 0      |          |              |       |          |          |          | 0        |         |     |               | (P)       |            |   |          |   |        |

| Power-on reset                            |     |             |         | 0      |          |              |       |          |          |          |          |         |     |               |           | New        |   |          |   |        |

| Power pads with appropriate ESD           | (P) | 0           |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| SOFT IP: Coordination with IO WG          |     | (5)         |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   |        |

| Control and command interface             |     | (P)         |         |        | (P)      |              |       |          | 0        |          |          | (P)     |     |               |           |            |   |          |   |        |

| Readout interface (E-link ?)<br>Summary   |     | (P)         |         |        | (P)      |              |       |          | 0        |          |          | (P)     |     |               |           |            |   |          |   |        |

| ATLAS/CMS/Neutral                         | •   | N           |         | •      | C        | C            | C     | <u> </u> | C        | <u> </u> | •        | •       | N   | ^             |           |            | ~ | AC       | N |        |

| O's                                       | A   | N<br>7 (    |         | A      | C<br>2 : | C<br>2 5     | C     | C<br>1 · | C<br>L ₄ | C<br>4 1 | A<br>1   | A       | N   |               | A         | ATLAS<br>1 |   | ሳS<br>14 |   | eutral |

| (P)'s                                     |     | / (<br>4 10 |         |        |          | 2 2          |       | 2        | L 10     |          |          | 7       | _   | -             |           |            |   | 24       |   | 2      |

|                                           |     |             |         |        |          |              |       |          |          |          |          |         |     |               |           |            |   |          |   | 18     |

7 25 **18**

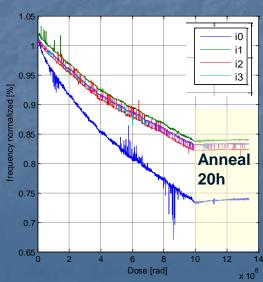

# PMOS drive current (Digital)

M. Menouni, CPPM

Acceptable for digital circuits ? (Yes but ---) Analog performance ?

Ring oscillator frequency with different transistor sizes and cold (-25 °C)

S, Bonacini, CERN

| #      | Wp  | Wn  | М |

|--------|-----|-----|---|

| Ring 0 | 260 | 195 | 1 |

| Ring 1 | 520 | 390 | 1 |

| Ring 2 | 520 | 390 | 2 |

| Ring 3 | 520 | 390 | 3 |

### Various interests in analog blocks

INFN (BG/PV, Torino, Padova): continuous-time front-end (PA and shaper), sybchronous comparator, ToT-based ADC, signal injection and calibration

- Bonn (Prague): continuous and switched amplifier, static and dynamic comparator, SAR ADC

- CERN: CLIC-PIX (ToT-based analog channel)

- CPPM: high-resolution ADC (8 bits), adaptation of MAPS front-end

- FNAL: Synchronous front-end, FLASH ADC (130 nm)

- LBNL: ToT-based channel (6-7 bits resolution)

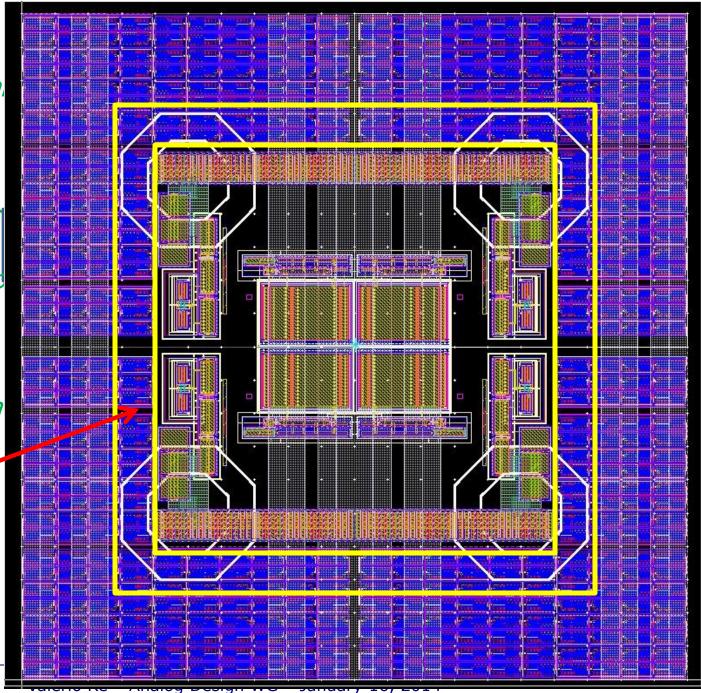

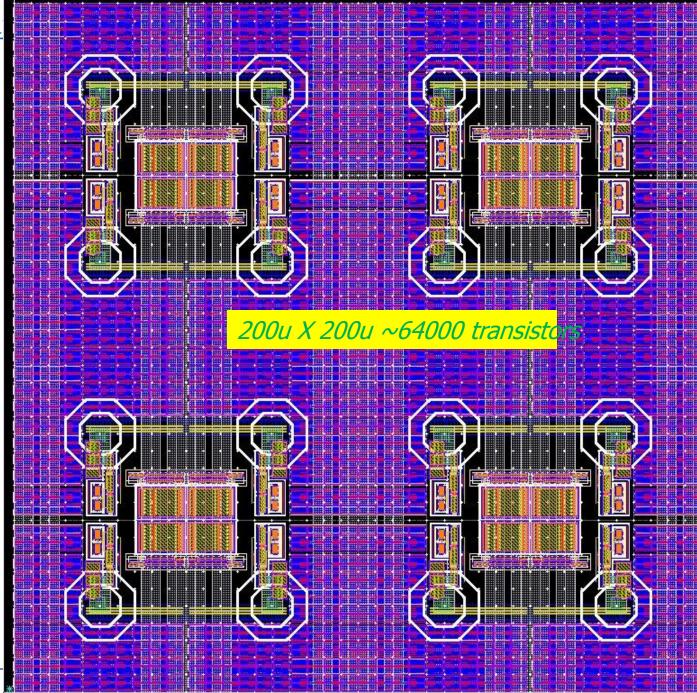

#### <u>A 2X2 Unit</u>

Is this a digital units

FEI4 Bump pitch

~16000 Transistors

~32000 transistor p

FEI4 equivalentregion (analog hole included)

"Pixels" communica horizontally and

vertically Quiet logic Area

Work in progress

A. Mekkaoui, LBNL