## **ALICE upgrade overview**

A. Kluge, March 18, 2014

For the ALICE collaboration

#### **Outline**

Upgrade specifications

Upgrade overview

Upgrade architecture

Slides taken from:

H. Äppelshauser, J-P. Cachemiche, A. Kluge, G. Martinez,

P. Moreira, L. Musa, W. Riegler, W. Trzaska

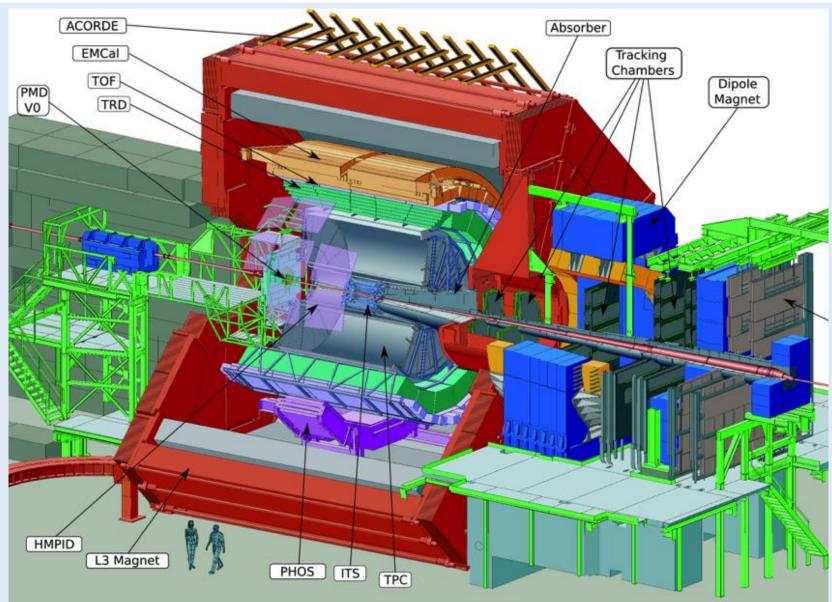

## ALICE & run 1/2

## **Upgrade strategy**

- High precision measurements of rare probes at low p<sub>t</sub>

- Cannot be selected with a trigger

- Require a large sample of events recorded

- Target

- Pb-Pb  $\rightarrow \geq 10 \text{ nb}^{-1} \rightarrow 8 \times 10^{10} \text{ events}$

- pp (@5.5 TeV)  $\rightarrow$  ≥ 6 pb<sup>-1</sup>  $\rightarrow$  1.4 x 10<sup>11</sup> events

- Gain factor 100 in statistics

## **Upgrade strategy**

Upgrade ALICE read-out and online systems

**Upgrade in LS2 2018/19**

- Read-out all Pb-Pb interactions at

- 50 kHz (L =  $6 \times 10^{27}$  cm<sup>-1</sup>s<sup>-1</sup>) with min bias trigger

- Online data reduction ← no filtering

- Reconstruction of clusters and tracks

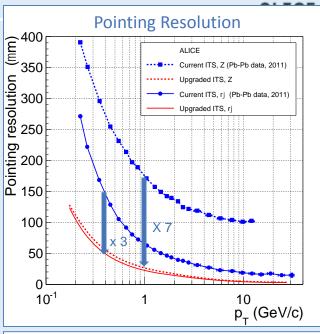

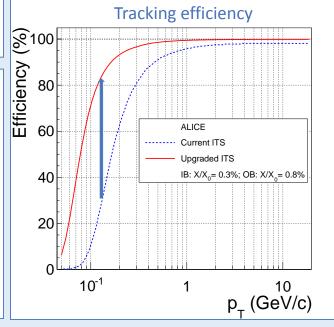

- Improve vertexing and tracking at low p<sub>t</sub>

- New inner tracking system

#### LoI & TDR

## Inner tracking system

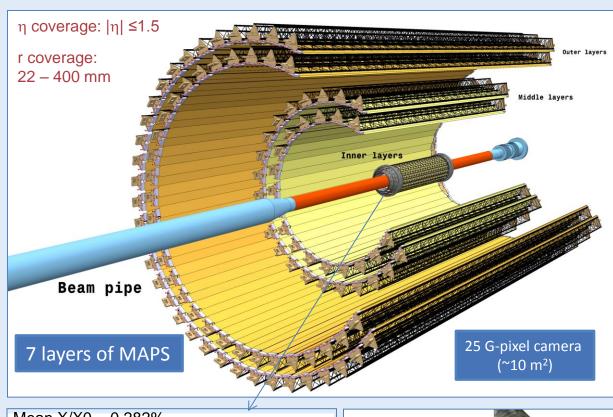

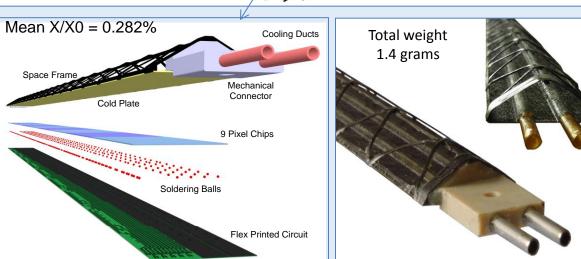

#### **New ITS Layout**

#### **PIXEL Chip - technology**

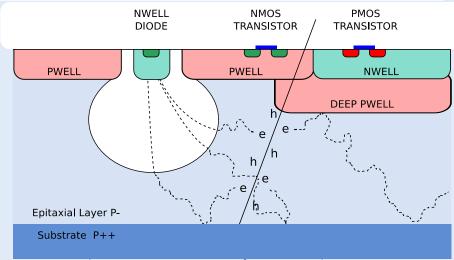

## Monolithic PIXEL chip using Tower/Jazz 0.18 µm technology

- feature size 180 nm

- gate oxide < 4nm</li>

- metal layers 6

- high resistivity epi-layer

- thickness 18-40 μm

- resistivity 1-6 k  $\Omega \times cm$

- "special" deep p-well layer to shield PMOS transistors (allows in-pixel truly CMOS circuitry)

- Several prototype architectures

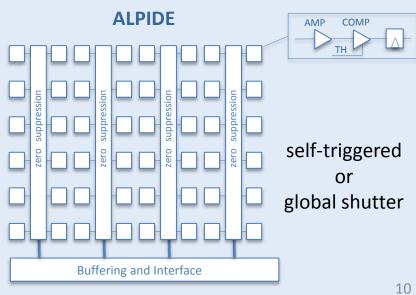

- ALPIDE self-triggered or global shutter

- MISTRAL/ASTRAL rolling shutter

Schematic cross-section of CMOS pixel sensor (ALICE ITS Upgrade TDR)

Power density < 50 mW/cm<sup>2</sup>

#### New ITS – pixel prototype chips & experimental results

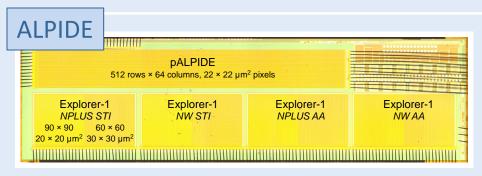

pALPIDE: sizeable prototype of final chip (digital output)

Explorer: prototype chip with analogue output

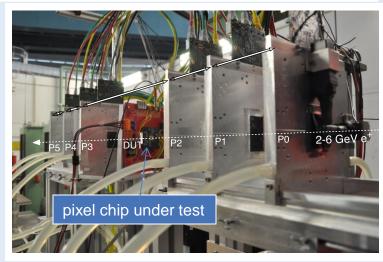

Measurements at DESY test beam (4.4 Gev electron beam) – Sep 2013

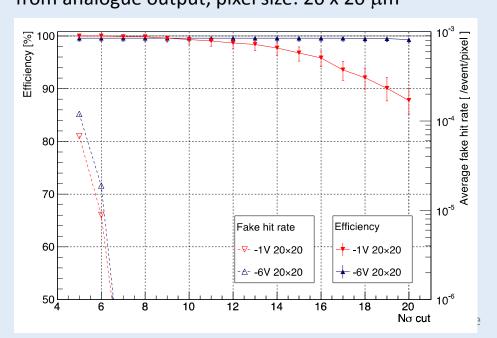

**Explorer chip**, performance of pixel chip from analogue output, pixel size: 20 x 20 μm<sup>2</sup>

pALPIDE chip, performance of pixel chip from digital output, pixel size: 22 x 22  $\mu$ m<sup>2</sup>

Threshold / Noise: 20

Detection efficiency: 99.7%

Fake hit rate < 10<sup>-8</sup>

Spatial resolution ~ 5μm

#### Readout – general scheme and data throughput

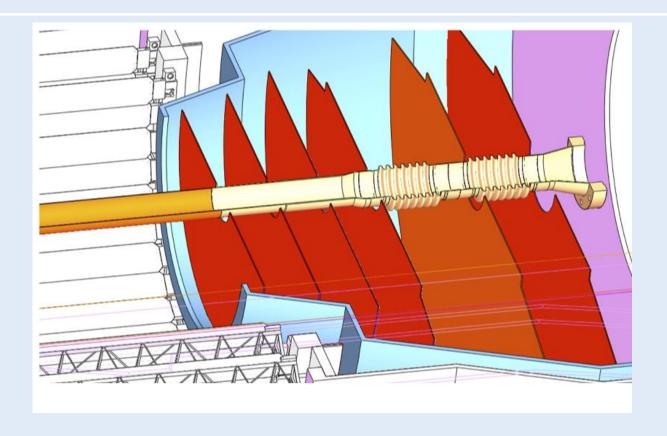

## **TPC**

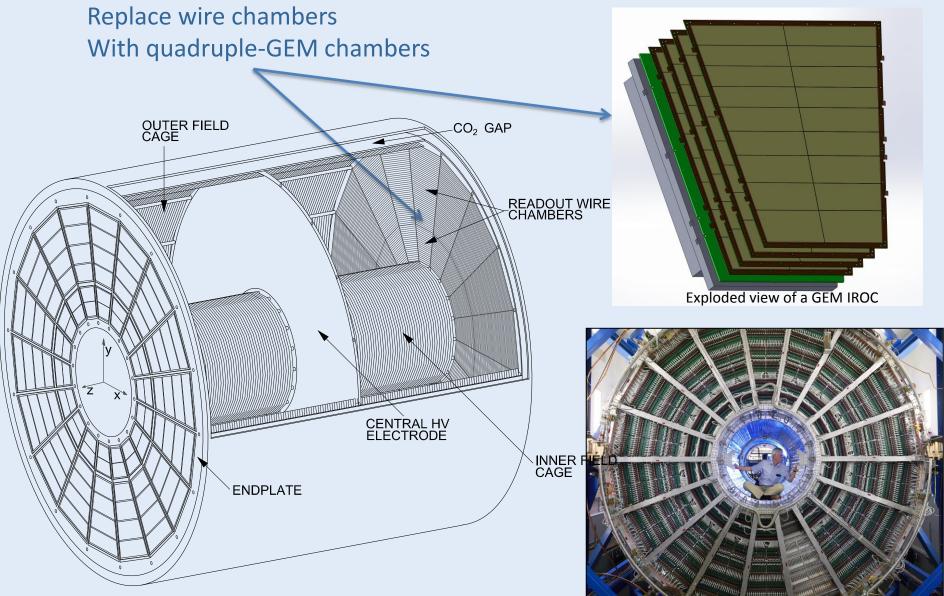

## **TPC** upgrade

## **TPC-present limitation & upgrade**

- drift time (electrons) = 100 μs

- after gating grid closed until 280 μs

- to prevent back drifting ions into drift region

- and space charge distortion

- → total time 280 µs → 3.5 kHz read-out rate

- avg. interaction rate 50 kHz → 20 µs

- drift time = 100 µs →

- pile-up → continuous trigger-less read-out

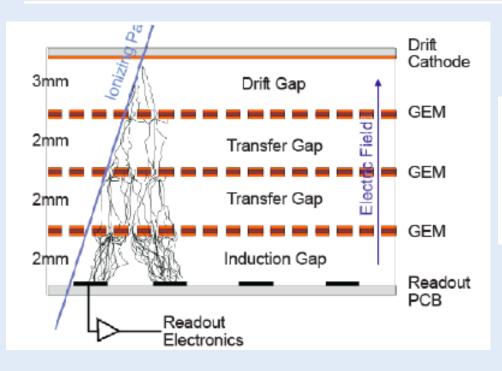

#### multiple GEM principle

- Fast electron signal (polarity!)

- no "ion tail"

- No "coupling to other electrodes"

- → Gas gain about a factor 3 lower than in MWPC

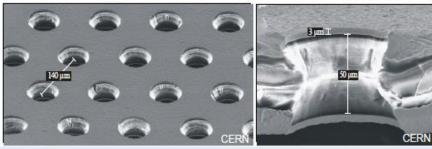

GEMs are made of a copper-kapton-copper sandwich, with holes etched into it

Electron microscope photograph of a GEM foil

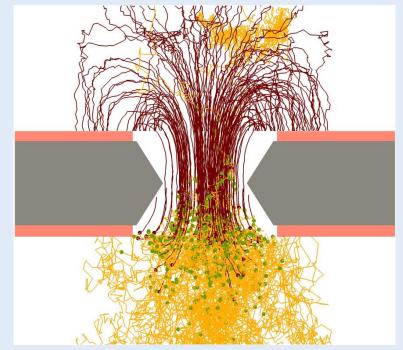

## 4 GEM simulation

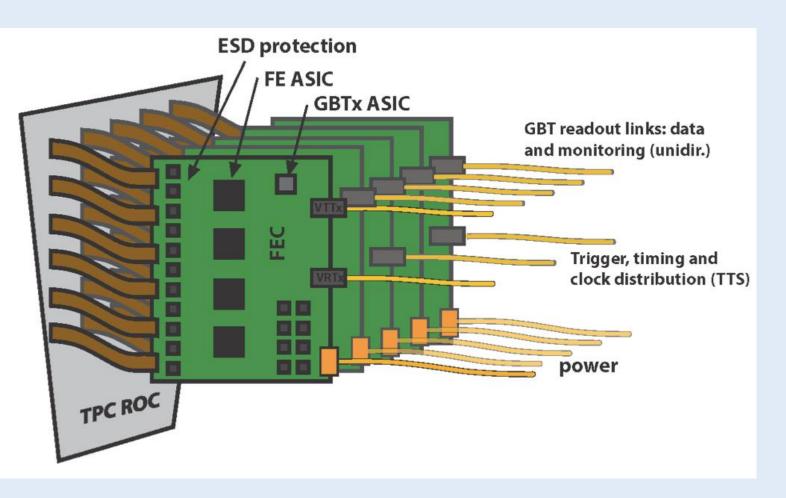

#### **TPC front-end card**

- ~ 500.000 channels @ 50 kHz read-out rate

- 3400 front-end cards & ~ 17.000 SAMPA ASICs

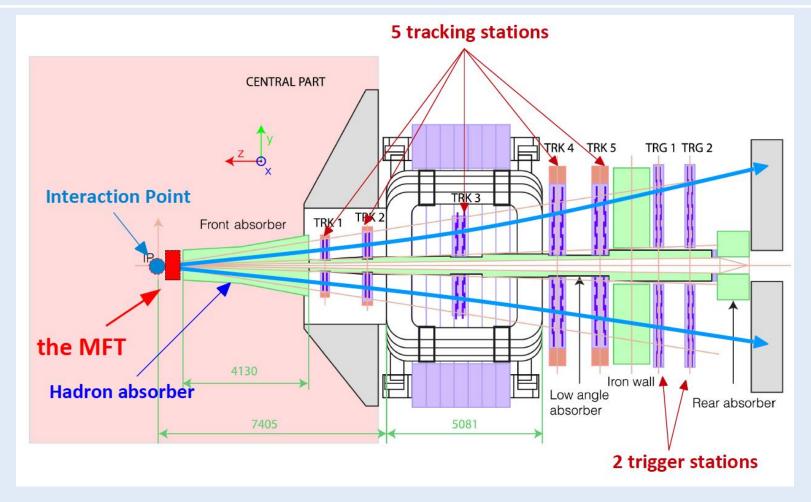

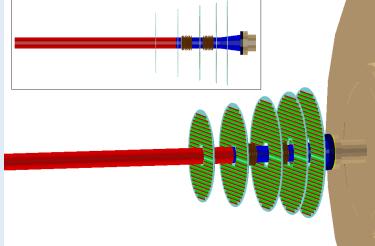

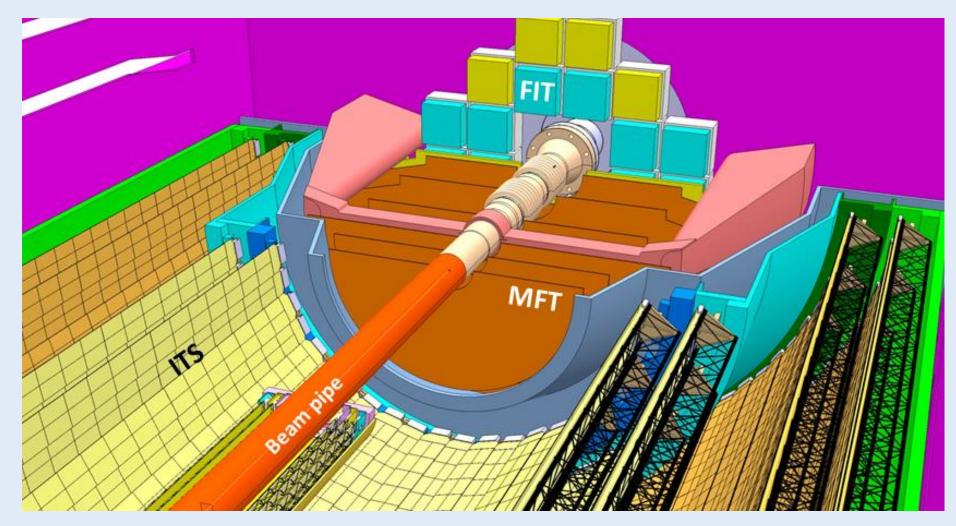

#### **Muon Forward Tracker - MFT**

## MFT and Muon-Spectrometer

Silicon pixel tracker in acceptance of Muon Spectrometer

between Interaction Point and Hadron Absorber

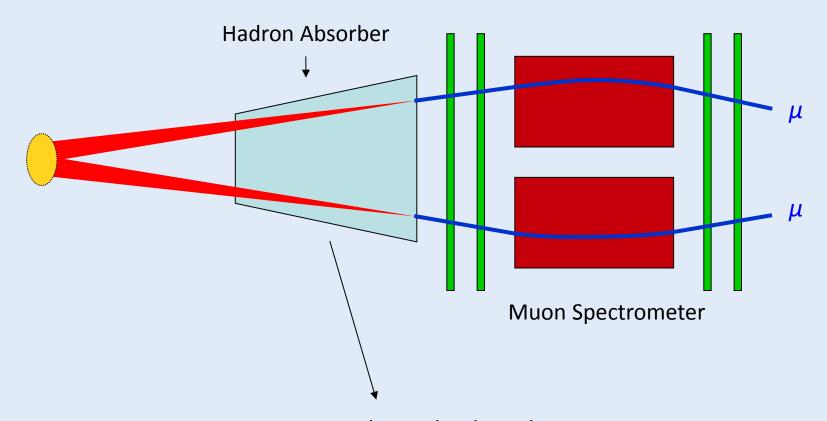

## MFT concept

Extrapolating back to the vertex region degrades the information on the kinematics

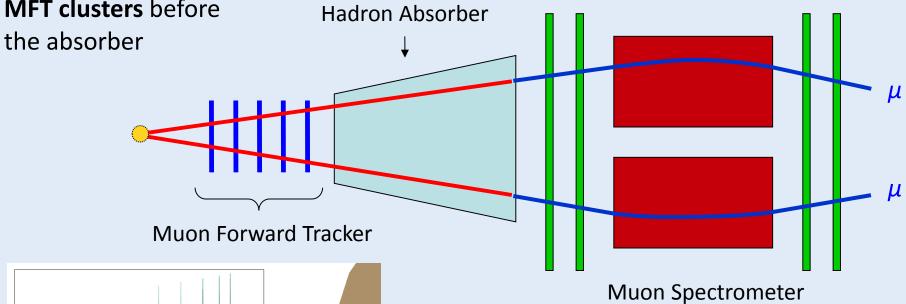

#### MFT concept

24

Muon tracks are extrapolated and "matched" to the MFT clusters before

**High pointing accuracy** gained by the muon tracks after matching with the MFT clusters

Maon Speetrometer

A. Kluge

## **MFT layout**

- Based on MAPS: common development with ITS

- Read-out based on GBT links

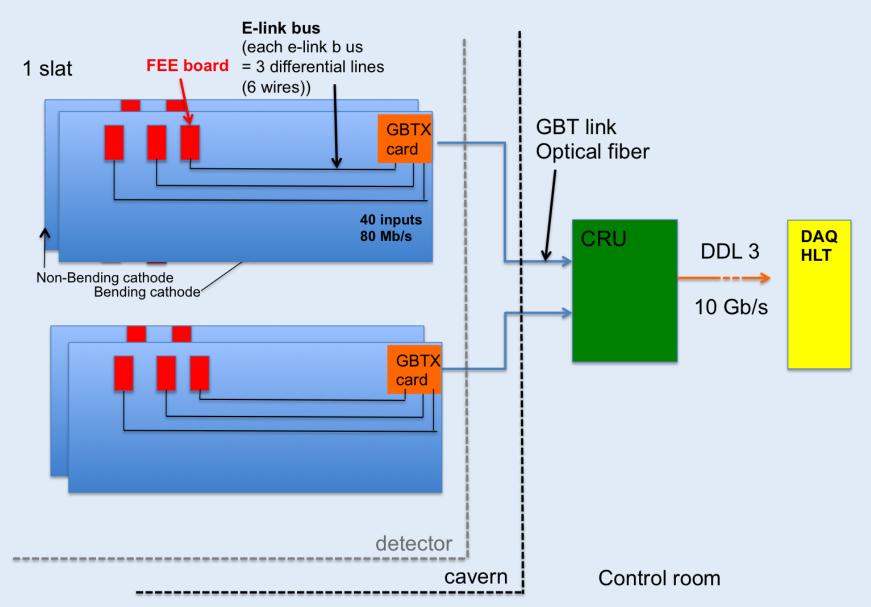

#### **Muon chambers - MCH**

#### Muon chamber

- ~1.000.000 MWPC

- upgrade to continuous read-out @ 100 kHz hit rate

- Replacement of the front-end by ~ 33.000

SAMPA ASIC

- Replacement of active patch panels (first level of data concentration)

- based on GBTs or electrical e-links

- Replacement of data concentrator by CRUs

#### muon chamber

## Fast interaction trigger

## **Fast interaction trigger - FIT**

## **Fast interaction trigger - FIT**

#### Photonis PLANACON® XP85012 or XP85112

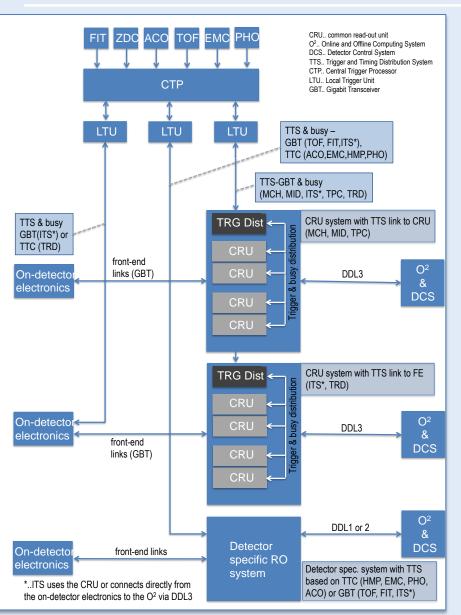

# Read-out & Trigger Upgrade architecture

### **Specifications**

- Interaction rate Pb-Pb:

- from 8 kHz  $\rightarrow$  50 kHz

- Trigger rate Pb-Pb:

- from  $\sim 3.5 \text{ kHz} \rightarrow 50 \text{ kHz}$

- All interactions are read AND recorded

- Interaction and trigger rate pp:

- $\rightarrow$  200 kHz

- Data rate driven by Pb-Pb

- TPC is read continuous & trigger less

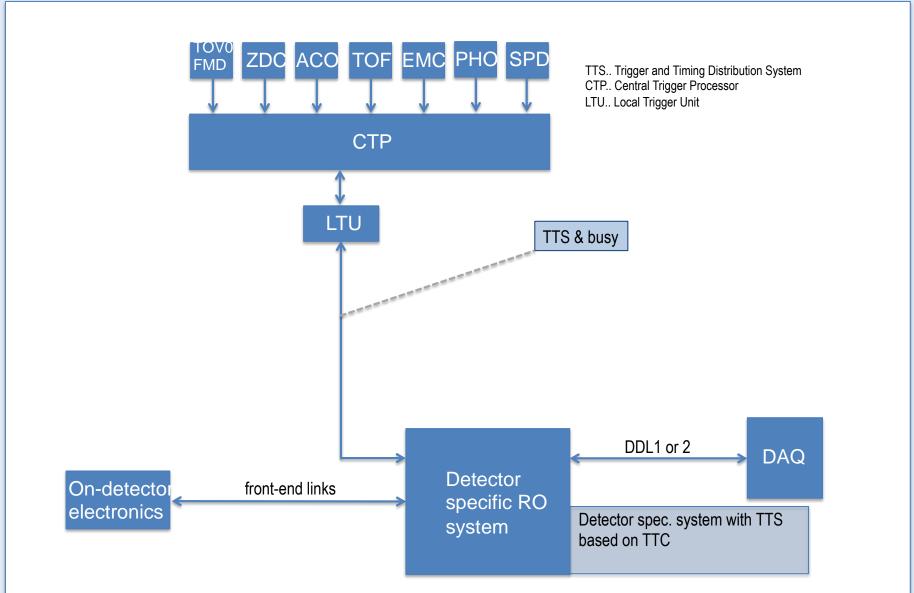

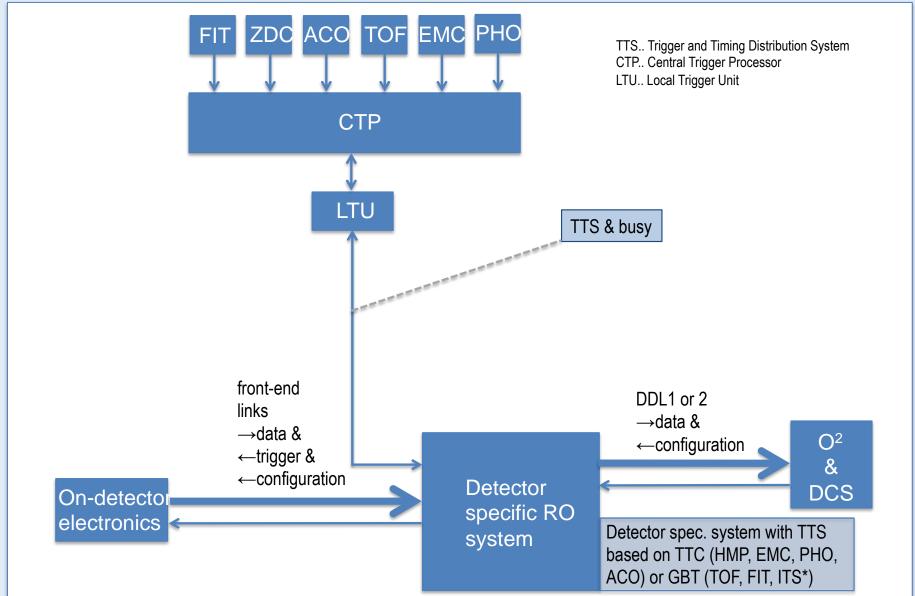

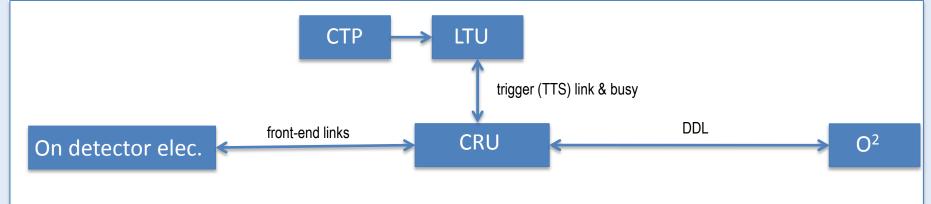

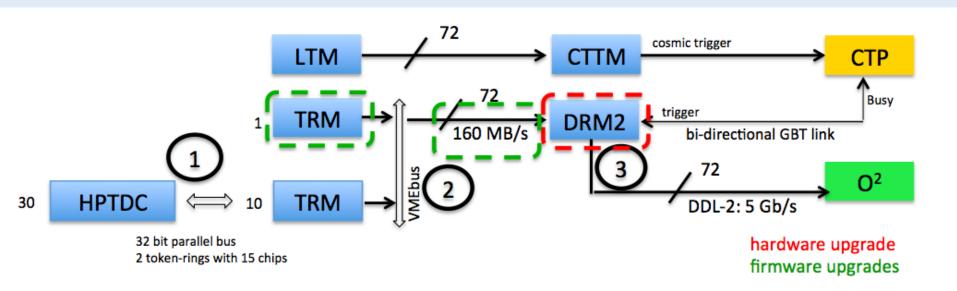

#### Run1 and Run2 architecture

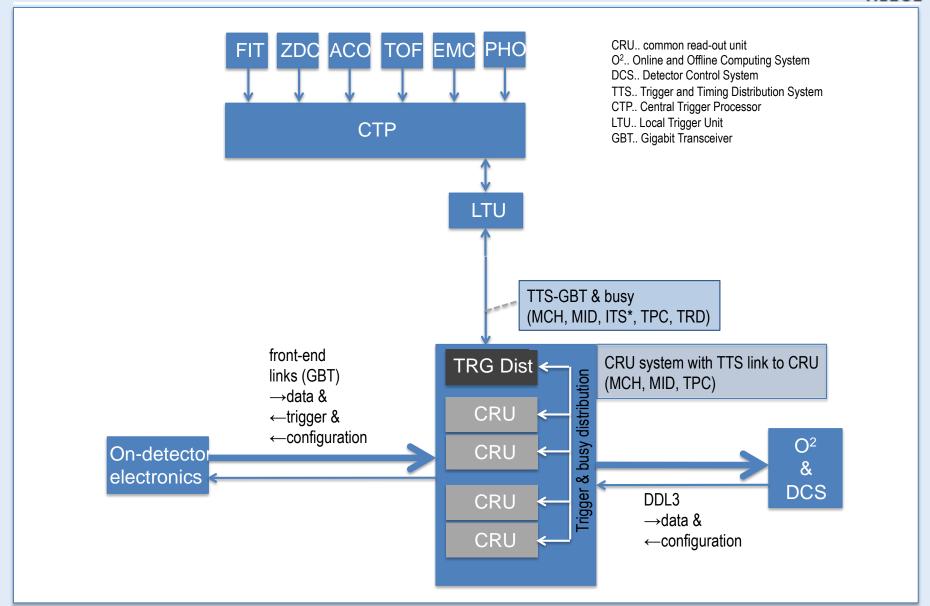

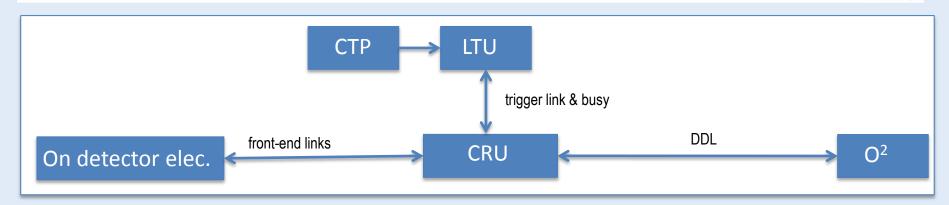

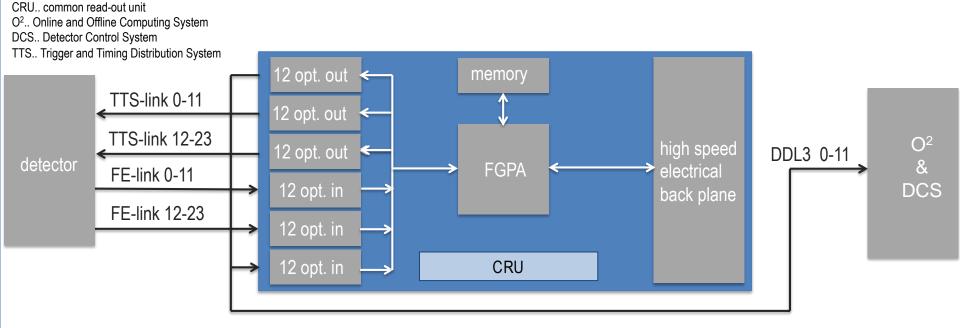

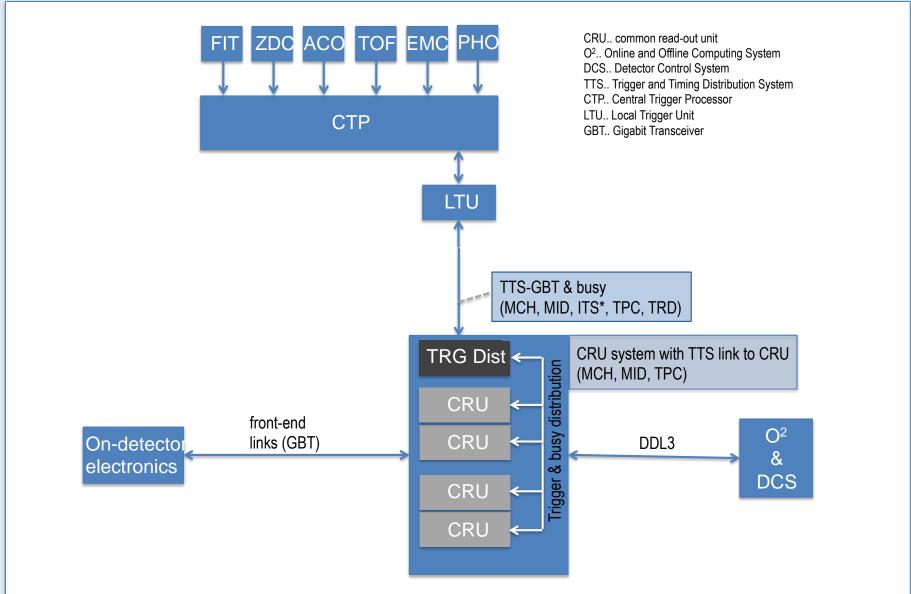

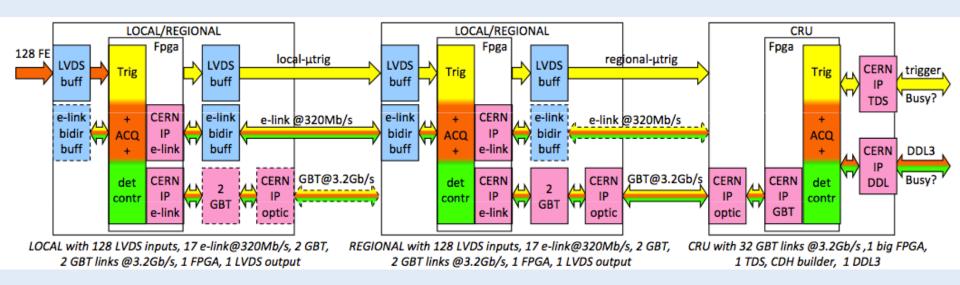

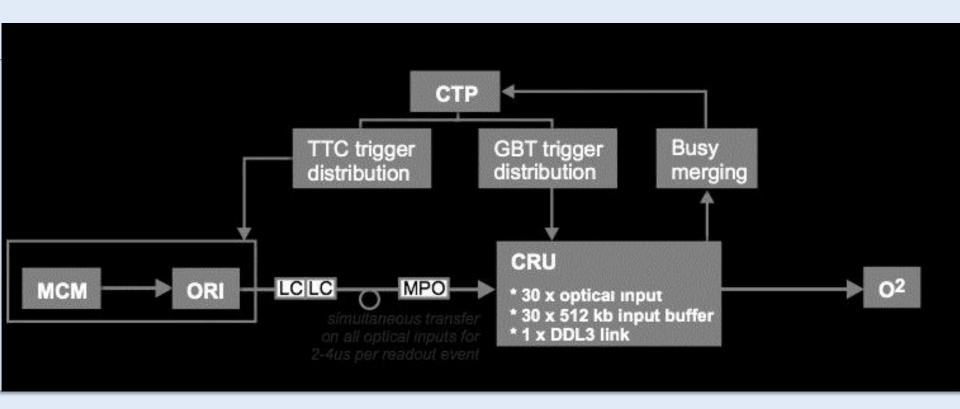

#### Common read-out unit - CRU & long trigger latency

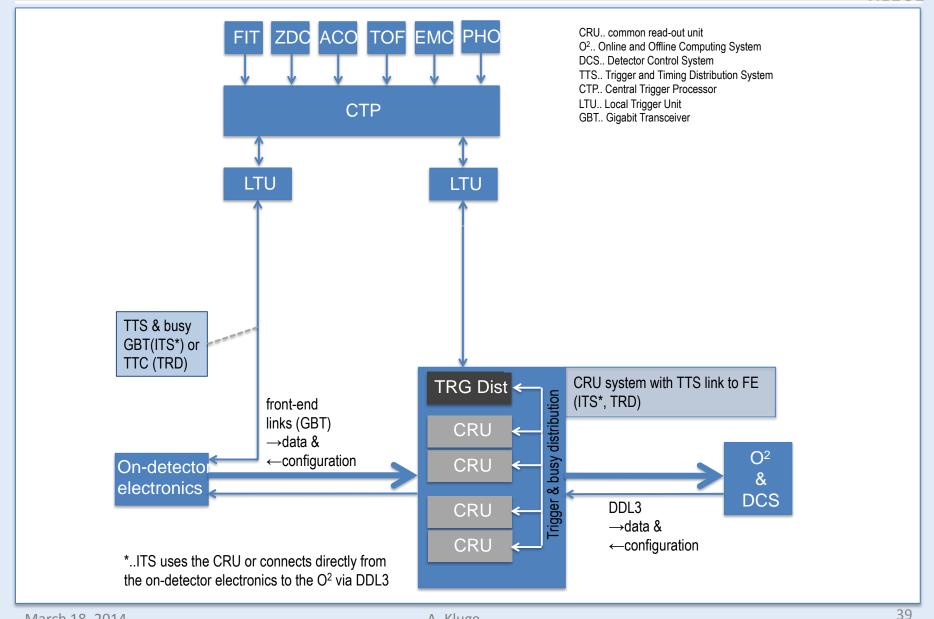

#### Common read-out unit - CRU & & short trigger latency

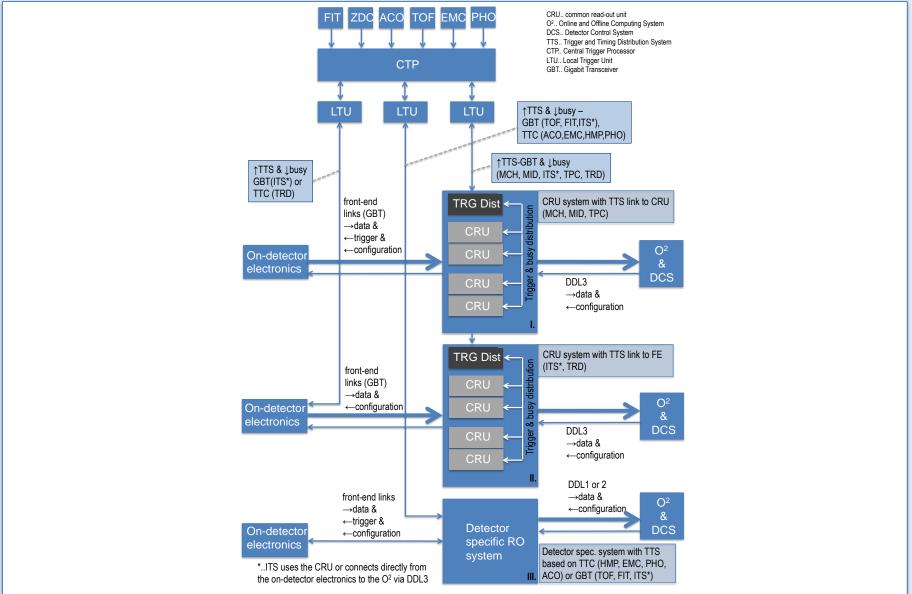

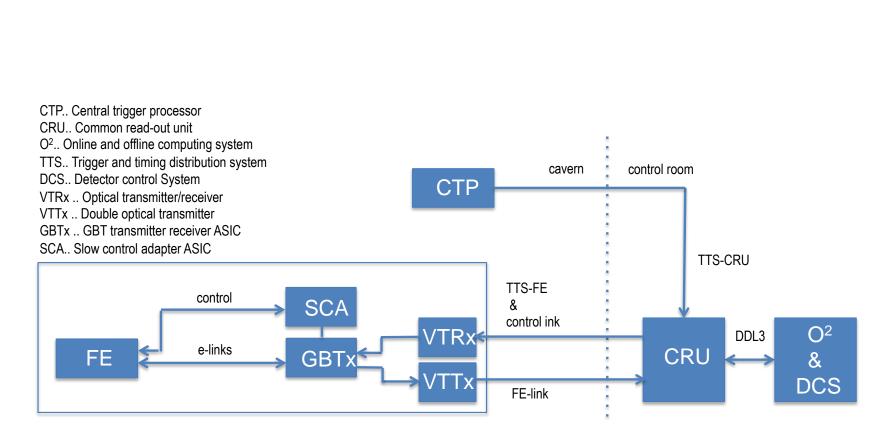

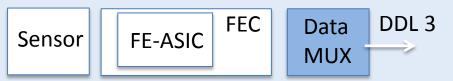

#### Upgrade architecture: det. spec. readout

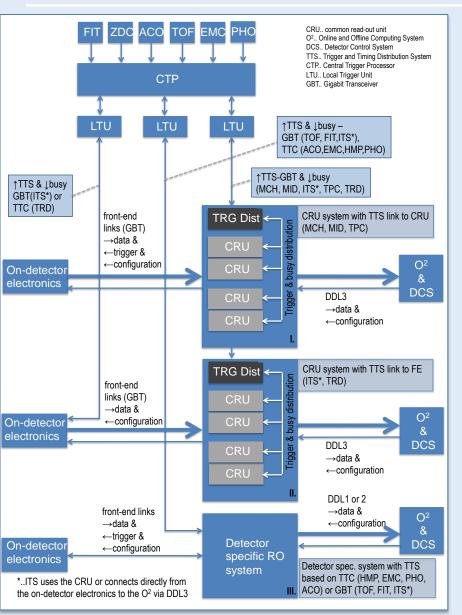

#### Upgrade architecture: full read-out system

#### Upgrade architecture: system components

- DDL

- common

- Off-detector read-out

- common readout unit or custom

- Front-end links

- versatile link (GBT) or custom

- CTP & LTU & TTS

- fast serial trigger link (FTL)& TTC

- On-detector electronics

- SAMPA & custom

# **Common components**

# Common Readout Unit – CRU & Detector Data Link - DDL

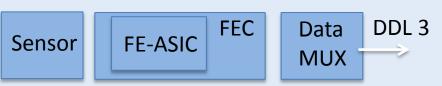

#### Read-out architecture

- Standard interface to DAQ/DCS

- Detector Data Links DDL 1, 2 already developed

- 2.125 and 4.25/5.3125 Gb/s

- DDL3 based on commercial standard

- 10 Gb/s GbE or PCle over cable or PCle plug-in cards

• Standard interface to Trigger

CTP LTU

trigger link

On detector elec.

CRU

DDL

O<sup>2</sup>

MA

O<sup>2</sup>

MA

O<sup>3</sup>

O<sup>4</sup>

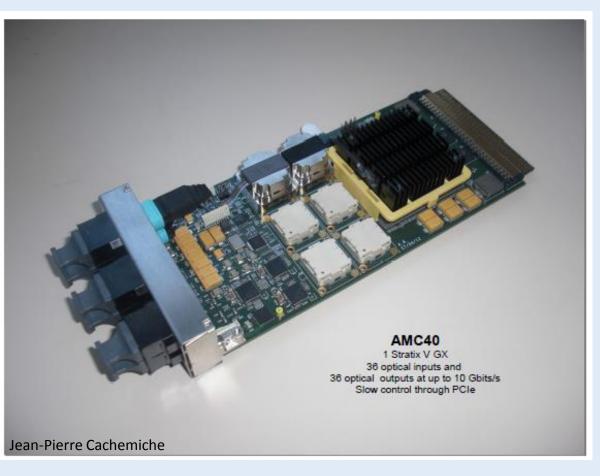

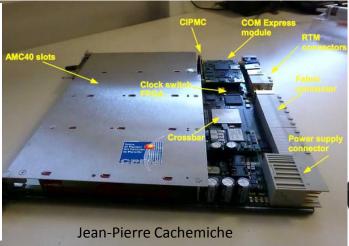

#### AMC40

#### AMC40 (LHCb)

- 4 x AMC40 →

- 1 x motherboard → 14 motherboards →

1 ATCA crate

- Trigger and timing distribution is via back plane

### **Common components**

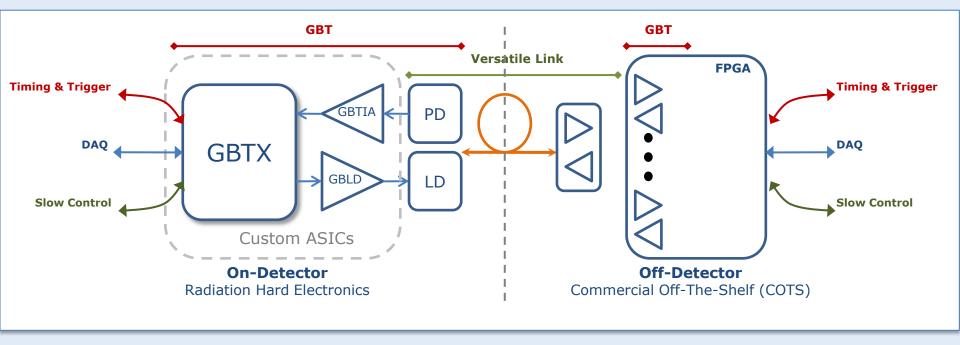

# Front-end (FE) links & Trigger and Timing Distribution System (TTS) Links

# **Common components**

# Front-end (FE) links &

# Trigger and Timing Distribution System (TTS) Links

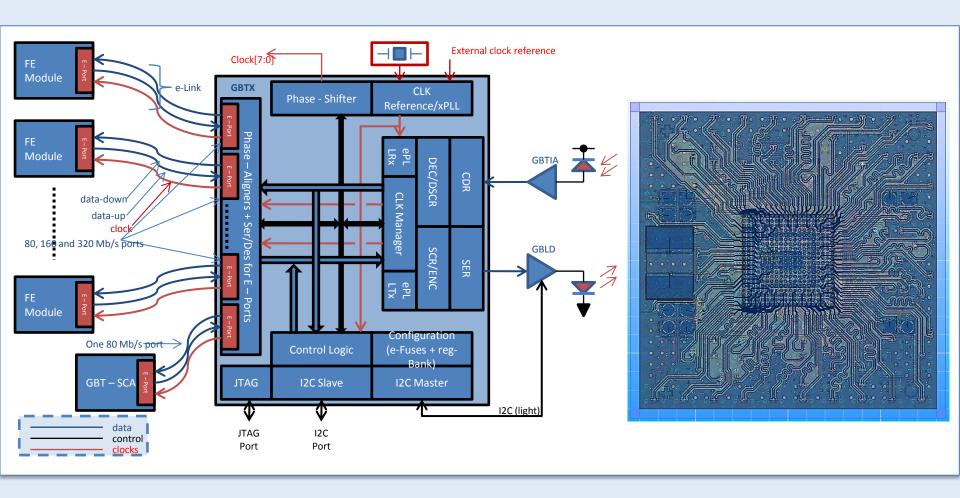

#### **GBT & Versatile link**

#### **GBTx**

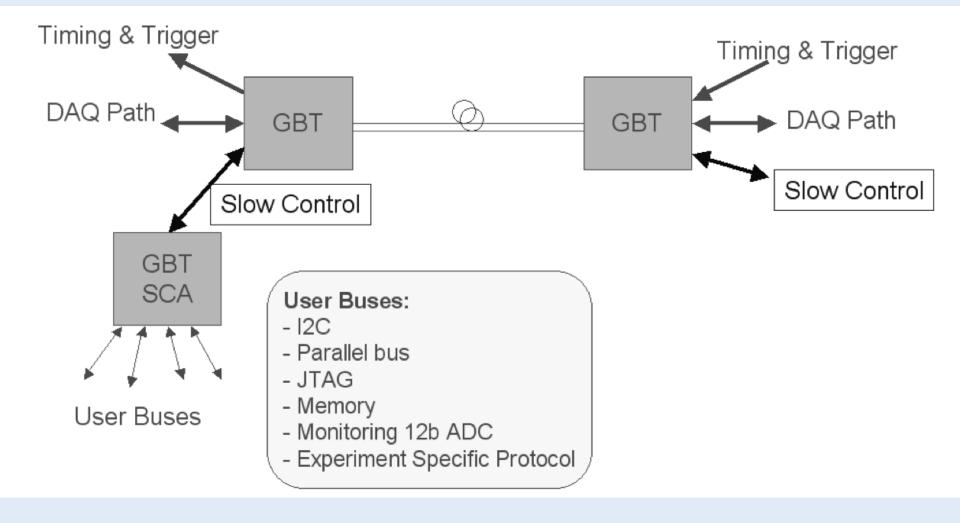

# **GBT-SCA:** slow control adapter

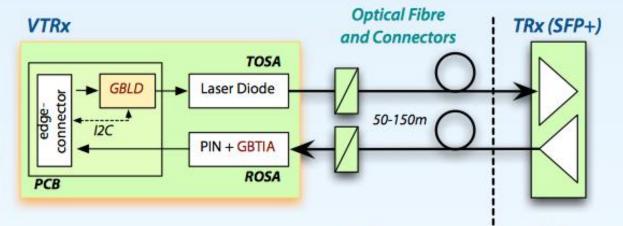

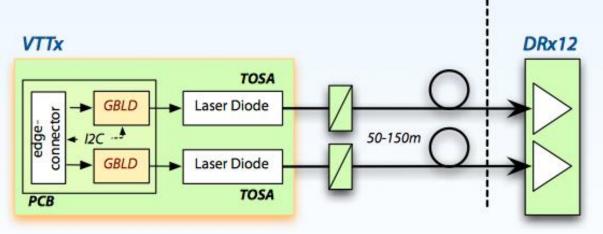

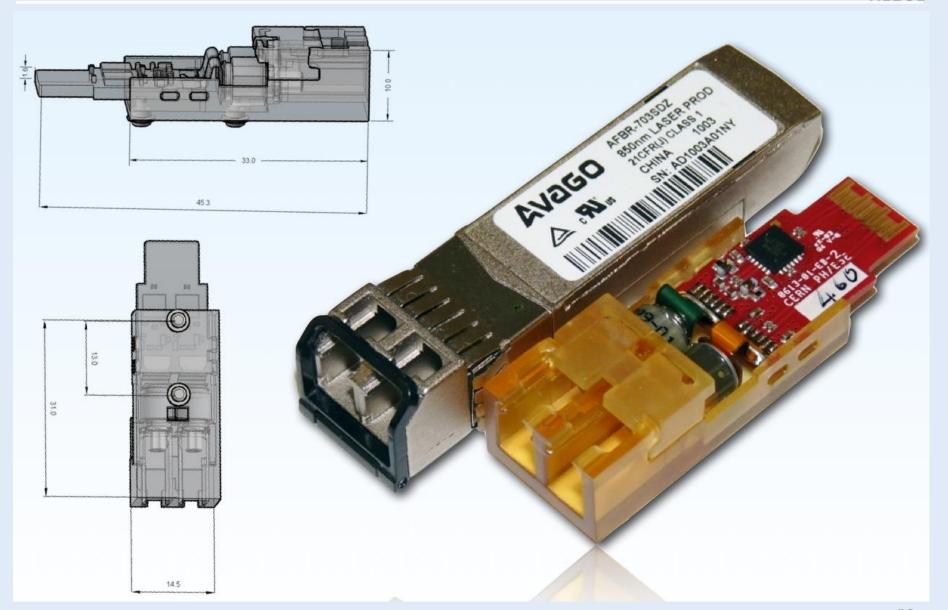

# Versatile link components: VTTx & VT

Singlemode EEL/InGaAs Multimode VCSEL/GaAs

On-Detector

Radiation zone

Off-Detector

Radiation-free zone

Multimode VCSEL

# Versatile link components: VTTx & VTRx

#### **CRU & GBT**

# Links

| Detector             | DDL1                  | $\mathrm{DDL2}$  | DDL3              | CRU-FE-links        | TTS-FE links |

|----------------------|-----------------------|------------------|-------------------|---------------------|--------------|

|                      | $2.125~\mathrm{Gb/s}$ | 4.25-5.3125 Gb/s | $10\mathrm{Gb/s}$ | $3.2~\mathrm{Gb/s}$ | 3.2 Gb/s     |

| TPC                  |                       |                  | 1200              | 6336                | 1764         |

| MCH                  |                       |                  | 250               | 500                 | 500          |

| ITS                  |                       |                  | *60               | *184                | 0            |

| MID                  |                       |                  | 1                 | 16                  | 16           |

| ZDC                  |                       |                  | 1                 | 1                   |              |

| TOF                  |                       | 72               |                   |                     |              |

| FIT                  |                       | 2                |                   |                     |              |

| ACO                  | 1                     |                  |                   |                     |              |

| $\operatorname{TRD}$ |                       |                  | 36                | 1044                | 0            |

| $\mathbf{EMC}$       |                       | 20               |                   |                     |              |

| PHO                  |                       | 16               |                   |                     |              |

| $_{\mathrm{HMP}}$    | 14                    |                  |                   |                     |              |

| Total                | 15                    | 110              | 1555              | 8081                | 2244         |

# **Common components**

# Central Trigger Processor (CTP) & Local Trigger Processor (LTU)

#### CTP & LTU

CTP & LTU: based on high performance FPGA processor Logic combinations fully programmable

# System description: Trigger signals

| Level           | Trigger           | Trigger     | Trigger           | contributing            |

|-----------------|-------------------|-------------|-------------------|-------------------------|

|                 | Input             | output      | decision          | detectors               |

|                 | to CTP            | at CTP      | at detector *     |                         |

|                 | [ns]              | [ns]        | [ns]              |                         |

| $\overline{LM}$ | 425               | 525         | 775               | FIT                     |

| L0              | 1200              | 1300        | 1500              | ACO, EMC, PHO, TOF, ZDC |

| L1              | <sup>#</sup> 6100 | $^{\#}6200$ | <sup>#</sup> 6400 | EMC, ZDC                |

- LM .. pretrigger wake up signal for TRD: by FIT only

- L0 .. main trigger signal: by FIT & additional trigger inputs

L1 .. optional EMC-jet and ZDC contribution: long latency

# **Common components**

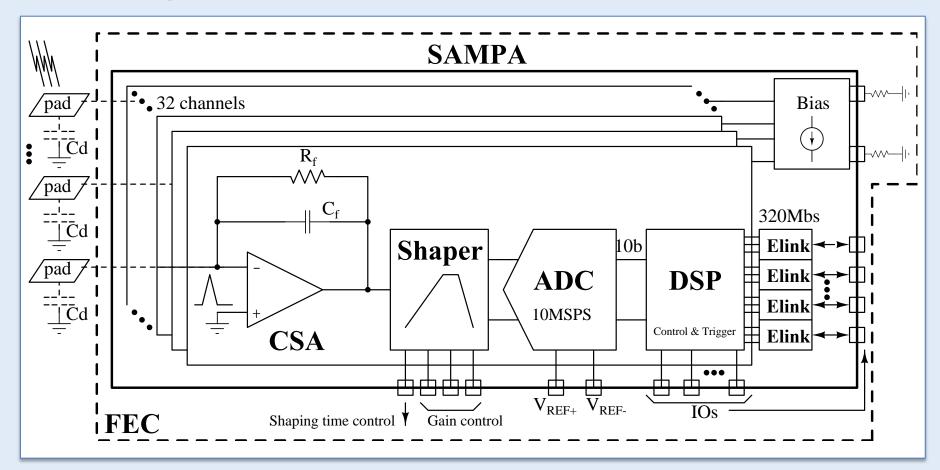

### Common TPC/MCH readout ASIC

#### **SAMPA**

- common read-out ASIC

- TPC & muon chambers

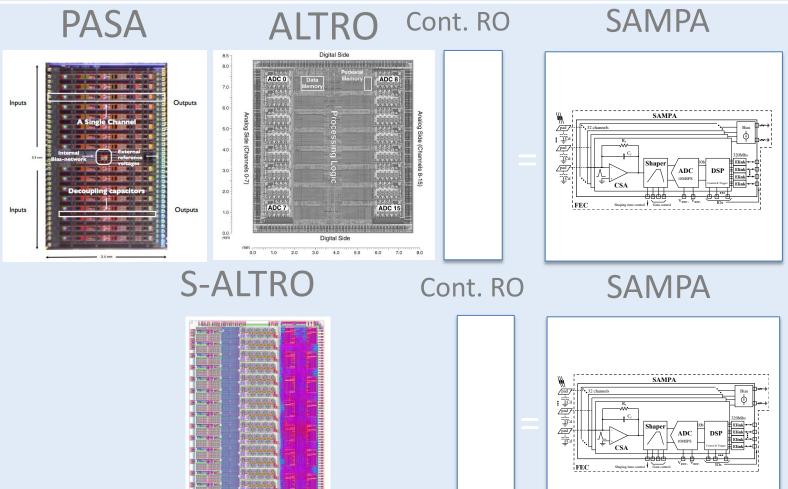

#### **SAMPA**

- SAMPA is evolution from PASA / ALTRO & S-ALTRO

- Analog specifications are almost identical

#### **SAMPA**

- TPC & muon chambers (MCH)

- 32 channel amplifier-shaper-ADC-DSP

- triggerless/continuous & triggered readout

- < 600 e @ 25 pF (TPC), < 950 e @ 40 p (MCH)</li>

- bi-polarity input

- 10 bit ADC 10/20 Msamples/s

- on ASIC base-line correction and zero suppression

- 4 x 320 Mbit/s serial outputs

- 130 nm TSMC CMOS process

# **Detector Summary**

# Sub-detector parameter overview

| Det         | triggered by                    | Pb-Pb RO   | TTS                  | CRU used     |

|-------------|---------------------------------|------------|----------------------|--------------|

| Det         |                                 |            |                      | Offo used    |

|             | () = optional                   | rate [kHz] | FTL/TTC              |              |

| TPC         | (L0  or  L1)                    | 50         | $\mathrm{FTL}$       | у            |

| MCH         | (L0  or  L1)                    | 100        | $\mathrm{FTL}$       | у            |

| ITS         | L0                              | 100        | $\operatorname{FTL}$ | *y           |

| MID         | L0  or  L1                      | >100       | ${\rm FTL}$          | у            |

| ZDC         | L0                              | >100       | $\mathrm{FTL}$       | у            |

| TOF         | L0  or  L1                      | >100       | $\mathrm{FTL}$       | $\mathbf{n}$ |

| ${\bf FIT}$ | L0  or  L1                      | 100        | $\mathrm{FTL}$       | $\mathbf{n}$ |

| ACO         | L0  or  L1                      | 100        | $\mathrm{TTC}$       | $\mathbf{n}$ |

| TRD         | LM&(L0 or L1)                   | 39         | FTL&TTC              | у            |

| EMC         | $^{\#}\mathrm{L}0\&\mathrm{L}1$ | 46         | $\mathrm{TTC}$       | $\mathbf{n}$ |

| PHO         | $^{\#}\mathrm{L}0\&\mathrm{L}1$ | 46         | $\mathrm{TTC}$       | n            |

| HMP         | $^{\#}\mathrm{L}0\&\mathrm{L}1$ | 2.5        | $\mathrm{TTC}$       | $\mathbf{n}$ |

# Sub-detector upgrade effort

| Det                  | #                   | Run1&2           | upgrade          | FE ASIC      | FEC              | ROC      |

|----------------------|---------------------|------------------|------------------|--------------|------------------|----------|

|                      | channels            | RO rate          | RO rate          |              |                  |          |

|                      |                     | $[\mathrm{kHz}]$ | $[\mathrm{kHz}]$ |              |                  |          |

| TPC                  | $5 \times 10^5$     | 3.5              | 50               | 17000 SAMPA  | 3400             | CRU      |

| MCH                  | $10^{6}$            | 1                | 100              | 33000  SAMPA | 500              | CRU      |

| ITS                  | $25 \times 10^{9}$  | 0.5              | 100              | 25000  ASICs | 184              | CRU      |

| MID                  | $21 \times 10^{3}$  | 1                | 100              | FEERIC       | 234              | CRU      |

| ZDC                  | 22                  | 8                | 100              |              | commercial&1 ZRC | CRU      |

| TOF                  | $1.6 \times 10^{5}$ | 40               | 100              |              |                  | 72  DRM  |

| FIT                  | 160 + 64            | 80               | 100              |              | upgrade          | DRM(TOF) |

| ACO                  | 120                 | 100              | 100              |              |                  |          |

| $\operatorname{TRD}$ | $1.2 \times 10^{6}$ | 1                | 50               |              |                  | CRU      |

| EMC                  | $18 \times 10^{3}$  | 3.7              | 46               |              |                  |          |

| PHO                  | $17 \times 10^{3}$  | 3.7              | 46               |              |                  |          |

| $_{\mathrm{HMP}}$    | $1.6 \times 10^{5}$ | 2.5              | 2.5              |              |                  |          |

# Summary

- Rate upgrade: 50 kHz

- New ITS & MFT

- TPC GEMs & continuous, trigger-less read-out

- Muon system electronics upgraded

- Common component approach widened

# Backup

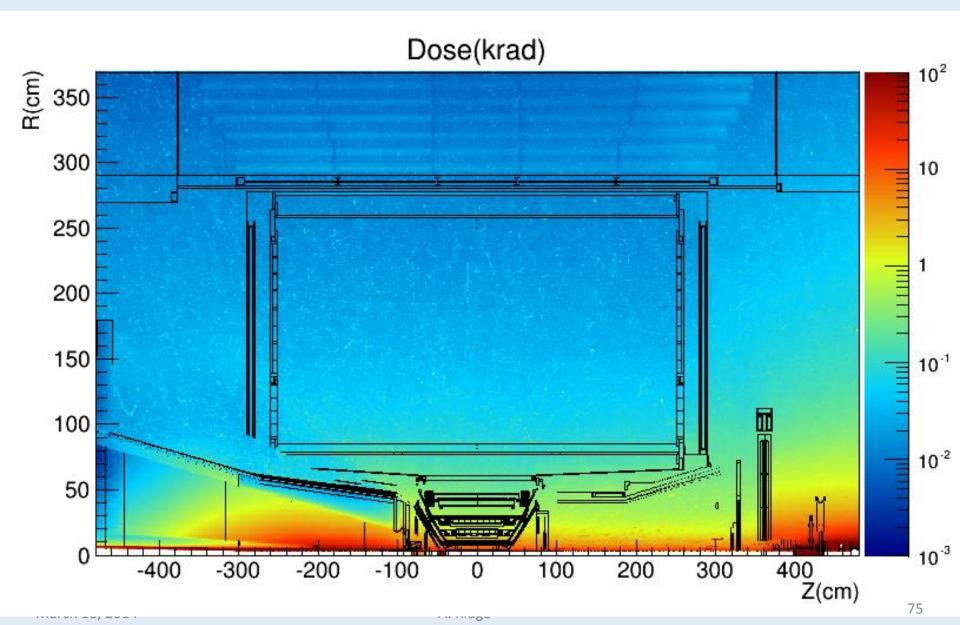

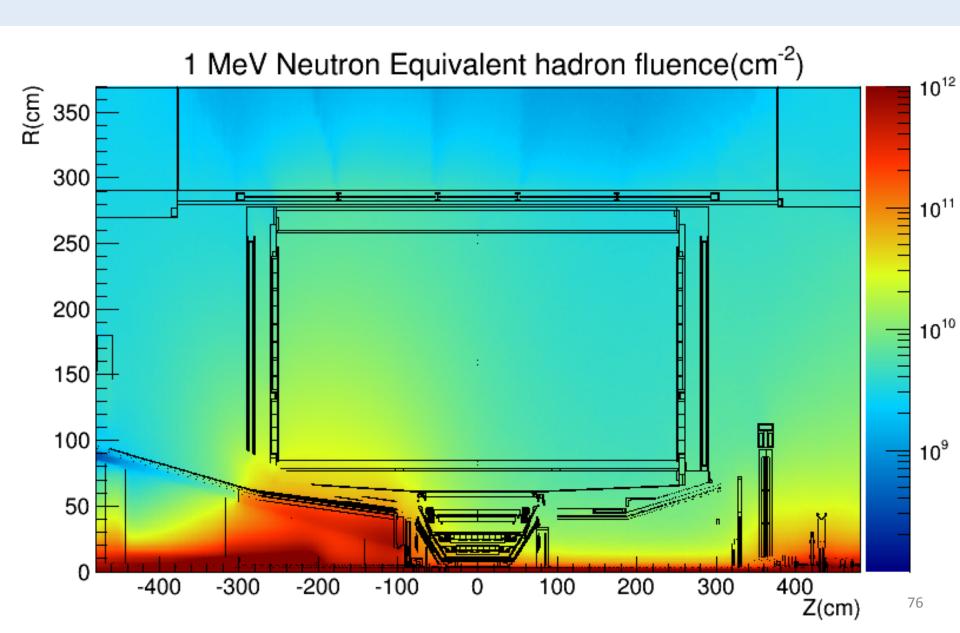

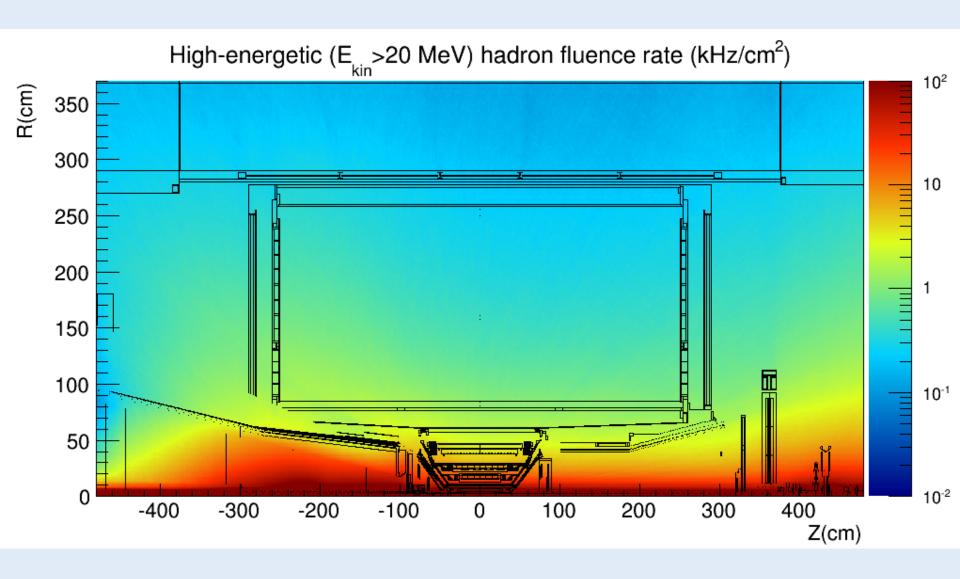

# **Radiation Levels**

#### **Radiation levels**

| Element  | r    | $\mathbf{z}$  | TID                  | 1 MeV neq            | >20 MeV had. |

|----------|------|---------------|----------------------|----------------------|--------------|

|          | (cm) | (cm)          | (krad)               | $({\rm cm}^{-2})$    | $(kHz/cm^2)$ |

| ITS L0   | 2.2  | [-13.5, 13.5] | 646                  | $9.2 \times 10^{12}$ | 1600         |

| ITS L1   | 2.8  | [-13.5, 13.5] | 387                  | $6.0 \times 10^{12}$ | 1000         |

| ITS L2   | 3.6  | [-13.5, 13.5] | 216                  | $3.8 \times 10^{12}$ | 500          |

| ITS L3   | 20   | [-42.1, 42.1] | 13                   | $5.2 \times 10^{11}$ | 28           |

| ITS L4   | 22   | [-42.1, 42.1] | 9                    | $5.0 \times 10^{11}$ | 24           |

| ITS L5   | 41   | [-73.7, 73.7] | 6                    | $4.6 \times 10^{11}$ | 10           |

| ITS L5   | 43   | [-73.7, 73.7] | 4                    | $4.6 \times 10^{11}$ | 9            |

| MFT D0   | 2.5  | -50           | 395                  | $6.7 \times 10^{12}$ | 1100         |

| MFT D1   | 2.5  | -58           | 392                  | $6.4 \times 10^{12}$ | 1040         |

| MFT D2   | 3.0  | -66           | 767                  | $5.9 \times 10^{12}$ | 760          |

| MFT D3   | 3.5  | -72           | 427                  | $4.3 \times 10^{12}$ | 520          |

| MFT D4   | 3.5  | -76           | 541                  | $4.8 \times 10^{12}$ | 560          |

| FIT1     | 5    | -80           | 181                  | $3.0 \times 10^{12}$ | 280          |

| FIT2     | 5    | 340           | 103                  | $1.4 \times 10^{12}$ | 200          |

| TPC In   | 79   | [-260, 260]   | 2.1                  | $3.4 \times 10^{11}$ | 3.4          |

| TPC Out  | 258  | [-260, 260]   | 0.3                  | $5.2 \times 10^{10}$ | 0.7          |

| TRD      | 290  | [-390, 390]   | 0.4                  | $4.8 \times 10^{10}$ | 0.54         |

| TOF      | 370  | [-370, 370]   | 0.13                 | $2.6 \times 10^{10}$ | 0.26         |

| EMCAL    | 430  | [-340, 340]   | 0.06                 | $1.5 \times 10^{10}$ | 0.02         |

| MCH S1   | 19   | -536          | 0.42                 | $4.2 \times 10^{11}$ | 3            |

| MCH S2   | 24   | -686          | 0.19                 | $1.4\times10^{11}$   | 1            |

| MCH S3   | 34   | -983          | 0.14                 | $1.6\times10^{11}$   | 0.9          |

| MCH S4   | 45   | -1292         | 0.18                 | $3.0 \times 10^{11}$ | 1            |

| MCH S5   | 50   | -1422         | 0.91                 | $2.5\times10^{11}$   | 0.7          |

| CTP Rack | 600  | -1295         | $4.8 \times 10^{-3}$ | $7.8 \times 10^{9}$  | 0.03         |

|          |      |               |                      |                      |              |

Factor 10 safety on TID & neq:

TID/neq numbers factor 2 higher than ALICE-Run1/2 design rates

Factor 2 safety on >20 MeV hadrons: factor 3 higher than ALICE-Run1/2 design rates

**Table 3.1:** Total Ionizing Dose (TID) and 1 MeV neq hadron fluence for  $10\text{nb}^{-1}$  PbPb +  $6\text{pb}^{-1}\text{pp} + 50\text{nb}^{-1}\text{pPb}$  collisions (including a safety factor 10) as well as high energy hadron fluence for 50 kHz PbPb collisions (including a safety factor 2).

# Radiation

#### Radiation

#### Radiation

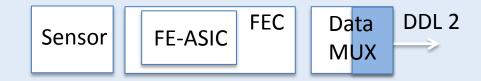

# **Detector Summary**

#### Muon identifier

- 21.000 channels (RPC) Sensor

- sor FE-ASIC FEC

- replacement of front-end electronics to slow down aging speed of RPCs

- by operation in avalanche mode reducing charge produced in the gas

- Front-end ASIC is replaced by FEERIC ASIC

- with amplification

- Readout out at 100 kHz @ 0 % busy

#### Muon identifier

- Replacement of 2 levels of data concentrators by 234 new front-end cards and CRUs

- Small scale system with FEERIC will be tested already in run 2

#### Muon identifier

#### TRD

1.151.000 channels

- rate upgrade from 8 kHz to 50 kHz with 23 % busy

- triggered operation (LM & L0)

- FE electronics unchanged, but data load reduced with firmware change

- pre-processed data (tracklets) are transferred only or

- partial read-out based on electron region candidates

- Data MUX is CRU

#### **TRD**

#### TOF

~160.000 MRPC pads

- rate upgrade from 10s of kHz to 100 kHz PbPb without dead time

- max limit by HPTDC in FEC is 265 kHz

- rate limit comes from VME based read-out and data format

- upgrade firmware for data format and VME protocol

- replace 72 2<sup>nd</sup> level data concentrator boards (DRM)

#### TOF

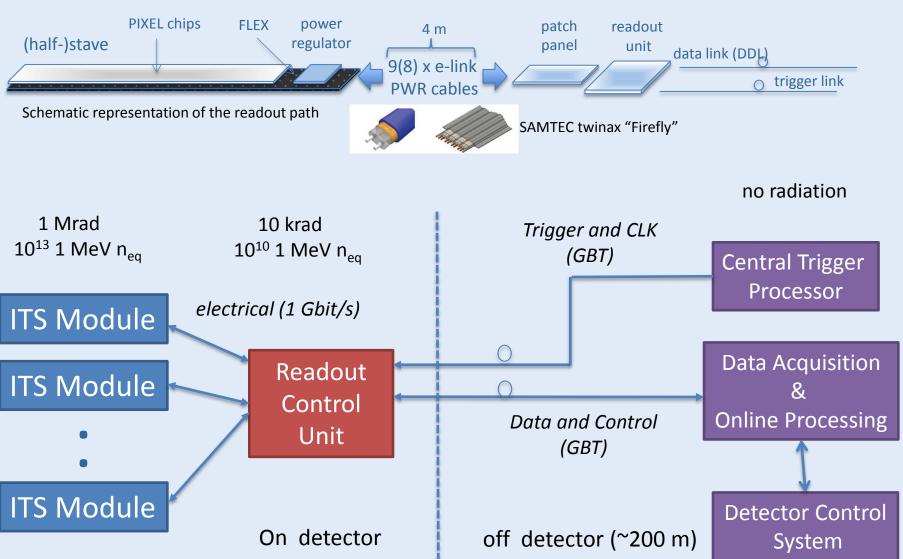

# **Detector developments: ITS**

25 G pixels

- complete new detector

- ASIC, sensor, read-out, mechanics cooling

- triggered @ L0

- Detector module sends data 1 Gb/s links

- base-line electrical

- close to detector link interface needed

# Detector developments: FIT

• 160 MCP-PMT +

- 64 Scintillators

- Provides interaction trigger

- timing reference for TOF

- multiplicity measurement

- New detector implementation

- new front-end

- RO based on TOF read-out scheme

# **Detector developments: ZDC**

22 channels

- Sensor FEC Data DDL 3

- outside of radiation zone

- use NIM, VME and commercial electronics

- provides timing trigger

- upgrade from 8 kHz to 16 kHz by introduction of multi-event buffers in firmware (run 2)

- to 100 kHz without dead time

- commercial digitizers with on board FPGAs

- TDC model firmware upgrade

- replacement of data concentrator card (ZRC) and

- use CRU

### **Detector developments: EMC**

~ 18.000 channels

**FFC**

DDL<sub>2</sub>

- provides trigger

- L0 input: sum

- L1 input: shower and jet

- has already been upgraded to 46 kHz @ 15 % busy

- front end (ALTRO) limits to 50 kHz

- data reduction by on-line data evaluation

- replacement of data concentrators by SRU (Scalable Read-out Unit, RD51)

# **Detector developments: PHO**

~ 17.000 channels

- provides trigger

- L0 input: sum

- taking same approach as EMC to 46 kHz @ with busy time

- front end (ALTRO) limits to 50 kHz

- data reduction sample number reduction

- replacement of data concentrators by SRU (Scalable Read-out Unit, RD51)

- replacement of trigger region units (TRU)

# **Detector developments: HMP**

Sensor FEC Data DDL 2 MUX

- ~160.000 channels MWPC

- RO rate to 2,5 kHz

- No detector/electronics change