## LHCb Upgrade

### Electronics Status & Outlook

### on behalf of the LHCb collaboration

Ken Wyllie, CERN

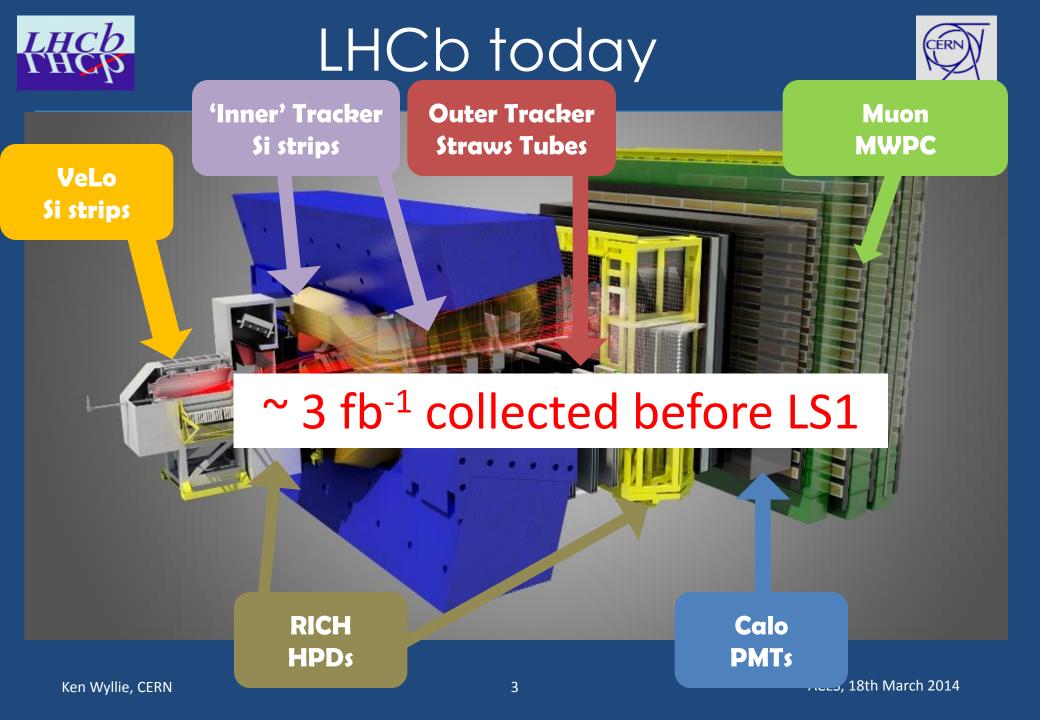

Upgrade philosophy Electronics Architecture Review of electronics R&D

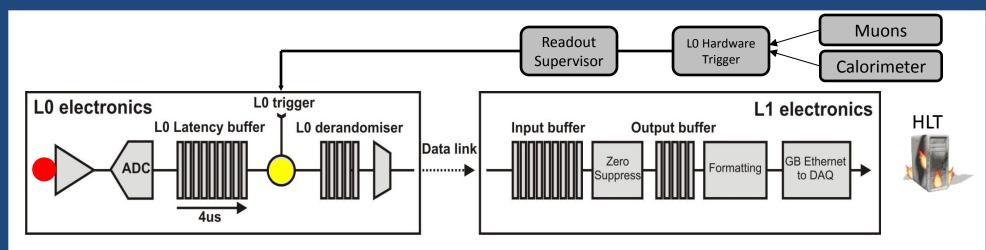

# Existing readout system

| Bunch crossing rate | 40 MHz *                  |

|---------------------|---------------------------|

| L0 trigger rate     | 1 MHz average             |

| L0 trigger latency  | 4 $\mu$ s fixed (160 BXs) |

| Event readout time  | 900 ns                    |

| Event rate to DAQ   | 1 MHz                     |

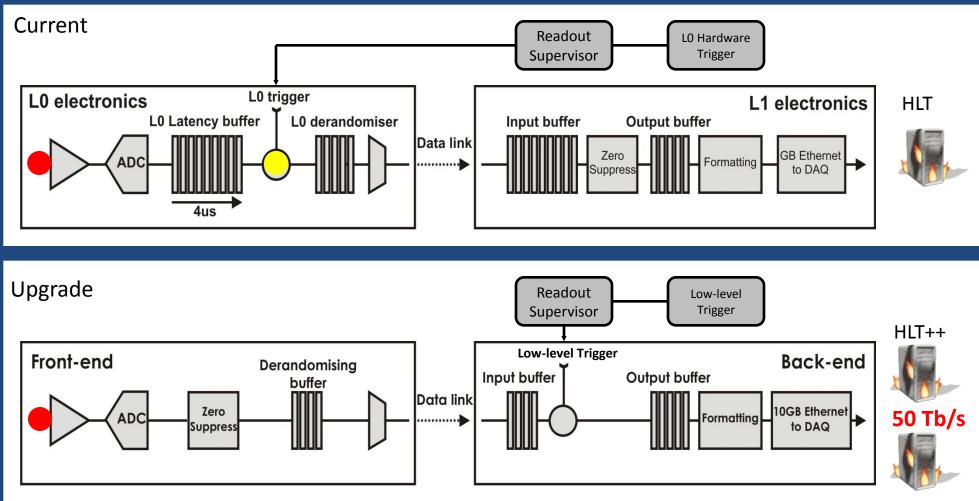

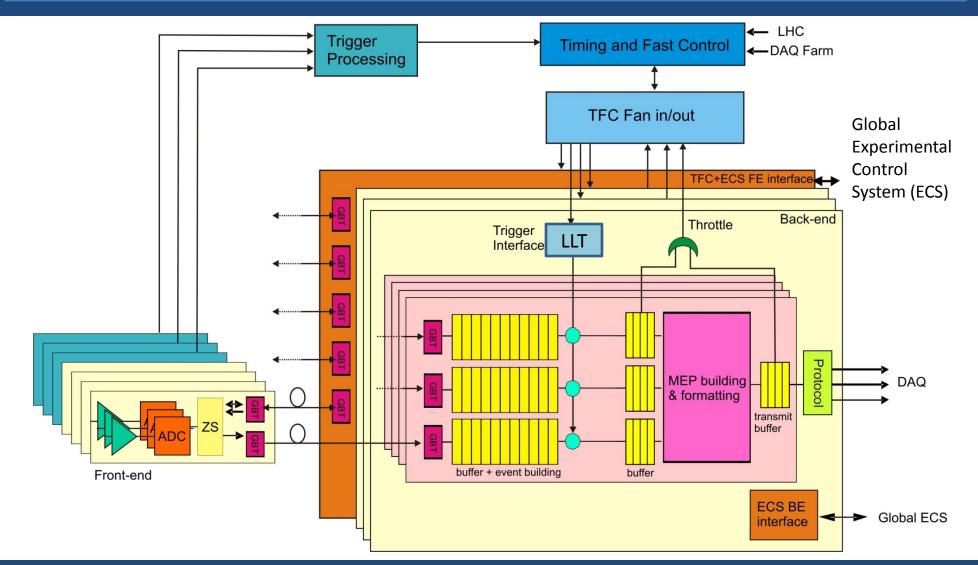

# Upgrade architecture

#### No 'front-end' trigger, Event rate to DAQ nominally 40 MHz

## Can we do it?

..... actually, can we afford it?

10Gbit/s

Trends in high speed optical data transmission

40Gbit/s

..... and strong programme for rad-tolerance ..... and trends in embedded links in FPGAs

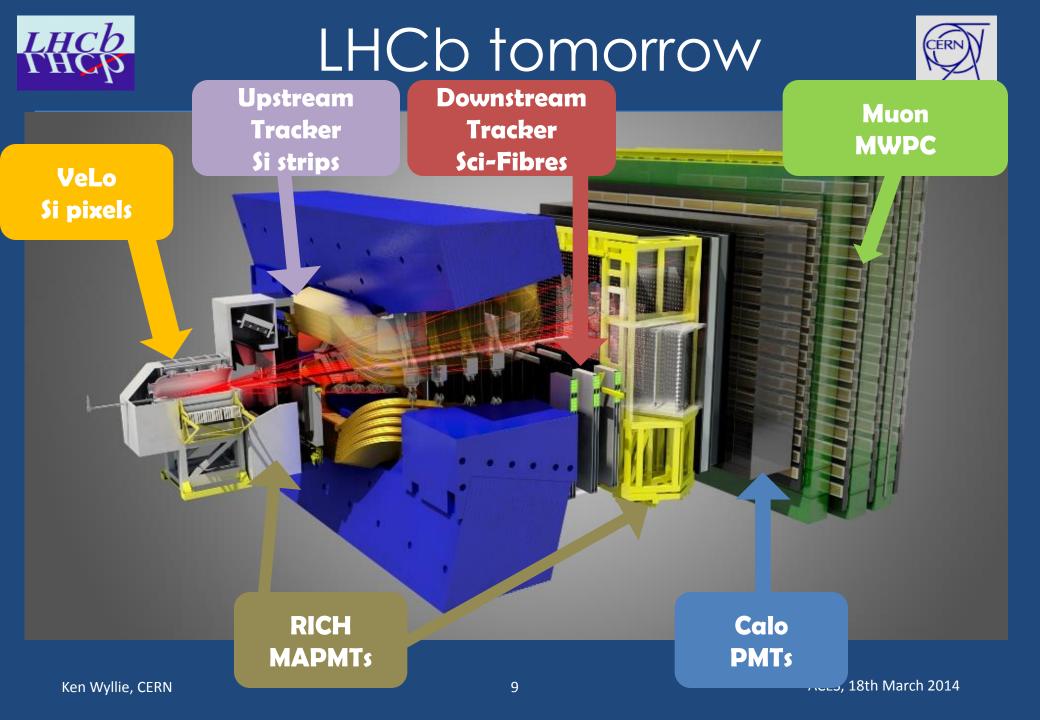

# Upgrade installation in LS2

1Gbit/s

Data compression on front-end driven by cost:

no compression

~ 80,000 links (4.8 Gb/s)

20 MCHF

compression

~ 12,500 links (cf 8,000 today)

3.1 MCHF

NB: Compression (zero-suppression) currently done in off-detector FPGAs:

careful balance of complexity vs robustness needed a few iterations get it right !

### => Aim for flexibility + scale-ability in upgrade

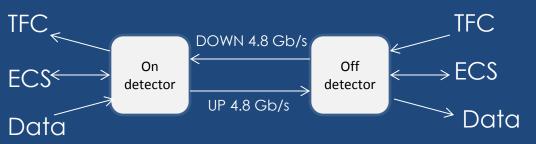

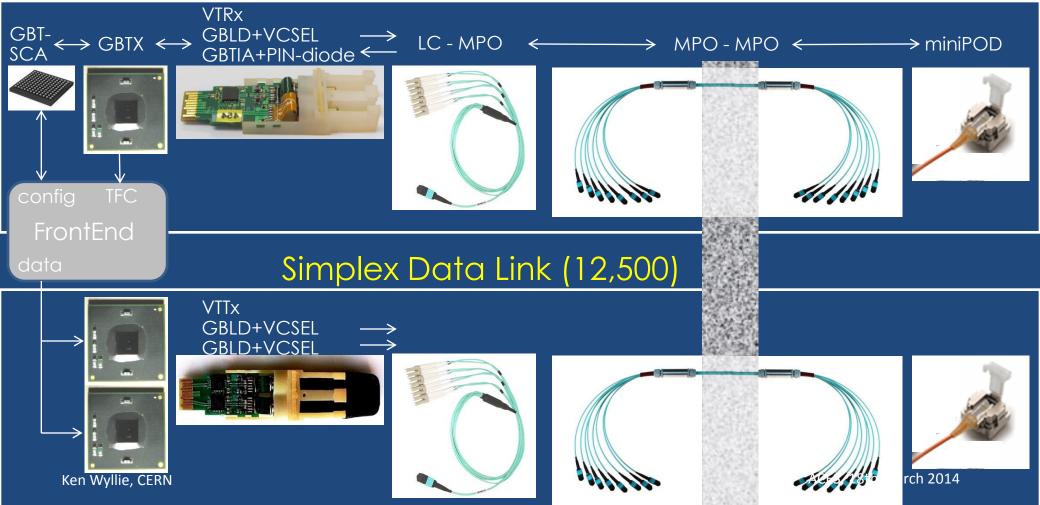

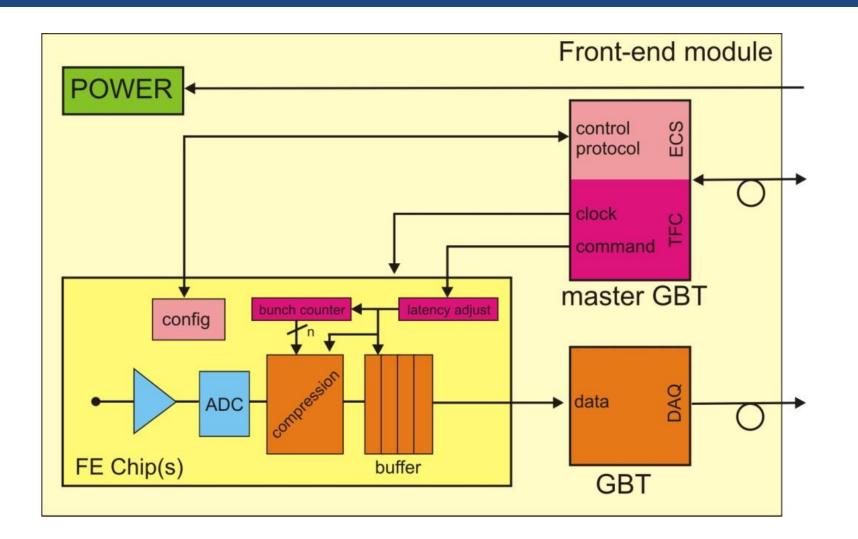

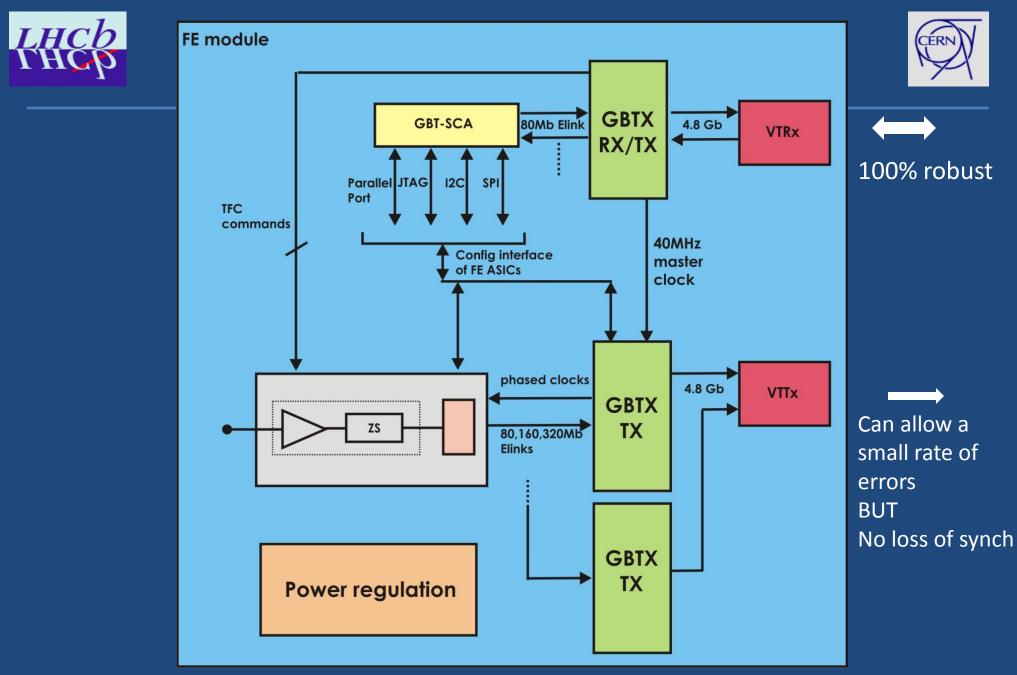

### New compact link offers combined Data, TFC, ECS

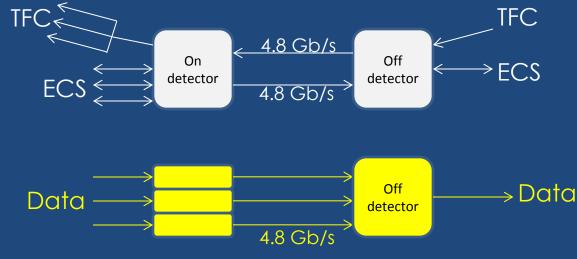

# Need UP bandwidth >> DOWN bandwidth => Combine TFC+ECS; Separate Data

# Review of electronics R&D (non-exhaustive)

# Generic Implementation

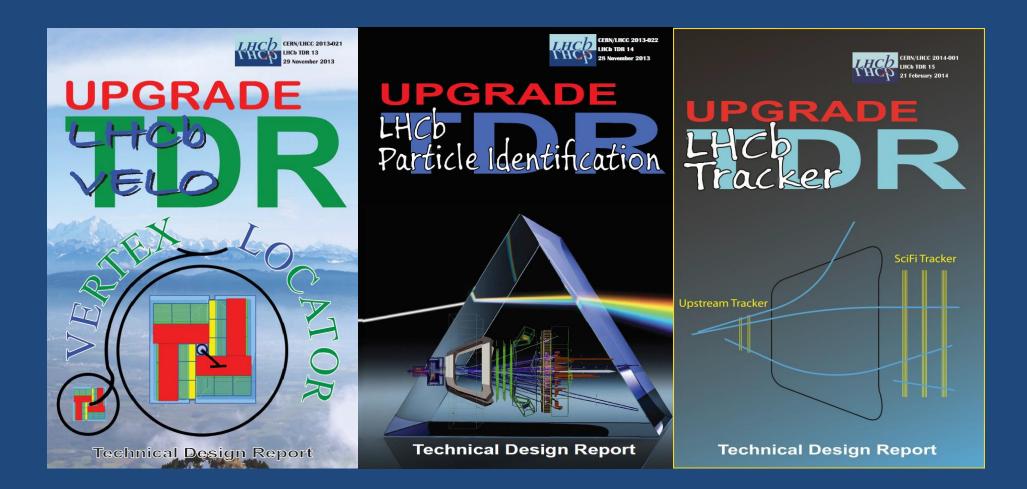

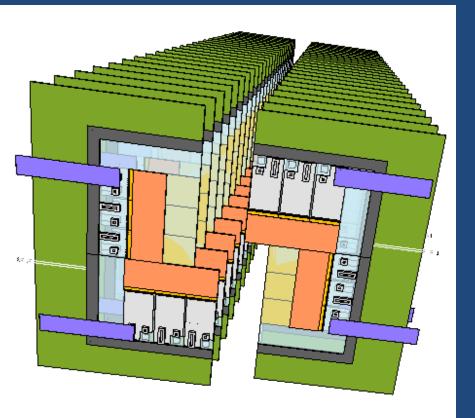

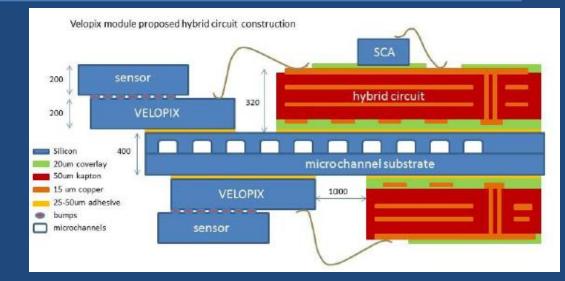

# VeLo (Si pixels)

### 26 planes of sensor tiles 5.1mm to beam

### FE Electronics in VeloPIX chip:

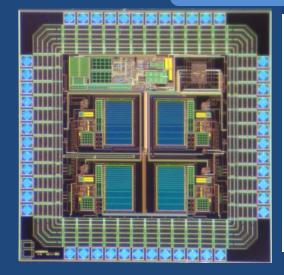

55 μm pixels, 256 x 256 array 130 nm CMOS Binary readout Development of TimePIX3

# VeloPIX data rate

#### Matrix = $128 \times 64$ super-pixels <u># tracks per 25ns</u> Data packet [mm] 110um 30 SP addr 13b Timestamp 9b Hitmap 8b 1.7 1.3 0.8 > 3 7 20 8.5 3.0 1.1 10 2 Super 6 220um Pixel 8.5 1.7 core -10 5 1 3.0 1.3 Hottest chip: -20 4 $\mathbf{0}$ -30 1.1 0.8 16 Gbit/s of data -40 20 -20 40 0 Analog FE x [mm]

### Four serialisers per chip @ 5.12 Gbit/s

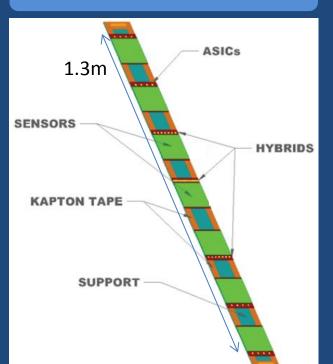

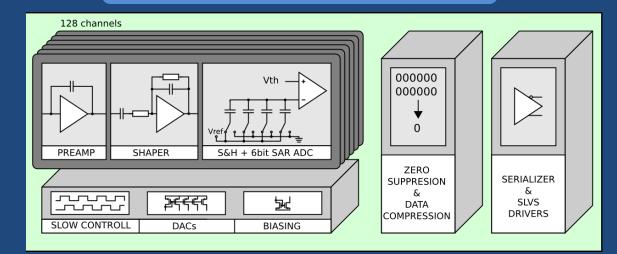

# 🙀 Upstream Tracker (Si strips)

#### 4 planes of 16 staves

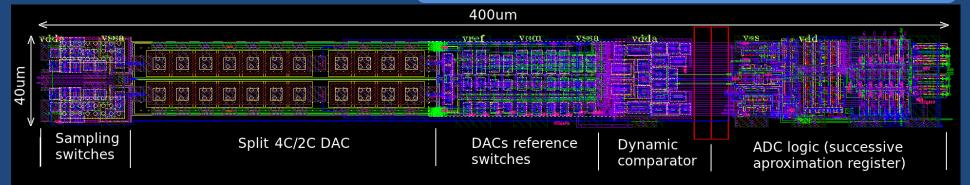

#### SALT chip in 130nm CMOS

#### Prototype 6-bit SAR, 0.35 mW @ 40 MS/s

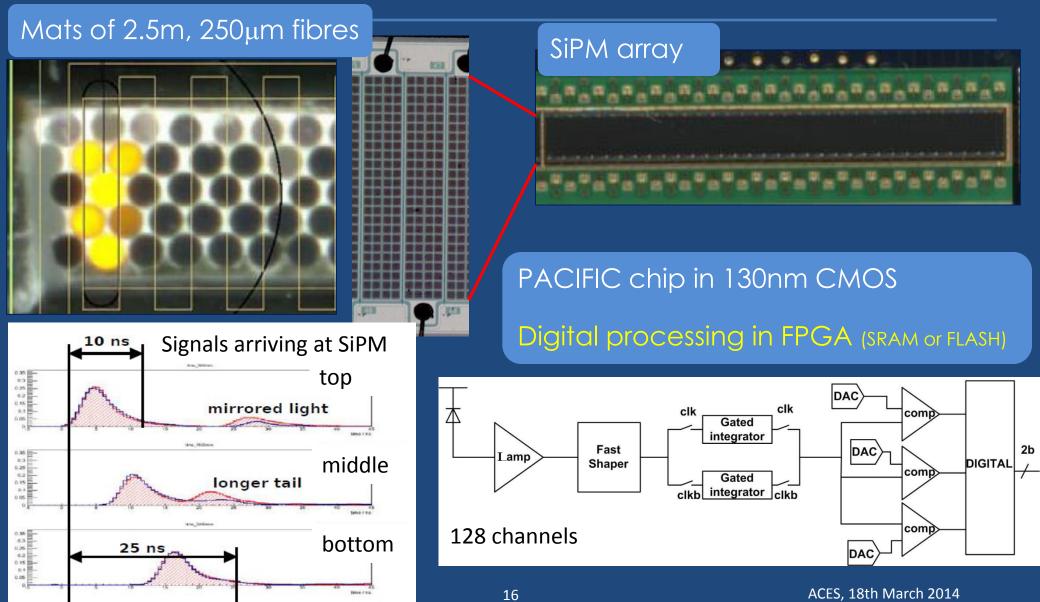

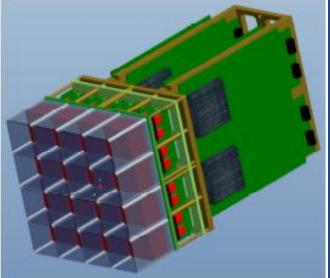

# SciFi Tracker (SiPMs)

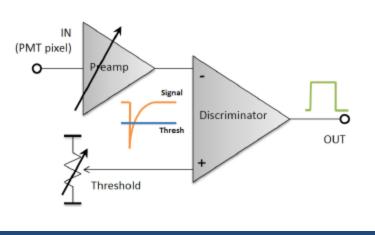

# RICH (MAPMTs)

#### 4,500 64-channel PMTs

#### CLARO chip in 0.35 $\mu m$

### FPGA for digital processing (SRAM)

Low occ. regions => Zero Suppression High occ. regions => no Zero Suppression

8000 PMTs

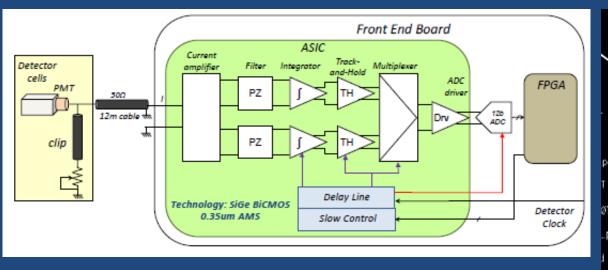

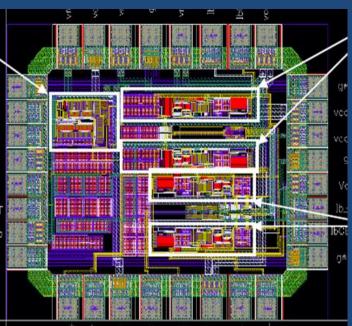

# Calorimeter (PMTs)

#### ICECAL chip in 0.35 $\mu$ m

### FPGA for digital processing (FLASH)

## Muons (MWPCs)

#### Re-use front-end ASICs on chambers (CARIOCA + DIALOG)

New 'Off-detector' cards with new chip nSYNC

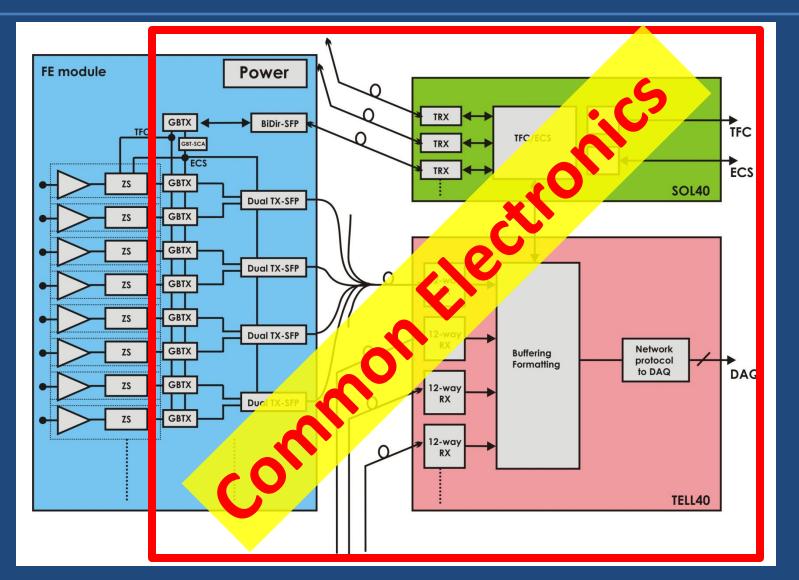

Generic Link: GBT chips + Versatile Link + commercial components Duplex Master Control Link (2,500)

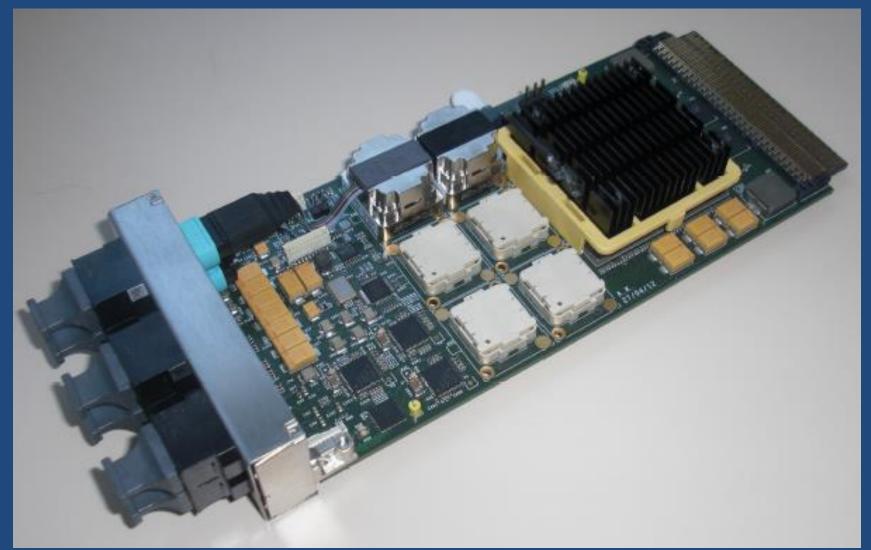

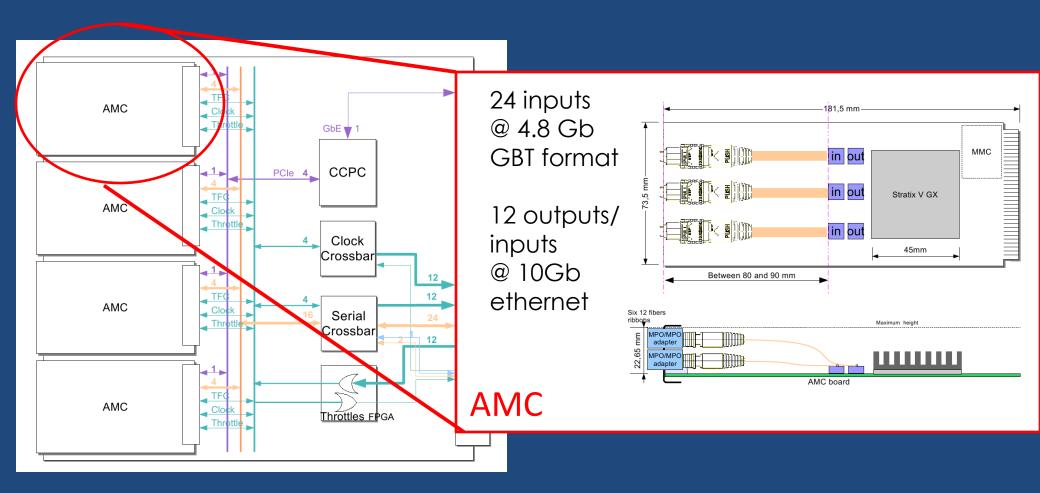

# Common 'readout' board 🖗

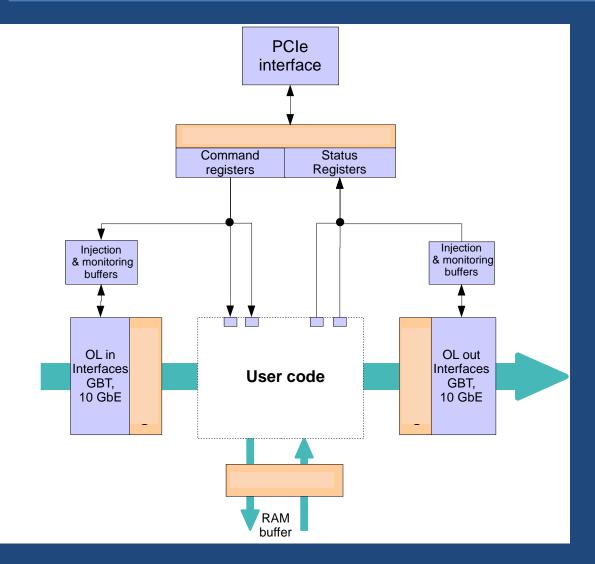

GOAL: Generic FPGA-based hardware for many tasks:

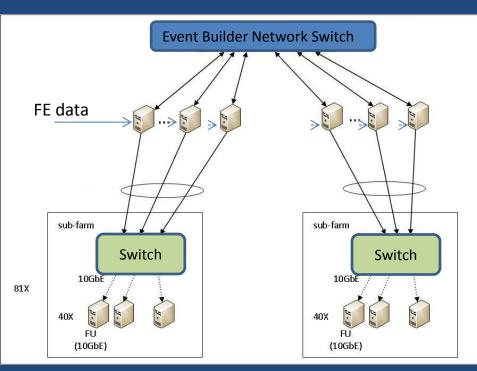

- TELL40 for Data

- SOL40 for ECS/TFC

- TRIG40 for LLT

each with different firmware flavours

1<sup>st</sup> developments focussed on ATCA + AMC R&D close to completion Small production made for lab systems

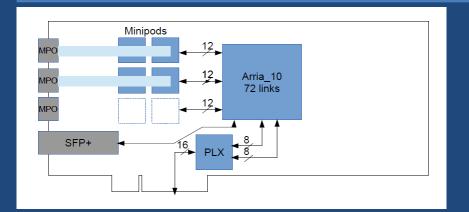

## Example: TELL40

96 inputs @ 4.8 Gb  $\rightarrow$  processing in FPGA $\rightarrow$  48 10G ethernet ports

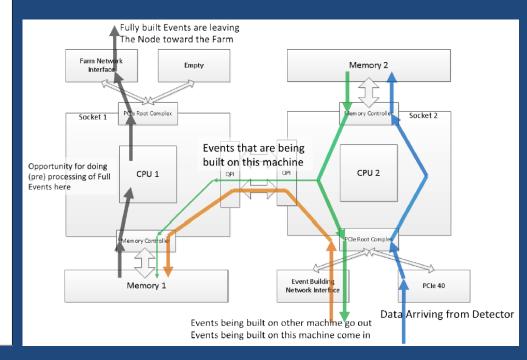

## Move to PCle ?

### Use PC memory & processors for event building

Choose network interface at last moment (cheapest)

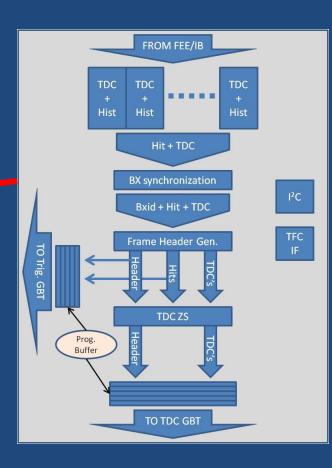

# TELL40 firmware

#### Project across many groups

Centrally coordinated

Common interfaces

User code for data processing

100 Gbit/s Ethernet or Infiniband

4.8 Gbit/s

10/40 Gbit/s

Ethernet or

Infiniband

LHCb THCp Long distance transmission?

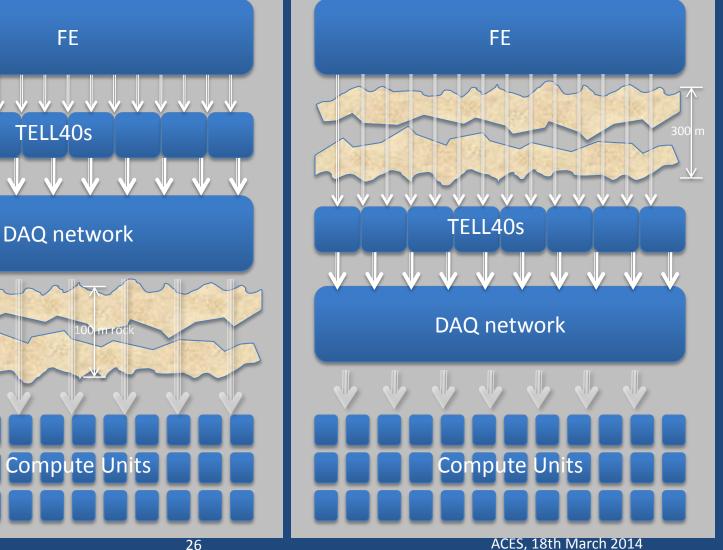

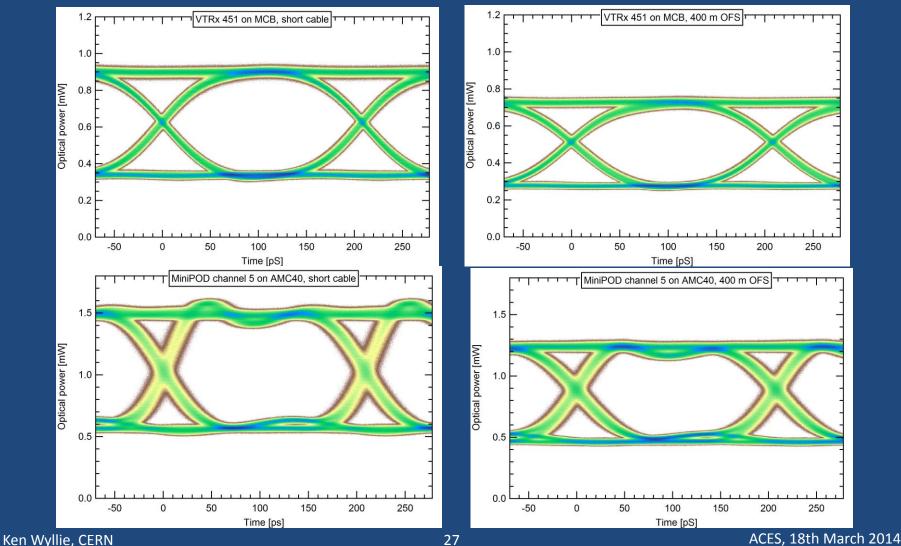

# Long distance transmission?

Short fibre

400m OM4 fibre

### All data in a box

Clear architecture concept with many common items

R&D for sub-detectors is moving well

We rely on new generic developments (GBT, Versatile Link, DC-DC)

Manpower is improving

Aggressive but feasible schedule...... Shift of LS2 helps!

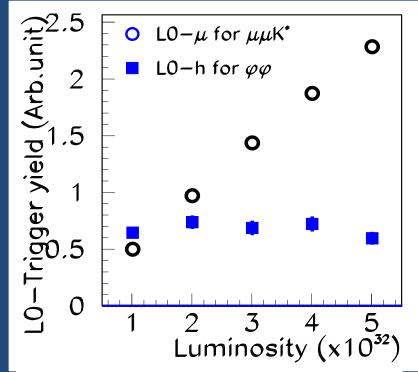

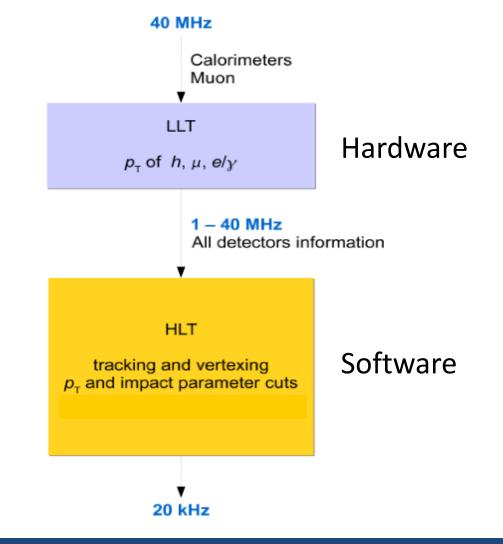

# Motivation for upgrade

At L = 2(+) x  $10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>, beyond 5 fb<sup>-1</sup>, statistics don't improve much

Big statistical improvement if:

increase L to 2 x 10<sup>33</sup>, AND

improve efficiency of trigger algorithms

BUT ..... with current L0 trigger:

rate & latency limited by electronics  $(1 \text{ MHz}, 4 \mu \text{s}) => \text{ saturation}$

### BUT.... efficient trigger decisions require:

- long latencies (>> 4  $\mu$ s)

- computational power

- data from many (all) sub-detectors (momentum, impact parameter .....)

- $\Rightarrow$  Trigger in software

- $\Rightarrow$  Use data from every bunch crossing

- $\Rightarrow$  Upgrade electronics + DAQ <u>for LS2</u>

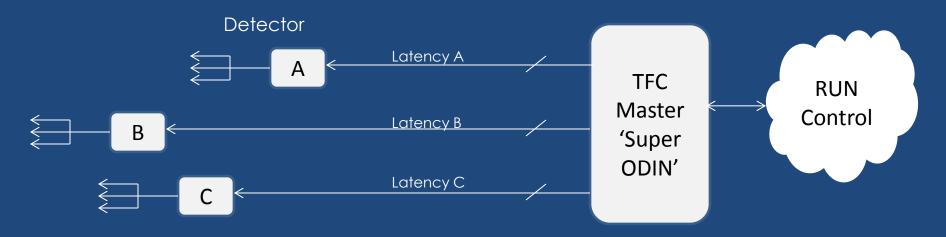

# Kick Architecture: more detail 👰

## *LHCb* Triggering doesn't completely disappear

Control with synchronised fast commands eg bunch-counter reset

Latencies will be measured => pre-scaling of commands by S-ODIN Absolute measurement with: pulsed laser cosmics low intensity LHC beam collisions

Ken Wyllie, CERN