18

## **Collaborating institutions**

- Syracuse University: M. Artuso, S. Blusk, T. Skwarnicki, S. Stone, R. Mountain, J. Wang, P. Gandini, C. Hadjvasiliou, M. Kelsey, S. Ely, T. Britton + 8 undergraduate research assistants

- University of Maryland: H. Jawahery, D. Roberts, J. Andrews, J. B. K. Hamilton, J. Wimberely + EE T. O'Bannon

- University of Cincinnati: B. Meadows, M. Sokoloff, A. Davis

- MIT: M. Williams, P. Ilten

- INFN/University of Milano: N. Neri, J. Fu + EE M. Citterio, A. Abba, F. Caponio, M. Lazzaroni, ME S. Coelli, M. Monti,

- University of Zurich: N. Serra, O. Steinkhamp, E. Graverini,

F. Lionetto, K. Mueller, EE S. Saornil

- AGH Krakow: (EE/Faculty) Marek Idzik, Tomasz Fiutowski, Krzysztof Swientek, Tomasz Szumlak, PhD student: Miroslaw Firlej, Jakub Moron

- □ UT Conceptual design review took place on November 14–15, 2013

- Referees: M. Newcomer (University of Pennsylvania), T. Affolder (U. Liverpool),

D. Lynn (Brookhaven), from LHCb K.

Wyllie and F. Alessio (CERN).

- □ Web site https://indico.cern.ch/ conferenceDisplay.py?confId=272144

### introduction

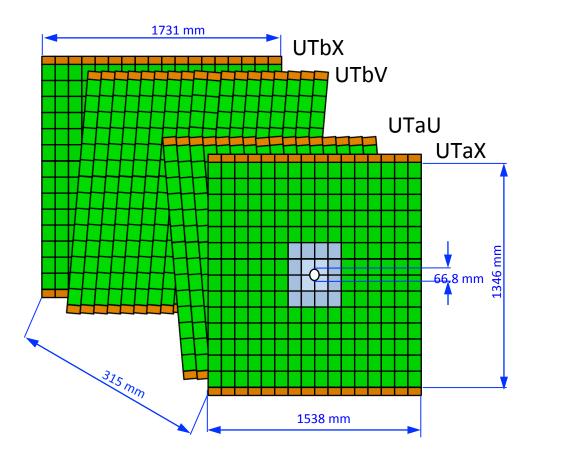

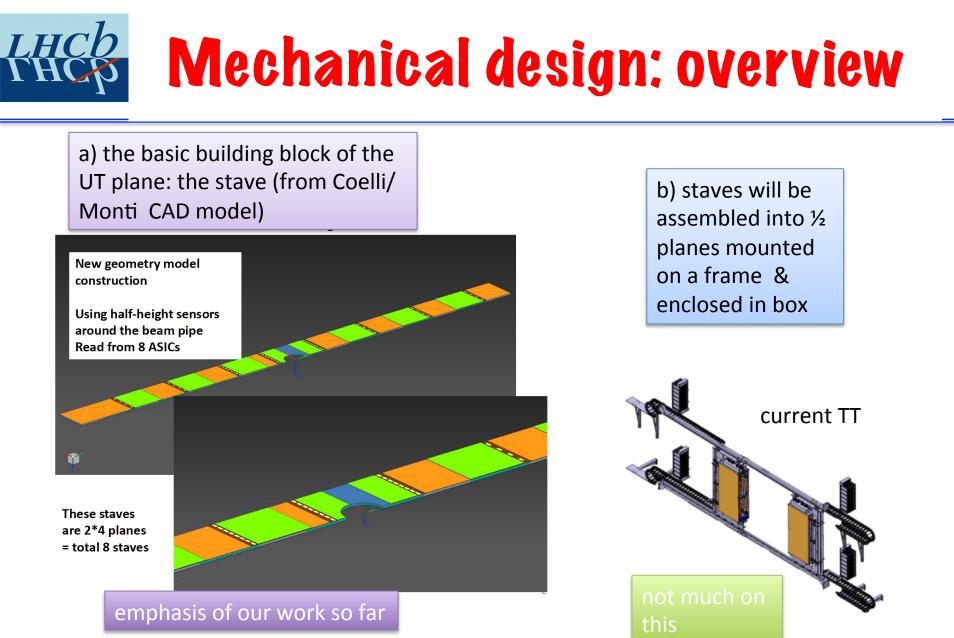

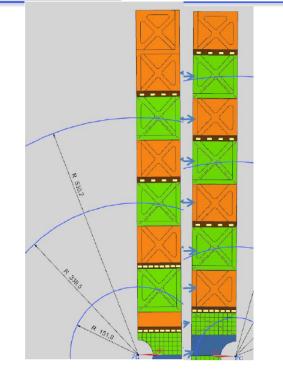

- 4 planes constructed of double-sided staves partially overlapping in the x-direction to ensure 100% coverage

- higher segmentation in the region surrounding the beam pipe

- Inner detectors with circular cut to maximize acceptance

- Electronics located near sensors to allow segmentation & improved signal/noise

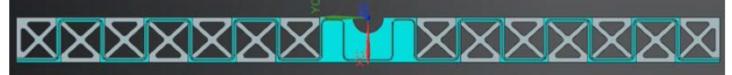

- Basic mechanical unit "stave"

#### With input from R. Mountain, S. Stone, S. Coelli, M. Monti MECHANICAL DESIGN

### the stave

Biggest heat source FE electronics (currently ~5 mW/ch, may go down when FE is reoptimized for lower detector capacitance)

- CO<sub>2</sub> evaporative cooling distributed by "snake pipe" running under FE electronics row (alternative with 2 straight pipes being studied)

- Mechanical support/thermal coupling provided by a variety of CF based materials (facings, ALLCOMP, ROHACELL, carbon foam)

upstream face

downstream face

## Feedback on stave design

- □ The stave design follows developments from ATLAS and in principle should work with a couple of caveats. The snake pipe design may have problems with extra pressure drops or internal pressure forcing the pipe to straighten. We recommend also modeling a straight pipe design similar to what was presented but with the carbon foam optimally placed for maximum cooling. Also, if the pipe and cooling with the snake pipe does work, it is worth considering a mirror image design in which the pipe enters from the other edge of the stave so that the pipe more closely approaches the beam pipe cutout region in the middle of the stave. The team should focus on quickly resolving the pipe design as this impacts the stave construction.

- Determination of the cooling tube design (snake vs straight) is our top priority and is ongoing now. Both prototyping of real material demonstrator modules and the related thermal simulations are being pursued to settle this issue. These will be more advanced than the results previously shown. We expect to have a resolution in Q1 2014.

## Stave design (2)

- Consider whether the cutouts in the rohacell core are worth the effort in terms of radiation length savings. Also, one needs to consider that rohacell is hygroscopic and whether this will create problems in the different environments that the stave will inhabit from construction to installation.

- Confirm the radiation hardness of rohacell to the expected upgrade fluencies.

- The Rohacell core pieces with cutouts are 42% of the pieces without cutouts. This gives a radiation length contribution per plane of 0.019% as opposed to 0.046%, a savings of 0.027%. Glue layer needed to attach the Rohacell to the embedded structure needs to be taken into account!

- On the hygroscopicity of Rohacell, the moisture absorption is roughly 10% of the ambient relative humidity, and linear expansion has been measured to be 0.5% at 60% humidity [NIM.A400(1997)224]. In the first half of 2014, we will make our own measurements of this effect and set standards for the ambient humidity during construction. Additionally we will consider sealing the stave so as to prevent any moisture uptake.

- Rohacell has been reported earlier to show a small degradation of compressive strength, and a reduction in its deflection at fracture to 2.5 mm, at 10 MRad for a different density version of the foam. A reduction of the breaking force has been reported at 20 Mrad [PHENIX-MVD-97-5, IU-ATLAS-96-1, LHCb EDR 2002-009]. During 2014, we plan to measure the deflection as well as its tensile strength to above 30 Mrad, as part of the UT irradiation test program. These previous irradiation measurements have been made for flexural deformation (horizontal three-point tests), whereas in the UT we will mount the stave vertically and so it is tensile deformation that is more relevant here. The flexural motion is already bounded by the need to protect the wirebonds. Importantly, the use of this foam is not as a structural element per se, but as a core in a sandwich structure in which its main functionality is to separate the facings. Additionally, in the very central region of the UT, Rohacell may be replaced by carbon foam so that it will never receive the maximum irradiation exposure.

- To be cautious, we will also investigate other structural foams in case one or another of these issues proves intractable.

## Stave design (3)

- Methods of measuring the change in shape of the stave when chilled needs development.

- This measurement is part of the prototyping effort and will be developed in the early part of 2014 (now). A combination of optical and mechanical techniques will be developed.

- These measurements will be backed by thermo-mechanical simulations, to study temperature induced deformations in the stave.

- □ No mechanical simulations were presented. A vibrational frequency analysis is suggested and understood in terms of stave bending stiffness. The impact of the mounting method and its impact on the first vibrational mode should be simulated. If there are any data on the vibrational spectrum of the area in which LHCB sits these should be made available.

- Dynamic mechanical simulations, including vibrational modes, will be made in the first half of 2014, following the thermo-mechanical deformation studies. This study will also include vibrational excitation of wirebonds.

- Bonding of pipes to carbon foam should be studied more. Might be able to improve uniformity and reliability.

- This bonding technique will be studied in detail during the development and construction of the demonstrator modules.

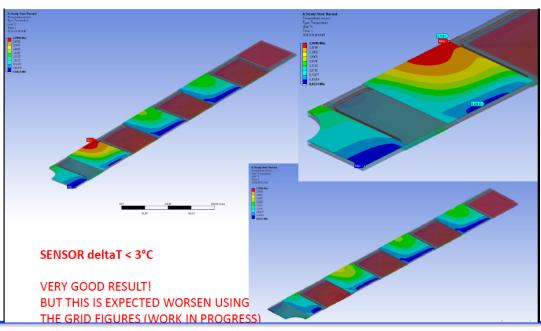

## **Thermal simulations**

- □ The thermal simulations are nascent and will need to be refined. The environment inside the "box" needs specification so that convection and radiative power transfer can be included.

- The radial dependence of detector current in the innermost sensor should be modeled.

- Agreed. Refinements to the thermal simulations are ongoing now. These include more realistic radially-dependent sensor self-heating, data/power-flex power consumption, and refined material parameters.

- The box and its environment will be specified early in 2014 and included in the next round of thermal simulations.

- □ The simulations should show the margin that the innermost sensors have from thermal runaway after full irradiation and after the correct radial dependence of detector current has been implemented.

- Agreed. We plan to couch the results in this more conventional manner.

- An optimized modeling of a straight pipe design with the thermal foam optimally located is suggested.

- This optimization will be part of the first round of thermal simulations, which will help decide the snake vs straight tube geometry and which are ongoing now.

- Power generated in the bus cables should be included in the simulations as soon as a bus tape preliminary design in generated.

- See above.

#### □ See

<u>https://indico.cern.ch/getFile.py/access?</u> <u>contribId=4&resId=0&materialId=slides&confId=292452</u> (Coelli/ Monti)

Sensor appears with reasonably uniform temperature & target temperature of -5°C within easy reach Alternative configuration with 2 straight pipes being studied

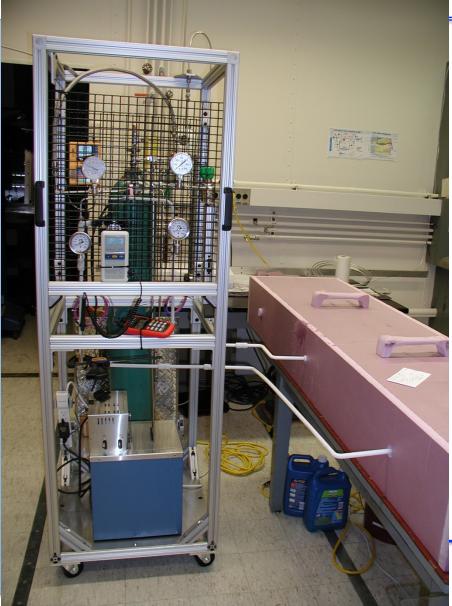

# **Kack** CO<sub>2</sub> COOLING - Blow-Thru System

- CO<sub>2</sub> Blow-Thru System

- Operating now (in mech lab)

- Cooling a test loop (with 40 W heat load)

- Can easily and stably run at -25°C, have reached as low as -50°C

- Learning operational details

- Temperature/pressure control

- Move evaporation point to where it is needed, in the steady-state

- Suppress burping, snowing

- Plan is to use this system to cool full size mock-up of stave (including Si sensors, flex mechanical samples..) & measure temperature profile, first data available next week

## Assembly issues (1)

- Hierarchy of alignment and placement precisions needs to be made more explicit.

- Sensor survey precision needs specification and a method of surveying needs development. The stave is a long object that does not fit onto typical optical metrology machines.

- The conceptual design of the hybrid placement and the alignment scheme is being developed further at this time. The specifications and metrology techniques will be determined by end Q1 2014. An optical microscope or similar device will be obtained.

- The basic specification is to place the sensors with an precision of ~30 µm (1/3 of a fine strip pitch), and to reference targets on each sensor to targets on the stave. The staves will be surveyed in place when mounted in the frame and referenced to the global LHCb coordinate system. Ultimately, these data will be fed into the precision alignment software procedure, which will be made with tracks from data.

- The hybrid alignment and placement will be addressed more completely through a combination of prototyping and engineered fixturing design, which are ongoing now and expected to be completed by end Q2 2014.

### Assembly of modules, bus tape onto stave (2)

- Mounting of the modules will likely be problematic and will likely be the critical step in the assembly. Development of a module mounting scheme and practical testing should take place earlier rather than later and should be concurrent to the stave design/construction project.

- The gluing of long kapton bus tapes onto the stave surface may have difficulties with regards to alignment and bubbling. Development of this method should similarly be begun sooner rather than later.

- Assembly technique prototyping is planned for Q2 2014. The issue of the bowing of the sensors will be taken up in the design of the vacuum tooling being developed to manipulate the hybrids.

- Several options exist for bonding the bus tapes, such as co-curing or running the bus as cables above the sensors. These issues are being addressed now as the bus tape design progresses.

- A fairy comprehensive and standard list of QA procedures was presented and seemed reasonable. Details of the QA procedures will emerge as the designs mature.

- No response required.

- The mechanics for the frame insertion and removal was not presented. Can the existing mechanism be re-used or is this another development project?

- The U-V tilt and its impact on the global frame needs to be worked out more.

- We will attempt to re-use the existing rail structure, but the frame on which the staves will be mounted will have to be a new design. This will include the implications of the stereo staves. We plan to have a realistic design during Q3 2014.

### Shipping to CERN/Infrastructure issues

- Shipping and handling of hybrids and staves needs to be developed more; can cause bigger issues.

- The completed and integrated stave will be handled and shipped in a strong-back frame. The details of local handling will be developed as the prototypes of the staves and hybrid mounting schemes progress. The extended handling issues involved with shipping, reception, and mounting on the frame will be developed with during Q3 2014.

- The mechanics for the frame insertion and removal was not presented. Can the existing mechanism be re-used or is this another development project?

- We will attempt to re-use the existing rail structure, but the frame on which the staves will be mounted will have to be a new design. This will include the implications of the stereo staves. We plan to have a realistic design during Q3 2014.

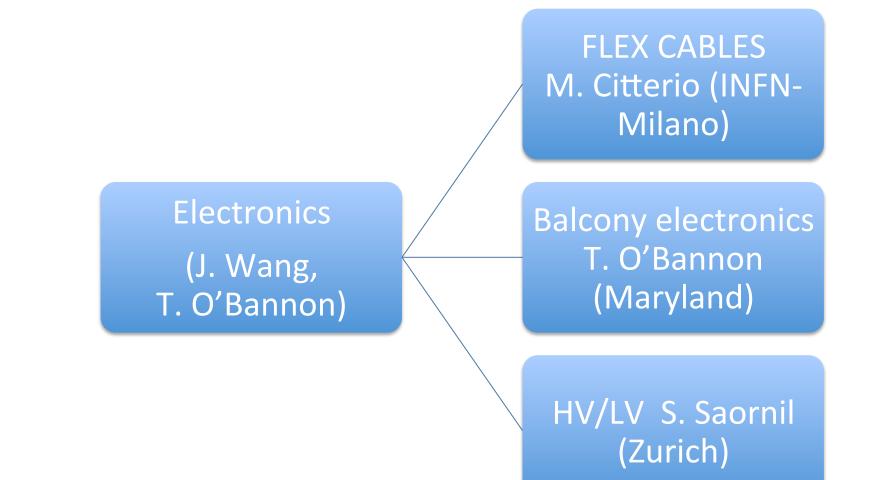

With input from J. Wang, T. O'Bannon, S. Saornil, M. Citterio

### ELECTRONICS

UT Mechanical Responses to Conceptual Design Review

### Electronics & DAQ

#### The main components:

- Front end ASIC

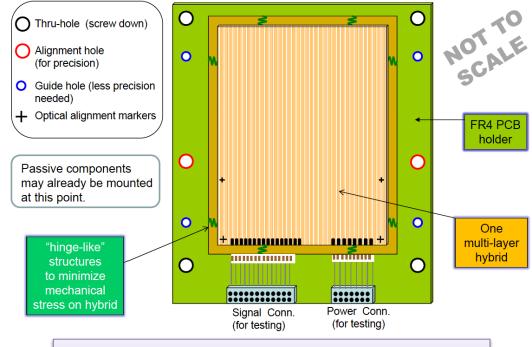

- Hybrids

- Cables

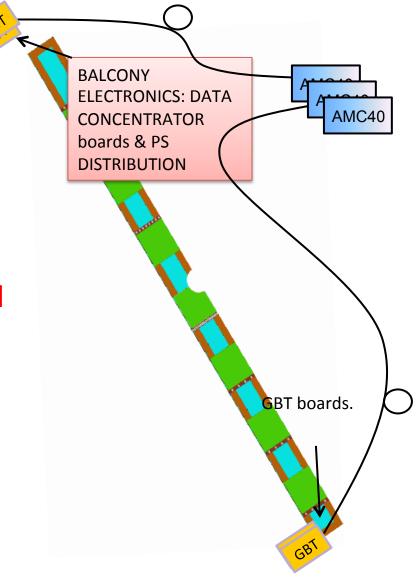

- Balcony electronics

- Data boards (tell40) & experimental control infrastructure are common to the experiment but require firmware to customize them to our needs

#### **ELECTRONICS: GENERAL COMMENTS**

#### The general guidelines:

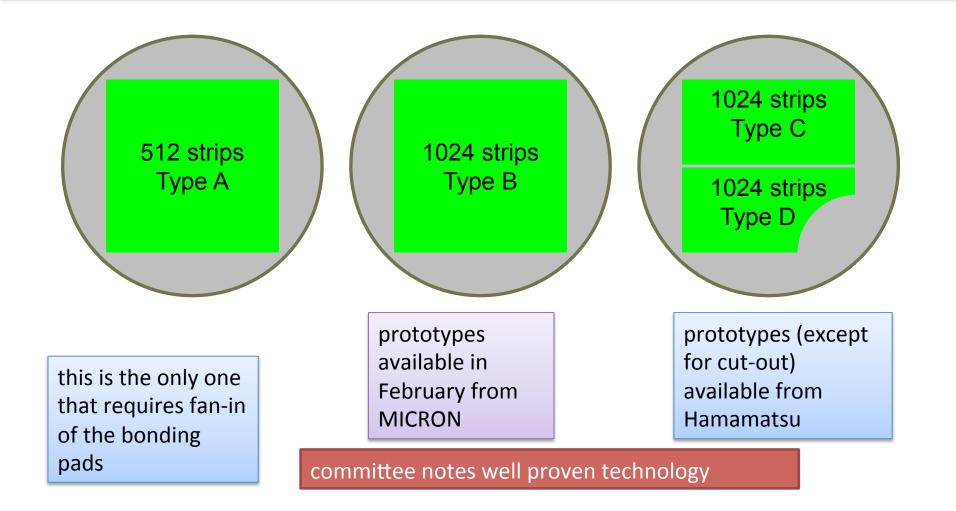

- □ Simplify (less power, less data lines, less variants in design (e.g. hybrids and cables)

- Validate system design (data flow, grounding and shielding)

- Use well proven technologies when practical

- Make sure that all the components can withstand the level of radiation that they are going to be exposed to

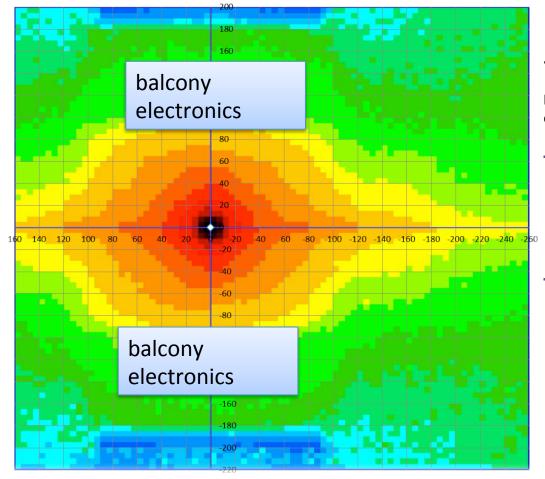

#### Radiation level (from M. Karacson)

XY Dose at Z=230cm, 50 fb-1

# Expected radiation levels for 50 fb<sup>-1</sup> (more details at

https://indico.cern.ch/getFile.py/access? contribId=5&resId=0&materiaIId=slides&confId=292452 )

- at inner radius fluence

3x10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup> (dose 40 MRad)

- at balcony electronics region maximum fluence 1.8x10<sup>12</sup> n<sub>eq</sub>/cm<sup>2</sup> (dose ~100KRad) [this is the maximum, but there is uncertainty of about a factor of 2]

22/1/2014 M. Artuso LHCb Technical Board

- □ Schedule is tight⇒a complete chip from first submission. Intermediate steps should be minimized

- Current plan is to have an intermediate step in February 2014 submission and full chip submission in November. We think that this is the most appropriate way to proceed. I Need to specify digital functions Process in advanced stage

#### Salt chip specifications: analog/geometry

| Parameter                                                                        | Specification                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| sensor capacitance                                                               | typical: 5-10 pF,≤ 20pF                                                                                                |  |  |  |

| dynamic range                                                                    | Max 30 Ke [60-70 mV/fC gain]                                                                                           |  |  |  |

| return to the baseline with<br>uncompensated 0 to replace multipole<br>filtering | NO, presently shaper configuration<br>unchanged, no major gain in power<br>consumption anticipated with this<br>change |  |  |  |

| Power consumption of additional active filter elements                           | out of 1.8 mW ~0.6 mW shaper,<br>power of the analog FE re-optimized<br>for lower capacitance                          |  |  |  |

| Spillover subtraction rather than complex multipole filtering?                   | We do not want to increase the data rate, no major gain here                                                           |  |  |  |

| Pitch                                                                            | fixed to 73 μm (⇒design simplification of sensors and hybrids)                                                         |  |  |  |

| effects of large charge deposition?                                              | frequency, no long tails expected                                                                                      |  |  |  |

#### Overdue burden in power consumption?

NO! Power ~0.35 mW (+0.35mW for single-ended to differential conversion)

#### Overdue burden in data rate?

| NO!           | Component                                                       | Contribution to the data rate    |           |

|---------------|-----------------------------------------------------------------|----------------------------------|-----------|

|               | Header for events without beam crossing                         | 19.6%                            |           |

|               | Header for events with beam crossing and no hit in the detector | 33.3%                            |           |

|               | Header for events with real hits                                | 14.2%                            |           |

|               | Channel address information for events with real hits           | 19.2%                            |           |

|               | ADC information                                                 | 13.7%                            |           |

| Note: ADC inf | ormation monitors loss of gain, c                               | lusters with anomalous shape, ev | ents with |

| high energy d | eposition                                                       |                                  | 26        |

## SALT ADC-continued

# Provision for post-fabrication tuning of zero suppression algorithm?

We believe that the zero suppression algorithm, derived from the VELO experience, is adequate for our needs.

SEU? will be measured in a test run in radiation (~ April 2014). Currently no alternative planned.

### SALT CHIP -MISC

Is hard reset needed?

From ASIC point of view it is not important to have hard reset. Power-On-Reset and Hard Reset pad with pull-up will be implemented. The pad may be not connected, however it may be very useful to have this connection. To avoid long cables, in case we decide to have Hard Reset, it may be generated locally by GBT-SCA chip

SLVS drivers:

Configurable current? Resistor or on board DAC ?

```

We will add DAC in SALT (not yet in February...)

```

#### □ PRE-EMPHASIS? (signal integrity)

Need for this will be checked with cable prototypes, if necessary preemphasis will be added (not in February submission)

- □ TFC interface almost finalized and time adjustment

- implemented in ASIC to compensate for cable delays

- □ SLVS drivers will have configurable current (DAC)

- Only 1 clock transmitted

Re-use/re-borrow: currently voltage regulator & buffer

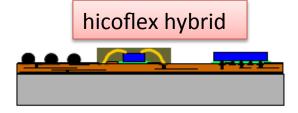

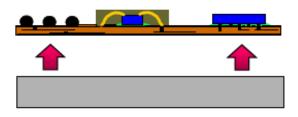

## hybrids and cables

HIGHTEC Custom made MicroCircuits

#### **HiCoFlex**<sup>®</sup> (also for MCM-D)

- Vias are formed by etching Polyimide prior to next level metallization

- 1–4 metal layers

- The release layer is used for lift-off

"a hi-tech hybrid technology was presented motivated by the goal of implementing the data transmission in the most compact form & using the same technology for hybrids and cables

#### **problems**:

- Expensive

- Sensor-ASIC alignment issues for hybrids

#### the hybrid "hitech" problem

once the rigid substrate is detached, hybrid is very flexible and is not suitable for precision wirebonding to the Si hybrid conventional hybrid-flex ( adapted from ATLAS/ CMS trackers), see talk by S. Blusk, https://indico.cern.ch/getFile.py/access? contribId=8&resId=0&materialId=slides&confId=272144

now we agree that this will be our baseline solution

## balcony electronics

- Power distribution scheme needs more study

- Noted and being worked on

- Use of commercial electronics assessed against expected radiation level

- This is particularly relevant for FPGAs that are currently envisaged

- □ The main design choice in this system:

- In low occupancy regions many independent SALT chips are aggregated onto a single GBT link. The decoding of these independent data streams buried within GBTX frames require significant FPGA resources, the alternatives in front of us are either an increase in TELL40 # (\$\$ that we may not have) or to put more intelligence in the balcony electronics (radiation? Complexity in an area not easily accessible? Is it really cheaper?)

- The review committee notes that this is a critical design issue to address with high priority

- □ Mechanism to add extra-bits to BXID should be studied This is not a problem. We are not the only sub-detector to send only few BXID bits, and we expect that a common solution will be provided.

- □ TFC commands should be discussed and decision on necessary bits made. BX-Veto and Header Only are equivalent for the SALT. TFC commands are documented in <u>https://twiki.cern.ch/twiki/bin/view/LHCb/SiliconStripTracker#TFC\_commands</u>

- TFC fan-out? No fanout for the TFC signals is foreseen in the latest design. We will accommodate more master GBTx to provide each group of 4 ASICs with it's own TFC link.

- The current scenario assumes one 'TFC command bus " connected to 4 SALT ASICS. This should be investigated. Ongoing, several options being studied.

- Are configuration times acceptable? (ECS optimized for compactness) Each I2C bus (at 400KHz) will connect only 4 ASICS, and each ASIC needs 16Kbits to be configured. The full detector would need less than 100Mb to be configured, and this will be distributed among several SCA chips (there is 80Mb available to each SCA). At this point we consider this is not a problem.

- DCS should be designed to be independent of TFC. The system relies on the SOL40 and the GBTx-SCA. The communication between the SOL40 board and the GBT-SCA chips is the only requirement for the DCS to work. Thus it is independent from the TFC.

### MANPOWER, BUDGET, AND SCHEDULING

General remarks

- Schedule of this project is built around SALT development and production, arriving at a working chip is a high priority

- Budget implications (backup funds, ..)

- Manpower implication (r&D testing including radiation damage, wafer testing..)

- Overall management structure

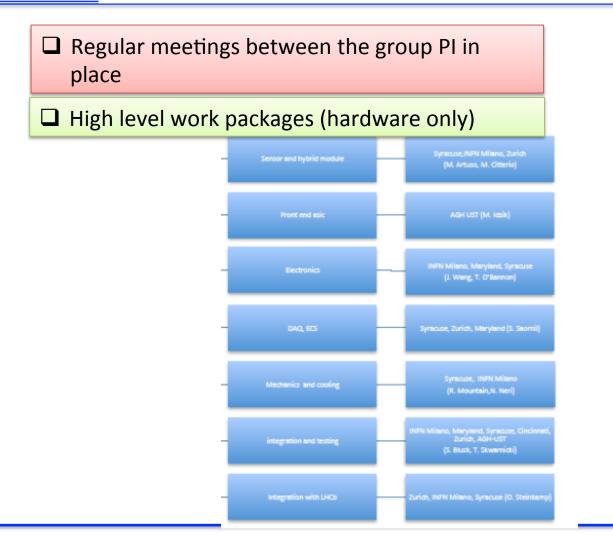

# **Management & Work packages**

### The electronics subprojects

## The DAQ subproject

#### DAQ (S.Saornil, Zurich)

#### Tell40 algorithm (J. Wang, Syracuse)

ECS/TFC (S. Saornil, Zurich)

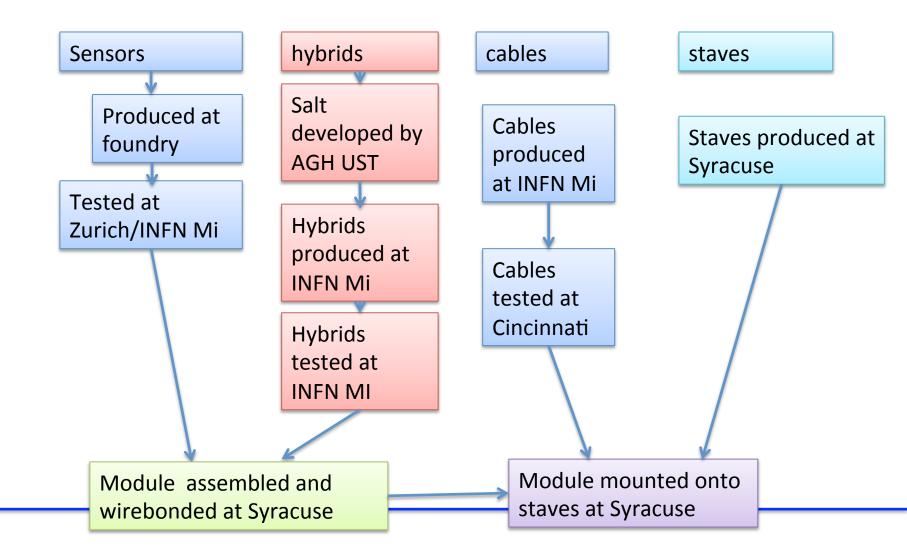

### Stave construction flow

## Milestones R&D

| Electronics<br>Layout<br>Sensor<br>Geometry                     | Finalize FE specification (process<br>block)<br>Decision on number of planes &<br>position<br>Finalize thickness &<br>segmentation<br>Input to workshop comparing<br>w/wo RICH1/B-field/BP options<br>Mockup of thermo-mechanical | May-13<br>May-13<br>Jun-13<br>Jun-13 | define<br>subtr<br>needs<br>docu | essing block alm<br>ed (pedestal<br>action, CMS,<br>s to be<br>mented) data<br>atting | nost |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------------------------------------------------------------|------|

| Infrastructure                                                  | sub-assembly; results                                                                                                                                                                                                             | Jul-13                               |                                  |                                                                                       |      |

| Electronics                                                     | Choice of power dist. DC-DC,<br>linear.                                                                                                                                                                                           | Aug-13                               | Aug-13 Shorter sensor,           |                                                                                       | sor, |

| Design                                                          | Inner sensor decision                                                                                                                                                                                                             | Oct-13                               | Oct-13                           |                                                                                       | ,    |

| Design                                                          | Design of single plane mechanics<br>completed                                                                                                                                                                                     | Oct-13                               |                                  |                                                                                       |      |

| Module                                                          | Production and QA procedures<br>defined and tested on a<br>demonstrator module                                                                                                                                                    | Oct-13                               | р                                | leed to<br>progress with                                                              | R    |

| Electronics                                                     | Validation FE-RO scheme                                                                                                                                                                                                           | Oct-13                               | h                                | ybrid and                                                                             |      |

| Electronics                                                     | Validation of power distribution scheme                                                                                                                                                                                           | Oct-13                               | (!                               | able design<br>schedule<br>djusted to                                                 |      |

| Detailed milestones for the project will be included in the TDR |                                                                                                                                                                                                                                   |                                      |                                  | ALT)                                                                                  |      |

### the end

#### backup slide with additional answers follows

#### Develop more detailed specifications for the SALT ASIC

We are engaged in a process with the SALT designers to agree upon specifications that give the desired performance without undue burden to the design. Analog/geometry/dsp specs done, now finalizing requirements on ECS/TFC and data formatting elements (e-ports)

#### Converge on final quantities of GBTX, VTTx/VTRx, ST linear regulators new deadline Jan. 31

We have a conservative part count which we are trying to trim down a bit to stay within budget.

#### □ Lots of items to be finalized⇒ meet on a regular basis

Electronics meetings at least weekly, sometimes more frequent if needed

# hybrids and cables other recommendations (noted & acted upon)

- proceed with actual electrical design and prototyping ASAP, with careful thought of

- power dissipation on power tape (and V drop because of ohmic losses)

- signal integrity on slvs lines

- grounding and shielding

- Remarks: system design to be optimized with consideration of:

- power requirements (see SALT design, reducing power requirements is VERY beneficial)

- signal integrity

- reduction in complexity