## ACCELERATOR CONTROL SYSTEMS

mark.plesko@cosylab.com

#### Glossary 1 - Networking

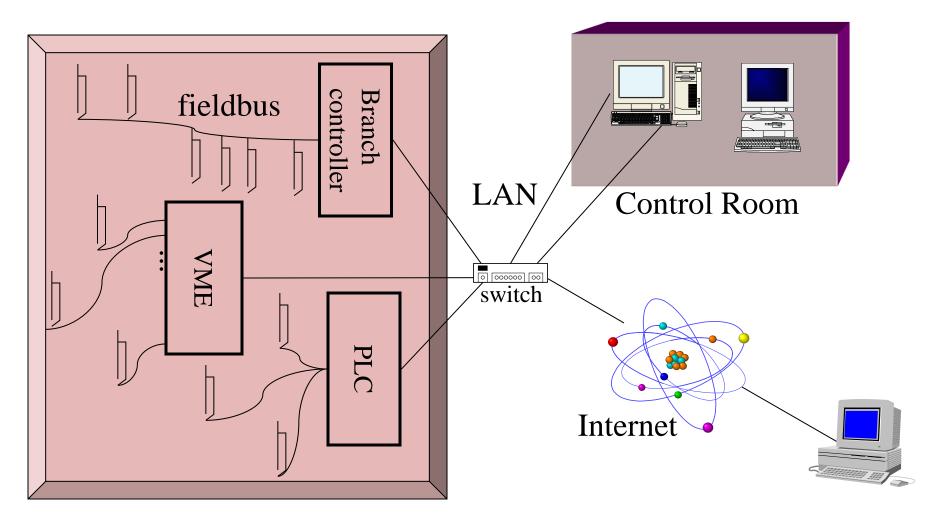

- LAN local area network: directly connected computers

- Ethernet physical (electric) communication

- TCP/IP how to send/receive and assemble small data packets over network, in LAN or Internet

- switch box which interconnects many computers

- fieldbus simple low-cost connection of many sensors to one CPU

#### **Glossary 2 - Electronics**

- I/O input/output: typical the place where digital data is transformed from/to something physical

- example: printer, disk, ADC, etc.

- ADC analog to digital conversion

DAC digital to analog conversion

- □ standard ranges +/-10V, +/-5V or 0-10V, 0-5V

- resolutions from 8 to 16 bits

- precision usually worse than resolution !

- Binary or digital I/O only two levels, for switches, etc.

- beware of different levels: TTL (5V), 24V

- open collector: the current for switching is not provided

#### **Glossary 3 - Interfaces**

interface - the agreed way how two different things fit together (hardware and software)

don't forget about the connector!

- RS-232 simple serial interface used in PC world GPIB - general purpose interface bus

- many commercial devices (even oscilloscopes) use one of these

- much work to interface, because software commands are not standardized - each device has own, often insufficiently documented

- API application programmer's interface: a set of library functions doing frequently needed actions

#### Glossary 4 - Hardware

- CPU central processing unit: heart of the computer, sometimes used for whole computer

- microcontroller microprocessor with integrated I/O

- FPGA Field Programmable Gate Array: millions of logic gates (AND, OR, etc.) that can be configured and connected with a "programming language" - VHDL

- DSP digital signal processor: specialized microcontroller doing fast Fourier and other transformations

- front-end: all that stands in front of the hardware

- VME standard format for I/O modules and processors

- PLC programmable logic controller: diskless microprocessor following simple logic instructions

- workstation high performance desktop computer

#### Glossary 5 - User Level COSYLAB

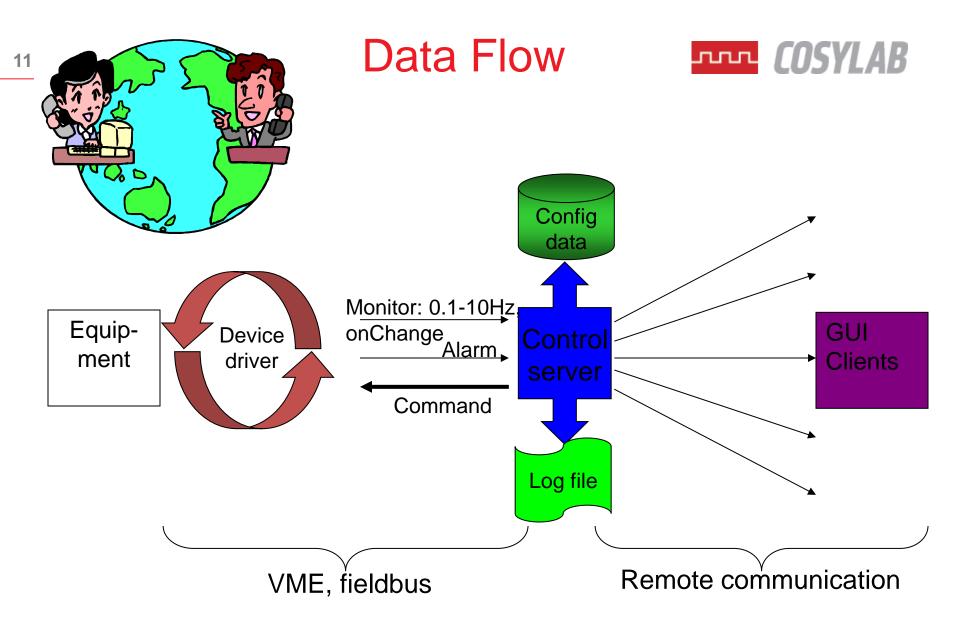

- GUI graphical user interface (buttons, menus)

- SCADA supervisory control and data acquisition: commercial CS, with GUI building tools and software bus

- database where data are stored and retrieved efficiently

- RDBMS relational database management system: a powerful database with data arranged in separate tables, linked by defining relations between columns

- SQL structured query language: the most common standardized language used to access databases.

- application one or more programs for a specific problem

- usually includes GUI for user interaction

### Glossary 6 - Programming m COSYLAB

- synchronous make request and wait for response

- asynchronous response comes later, independently

- polling periodic checking if response is ready

- callback a response sent asynchronously, interrupting the receiver

- scalability design how a CS is applied to large systems

- real-time a process must finish in a given time

- OO object oriented: programmer defines objects (structures) which exchange messages (function calls)

- very similar to "normal" way of thinking

- efficient approach for design, "software reuse" and upgrading

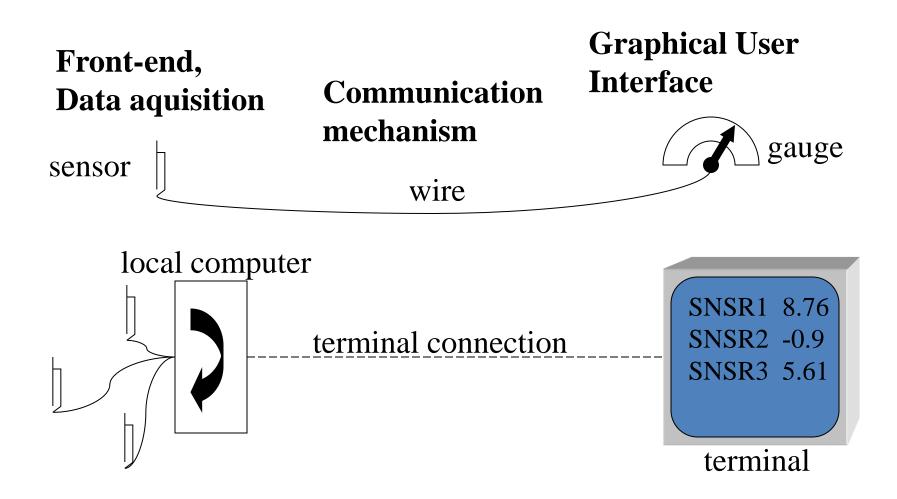

#### Let's first define what is a CS **COSYLAB**

- A tool that allows to operate the complexity of the accelerator from a single location

- Convert physical properties to electric (analog) signals

- convert analog signals to digital values

- transfer digital values over network

- Access remotely each single device

- Execute complex processes (injection, ramping, tuning, feedback systems, safety, etc.)

- Log and archive data, events, actions

- Allow physicists to "run" the accelerator with Matlab ③

#### From the Analog to the Digital... **COSYLAB**

####

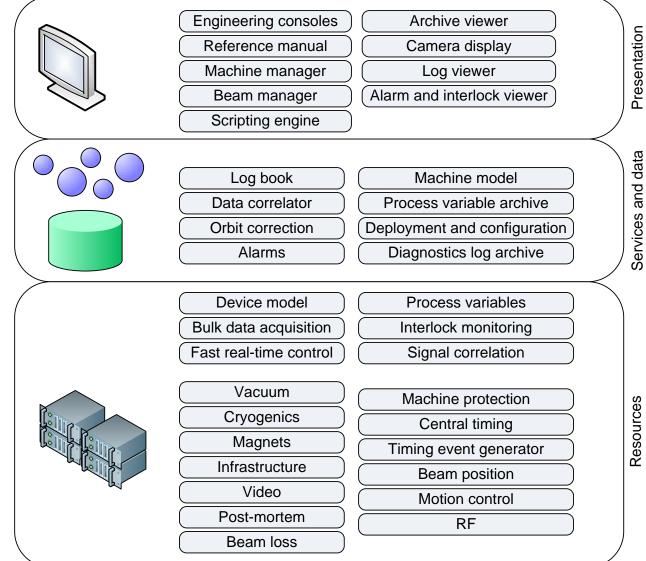

### COMPONENTS OF THE CONTROL SYSTEM

#### <sup>13</sup> Main CS Components

What has to be in real time?

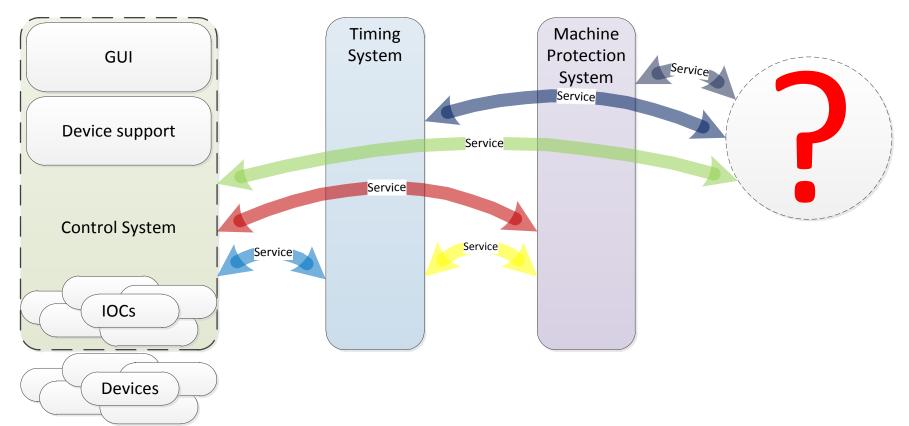

Interconnection of components and services

Which components are getting more important?

#### LHC MACHINE

#### Middleware or software bus

PURPOSE

NETWORK

TECHNICAL

GIGABIT

OPERATOR

CONSOLES

FILE SERVERS

RT Lynx/OS

OPTICAL

BEAM POSITION MONITORS.

BEAM LOSS MONITORS.

BEAM INTERLOCKS.

RE SYSTEMS. ETC.

VMÉ FRONT ENDS

- What is their purpose, are they really different

- Yes in terms of technical implementation

- Probably yes in terms of performance

- No in terms of what they provide for the CS

EPICS, CMW/FESA, TANGO, TINE, DOOCS, MADOCA,...

FIXED

DISPLAYS

APPLICATION SERVERS

WORLDFIP

Front Ends

SEGME1 Bits/sec)

2.5 MB

SENSORS

QUENCH PROTECTION AGENTS.

POWER CONVERTERS FUNCTIONS

GENERATORS, CRYO TEMPERATURE

nn COSYLAB

OPERATOR

CONSOLES

SCADA SERVERS

ACTUATORS AND SENSORS

CRYOGENICS, VACUUM, ETC.,

TIMING GENERATION

TCP/IP communication services

TCP/IP communication services

PLCs

TCP/IP communication services

RESOURCE TIER

RECTI/O

#### <sup>15</sup> Why is EPICS so popular?

- A very strong user and developer community

- A large number of supported devices, and a relatively small set of interfaces

- e.g. Universal motion control record

- Lightweight on dependencies

- Does not depend on relatively complex middleware

- few central services that would be singlepoints-of-failure.

#### Timing System

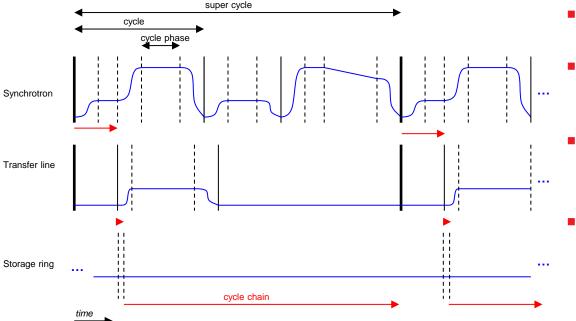

Graphical illustration of the concepts cycle phase, cycle, super cycle and cycle chain.

- Takes care of real-time (BTW, what is this?)

- Must be a common solution for the entire facility

- Should be one of the first systems to be completed

- Provides

- Triggers

- Delay generators

- Event distribution

- Time distribution

- Accuracy to within 1 us, 1ns and for FELs even to 10 fs !

#### What does timing system include?

- it's like an orchestra; ...the better in sync the better it sounds

- a conductor (=timing master) instructs

- performers (=timing receivers) to play out formerly agreed work

#### layers from <u>composer to performer</u>:

(super) cycle composer

- a high-level app for building table/s and play conditions defined by machine physics and beam requirements—and transforming into suitable format for (sw)

- timing-master real-time scheduler

- for priority scheduling of the events to be pushed through (HW-RT)

- timing master transmitter (нw-кт)

- transport layer

- for real-time distribution of events (also clock and possibly time) (HW-RT)

- timing receivers

- for real-time reaction to received events; providing host with triggers/IRQs, clock, and time (HW-RT)

#### Still Plenty of Work ...

- interface I/O boards to the devices

where to draw the line:ADC/DAC, serial/GPIB

- write low level device processing

drivers, filtering, state machine

- configure middle-ware database

name, type, properties (limits, conversion, updates, precision,...)

- make graphical user interface (GUI)

- Feedback systems separate communication, dedicated hardware

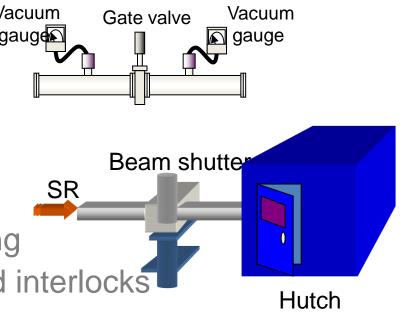

- Safety systems

equipment safety

interlocks

personal safety

- radiation monitoring

- access control and interlocks

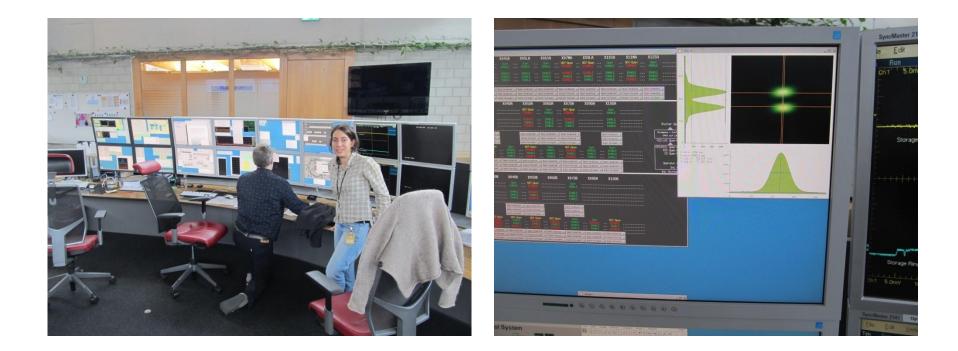

#### **20** Control Room For Display...

Success! Happy users. (above: first beam size measurements on new beamline)

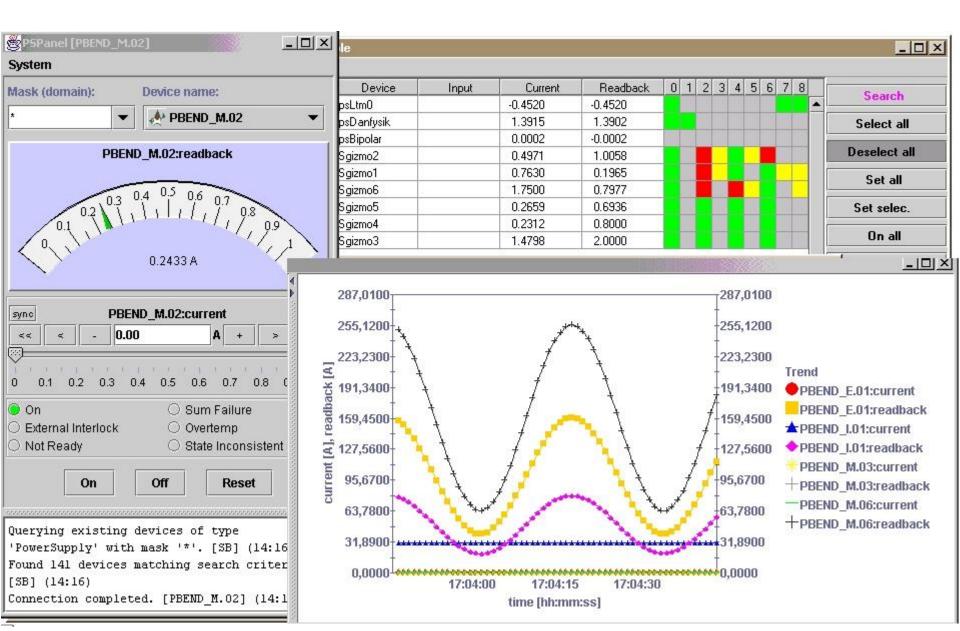

#### ... of Functional Panels...

21

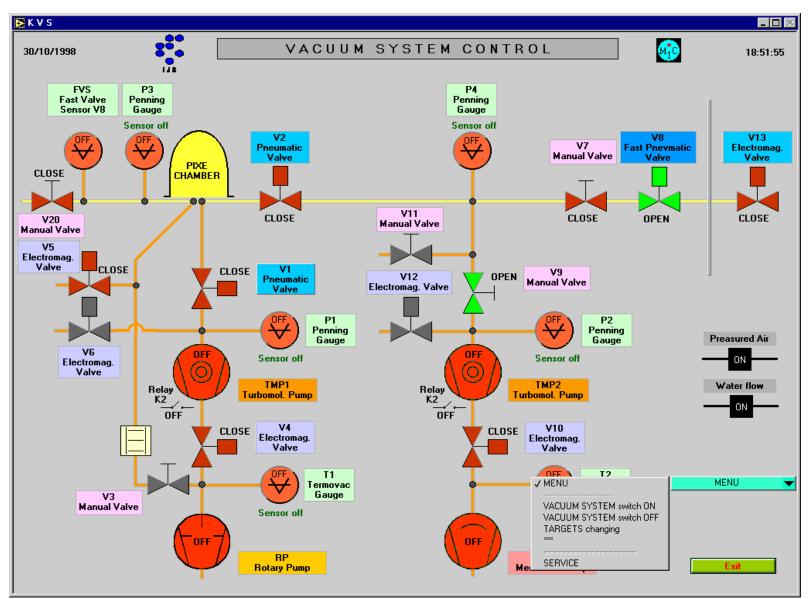

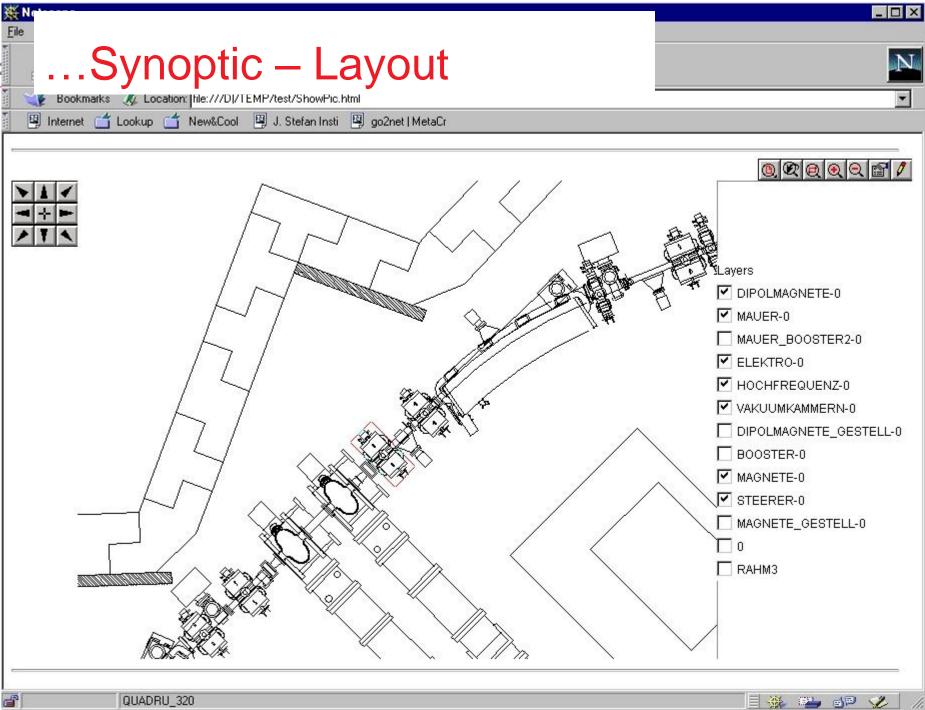

## ....Synoptic - Process Diagram...

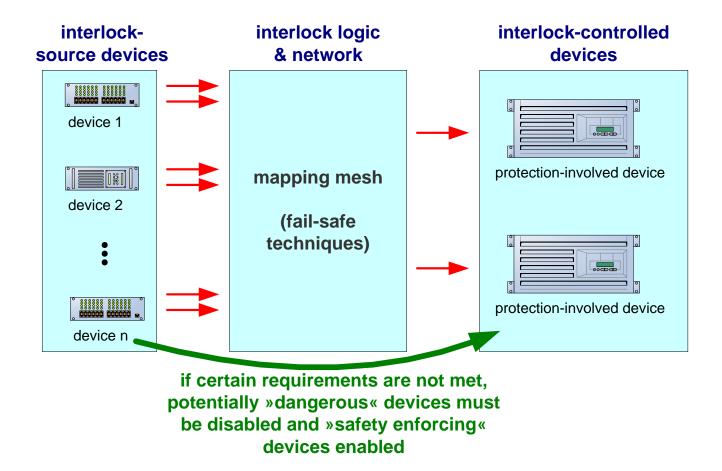

#### Machine Protection and Interlocks 1/2

Figure 20: From the protection system point of view there are two types of devices; interlock-source devices and interlock-controlled devices.

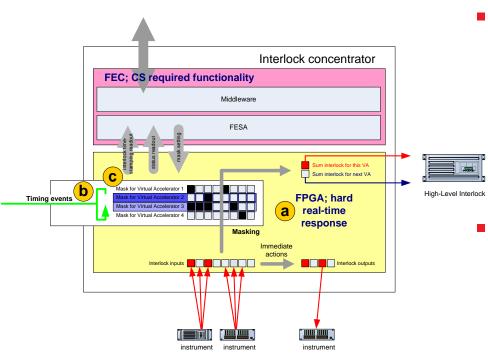

#### Machine Protection and Interlocks 2/2

Interlock concentrator schematic overview

# Balance between

- High Flexibility required: statespecific interlocks

- Includes complex FPGA logic

- ITER and ESS: interlock system is equally important as the main control system

## HARDWARE ISSUES (WHO CARES ABOUT THAT ANYWAY?)

#### VME, cPCI(e), PXI, xTCA (MTCA.4), etc.

Why don't all the labs make the same choice?

- Potential criteria for evaluation:

- Vendor support, maturity, longevity, maximum transfer rate, topology, form factor, availability, software support, user base, etc.

|                    | VME                                                                | ATCA                                                        | cPCI                                                   |

|--------------------|--------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| Vendor support     | High/Declining                                                     | Low/Growing                                                 | Medium/Stable                                          |

| Maturity           | High                                                               | Medium                                                      | High                                                   |

| Longevity          | Medium                                                             | High                                                        | High                                                   |

| Max. transfer rate | VME: 40MB/s<br>VME64: 80MB/s<br>VME64x: 160MB/s<br>VME320: 320MB/s | 1Gbps, 10Gbps<br>(Gigabit Ethernet);<br>250MB/s/lane (PCIe) | PCI: 133MB/s<br>PCIe: 250MB/s/lane<br>(up to 16 lanes) |

| Topology           | Master-slaves                                                      | Star<br>Dual star<br>Full mesh                              | Master-slaves                                          |

|                                    | VME                                             | ATCA                                    | cPCI                                                                   |

|------------------------------------|-------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|

| Form factor                        | 6U (64 bit)<br>3U (32 bit)                      | 12U (ATCA)<br>2U (μTCA)                 | 3U                                                                     |

| High availability                  | Medium                                          | High                                    | Medium                                                                 |

| Software support<br>(Linux, EPICS) | High                                            | Medium                                  | Medium                                                                 |

| Cost                               | High                                            | High                                    | Medium                                                                 |

| Users                              | SNS, SLS, Diamond<br>Light Source, NSLS II,<br> | XFEL (LLRF), ITER,<br>TPS (considering) | ALBA, TPS, CERN<br>(LHC collimation),<br>LANL, ORNL, ITER<br>(planned) |

- Main criteria for selecting hardware platform should be

- Usability

- Longevity

- NOT "top performance" or coolness factor

Acceptance by majority in the industry.

Jean-Francois Gournay (CEA) : stay with well-improved solutions as much as possible (we use the same analog IOs and binary IOs VME boards - still manufactured - for 20 years.

#### 33 Trendy and Sexy – the FPGA COSYLAB

- FPGA: Field Programmable Gate Array

- Integrated circuit designed to be configured by the customer <u>after</u> manufacturing

- "reduces hardware development to configuration"

- Obvious benefits

- Many inputs and outputs, parallel processing, full synchronization, real time, flexible,...

- Applications

- LLRF, MPS, timing,

DAQ,...

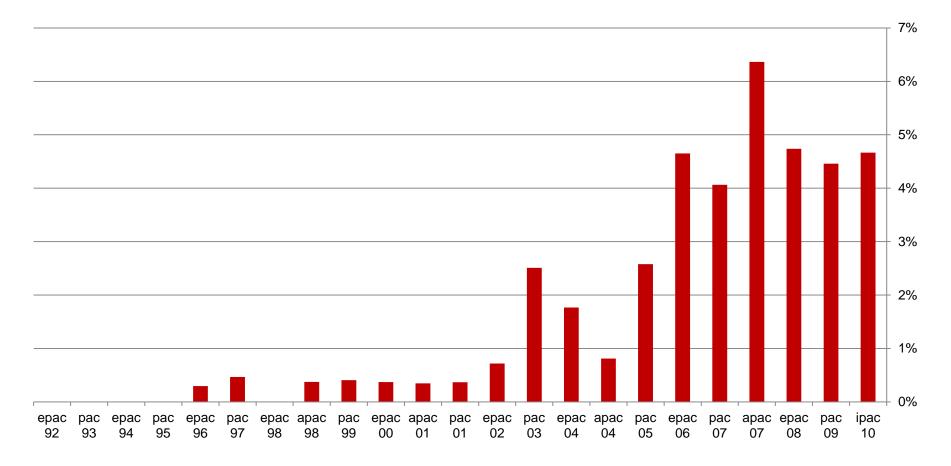

#### String "FPGA" in conference articles

Mastering complexity requires

<sup>35</sup> BRAIN power (more then CPU power)

- Advances in technology often give false sense of complexity reduction. Examples

- 1. FPGA development environment. For few 100 euros a PC card with free, well supported tools. Feels like an easy start, but it's a marginal win. True challenge is in domain expertise and system knowledge.

- 2. System 2.0 syndrome. With new tools and technologies, we'll fix ALL the shortcomings of the system 1.0 ... result: a proven, working system is replaced by an over-architected, heavy framework with late delivery.

- → Prudence, use of proven techniques

Elder Mathias (Canadian Light source) : *Be realistic on what is needed to commissioning the machine versus what is needed for optimal performance.*

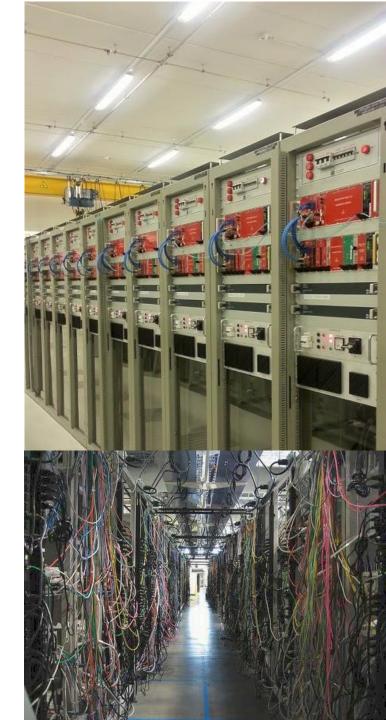

#### <sup>36</sup> Who Cares About Cables?

Always expect trouble! :)

- Devices not connected properly

- Cables not wired correctly

- SW not configured correctly

- GUIs need to be tweaked

- Users not trained enough (RTFM)

- Erroneous bug reports

- Integrators must be prepared for all of this

# CONTROL SYSTEM DEVELOPMENT

## Beside A Control System **COSYLAB**

- Control System (CS) is not a DVD with an installation wizard, but rather:

- Engineering according to specifications

- Configuration of packages like EPICS, TANGO, FESA, TINE, DOOCS, MADOCA, LabView...

- Outsourcing or in-house software and hardware development

- Installation

## <sup>39</sup> Role of CS in the project

- Relatively low technical risk

- Higher organizational risk

- Collaboration across all the departments

- Control system comes late in the project

- Integrates with most of other subsystems

- Control Systems are an engineering discipline like all the others, but with an even more complicated cycle

- Write specifications

- Architecture

- Design

- Prototyping fun part

- Test procedures

- Implementation (coding)

- Documentation

- Testing

- Debugging

- Acceptance

- Iterative development (evolution through upgrade phases)

# Teams and Division of Responsibility

Coordinators / **Storage Ring Booster** (expert) (expert) Liasons **Design team Diagnostics** Vacuum (External) project (External) project (for discussions) manager manager **Middleware** Hardware **FESA** Engineers Engineer Engineer Engineer

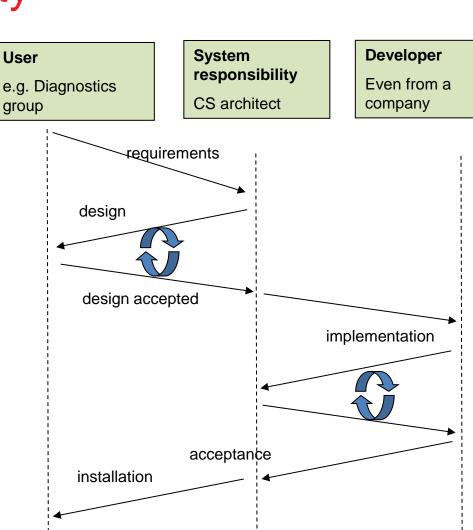

## Divide Work, but Maintain System Responsibility

- Define development procedures rigorously

- Divide the development among:

- Within CS group

- Other groups, experiments,...

- Outsourcing (companies)

- Use a <u>lightweight</u> project tracking and reporting tool

- CS group defines acceptance procedures

### Development process – our

- <sup>42</sup> experience from 100+ projects **COSYLAB**

- Start with requirements very early

- They will change later in any case, no matter how long you wait for the "final" requirements!

- Standardize development

- Applies to the whole cycle: design, implementation and testing procedure.

- More important than standardizing components.

Matt Bickley [JLab]: The aspect that I think has been most helpful has been standardization of hardware and software[...] Another decision was the choice to develop and rigorously adhere to standard testing and implementation procedures.

### Development process – our

- 43 experience from 100+ projects COSYLAB

- Vertical prototypes from the beginning

- With integrated software and hardware

- E.g. vertical column (MedAustron), Control Box (ESS), Fair Host Machine (GSI/FAIR),...

- Iterate frequently

- Yearly cycles

- First specific requirements usually come when people comment on the first prototype!

## 44 Define Systems and Interfaces COSYLAB

- List ALL needed services

- Define systems without duplicating services

- Understand connections between systems

- Define interfaces between systems

- All must agree on them early on in the project

## **FINAL THOUGHTS**

# Should we expect clear technological "winners"?

- Accelerator CS is a very broad field with specific needs for every job

- Timing needs

- Safety needs

- Reliability uptime needs

- Many installations are experimental by nature

Many arguments for very diverse approaches that blur the overall picture

- Computing power/\$ grows faster then project size

- Increasing expectations in power and flexibility of the CS

- Every added (cheap) CPU increases the entropy of the system

Increasing challenge of managing the added complexity

#### 47 Future challenges

- Large international projects with in-kind contributions: not technical, but managerial challenge.

- How can CS help

- How should we design the CS to solve these issues

#### 48 Conclusion

- CS has shifted over the years

- From research to engineering

- From performance to integration challenges

- But architecture and platforms are more or less stable

- So CS development task is how to integrate everything into the CS in-time, on-budget, and with a low-risk by using an increasingly large number of off-the-shelf components.

# **THANK YOU!**

Mark Plesko, mark.plesko@cosylab.com COSYLAB

Tel.: +386 41 934550

Web: www.cosylab.com