# The CMS HCAL FEE Control Module

S. Goadhouse<sup>a</sup>, T. Grassi<sup>b</sup>, T. O'Bannon<sup>b</sup>

(a) Univ. of Virginia, (b) Univ. of Maryland

# Introduction

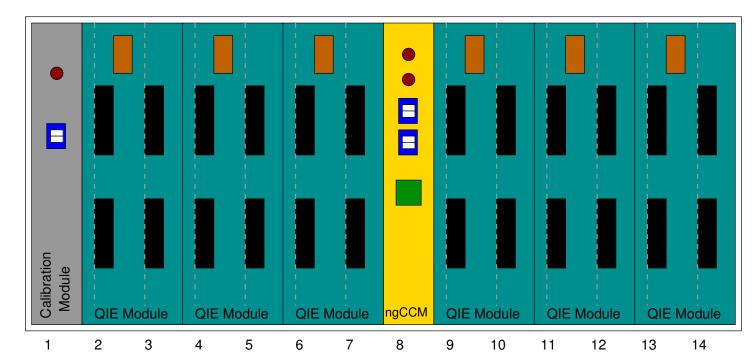

In the CMS Hadron Calorimeter, the Clock Control Module distributes the system clock to the readout modules and supports control and monitoring of the front-end electronics. In preparation for Phase 1 CMS Upgrades, a new prototype Clock Control Module, called the ngCCM, has been designed which uses the GigaBit Transceiver (GBT) transmission protocol over 4.8 Gbps optical fiber to connect to the counting room. Thus far, a prototype has been built and successfully integrated with other Forward HCAL prototype electronics for test beam studies.

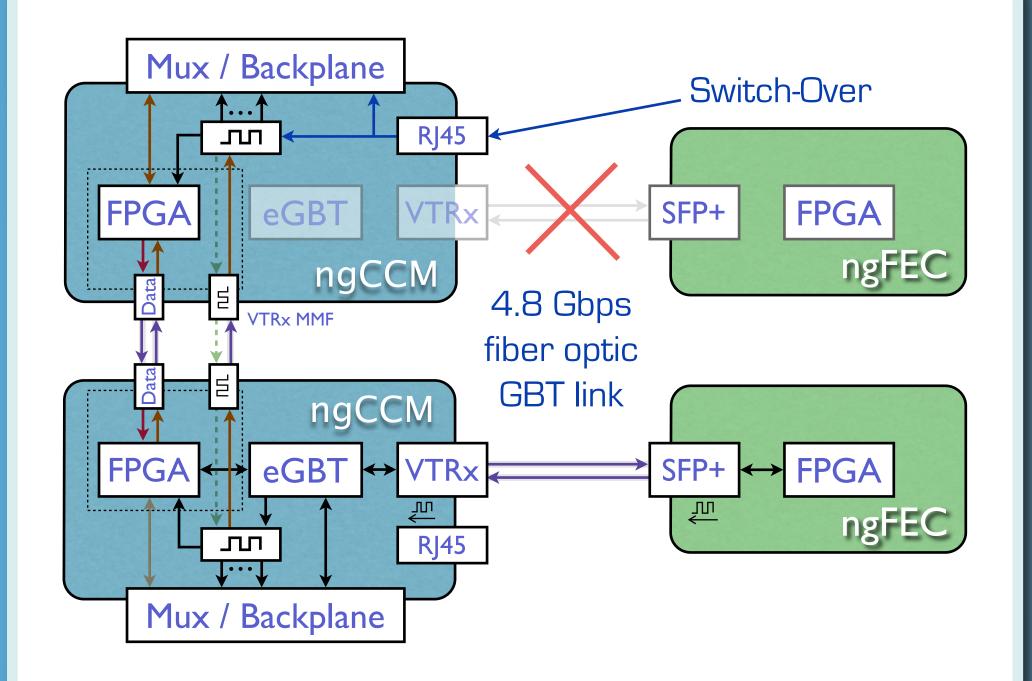

## Redundancy

In case of communications failure, the counting room can manually switch over a ngCCM so that it receives clock and control from its neighbor ngCCM. Clock is sent over one duplex optical fiber and an Igloo2 FPGA provides a reduced-function control path over another duplex fiber.

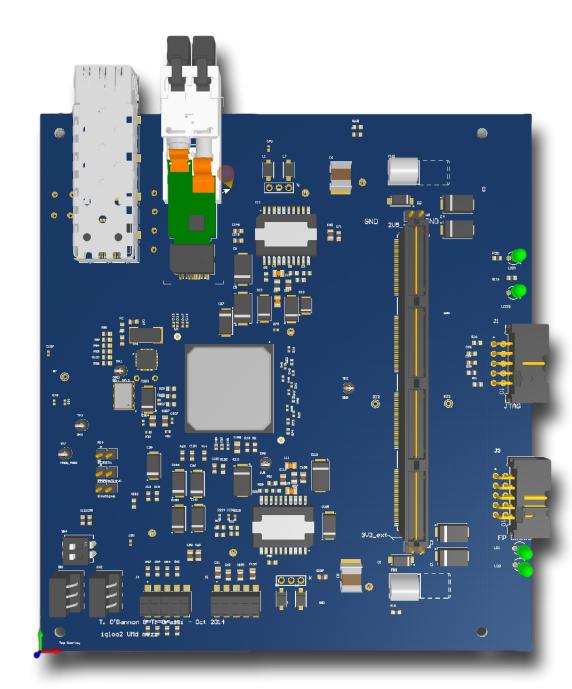

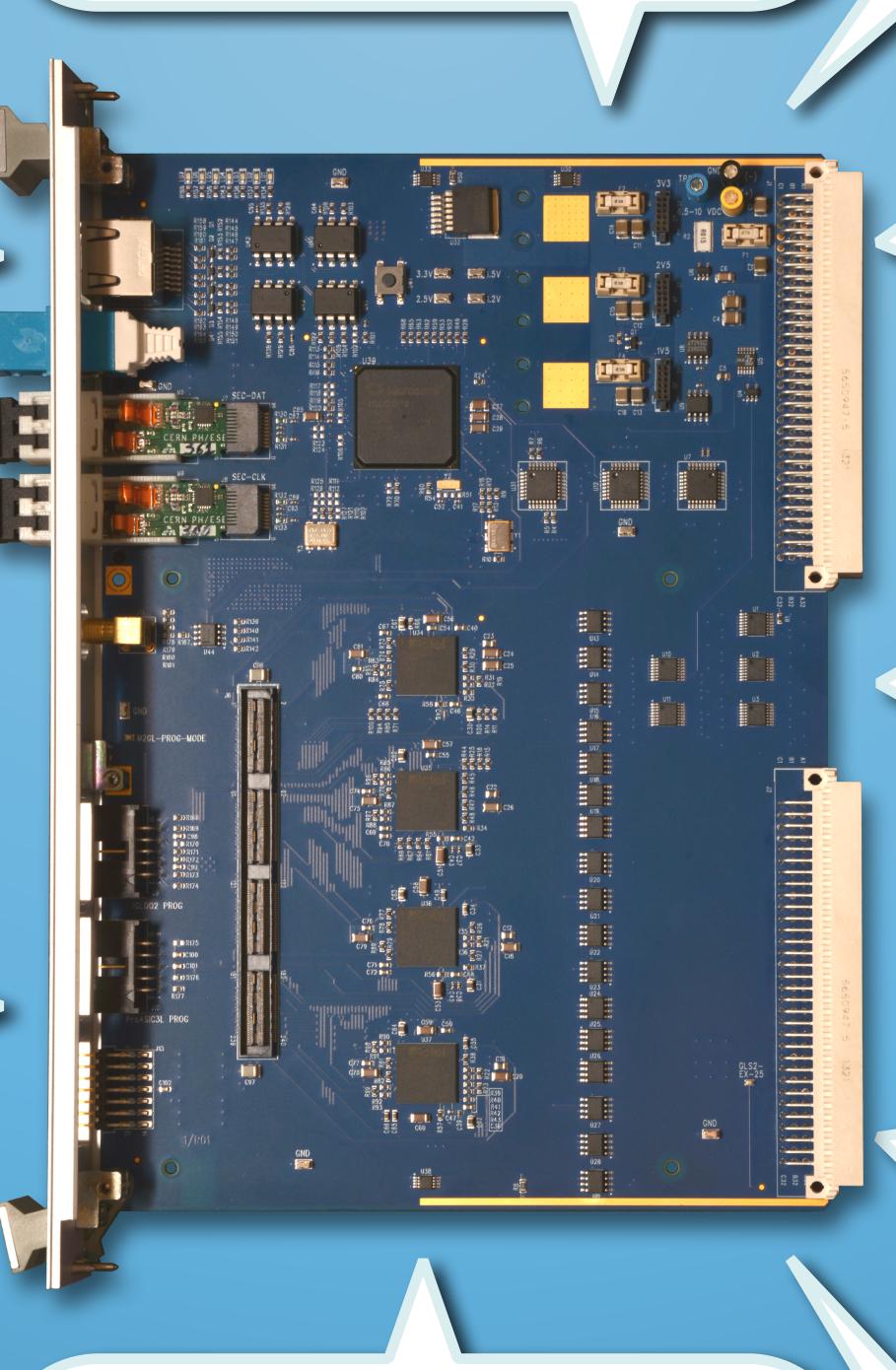

#### Mezzanine Board

Future Rad-tol Igloo2 Mezzanine

Primary Clock and Control are handled by an Igloo2 FPGA based mezzanine board which emulates the GBTx ASIC. A duplex optical fiber to a VTRx transceiver is used to supply clock and control and to receive status. The Igloo2 recovers the clock from the high-speed serial data stream before sending the clock to the motherboard for backplane distribution.

#### **Power Modules**

Three FEASTMP DC/DC Modules convert 6-11 VDC into 3.3 VDC, 2.5 VDC and 1.5 VDC while tolerating the high magnetic field environment.

# **Backplane Interface**

Four ProASIC3L FPGAs interface the control LVDS signals from the mezzanine to the backplane and they handle multiplexing signals with the redundant control path.

Other useful functions include an I<sup>2</sup>C-to-1 wire bridge which allows 1-wire temperature sensors to be read using I<sup>2</sup>C-over-GBT.

#### **6U/6HP Eurocard Board**

Planned Backplane Configuration from the TDR

# **Backplane Signals**

LVPECL Master Clocks, Reset, BC0, WTE LVPECL / LVTTL I<sup>2</sup>C LVTTL Power Enable

#### Radiation

The design primarily uses commercial components, which are known to have passed radiation tests at or beyond the expected 10 krad environment.

Additionally, the board contains a current threshold latch-up circuit which can automatically cycle power if needed.

## Remote FPGA Update

Using our JTAG-over-GBT design, most FPGAs in the front-end can be remotely reprogrammed.

#### I<sup>2</sup>C-over-GBT

Slow control in the front-end travels over a modified I<sup>2</sup>C bus. The ngCCM provides a conduit for I<sup>2</sup>C over the high-speed GBT link using I<sup>2</sup>C-over-GBT, which was developed specifically for the ngCCM.