# BL-TMR AND MITIGATION APPROACHES FOR FPGAS

Mike Wirthlin BYU

### 1. TMR Overview

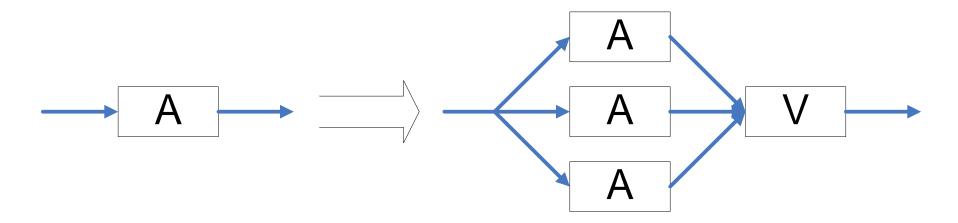

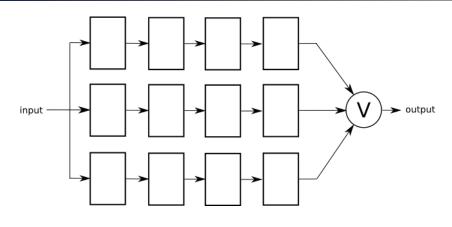

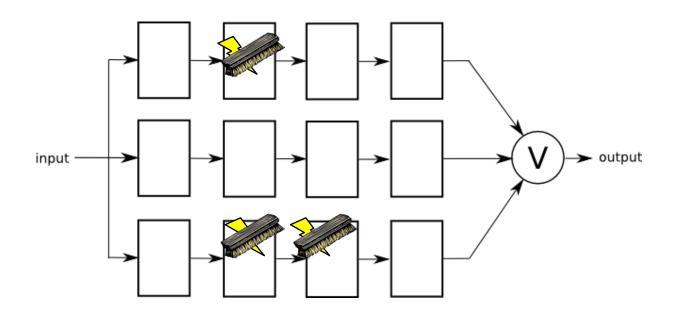

### Triple Modular Redundancy (TMR)

- A form of N Modular Redundancy

- Triplicate hardware resources

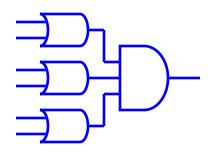

- Majority Vote on hardware outputs

- Tolerates any single fault

- Tolerates many multiple fault combinations

### TMR Granularity

Module Level

**RTL Level**

Logic Level

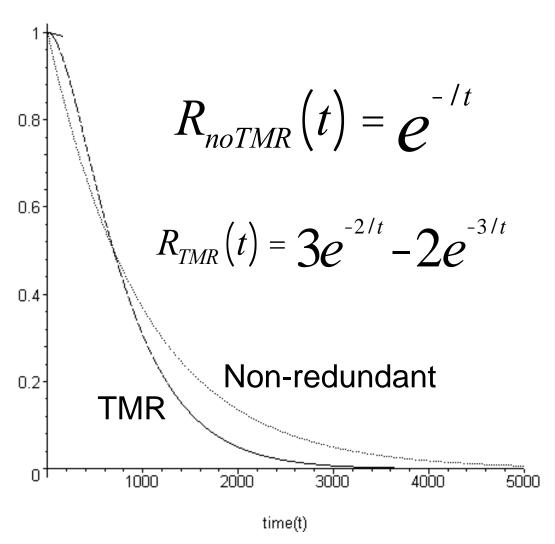

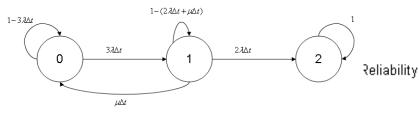

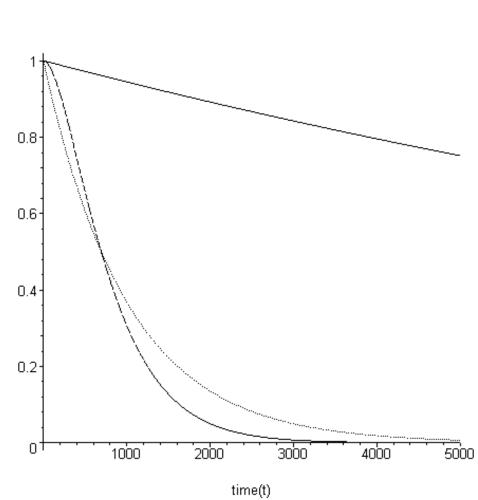

## TMR Reliability

TMR has lower reliability than nonredundant for long mission times

Reliability

Effective TMR almost always is coupled with "repair"

### TMR + Repair = Very Reliable!

$$R(t) = 1 - p_2(t)$$

(44)

=

$$\frac{(\mu + 5\lambda)\sinh(\frac{1}{2}t\sqrt{\mu^2 + 10\lambda\mu + \lambda^2})e^{-\frac{1}{2}(\mu + 5\lambda)t}}{\sqrt{\mu^2 + 10\lambda\mu + \lambda^2}}$$

+

$$\cosh(\frac{1}{2}t\sqrt{\mu^2 + 10\lambda\mu + \lambda^2})e^{-\frac{1}{2}(\mu + 5\lambda)t}$$

(45)

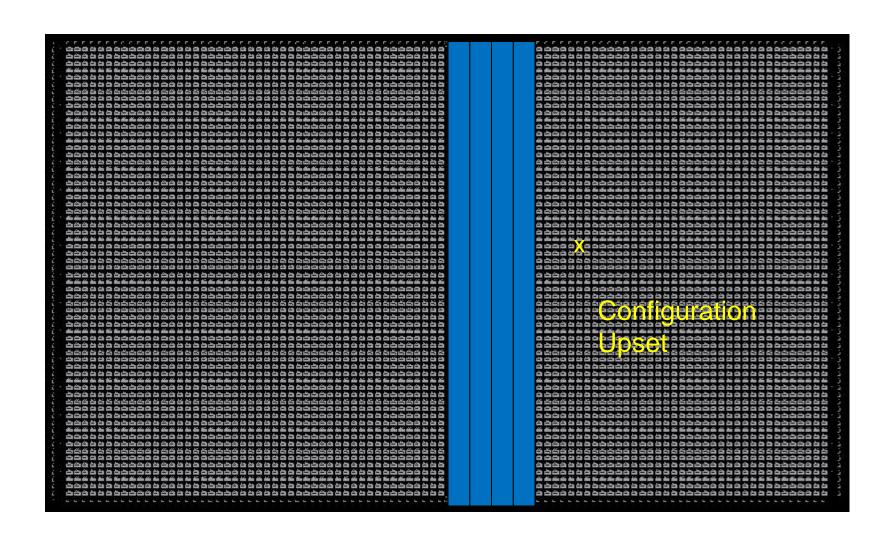

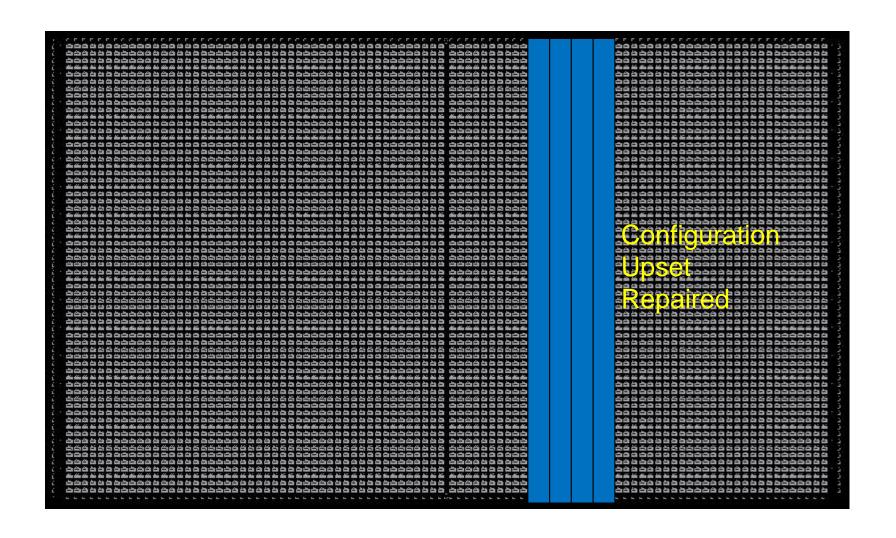

### FPGA Configuration "Repair"

### FPGA Configuration "Repair"

## TMR & Scrubbing Example

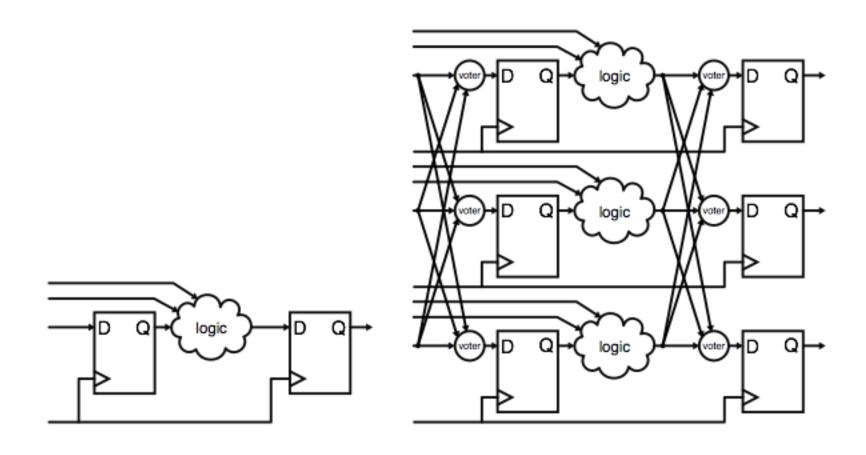

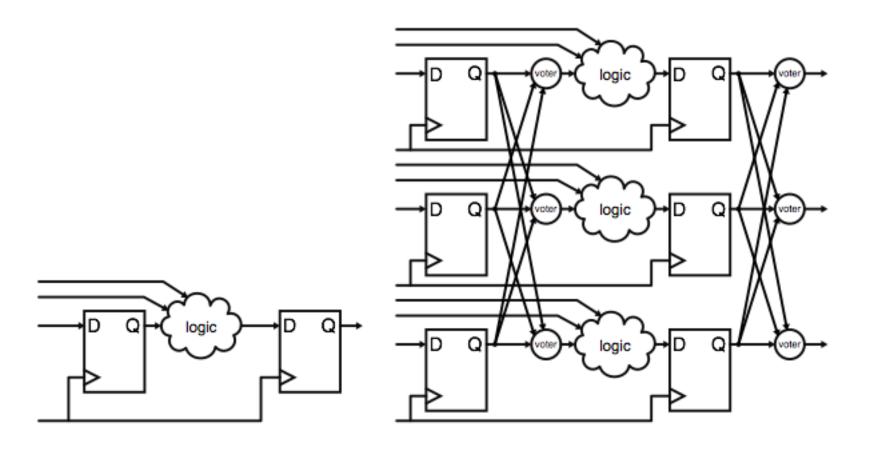

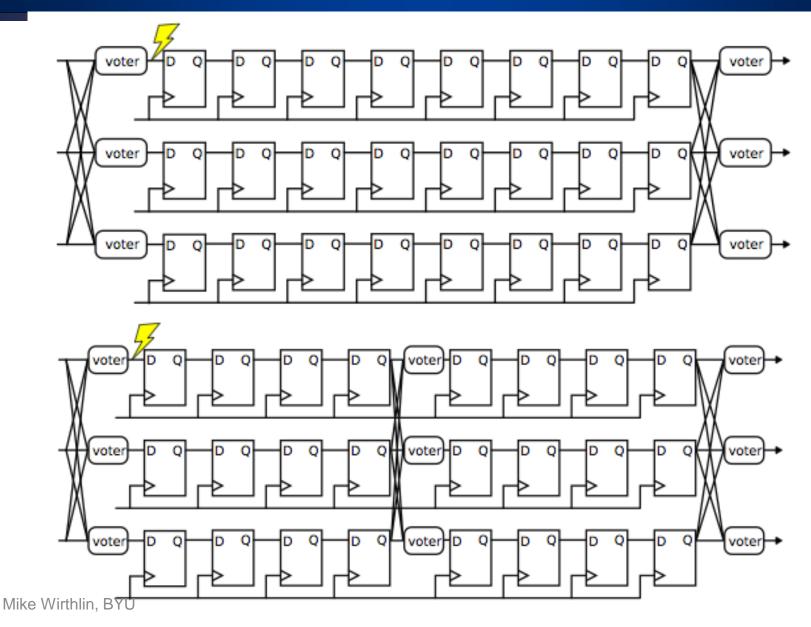

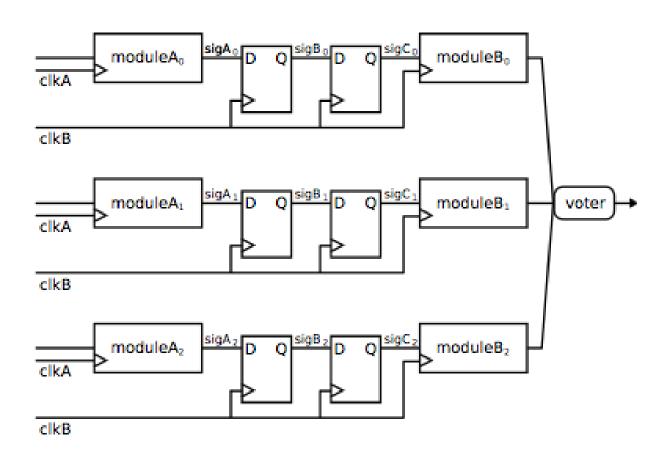

## Voters Before Flip Flops

## Voters After Flip-Flops

## More Frequent Voting

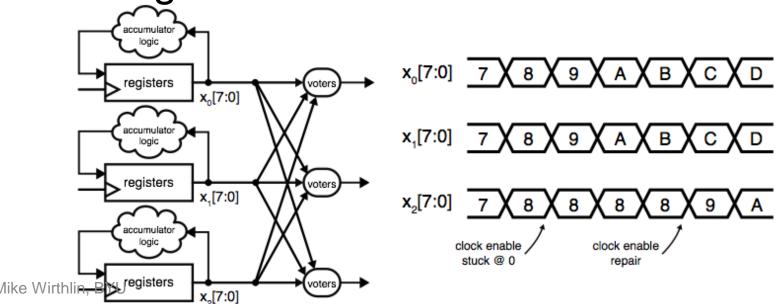

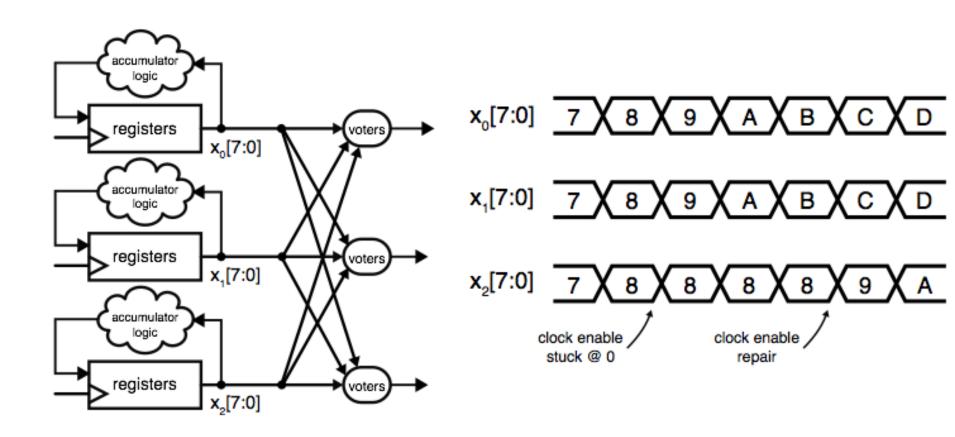

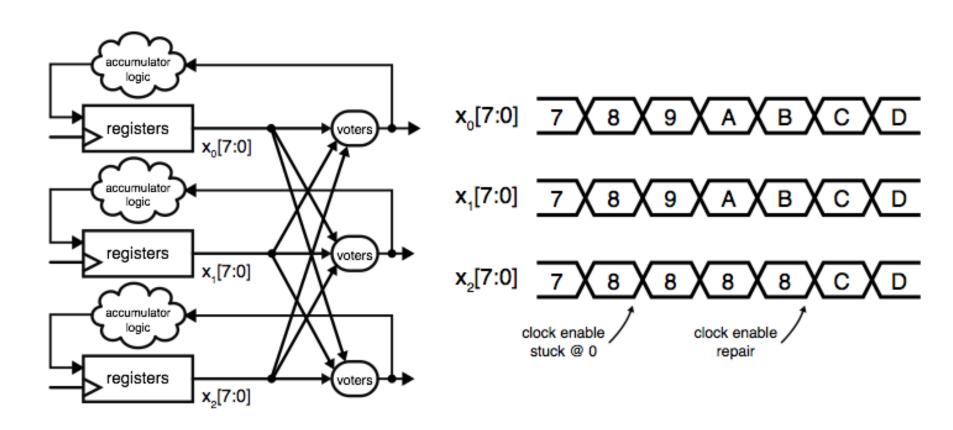

### TMR Synchronization

- Fault repair through scrubbing

- Fixes the cause of the error

- Does NOT fix the state of the circuit

- State of circuit must be synchronized to working circuits

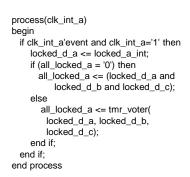

## Synchronizing Voters

## Synchronizing Voters

## Clock Domain Crossing

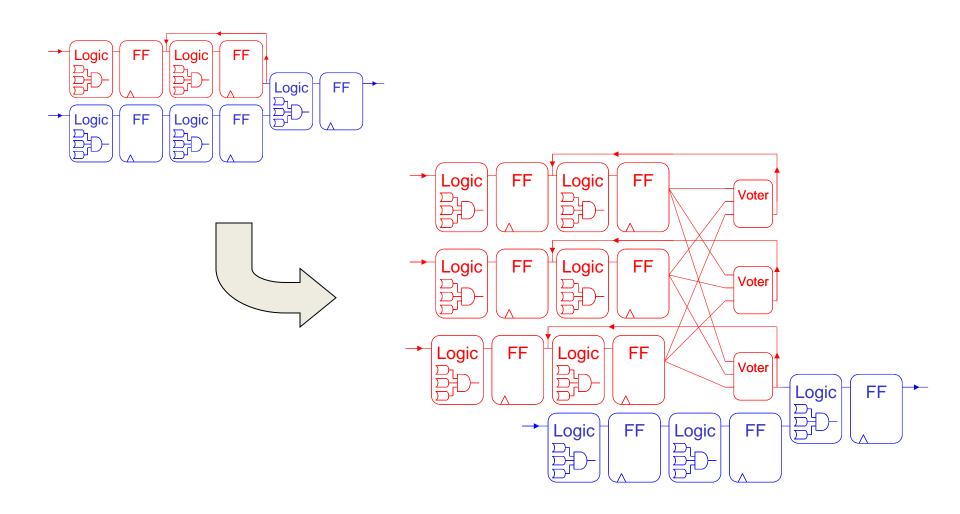

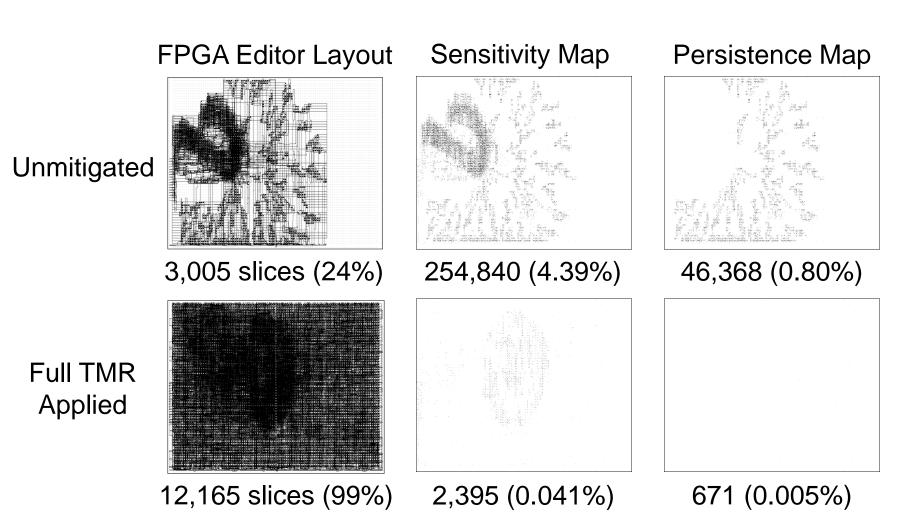

### **Partial TMR**

- TMR may be applied selectively

- Failures in some circuit areas cause more harm than others

- Some circuit areas are protected by other

SEE mitigation techniques (TMR not needed)

- Challenge: deciding where to apply TMR

- Circuits with feedback (state machines)

- Circuits with high "functional influence"

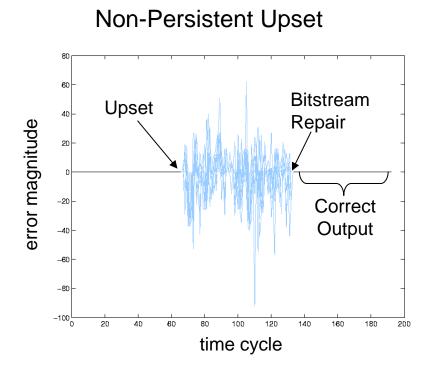

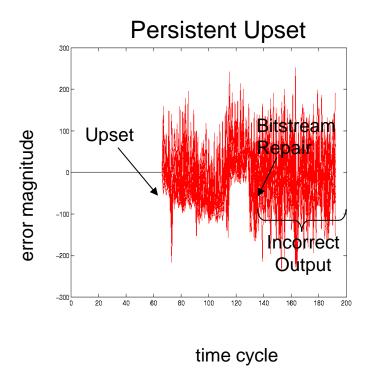

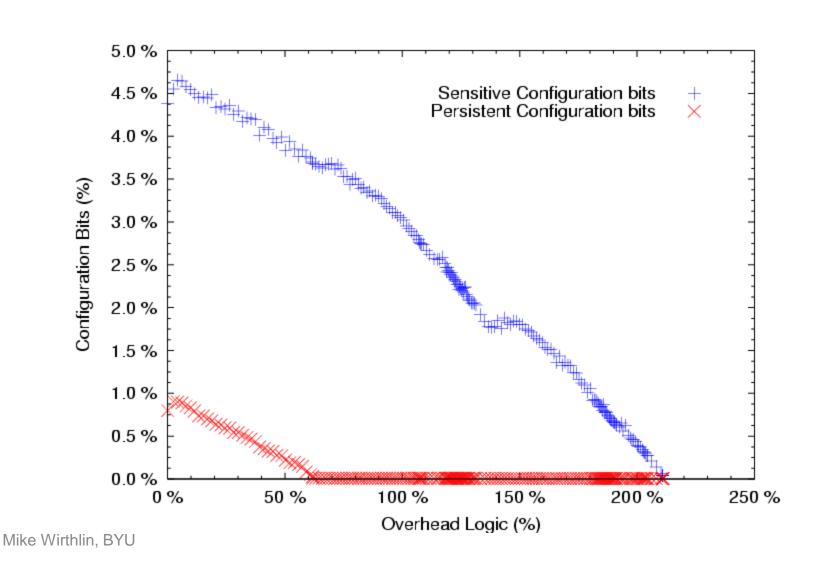

### Persistent vs. Non-persistent Upset

- Some upsets repaired through scrubbing

- Non-persistent upsets: repairable through scrubbing

- Persistent upsets: requires reconfiguration

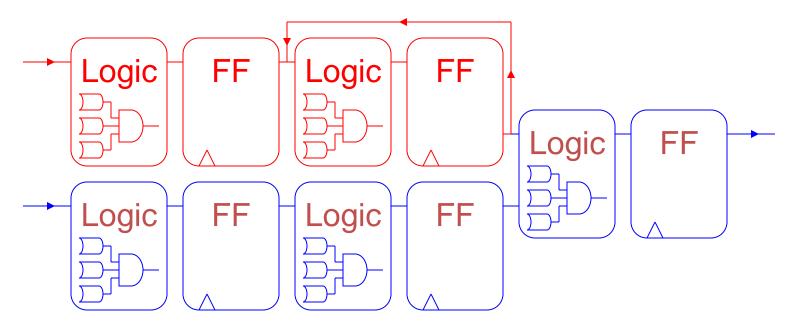

### Persistent Circuit Structures

- Non-Persistent Structure Feed-forward

- Persistent Structures Contribute to feedback

- Partial TMR Priority given to persistent structures

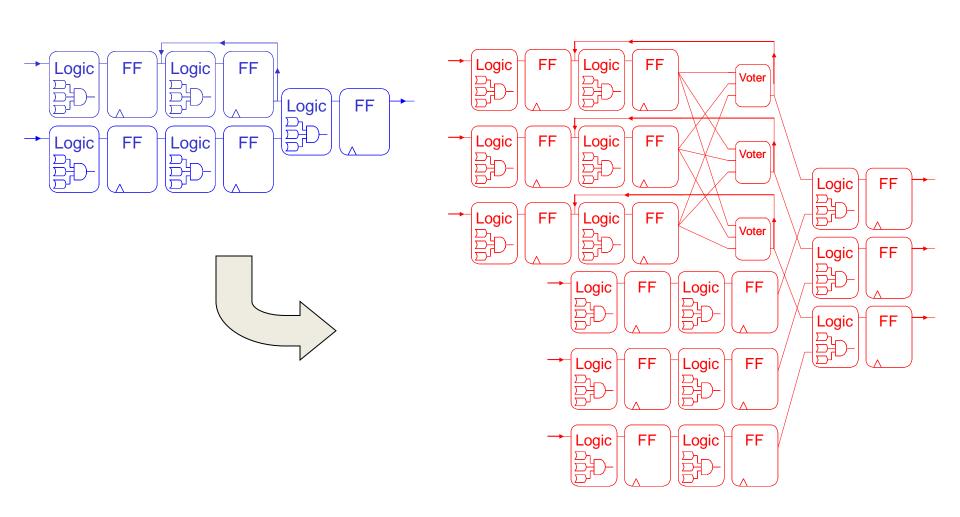

### Full TMR

## Partial TMR

### TMR Automation

- TMR is relatively easy to automate

- Analyze design

- Replicate resources

- Insert voters

- Verify resulting circuit

- Different Strategies for Automated TMR

- Netlist level

- HDL Level

- Selective/Partial

- Several tools available for Automatic TMR

### **Automated TMR Tools**

### **TMRTool**

**BL-TMR**

(and other several other academic projects)

### 2. BL-TMR

### **BL-TMR**

- BYU-LANL TMR Tool

- <u>BYU-LANL Triple Modular Redundancy</u>

- Developed at BYU under the support of Lands National Laboratory (Cibola Flight Experiment)

- Used to test TMR on many designs

- Fault injection, Radiation testing, in Orbit

- Testbed for experimenting with various application techniques (used for research)

### Ongoing Development

- Based on the success of BL-TMR, additional funding has been provided to extend BL-TMR for additional devices, environments, and address new problems

- Commercial companies concerned about SER rates

- Cisco Systems

- High Energy Physics

- Brookhaven National Laboratory (BNL), CERN

- Space system developers

- SEAKR systems, Sandia, LANL, Lockheed Martin

- Interest in BL-TMR is growing

- Commercialization currently under consideration

### BL-TMR (BYU/LANL TMR)

#### EDIF data structure & API

Parse, represent, and manipulate EDIF

#### Available tools:

- EDIF parser

- Half-latch removal

- SRL replacement

- Feedback cutset tool

- Full and partial TMR

- Detection circuitry insertion

- EDIF output

#### Project size

- ~50 Java packages

- 350+ Java classes

- 478,401 lines of code

- Includes contributions from CHREC member LANL

```

[brian@tiger:test] java -cp ~/jars/BLTmr.jar

byucc.edif.tools.tmr.FlattenTMR ../no tmr/synth/counters80.edf --

removeHL --full tmr --technology virtex -p xcv1000fg680 --log

counters80.log

BLTmr Tool version 0.2.3, 12 Oct 2006

Search for EDIF files in these directories: [.]

Parsing file ../no tmr/synth/counters80.edf

Removing half-latches...

Flattening

Flattened circuit contains 3451 primitives, 3461

nets, and 13692 net connections

Processing: ASUF 1.0

Forcing triplication of instance safeConstantCell zero

Analyzing design . . .

Full TMR requested.

Triplicating design . . .

domainreport=BLTmr domain report.txt

Added 1931 voters.

3431 instances out of 3451 cells triplicated (99%

coverage)

6862 new instances added to design.

3431 nets triplicated (6862 new nets added).

0 ports triplicated.

```

### **BL-TMR User Control**

- Provides significant control to user

- Can be scripted for complex BL-TMR runs

```

Usage:

java byucc.edif.tools.tmr.FlattenTMR <input file>

[(-o|--output) <output file>]

[(-d|--dir) dir1, dir2,..., dirN ]

[(-f|--file) file1, file2,..., fileN ]

[--tmrSuffix suffix1, suffix2,..., suffixN ]

[--full tmr]

[--tmr inports]

[--tmr outports]

[--no tmr p port1, port2, ..., portN ]

[--tmr c cell type1,cell type2,...,cell typeN ]

[--tmr i cell instance1, cell instance2, ..., cell instanceN ]

[--no tmr c cell type1,cell type2,...,cell_typeN ]

[--no tmr i cell instance1, cell instance2, ..., cell instanceN ]

[--notmrFeedback]

[--notmrInputToFeedback]

[--notmrFeedBackOutput]

[--notmrFeedForward]

[--noInoutCheck]

[--SCCSortType <{1|2|3}>]

[--doSCCDecomposition]

[--inputAdditionType <{1|2|3}>]

[--outputAdditionType <{1|2|3}>]

[--mergeFactor <mergeFactor>]

[--optimizationFactor <optimizationFactor>]

[--factorType <{DUF|UEF|ASUF}>]

[--factorValue <factorValue>]

[--low <low>]

[--high <high>]

[--inc <inc>]

[--removeHL]

[--hlConst <{0|1}>]

[--hlUsePort <hlPortName>]

[--technology <{virtex|virtex2}>]

[(-p|--part) <part>]

[--summary]

[--log <logfile>]

[--domainReport <domainReport>]

[--writeConfig[:<config file>]]

[-h|--help]

[-v|--version]

```

For detailed usage, try `--help'

### Sample Execution

```

[brian@tiger:test] java -cp ~/jars/BLTmr.jar byucc.edif.tools.tmr.FlattenTMR

../no tmr/synth/counters80.edf --removeHL --full tmr --technology virtex -p xcv1000fg680

--log counters80.log

BLTmr Tool version 0.2.3, 12 Oct 2006

Search for EDIF files in these directories: [.]

Parsing file ../no tmr/synth/counters80.edf

Removing half-latches...

Flattening

Flattened circuit contains 3451 primitives, 3461 nets, and 13692 net

connections

Processing: ASUF 1.0

Forcing triplication of instance safeConstantCell zero

Analyzing design . . .

Full TMR requested.

Triplicating design . . .

domainreport=BLTmr domain report.txt

Added 1931 voters.

3431 instances out of 3451 cells triplicated (99% coverage)

6862 new instances added to design.

3431 nets triplicated (6862 new nets added).

0 ports triplicated.

```

## Cost of TMR

|                                | Size Increase | Critical Path<br>Before TMR | Critical Path<br>After TMR | % Increase in<br>Critical Path |

|--------------------------------|---------------|-----------------------------|----------------------------|--------------------------------|

| blowfish                       | 3.1X          | 28.3 ns                     | 31.7 ns                    | 12.0%                          |

| des3                           | 3.4X          | 11.1 ns                     | 13.6 ns                    | 22.5%                          |

| qpsk                           | 3.1X          | 80.0 ns                     | 83.9 ns                    | 4.9%                           |

| free6502                       | 3.3X          | 29.6 ns                     | 33.1 ns                    | 11.8%                          |

| T80                            | 3.3X          | 27.8 ns                     | 33.7 ns                    | 21.2%                          |

| macfir                         | 3.9X          | 14.4 ns                     | 19.5 ns                    | 35.4%                          |

| serial_divide                  | 4.1X          | 9.2 ns                      | 12.2 ns                    | 32.6%                          |

| planet                         | 3.1X          | 10.9 ns                     | 12.6 ns                    | 15.6%                          |

| s1488                          | 3.1X          | 9.9 ns                      | 12.0 ns                    | 21.2%                          |

| s1494                          | 3.1X          | 10.4 ns                     | 12.2 ns                    | 17.3%                          |

| s298                           | 3.1X          | 15.8 ns                     | 19.1 ns                    | 20.9%                          |

| tbk                            | 3.9X          | 10.3 ns                     | 12.9 ns                    | 25.2%                          |

| synthetic                      | 4.0X          | 9.9 ns                      | 10.4 ns                    | 5.1%                           |

| Ifsrs                          | 6.3X          | 9.0 ns                      | 12.7 ns                    | 41.1%                          |

| ssra_core                      | 3.5X          | 6.1 ns                      | 7.2 ns                     | 18.0%                          |

| <b>mean</b><br>e Wirthlin, BYU | 3.6X          | 8.17 ns                     | 12.08 ns                   | 16.0%                          |

### **BL-TMR Incremental Results**

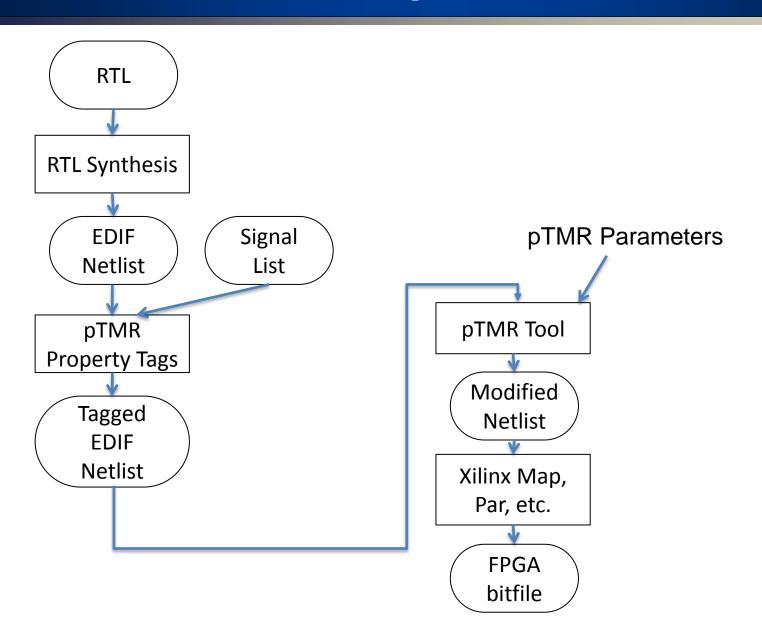

## 3. Design Flow

## Design Flow

### pTMR Steps

- 1. Component Merging

- 2. Design Flattening

- 3. Graph Creation and Analysis

- 4. IOB Analysis

- 5. Clock Domain Analysis

- Instance Removal

- 7. Feedback Analysis

- 8. Illegal Crossing identification

- 9. TMR Prioritization & Selection

- 10. Voter Selection

- 11. Netlist generation

### 11. Netlist Generation

- Circuit generated from pTMR rules

- Cells triplicated

- Voters inserted

- Netlist created for new circuit

## 3. Verifying BL-TMR

### Fault Injection

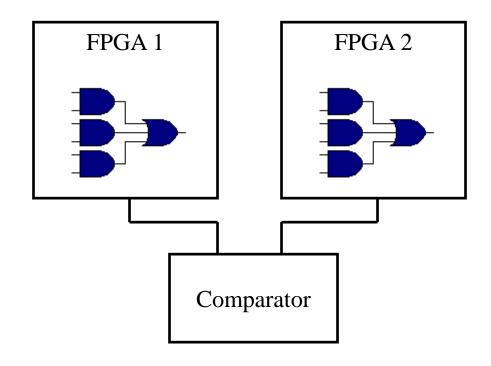

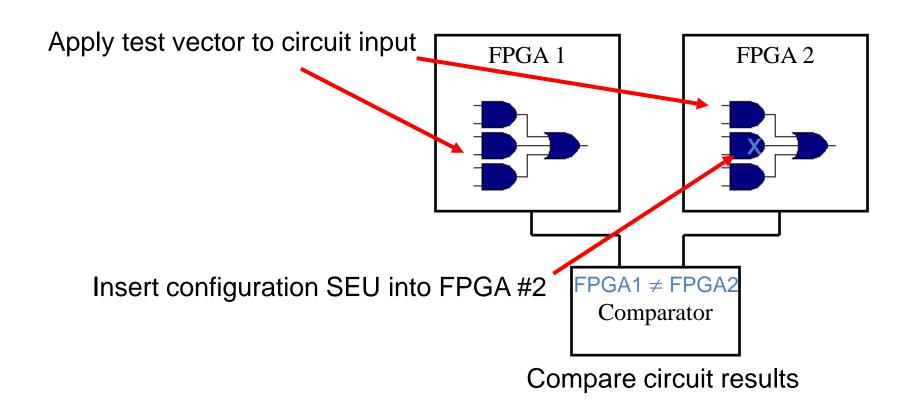

- Configure user design onto two identical FPGAs

- Compare results of two designs using Comparator FPGA

- Insert configuration SEUs into design under test (FPGA2) and compare results

- If discrepancies between FPGAs are found, record configuration error

## SEU Insertion Example #1

### Experimental Results – Design #2

### LANL Cibola Flight Experiment

- Los Alamos National Laboratory technology pathfinder

- validate FPGAs for high performance computing

- Investigate SEU behavior of Xilinx Virtex FPGAs

- Several BYU experiments validated in orbit

- TMR (including BL-TMR tool)

- Duplication with Compare

- DRAM controllers

Mike Wirthlin, BYU

Cibola Flight Experiment 560 km, 35.4° inclination

### Sandia MISSE-8

#### Under *direction* of Sandia National Laboratory

### BYU Experiments on ISS

- TMR PicoBlaze (Successful mitigation event!)

- Smart signal detection

- Reduced Precision Redundancy

- BRAM Scrubbing & BRAM ECC

Photo courtesy of Sandia National Labs

V4 FX60

Photo courtesy of NASA

Endeavor (STS-134) May 16, 2012

Photo courtesy of NASA

### Radiation Testing

- Apply Ionizing Radiation to Design with TMR

- Verify accuracy of artificial simulator

- Identify upset in non-configuration state

- Identify other failure modes

## UC Davis, Crocker Nuclear Laboratory

- Medium-energy particle accelerator (76-inch cyclotron)

- 63 MeV proton source

- □ Flux: 1e7

particles/cm²/second: (~1

upset/second)

- 16 hour test (~25,000 upsets)

### 5. TMR Summary

#### Pros:

- Significant improvements in reliability

- Easy to apply (limited design effort)

- Can be applied selectively

#### Cons

- Requires significant hardware resources

- Negative impact on timing

- Difficult to verify

### Alternatives to TMR

- Exploit specific circuit structures/styles

- Memories, state machines, processors, etc.

- Arithmetic structures

- Detection+

- Detecting a fault quickly opens up many lower cost mitigation strategies

- Temporal Redundancy

- Duplication with Compare

### **Future Plans**

- Clock domain aware TMR

- Timing aware TMR

- Improved support for clock and I/O resources

- Integrated Duplication with Compare (DWC)

- More frequent voting

- NMR (5-MR, 7-MR, etc.)

- Support for New FPGA Architectures

- Improved verification (formal verification)

- GUI support

- Improved partial TMR selection (Algorithmic pTMR)

### Questions?