## Upgrades of the ATLAS inner detector for HL-LHC (pixels)

Jörn Grosse-Knetter University of Göttingen

on behalf of the ATLAS Collaboration

- Introduction

- Module development:

- New FE Chip

- Sensor developments: planar, 3D, diamond, CMOS

- Read-out:

- Triggering aspects & data transmission

- Possible read-out scenario

- Mechanics

- ATLAS phase2-upgrade: complete re-design of inner tracking system for HL-LHC operation

- Most of current detector not suitable for HL-LHC

- Goal: maintain or improve tracking efficiency and small fake rate + b-tagging capabilities

- Several challenges:

- Higher track density

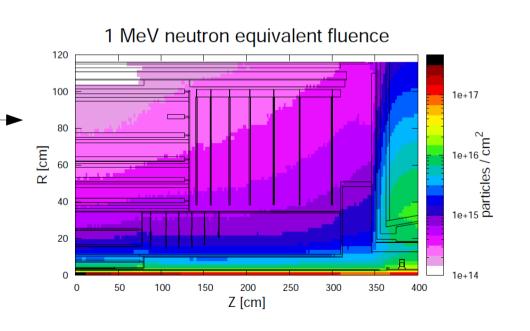

- Higher irradiation dose, fluence

- Higher hit rates

→ all silicon detector

- Re-design of triggering system

- Plans for new "inner tracker" (ITK) taking shape

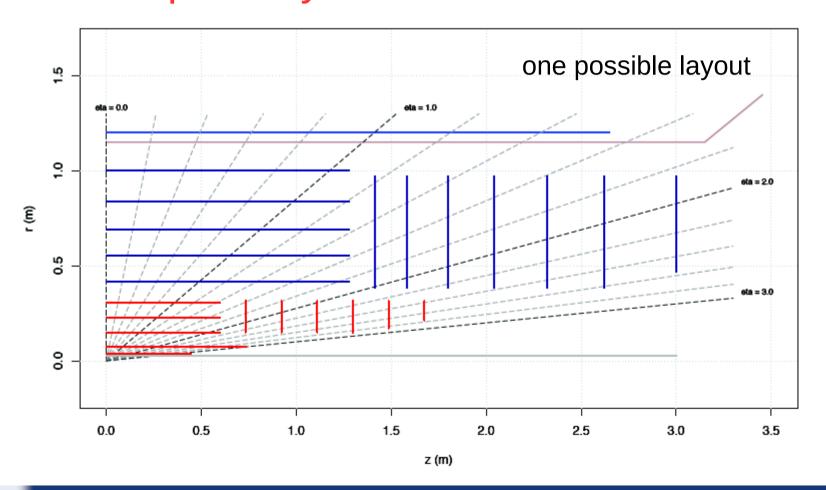

- New layout: all-silicon with outer strip layers and inner pixel layers

- Plans for new "inner tracker" (ITK) taking shape

- New layout: all-silicon with outer strip layers and inner pixel layers — this talk

- Pixel activities started to ramp up this year

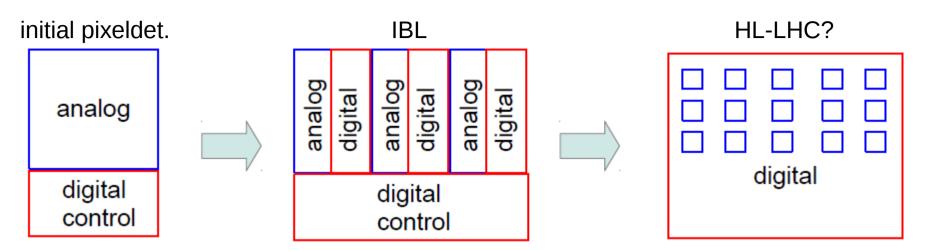

- Benefiting from 1<sup>st</sup> upgrade (insertable b-layer, IBL) that just completed:

- Already had a re-design of the read-out (FE, off-det.)

- Considered and used new sensor concepts:

- 3D in outer layers of IBL (inner: planar sensors)

- Diamond sensors in IBL-style diamond beam monitor (DBM)

- Improved mechanics/cooling concepts

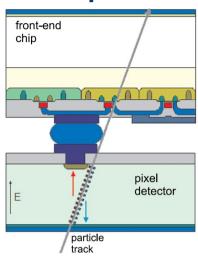

- Modules: use well-established hybrid concept

- Sensors:

- Planar-, 3D-silicon, diamond

- New concept: CMOS, combined with hybrid r/o

- FE chip: new design for all pixel layers (unclear availability of foundry that produced IBL FE)

- In any case, many improvements needed:

- Increased radiation hardness

- Smaller pixels

- Efficiency improvements in sensor design

- Low(er)-cost interconnect technology

- Expected design specifications for FE chip:

- Format, power similar to IBL FE

- Pixel size:

- Hit rate estimate: 2 GHz/cm<sup>2</sup>

- Preserve 50µm spacing between bumps

- 2500 μm² pixel area: needs a recovery time of 200ns → larger area not feasible (squared 50x50 μm²?)

- Trigger rate: 1MHz single level (+ safety margin)

- This requires several Gbps output per chip

- Many things are the same for ATLAS and CMS → collaboration via RD53

## ITK Pixel FE Chip (2)

- Need improvement in digital/analog isolation (50kHz firing rate for  $50x50 \mu m^2$  pixel)

- Combined with low threshold (IBL: ~1000e possible): very challenging

- Check radiation hardness of new 130nm or 65nm vendors:

- Target: 1 GRad

- Qualification studies with 3 vendors on-going, but much more to do

- Design changes needed for high output rate

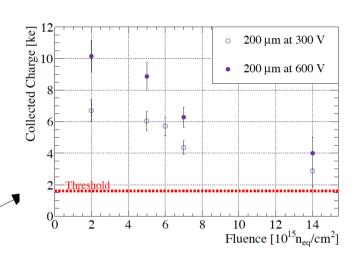

- Planar sensors (mostly n-in-p, also n-in-n)

- Good candidate for outer layers: larger areas

- Usage for inner layers: radiation hardness?

- Charge collection studies done after irrad. to  $\sim 10^{16} n_{eq} cm^{-2}$

- Other aspects investigated:

- Better efficiency with active edge sensors

- Thin sensors (<200 μm)</li>

- Pixel capacitance: small enough for FE?

- Improve biasing structures (know ineff. from past)

## ITK Pixel Sensors (planar-quad)

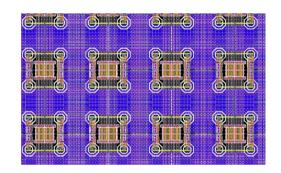

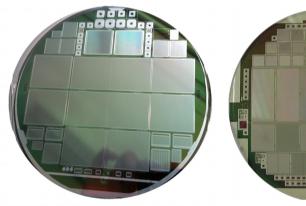

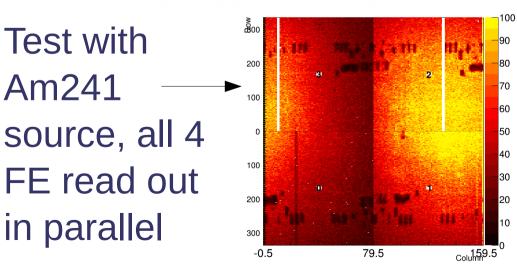

- 2x2 FE modules built with planar sensors

- Aim: reduce bump bond cost (scales per module)

- Starting from IBL design: 2x 2-FE-sensor

- Helps to build electrically functional quad-modules

- Flexes designed for these modules, bump bond tests

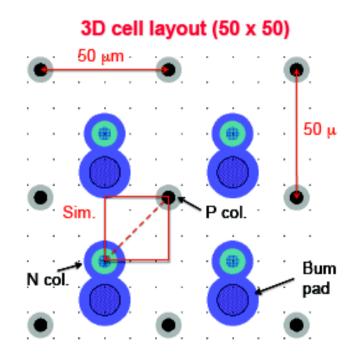

- 3D-sensors: driven by IBL vendors (CNM, FBK)

- Option for inner layers: adapt IBL design for new geometry and thickness

- Smaller pixel size requires thinner sensors to take advantage of the high pixel spatial resolution

- Radiation hardness: smaller inter-electrode spacing

- Slim or active edges

- Must tune pixel capacitance to meet FE requirements

- Diamond also option for inner layers

- Fluence >10<sup>16</sup>n<sub>eq</sub>cm<sup>-2</sup>: acceptable signal degradation

- Stable operation at low thresholds (1000e or lower)

- Sensor supply for 1-2 m<sup>2</sup> should be possible

- Vendor availability? Many produce pCVD but few at sensor quality

- Debug the bump-bonding issues from DBM

- Thinner sensors,

3D-diamond, ...

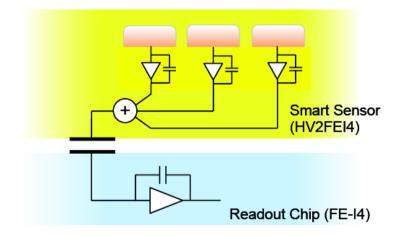

- HV/HR-CMOS: combine with hybrid concept

- Use recent developments on CMOS "smart diodes"

- Attach to "regular" FE chip for full read-out features

- Example: HV2FEI4 CMOS on IBL FE:

- Combined operation possible

- Used in src tests, testbeam

- Interconnect: bump bonds, gluing, TSV,...?

Starting demonstrator project to evaluate if suitable for ATLAS

- HV/HR-CMOS: combine with hybrid concept

- Use recent developments on CMOS "smart diodes"

- Attach to "regular" FE chip for full read-out features

- Example: HV2FEI4 CMOS on IBL FE:

- Combined operation possible

- Used in src tests, testbeam

- Interconnect: bump bonds, gluing, TSV,...?

- Starting demonstrator project to evaluate if suitable for ATLAS

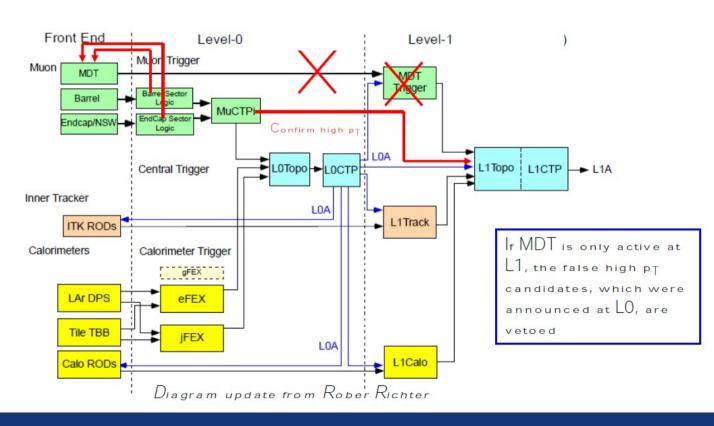

- HL-LHC will see a new L0 trigger in ATLAS partial/full read-out:

- L0 : 1 MHz 6 μs latency

- L1: 400 KHz 24 μs latency

- Pixel will do full readout on L0

## Data rates and bandwidths at 1MHz trigger:

| Detector | Number of   | Module type | Rate/module | GBT/stave | Rate/GBT | Link per              |

|----------|-------------|-------------|-------------|-----------|----------|-----------------------|

|          | modules per |             | [Mb/s]      | side      | [Mb/s]   | $\operatorname{side}$ |

|          | stave/disk  |             |             |           |          |                       |

| layer 1  | 22          | dual        | 5120        | 11        | 5120     | 176                   |

| layer 2  | 36          | quad        | 5120        | 18        | 5120     | 288                   |

| layer 3  | 35          | quad        | 2560        | 9         | 5120     | 288                   |

| layer 4  | 35          | quad        | 1280        | 5         | 5120     | 260                   |

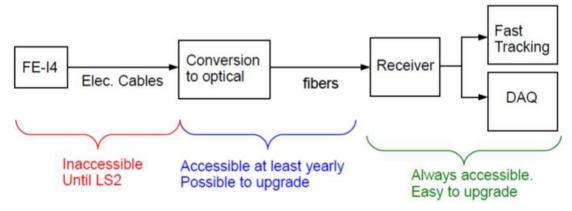

- Data links:

- Prefer to move opto comp. outside of det.volume: fast electrical cables

- Then via fast optical links: GBT fast enough?

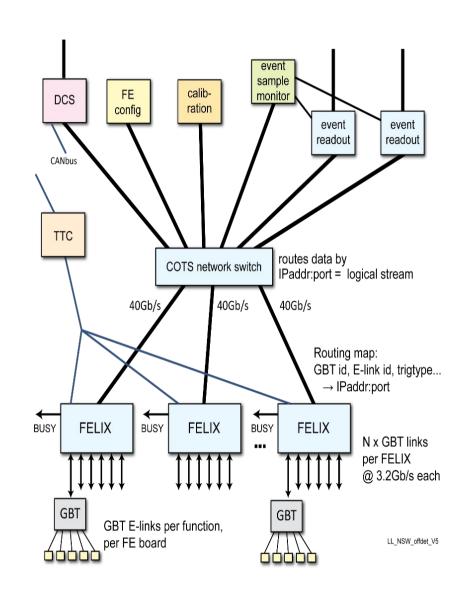

- Then, general ATLAS concept:

- data routed via switch

- Pixels: use DAQ HW also for calibration

- Goes beyond pure data transport needs

- Address scan control and data decoding (histogram) apects

- Developments on support structures

- Example: Stavelets = shorter staves

More dynamical layout, e.g. Alpine

Stave profile changes along longitud. direction, modules attached to inclined support

- HL-LHC ATLAS-Pixel development is picking up speed with more details under investigation

- Many challenges ahead:

- New FE design with new technology

- Decide on best sensor technology(ies?)

- Many new aspects beyond module design: readout, mechanics,...

Schedule: "technical design review" in 2017