# **VERTEX 2008**

#### **17th International Workshop on Vertex Detektors**

Gruvbryggan, Utö **SWEDEN** 27 July - 01 August 2008

Conference Summary by Roland Horisberger, PSI

Fantastic week with total of **42 talks** on all kinds of aspects vertexing and tracking with precision detectors:

| Session 1-3 Running and commissionin | a experience |

|--------------------------------------|--------------|

|--------------------------------------|--------------|

Session 4 R&D on future detectors

Session 5 Tracking and vertexing

Session 6-7 **Novel detectors and electronics**

Session 8 **Performance and data quality**

All contributions were really excellent and deserve to be mentioned

However, its just impossible to summarize all the talks in a fair way

→ do a bit of a personal choice (please excuse my ignorance)

### **Session 1-3 Running and commissioning experience**

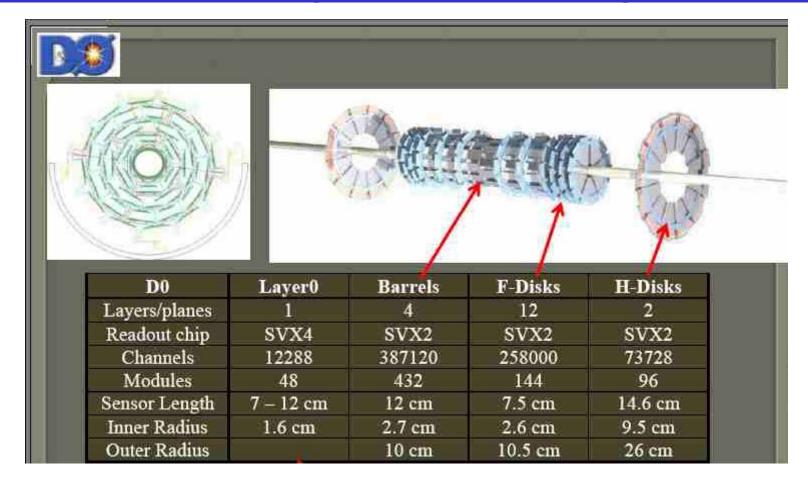

- D0 has been able to find the right balance between 'stable operations' and maintenance. (over 7 years)

- Continued studies with the system also fostered new experts to keep up with system knowledge

# Data quality / lost data

Overall only 2.5%

of luminosity

declared bad

for silicon data

Almost all losses due to various power supply failures

|              | Good   | Bad  | Special |

|--------------|--------|------|---------|

| May '07      | 98.0%  | 1.6% | 0.4%    |

| June '07     | 95.7%  | 4.3% | 0.0%    |

| July '07     | 99.7%  | 0.0% | 0.3%    |

| August '07   | 100.0% | 0.0% | 0.0%    |

| October '07  | 99.5%  | 0.5% | 0.0%    |

| November '07 | 99.8%  | 0.2% | 0.0%    |

| December '07 | 99.8%  | 0.2% | 0.0%    |

| January '08  | 100.0% | 0.0% | 0.0%    |

| February '08 | 95.4%  | 4.6% | 0.0%    |

| March '08    | 95.4%  | 4.6% | 0.0%    |

| April '08    | 99.5%  | 0.0% | 0.5%    |

| May '08      | 99.6%  | 0.4% | 0.0%    |

| June '08     | 95.9%  | 4.1% | 0.0%    |

→ Impressive achievment on operating a sizeable silicon system

done by "young leaders with senior support"

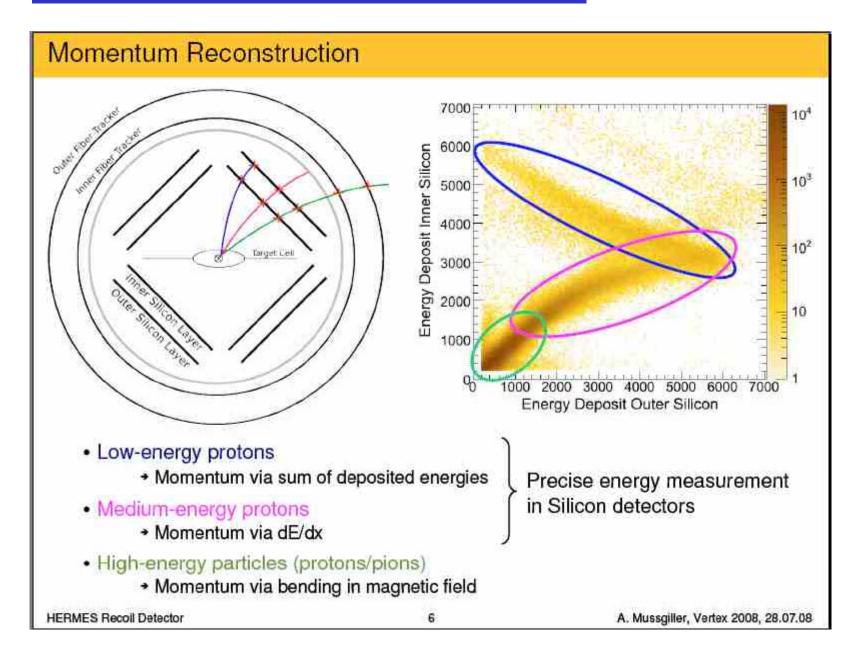

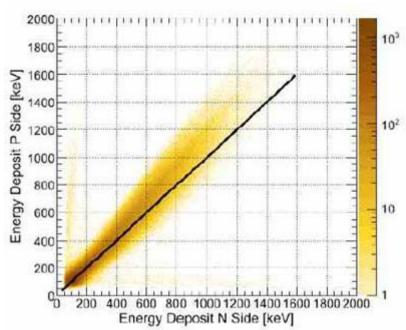

## **Hermes Silicon Recoil Detector**

- corrected beam induced pedestal drifts

- channel dependent pedestal & crosstalk corrections

- → dealt inventive with occuring problems

#### Finally get very nice calibrated system!

→ System is as good as it gets calibrated and understood

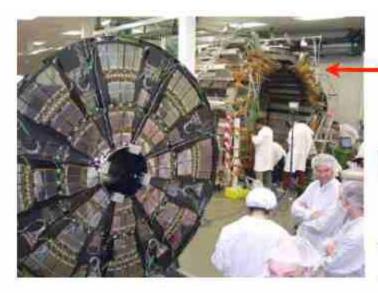

## **Commissioning CMS Silicon Tracker**

(very large system)

SST integration at CERN main site

The SST ready for transport to CMS (20km journey)

Many Issues: Synchronisation

Opto-Gain Scan noisy strips <1%

Latency scans

In very short period successfully installed and brought into operational mode (Congratulations)

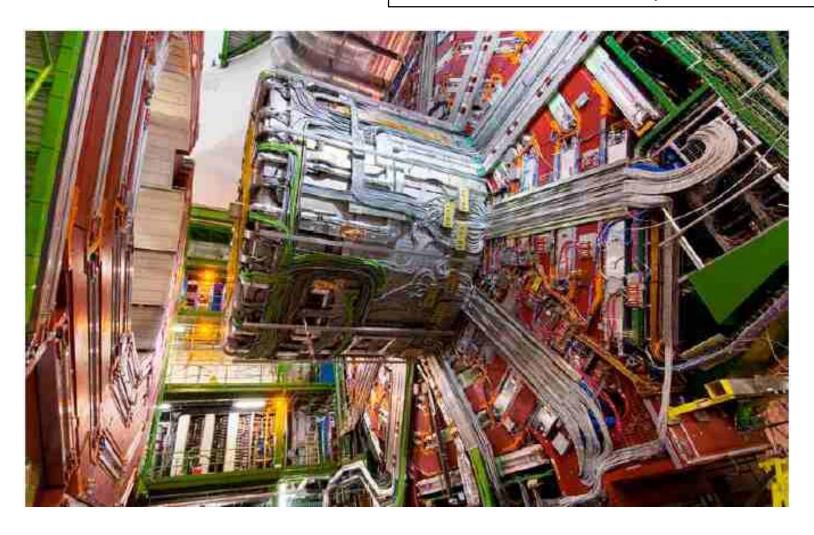

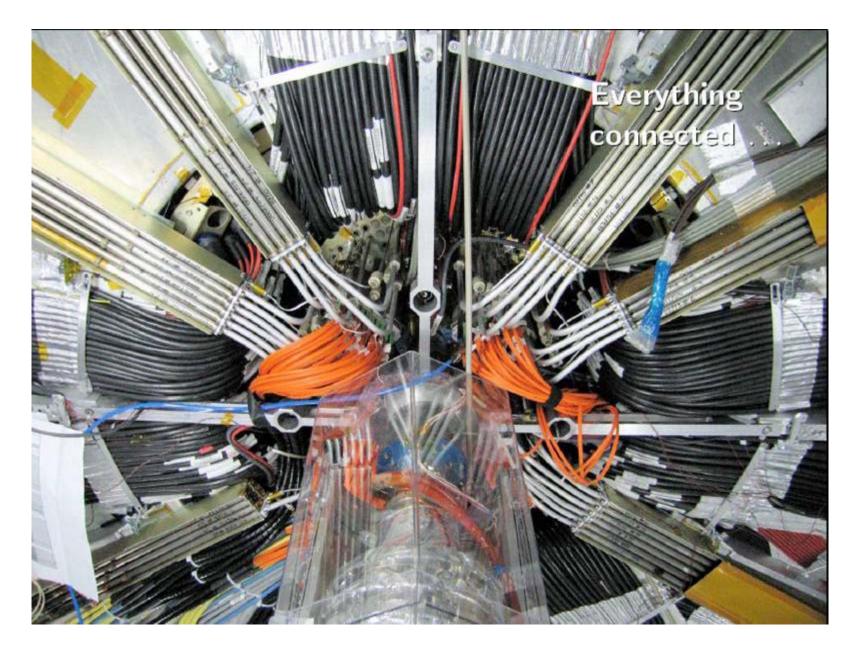

# **CMS YB0 Cabling**

Considerable effort → needs top attention

→ must be at start of planning

→ likely to live with in SLHC

→ don't under estimate cooling!

# **Commissioning the ATLAS Tracker**

Single cylinder tests

Sept. 2005: outer layer in thermal enclosure

Dec. 2006: inner layer insertion

#### Conclusions

The Atlas SCT is being commissioned quite rapidly.

Pace is signed by the evaporative cooling: use any slot available with cooling loops.

Cooling compressor accident delayed commissioning (exp. pixels) and stable running.

Cooling now back, beam pipe bake-out taking place in this moment.

Gaining experience with a very complex system

Modules seem to behave very uniformly.

Solving initial problems at the <~ % level.

Cosmic rays detected in conjunction with other detectors

DAQ, DCS and Monitoring tuning up

Ready for collisions in a few weeks!

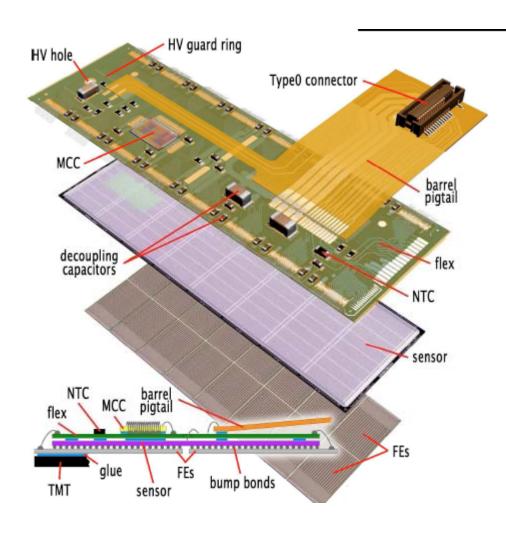

## **Atlas Pixel Detector Installation & Commissioning**

#### Thickness:

Sensor  $250\,\mu\mathrm{m}$  Drond-end  $196\,\mu\mathrm{m}$  Flex hybrid printed circuit  $100\,\mu\mathrm{m}$

#### Sensor:

- Oxygenated high resistivity Si

- n+ in n-bulk

- 150 600 V bias

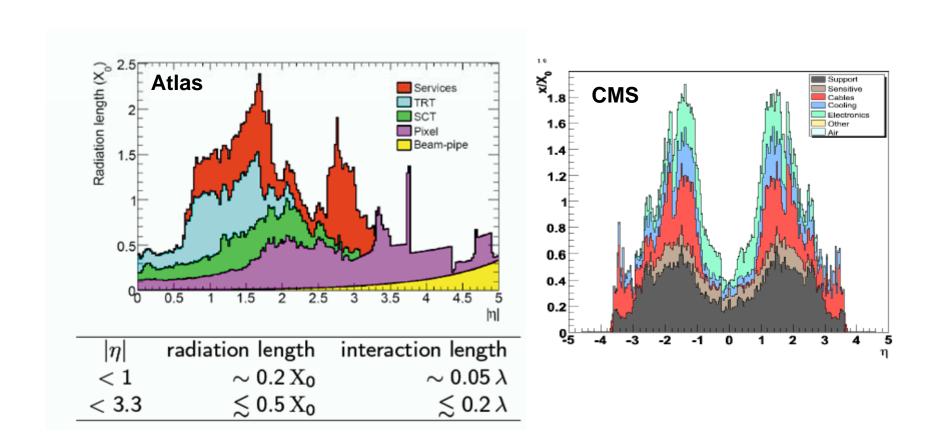

## **Material Budget of LHC Experiments**

CMS & Atlas both slipped considerable in keeping X/X<sub>0</sub> originally aimed for !

Old argument that Silicon would be too thick is a myth. "It's the power & cooling.. stupid.."

### Issues with Optical Connections (In-Link)

- Light output lower then expected, but sufficient to control modules (clock, configuration, commands).

- Light output increased by 16% in two month.

#### **Experience in CMS**:

- Optical connectons can easily become dirty → absolution, reflections

- Affect digital just like analog

- Slack management with short optical fibres pieces is terrible

Very neatly done! All set to go! → Congratulations

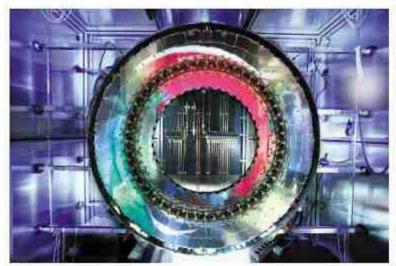

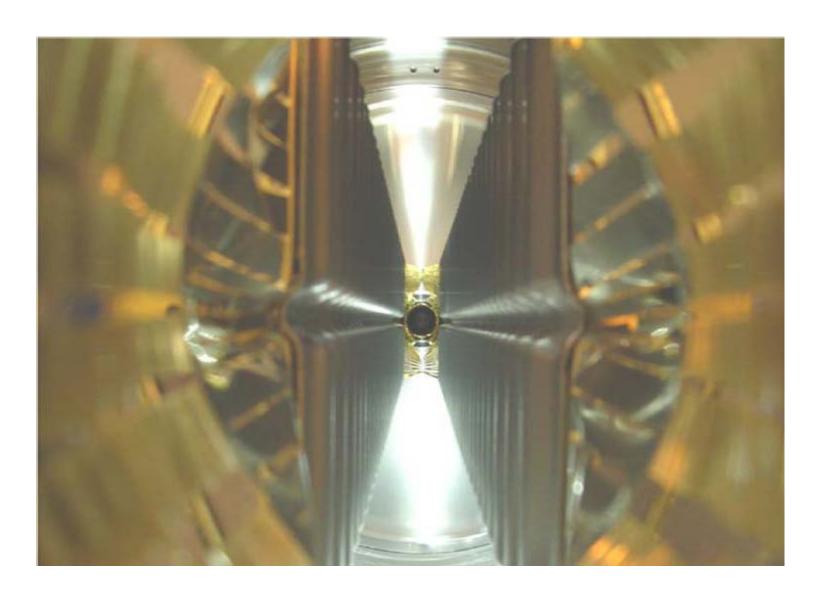

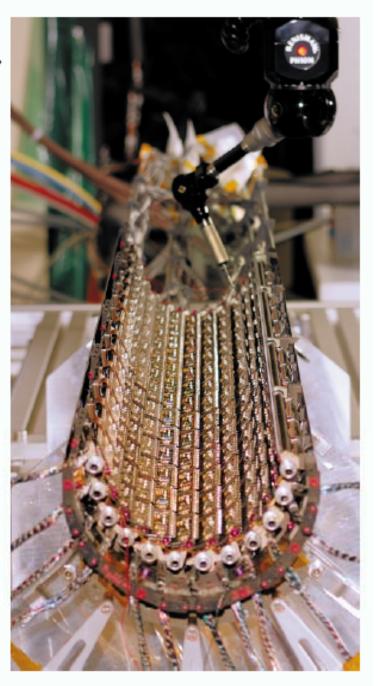

# **LHCb Velo Installation & Commissioning**

### **Conclusions**

- All components fully installed and tested.

- Extensive commissioning programme over last year.

- First operation of whole detector under vacuum

- 99.2% of channels fully operational.

- LHCb VErtex LOcator in good shape for first beams

Again: Power supply issues!

## CDF silicon cooling: problems and recovery

With great admiration I observe how difficult situations can be mastered!

### BCM Detector Modules Installed

BCM modules were installed on Beam Pipe Support Structure in November 2006 and lowered into ATLAS pit in June 2007

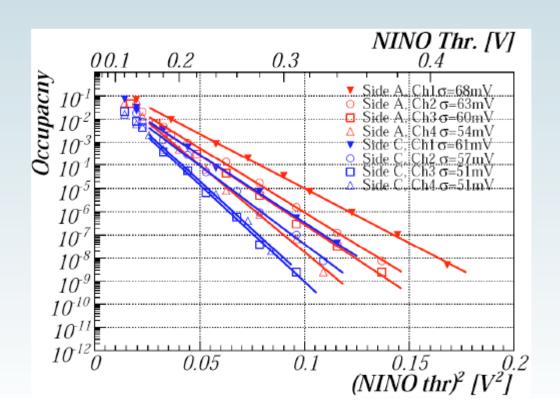

### Performance of installed NINO boards

Noise rate measured in ATLAS pit (after installation of NINO boards in ATLAS)

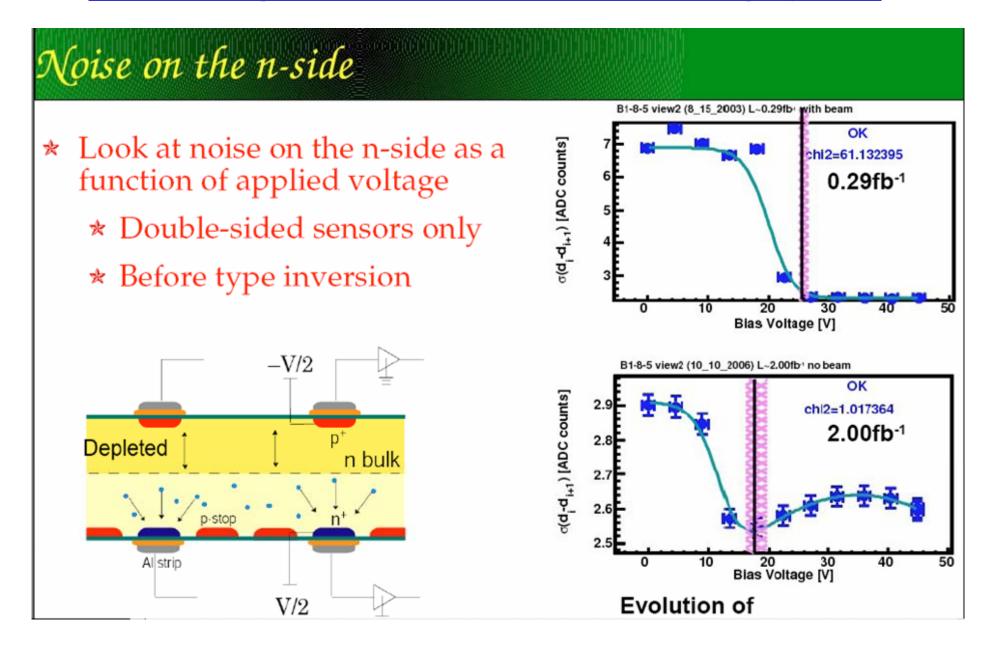

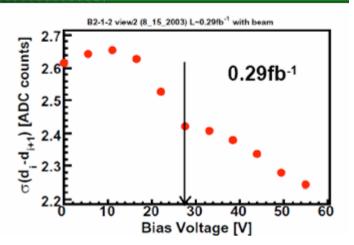

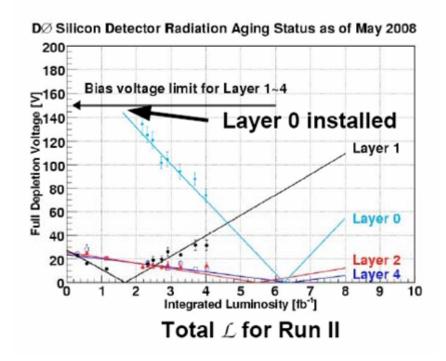

### Rad. Damage Studies of D0 Silicon Tracking System

# Double-sided Double-metal Noise

- Unexpected behavior for doublesided double metal sensors

- Believed to be a result of charge buildup in thin insulating layer between metal layers

- Position of kink interpreted as V.

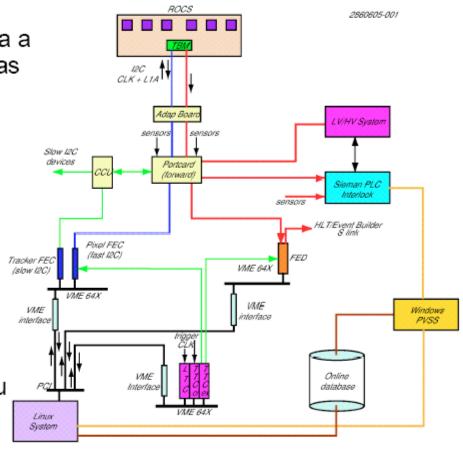

### **CMS Pixel Commissioning**

# **Finding an Operational Point**

In order to be able to configure and read out data a large number of settings has to be determined

ROC settings: Timing, Pulse Height, Gain settings, Linearity.

#### **TBM Gains**

Delay settings for 40MHz communications

AOH bias and gain

Address levels in the FED +ADC phase adjustment

Note that in this design you need to control the charge injection via software

CMS Pixel System has many knobs to turn → non trivial adjustment needed

"Pixel In Box" was extremely usefull to connect to the final DAQ environment

## Pixel in a Box

- To test integration with run control and participate in global CMS runs before the full detector was installed we prepared a small test system with one panel.

- Useful to debug run control and other operational issues.

- Installed in CMS from March-July 2008

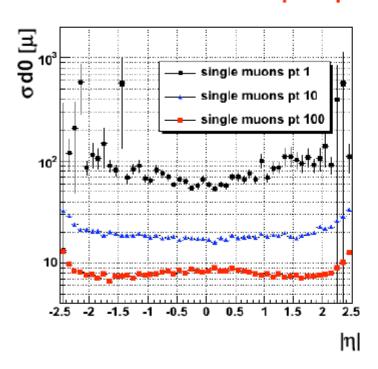

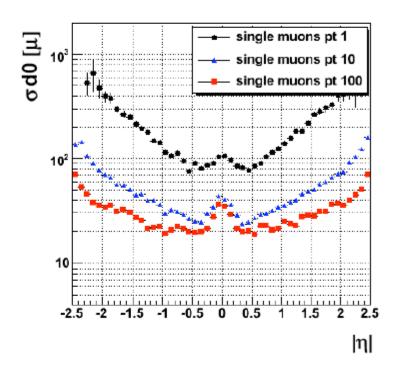

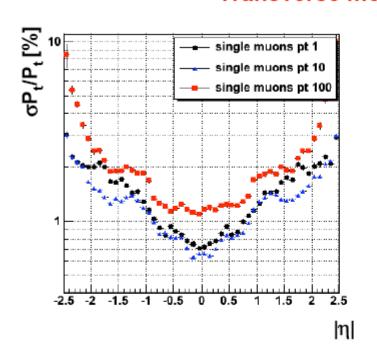

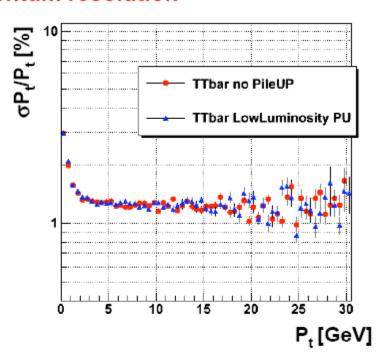

### **CMS Track Reconstruction Performance**

### **Track reconstruction performance**

#### Impact parameter resolution

Resolution on transverse impact parameter is expected to be:

- ~50-60 microns for ~1 GeV particles

- ~10 microns for 100 GeV particles

#### **Transverse momentum resolution**

→ CMS tracker has excellent performance !!

but . .. ..

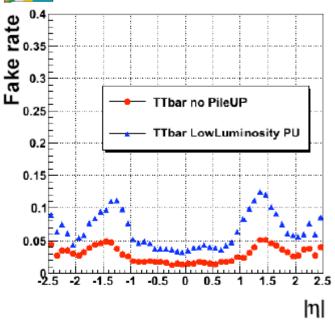

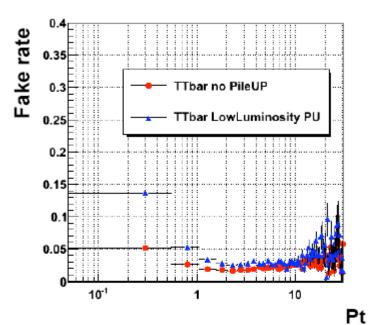

### **Track reconstruction performance**

Fake rate = (# tracks NOT associated to simulation)

(# reconstructed tracks)

A reconstructed track is associated to a simulated one if more than 75% of its hits are "matched" to the ones of the simTrack.

Most of the fakes are in:

- the low pt region

- barrel-endcap transition eta region

→ material budget

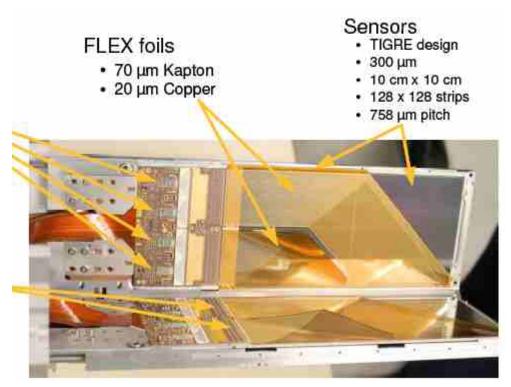

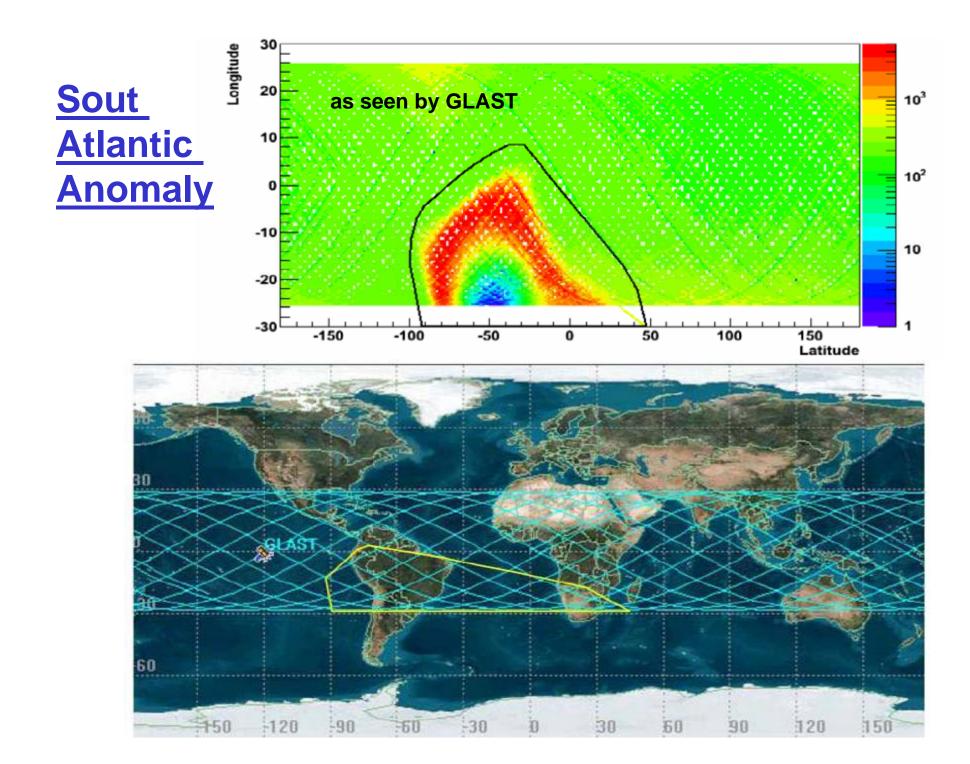

# The GLAST mission

Large Area Telescope (LAT)

20 MeV - 300 GeV

>2.5 sr FoV

GLAST Burst Monitor (GBM) 8 keV – 30 MeV 9 sr FoV

- gamma ray mapping of sky

- large silicon tracker pair spectrometer system in space (~70m²)

- successfully launched 11. June 2008

- now in phase of commissioning follow by 1 year of observation

Note: seem to have cooling under control

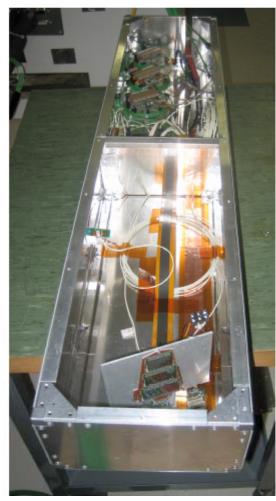

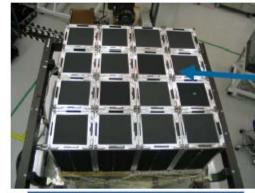

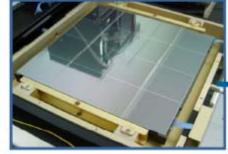

# **Tracker Design Overview**

#### • 16 tower modules

- 37 × 37cm<sup>2</sup> active cross section/layer

- 2 mm inter-tower separation in order to minimize the inactive area

- 70m2 of Si (in space!!!)

- 11500 SSD 8.95X8.95 cm<sup>2</sup>

- 384 strips 880,000 channels

- 440 µm thick

- 228 µm strip pitch:

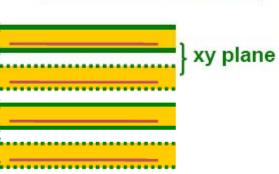

#### • 18 xy layers per tower

- 19 "trays" structure

- 12 with 2.7% X<sub>0</sub> W

- 4 with 18% X<sub>0</sub> W

- · 3 with no converter foils

- · every tray is rotated by 90°

- W foils are followed by

- x,y plane of detectors

- 2mm gap between

- Electronics on sides of trays:

- Minimize gap between towers

F.Gargano - Vertex 2008 - July 28-August 1

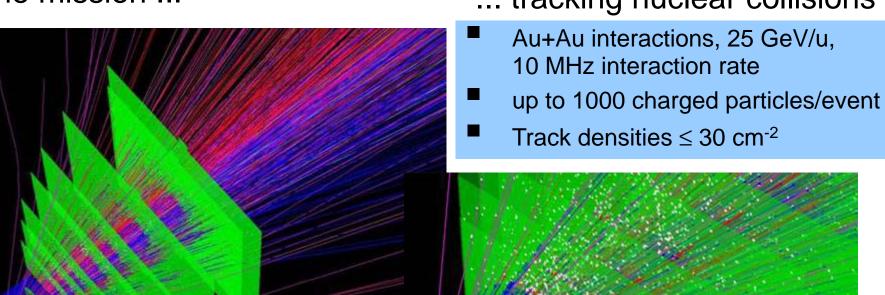

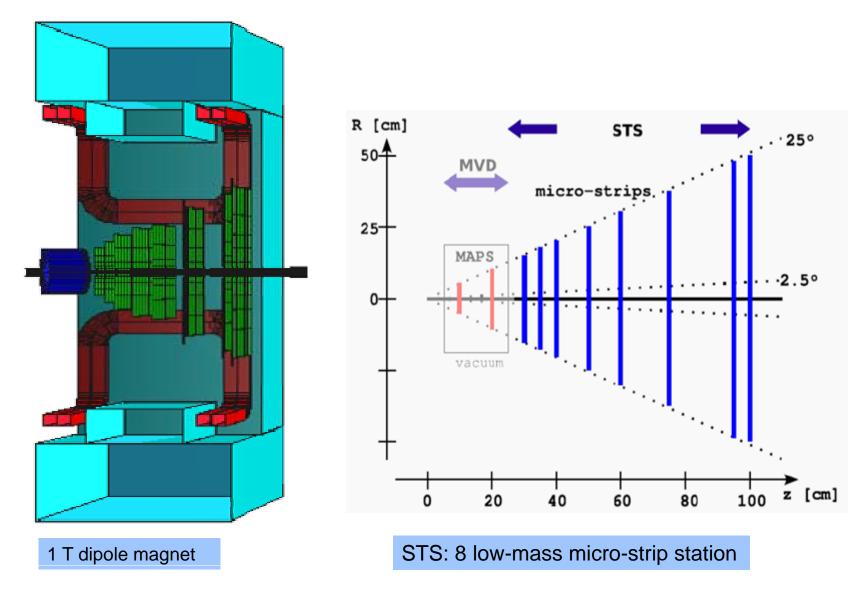

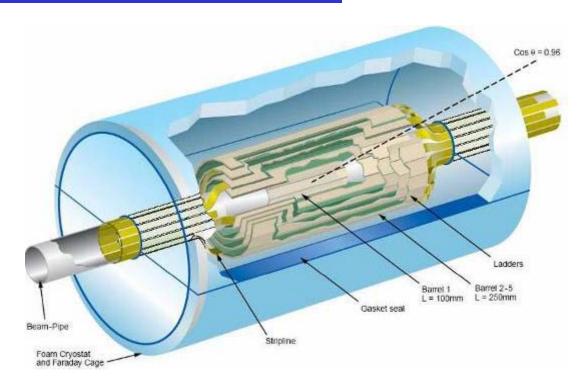

## **Silicon Vertex Detectors for FAIR**

Compressed Baryonic Matter Experiment

tne mission ... ... tracking nuclear collisions

UrQMD generator:

Monte Carlo tracks ...

+ micro vertex detection: presentation by M. Deveaux

# Exploration of a system concept

Development have started → we look forward for future Vertex Conferences!

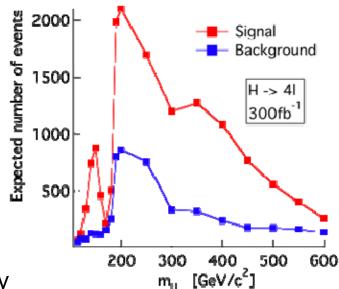

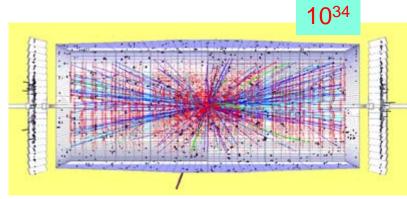

# **CMS Tracker Upgrade programme**

- Limited statistics eg:

- and time to reduce errors

- However, the environment is very challenging:

■  $H \rightarrow ZZ \rightarrow \mu\mu ee$ ,  $M_H = 300 \text{ GeV vs luminosity}$

Full LHC luminosity ~20 interactions/bx

Proposed SLHC luminosity ~300-400 interactions/bx

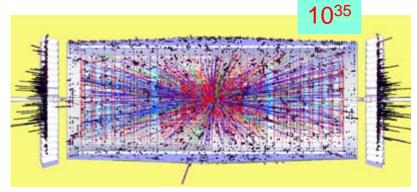

### **Different Strawman layout now under study**

- A working idea from Carlo and Alessia

Strawman A

- Take current Strawman A and remove 1 "TIB" and 2 "TOB" layers

Vertex 2008 33

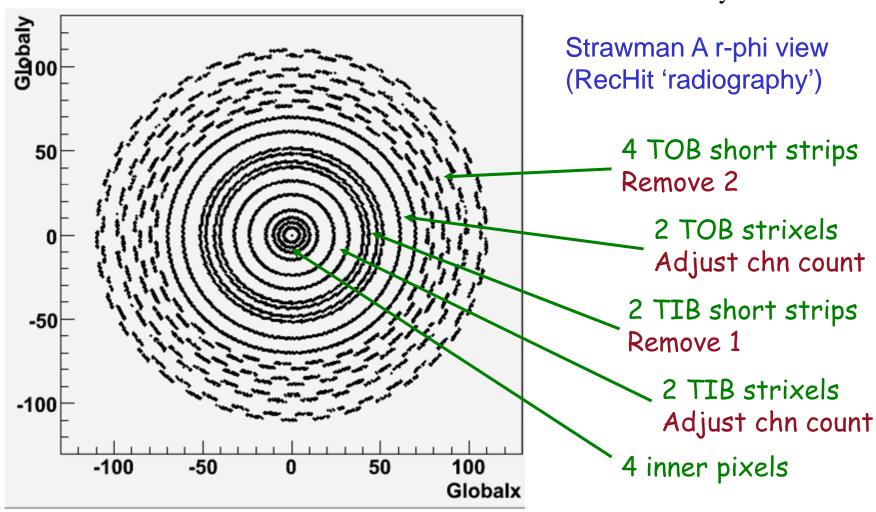

### **Strawman B**

- Adjust granularity (channel count) of Strawman B layers

- Keep the TEC for now until someone can work on the endcaps

Vertex 2008 34

# **LHCb Upgrade**

- •Upgrade LHCb detector such that it can operate at 10 times design luminosity of  $\mathcal{L} \sim 2 \times 10^{33} \, \text{cm}^{-2} \text{s}^{-1}$

- •Accumulate ~100 fb<sup>-1</sup> without detector replacement

- → looking to use hybrid pixel detectors for VELO replacement

- → adapt FPIX chip development for former BTeV experiment

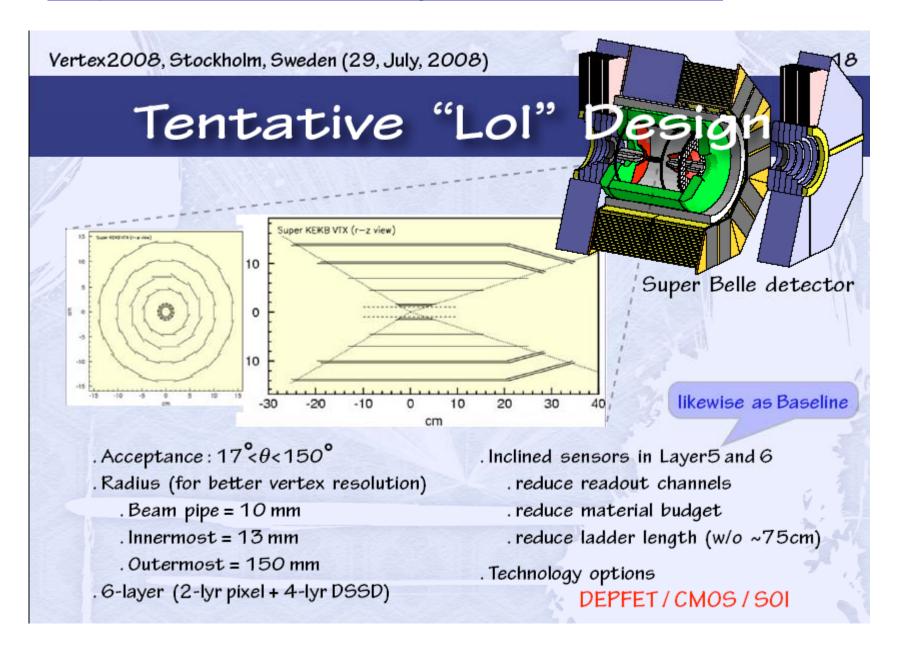

# **Super Belle B-factory Vertex Detector**

# Technology options

| 13      |                           | DEPFET                                                       | CMOS (CAPS/MAPS)                               | 501                                 |

|---------|---------------------------|--------------------------------------------------------------|------------------------------------------------|-------------------------------------|

| Ma      | aterial budget            | 20 ~ 100μm<br>(adjustable)                                   | <~ $50\mu m$ (sensitive area $5$ ~ $10\mu m$ ) | 50~100μm<br>(could be <~50μm)       |

| Siz     | ze                        | limited by wafer<br>(50 x 75 mm²)                            | limited by reticle<br>(21 x 21 mm²)            | limited by reticle<br>(21 x 21 mm²) |

|         | wer<br>consumption        | small (0.5w)<br>(reset switcher chip:<br>Voltage swing > 8V) | small                                          | small                               |

| 8 7 7 8 | adhardness<br>(3MRad/yr?) | tested < 1MRad<br>(up to 8MRad?:<br>irradiation test)        | intrinsic rad. hard<br>(must be > 30MRad)      | tested > 30MRad                     |

|         | OkHz<br>trig. rate        | estimated<br>~1% ineff.                                      | ?<br>(CAP3 too slow)                           | not proved                          |

| Av      | vailability               | MPI only<br>(already used<br>in other exp.)                  | R&D in progress                                | R&D in progress                     |

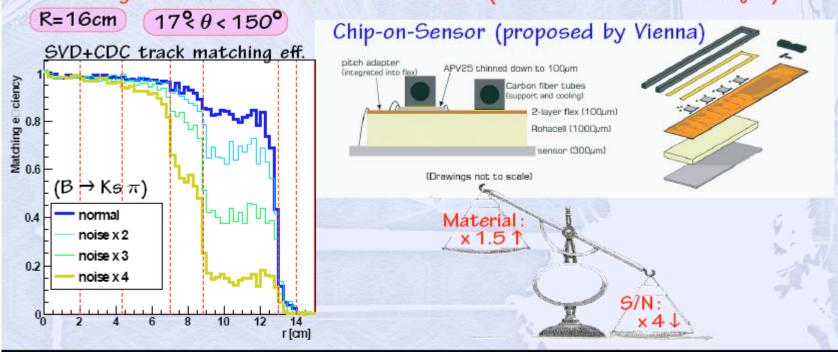

### Readout Chip for outers

High trigger rate (~10kHz): Pipeline readout → APV25

beam BG tolerant: Shorter shaping time is preferred, but not critical

longer sensor + APV25 → worse S/N (VA1TA~16 for outer layer)

# FE Electronics for the B-Layer replacement or SLHC in ATLAS

Vertex2008

July 28-August 1, 2008, Utö Island, Sweden

Roberto Beccherle

[on behalf of the ATLAS Pixel Collaboration]

Email: Roberto.Beccherle@ge.infn.it

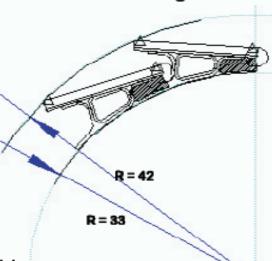

# **B-Layer replacement options**

- Replace the Pixel Detector with a simpler 2 hit system with present technology (case of disaster) is not realizable (collaboration to build it, spares not available)

- B. Insertion of a smaller b-layer and a smaller beam pipe inside the existing detector.

- Insertable B-Layer with present technology:

- Possible fall-back from preferred solution.

- Insertable B-Layer with new technology.

- Seems feasible (Requires new smaller beam-pipe).

- I 6-staves not shingled b-layer.

- New chip design (FE-I4): Live fraction, I/O bandwidth;

- New Sensor design: Increase radiation hardness (400 fb<sup>-1</sup> between 2013 and 2016)

due to the smaller radius and the ramping up of LHC luminosity.

- R&D and prototyping in 2009 construction 2010-2012;

- The critical part is the very short R&D time available for the new design.

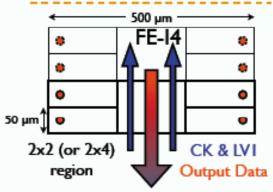

# Need for a new architecture

- Double column bus occupancy and the number of EoC buffers implemented as in FE-I3 and power consumption do not scale well with size and higher event occupancy.

All data is processed and copied to the EoC buffers, but only < 1% gets triggered!</li>

- The basic idea is to store all the information as long as posible locally in the Pixel region and to transfer to the periphery only the amount of information that has really to be transferred off chip.

- We still want to keep the Time over Threshold option, as in FE-I3.

- Storing all information directly in the pixels is also not feasible as one buffer per pixel would surely not be enough, and two would not fit.

- Therefore the idea is to put together "as many pixels as possible" forming "local regions" of pixels that can share buffers and logic in order to optimize the overall number of needed buffers.

- There has to be a compromise between the number of pixels grouped together which leads to a lower number of buffers, but a higher complexity in the routing and combinational logic needed to deal with the common region.

Vertex 2008, July 28-August 1, 2008

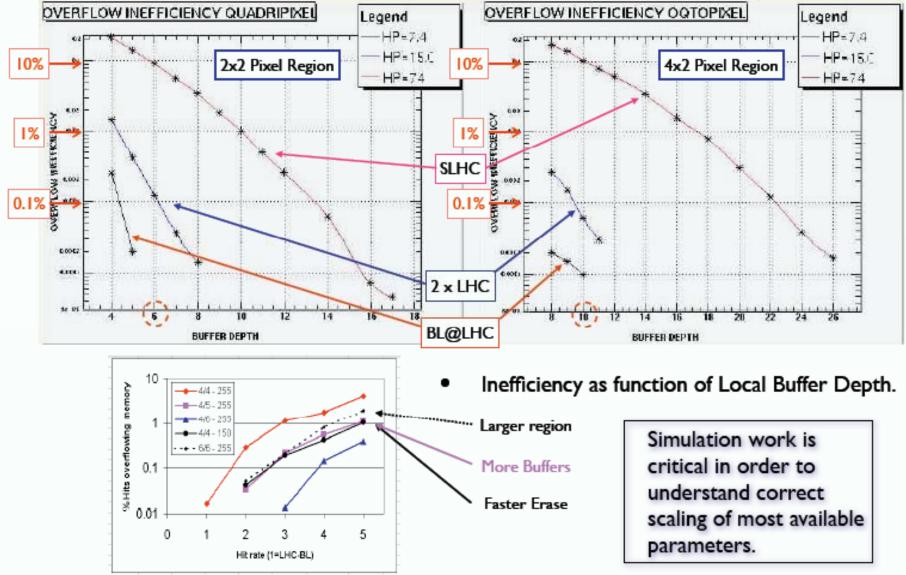

# Local Buffer depth effects

### **ILC** vertex detector

- Precision measurement of jet energies is not enough: which are b-jets, charm-jets or light quark jets? For the heavy quark jets, which are quarks and which antiquarks? Latter is most cleanly established by measuring the 'vertex charge', pioneered with considerable success by SLD

- Achieving the required performance is the task of the most expensive ILC detector R&D topic – currently 9 options are being pursued

### **VXD** technologies

- All approaches aim for ~3  $\mu$ m precision and <40  $\mu$ m 2-hit resolution

- Target material budget is ~0.1% X₀ per layer

- They vary from single-bunch time stamping to time integrating with special compensating features

- List them in approximate order of adventurousness one or two are more likely to be candidates for second generation upgrades

#### FPCCD – Yasuhiro Sugimoto (Takubo-san, this wkshop)

•CCD with 5  $\mu$ m pixels, read out once per train; 20 times finer pixel granularity instead of 20 time slices

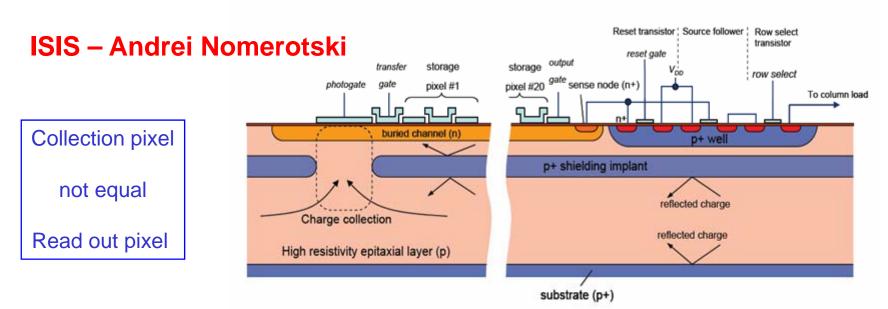

#### **CPCCD – Andrei Nomerotski**

- •Fast readout of CCD aiming for 50 µs frame rate

- •Main novel features are column parallel readout, with bump-bond connections on 20  $\mu m$  pitch to readout chip including amp, analogue CDS, ADCs, sparsification and memory

#### **CMOS MAPS (MIMOSA) – Marc Winter**

•3T architecture, limited to NMOS transistors in pixel

#### DEEP n-well – Valerio Re (Francesco Forti, this wkshop)

•Full CMOS in pixel, collecting signal charge o nthe deep n-well that houses the NMOS transistors (triple-well process)

#### **CAP – Gary Varner**

•CMOS MAPS, with signal storage (after charge-to-voltage conversion) on inpixel capacitors

#### **DEPFET – Laci Andricek**

•Signal charge stored on 'internal gate' – unique in-house technology

#### **Chronopixels – Dave Strom**

•Goal is to time-stamp (single bunch) by pixel functionality that can fit into a 10  $\mu$ m pixel (full CMOS wirh 45 nm design rules)

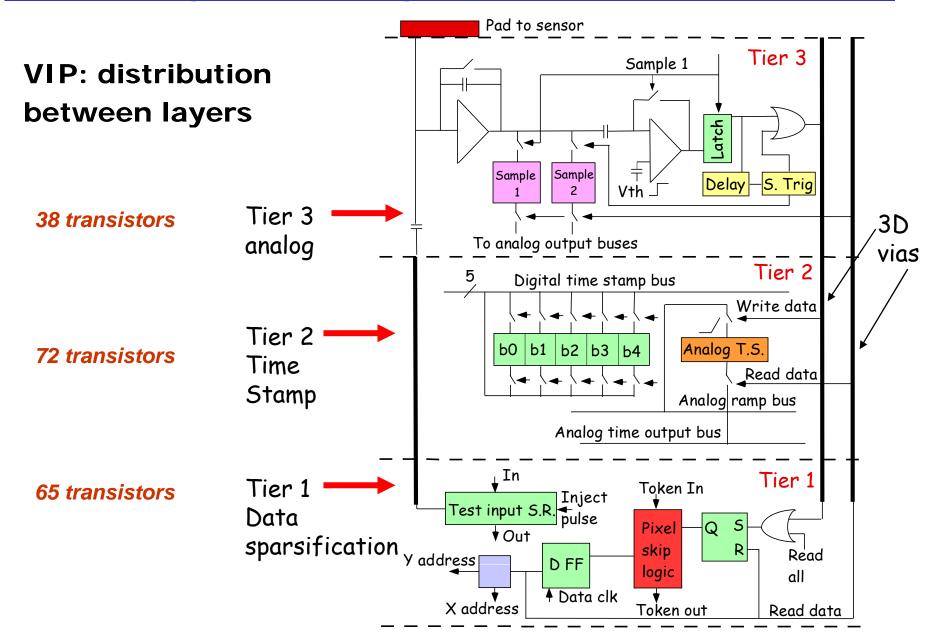

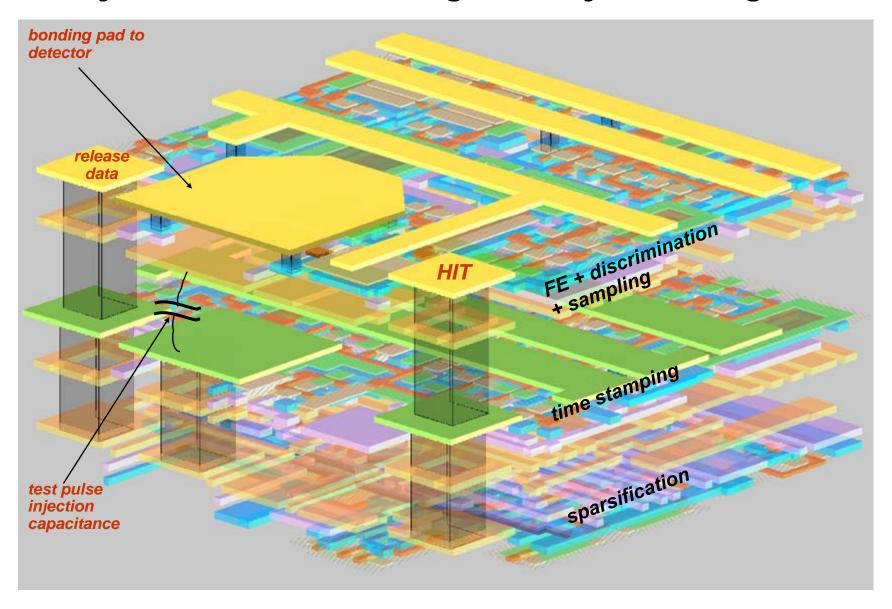

Vertically integrated pixel detectors (SOI & 3D) – Ray Yarema (Grzegorz Deptuch, this wkshop)

•An impressive strategy to be liberated from the constraints of CMOS by developing tiered systems

#### **Vertical Integration of Integrated Circuits & Pixel Detectors**

#### VIP: layout view with 3D Design Tool by Micro Magic:

First chips have been manufactured !!! → yield could improve when going to bulk CMOS

### New Manufacturers Developing Detector Grade Diamond

#### Status:

RD42 has begun working with two companies (Germany, US) to develop detector grade diamond material

lacktriangle First samples from companies show charge collection distance  ${\sim}100\mu\mathrm{m}$

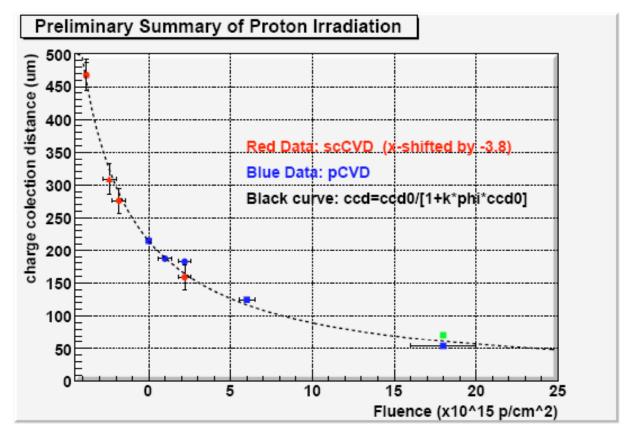

#### Radiation Hardness Studies with pCVD and scCVD Trackers

#### Proton Irradiation Summary - preliminary:

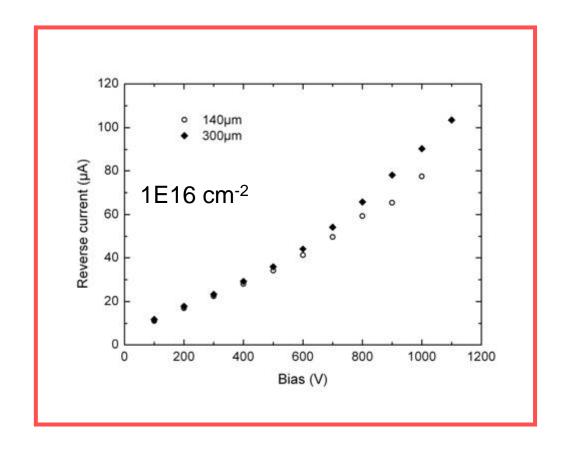

Preliminary summary of proton irradiation results for pCVD (blue) and scCVD diamond (red) at E=1V/ $\mu$ m up to  $1.8 \times 10^{16}$  p/cm $^2$  ( $\sim$ 500Mrad). pCVD and scCVD diamond follow the same damage curve:  $1/\text{ccd}{=}1/\text{ccd}_0$  +k  $\phi$ .

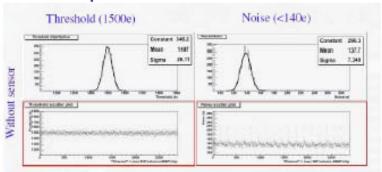

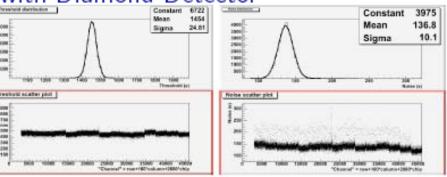

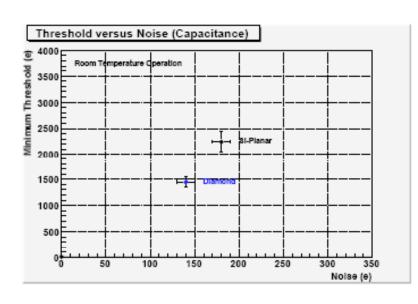

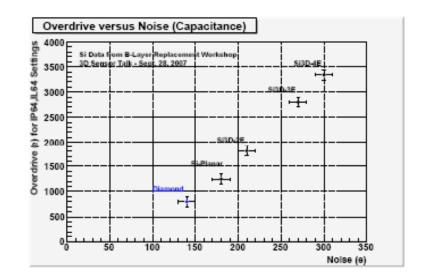

#### The ATLAS pixel module - Noise, Threshold

Bare Chips

with Diamond Detector

Noise  $\sim 140e$ , Mean Threshold 1500e, Threshold Spread  $\sim 25e$ .

#### Radiation Hardness Comparison

7

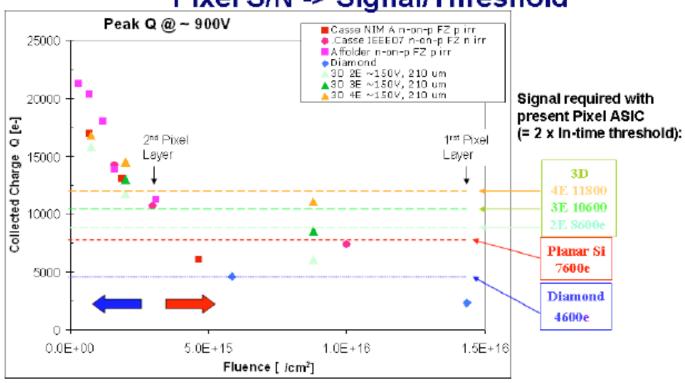

Signal/2x In-time Threshold (from H. Sadrozinski Jun08 ATLAS talk):

Pixel S/N -> Signal/Threshold

Need to optimize FEE

Marginal performance for innermost Pixel Layer

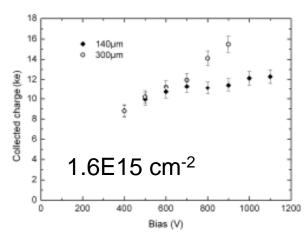

#### **Charge Collection Efficiencies Studies in Silicon**

#### One comment on thin devices

SLHC we will dissipate as much power to sensor as to ROC

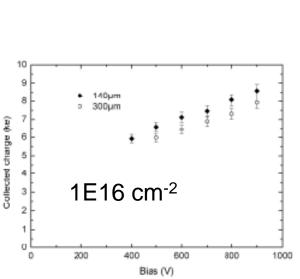

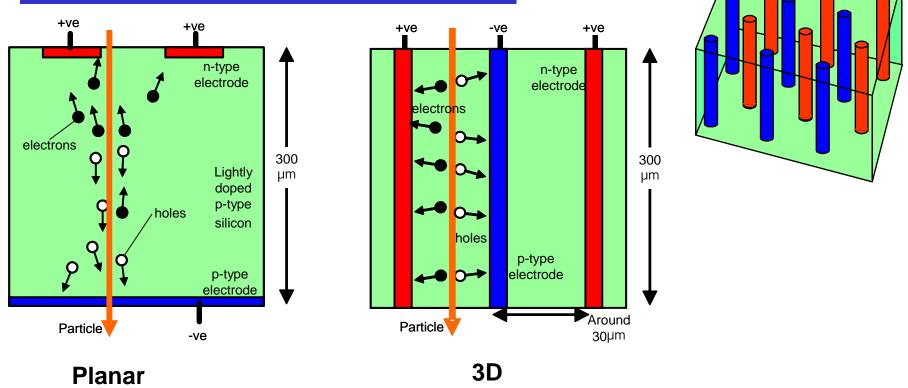

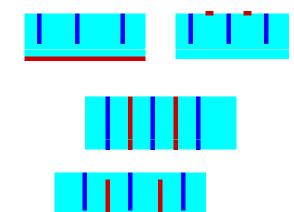

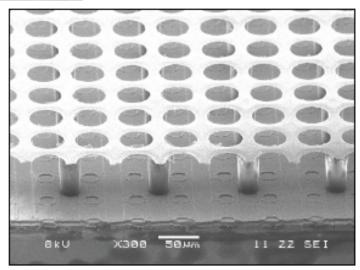

### **3D Detector Structure**

**Single Sided Single Type Columns (semi-3D)**

Single Sided Double Type Columns (classic 3D)

**Double Sided Double Type Columns (new 3D)**

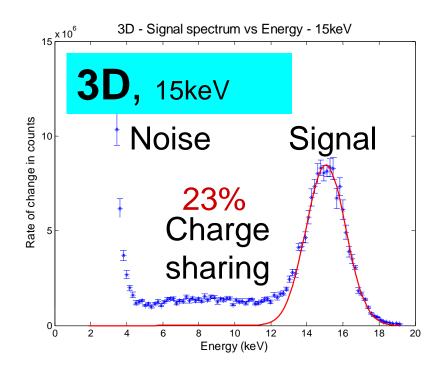

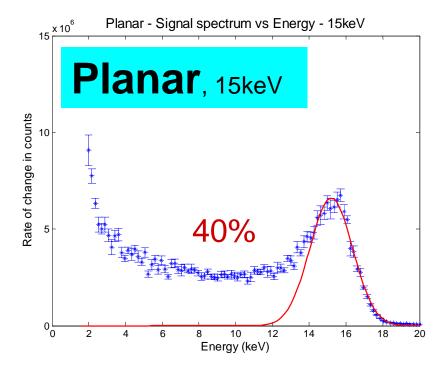

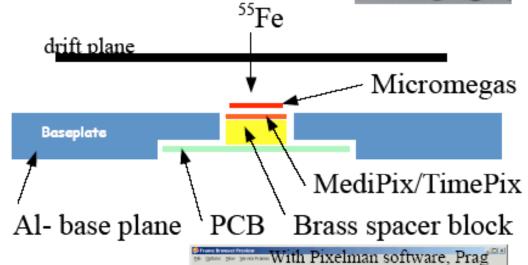

### Spectral scan

Medipix application 55um pixel size

- Monochromatic beam

- Threshold scanned through signal into noise

- Charge sharing reduced in 3D detector

- self shielding geometry

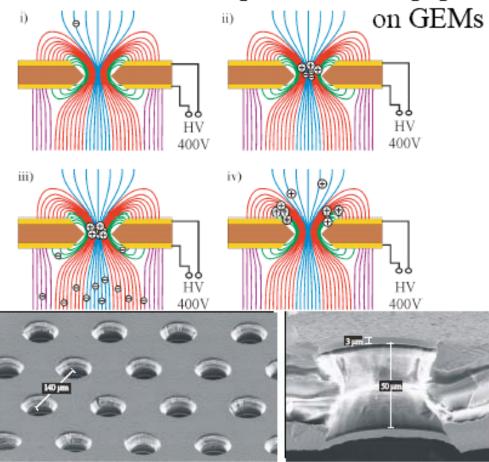

# The 2 Favorites: Micromegas & GEMs

1996 first publication of MM

Drift plane

Micromesh

Anode strips

I. Giomataris Pillar

1997 F. Sauli publishes first paper

### InGrid

IMT Neuchatel: 15 or 20 μm highly resistive aSi:H protection layer (~10<sup>11</sup> Ω·cm) MESA+: InGrid

chip survives several 1000 discharges induced by Thorium

## **Summary & Conclusion**

- The conference was just like the weather → fantastic

- I would like to thank and congratulate all the speakers for their excellent talks

- Most of all, I would like to thank Richard Brenner his people that made this conference such a success.

- I wish everyone a good return and a successful continuation of their work, hoping that it can be reported and shared in VERTEX conference to come.